JAJSI42D March 2016 – October 2019 DS250DF410

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要 (続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics

- 7.6 Timing Requirements, Retimer Jitter Specifications

- 7.7 Timing Requirements, Retimer Specifications

- 7.8 Timing Requirements, Recommended Calibration Clock Specifications

- 7.9 Recommended SMBus Switching Characteristics (Slave Mode)

- 7.10 Recommended SMBus Switching Characteristics (Master Mode)

- 7.11 Recommended JTAG Switching Characteristics

- 7.12 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Device Data Path Operation

- 8.3.2 Signal Detect

- 8.3.3 Continuous Time Linear Equalizer (CTLE)

- 8.3.4 Variable Gain Amplifier (VGA)

- 8.3.5 Cross-Point Switch

- 8.3.6 Decision Feedback Equalizer (DFE)

- 8.3.7 Clock and Data Recovery (CDR)

- 8.3.8 Calibration Clock

- 8.3.9 Differential Driver with FIR Filter

- 8.3.10 Debug Features

- 8.3.11 Interrupt Signals

- 8.3.12 JTAG Boundary Scan

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

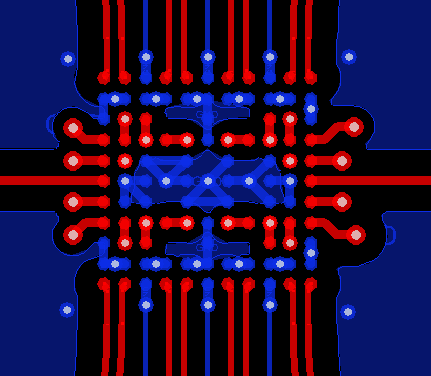

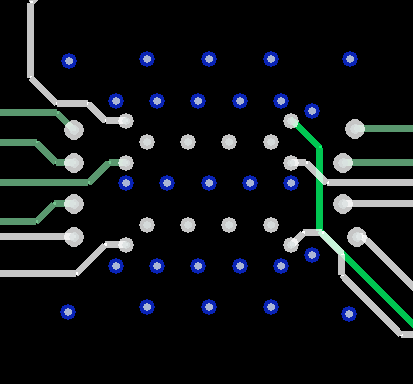

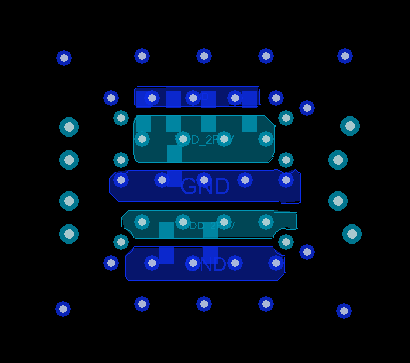

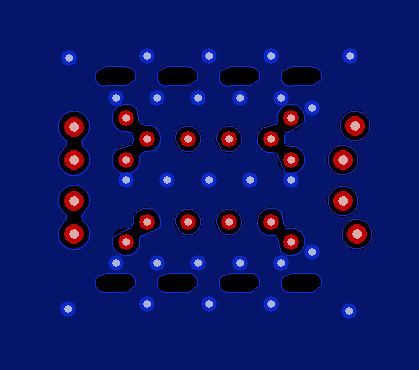

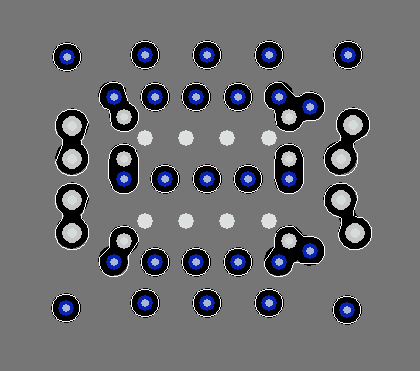

11.2 Layout Example

The following example layout demonstrates how all signals can be escaped from the BGA array using microstrip routing on a generic multi-layer stackup. This example layout assumes the following:

- Trace width: 0.159 mm (6.25 mil)

- Trace edge-to-edge spacing: 0.197 mm (7.75 mil)

- VIA-to-VIA spacing: 0.7 mm (27.9 mil) minimum; Note: 1.0 mm VIA-to-VIA spacing is also achievable if PCB manufacturing rules stipulate

- No VIA-in-pad used

- Note: Some TI test pins (i.e. NC_TEST[5:0]) are routed in this example layout, but in most applications these pins can be left floating.

Note that many other escape routing options exist using different trace width and spacing combinations. The optimum trace width and spacing will depend on the PCB material, PCB routing density, and other factors.

Figure 25. Top Layer

Figure 25. Top Layer  Figure 27. Internal Low-Speed Signal Layers

Figure 27. Internal Low-Speed Signal Layers  Figure 29. Bottom Layer

Figure 29. Bottom Layer  Figure 26. Layer 1 GND

Figure 26. Layer 1 GND  Figure 28. VDD Layer

Figure 28. VDD Layer