SLLSEA8A January 2012 – March 2016 SN65LVCP114

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6

Register Maps

- 9.6.1

SN65LVCP114 Register Mapping Information

- 9.6.1.1 Register 0x00

- 9.6.1.2 Register 0x01

- 9.6.1.3 Register 0x02

- 9.6.1.4 Register 0x03

- 9.6.1.5 Register 0x04

- 9.6.1.6 Register 0x06

- 9.6.1.7 Register 0x07

- 9.6.1.8 Register 0x08

- 9.6.1.9 Register 0x0A

- 9.6.1.10 Register 0x0B

- 9.6.1.11 Register 0x0C

- 9.6.1.12 Register 0x0D

- 9.6.1.13 Register 0x0F

- 9.6.1.14 Register 0x10

- 9.6.1.15 Register 0x11

- 9.6.1.16 Register 0x12

- 9.6.1.17 Register Descriptions

- 9.6.1

SN65LVCP114 Register Mapping Information

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

1 Features

- Quad 2:1 Mux and 1:2 Demux

- Multi-Rate Operation up to 14.2 Gbps Serial Data Rate

- Linear Receiver Equalization Which Increases Margin at System Level of Decision Feedback Equalizer

- Bandwidth: 18 GHz, Typical

- Per-Lane P/N Pair Inversion

- Port or Single Lane Switching

- Low Power: 150 mW/Channel, Typical

- Loopback Mode on All Three Ports

- I2C Control in Addition to GPIO

- DIAG Mode That Outputs Data of Line Side Port to Both Fabric Side Ports

- 2.5-V or 3.3-V Single Power Supply

- PBGA Package 12-mm × 12-mm × 1-mm, 0.8-mm Terminal Pitch

- Excellent Impedance Matching to 100-Ω PCB Transmission Lines

- Small Package Size Provides Board Real Estate Saving

- Adjustable Output Swing Provides Flexible EMI and Crosstalk Control

- Low Power

- Supports 10GBASE-KR Applications With Ability to Transparency for Link Training

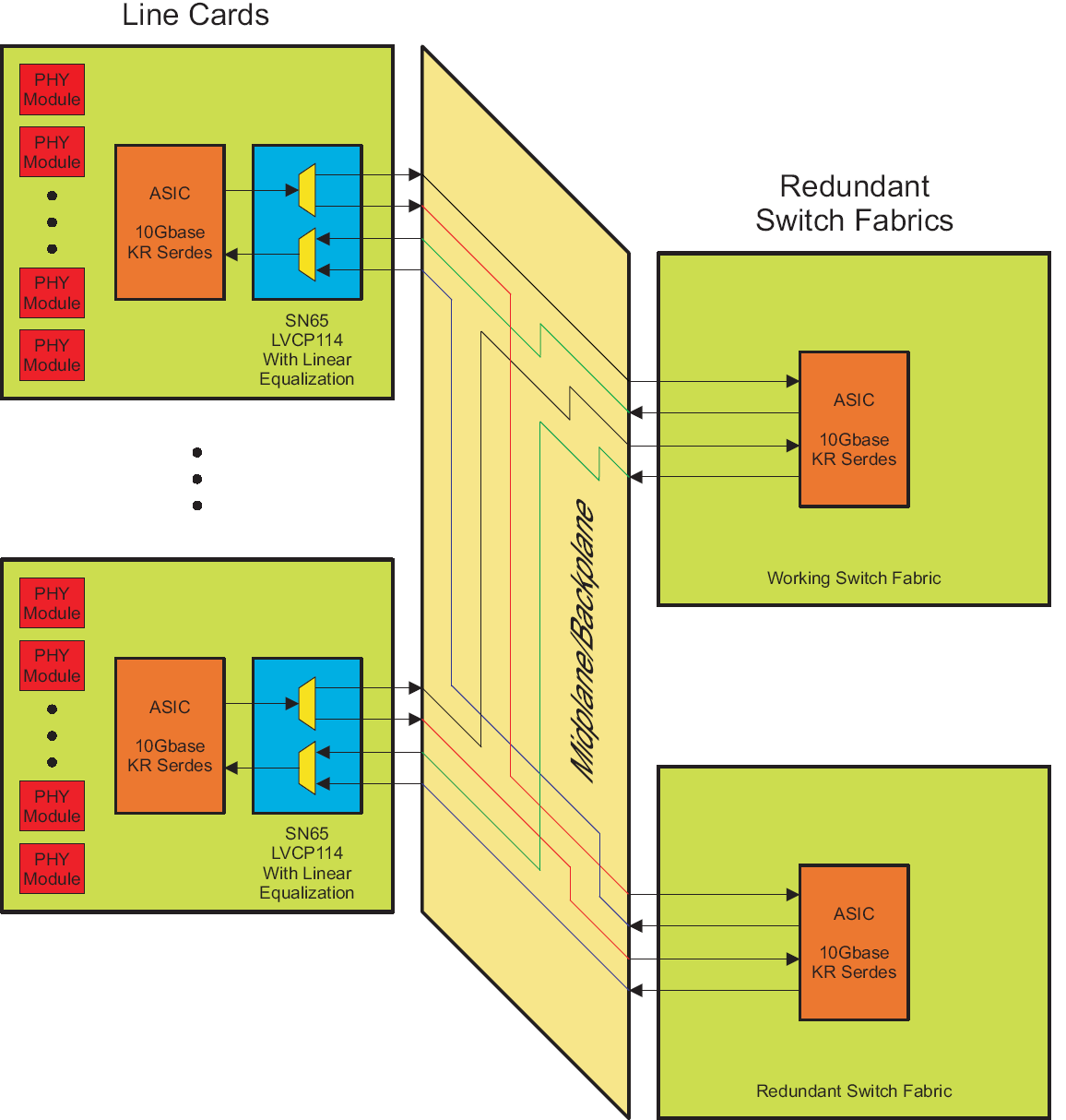

2 Applications

- High-Speed Redundancy Switch in Telecom and Data Communication

- Backplane Interconnect for 10G-KR, 16GFC

3 Description

The SN65LVCP114 device is an asynchronous, protocol-agnostic, low-latency QUAD mux, linear-redriver optimized for use in systems operating at up to 14.2 Gbps. The device linearly compensates for channel loss in backplane and active-cable applications. The architecture of SN65LVCP114 linear-redriver is designed to work effectively with ASIC or FPGA products implementing digital equalization using decision feedback equalizer (DFE) technology. The SN65LVCP114 mux, linear-redriver preserves the integrity (composition) of the received signal, ensuring optimum DFE and system performance. The SN65LVCP114 provides a low-power mux-demux, linear-redriver solution while at the same time extending the effectiveness of DFE.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| SN65LVCP114 | NFBGA (167) | 12.00 mm × 12.00 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

SN65LVCP114 Typical Implementation