JAJA186

## 電流ソース回路と電流シンク回路の実装と応用

このアプリケーション・ガイドは、次に示す回路の設計と 応用の基本的な参考書として使用されることを想定してい ます。

- ・電流ソース(吐き出し)回路

- ・電流シンク(吸い込み)回路

- ・フローティング電流ソース(吐き出し)回路

- ・電圧・電流変換回路(相互コンダクタンス増幅回路)

- ・電流・電流変換回路(カレント・ミラー回路)

- ・電流・電圧変換回路(トランスインピーダンス増幅回路)

このアプリケーション・ノートは網羅的な回路集ではな く、推奨される回路の抄録です。必要な場合は、推奨部品 の製品番号と部品値が示されます。追加の部品が安定性の ために必要な場合は、それも示されます。

経験が豊富な設計者の場合は、アプリケーションによって は敢えてこれらの部品を省略するという選択も可能です。 また、それほど経験を積んでいない設計者でも、このアプ リケーション・ガイドを見れば失敗なく回路の安定性を保 ちながら、正常に動作する回路を組むことができます。

紹介されているアプリケーションは、このアプリケーショ ン・ガイドの範囲を超えたレベルの設計を試みようとする 設計者の想像力に手がかりを与えることを目的としてい ます。

R. Mark Stitt

| 固定電流ソース回路の設計                                          | 3                |

|-------------------------------------------------------|------------------|

| IC製品REF200の電流ソース回路の記述                                 | 2                |

|                                                       |                  |

| REF200のピン接続: 50 $\mu$ A電流シンク回路用                       |                  |

| REF200のピン接続: 50 $\mu$ A 電流ソース回路用                      |                  |

| REF200のピン接続: 200 $\mu$ Aフローティング電流ソース回路用               |                  |

| REF200のピン接続: 300 $\mu$ A フローティング電流ソース回路用              | 6                |

| REF200のピン接続: フローティング電流ソース回路 400 $\mu$ A用              | 6                |

| REF200と外部オペアンプ1つを使用した抵抗プログラマブル電流ソース回路およびシンク回路: 電源レールお | よび100 <i>µ</i> A |

| よりも大きい出力電流(current out)への動作可能電圧を持つ電流ソース回路またはシンク回路     | 6                |

| 電流出力のある電流ソース回路またはシンク回路                                | 7                |

| リファレンス電圧を使用した電流ソース回路とシンク回路                            | 7                |

| 出力電流が100 $\mu$ Aより大きい浮遊電流ソース回路                        | 8                |

| アンプ1つと直列パス・エレメントを使用した電流ソース回路/シンク回路、およびカレント・ミラー回路      | 9                |

| 100 $\mu$ Aより大きい電流と非分離型電源を使用した浮遊電流ソース回路               | 11               |

| 出カインピーダンスの向上、高周波数パフォーマンス、高動作可能電圧を目的とする電流ソース回路のカスコー    | ーディング12          |

| FETを使用したカスコーディング                                      | 12               |

| REF200を使用したフローティング・カスコード接続型電流ソース回路 200 $\mu$ A        | 13               |

| REF200を使用したフローティング・カスコード接続型電流ソース回路300 $\mu$ A         |                  |

| REF200を使用したフローティング・カスコード接続型電流ソース回路400 $\mu$ A         |                  |

| ・<br>東流ソース同路のノイズの低減                                   | 1.1              |

| 固定電流ソース回路のアプリケーション                                  | 15 |

|-----------------------------------------------------|----|

| 電流ソース回路を使用したリファレンス電圧                                | 15 |

| リファレンス5mVを使用した、オペアンプのオフセット調整電圧回路(OFFSET ADJUSTMENT) | 16 |

| フローティング・リファレンス電圧を使用したウィンドウ比較回路                      | 17 |

| リファレンス電流を使用したRTD励起回路(RTD EXCITATION)                | 18 |

| リファレンス電流を使用したデッド・バンド回路                              | 19 |

| 双方向電流ソース回路                                          | 21 |

| 双方向電流ソース回路を使用した電圧制限回路                               | 21 |

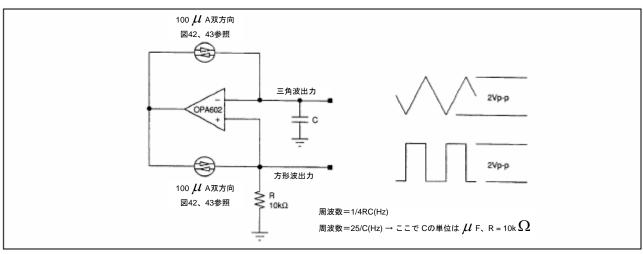

| 双方向電流ソース回路を使用した高精度三角波形発生回路                          | 22 |

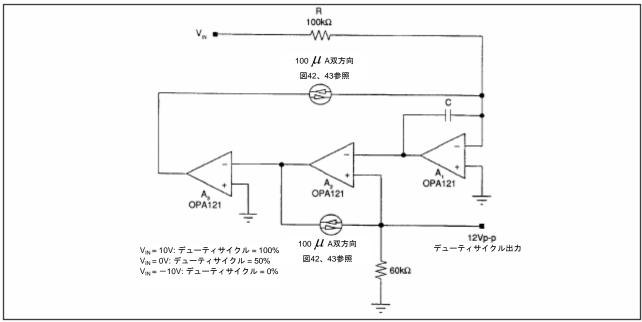

| 双方向電流ソース回路を使用したデューティ・サイクル変調回路                       | 23 |

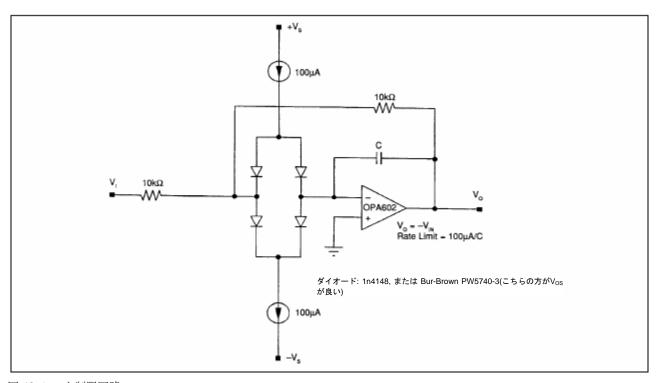

| スルー・レート制限回路                                         | 24 |

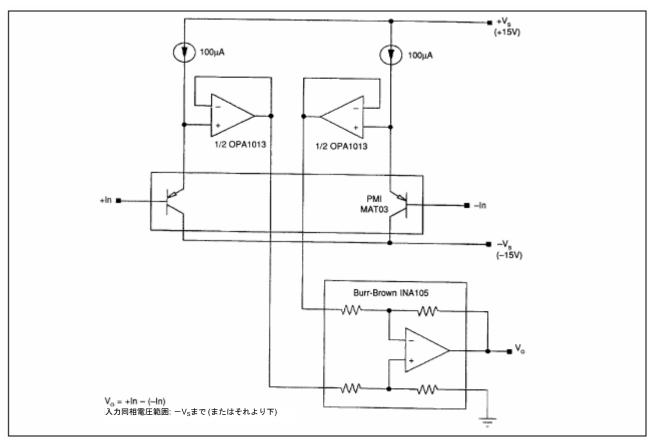

| 単電源計測アンプ                                            | 24 |

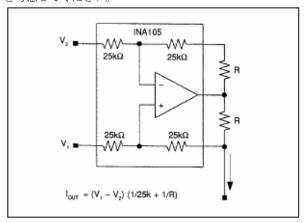

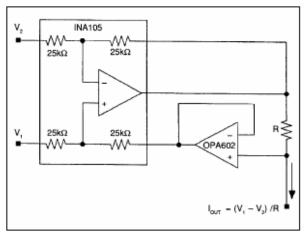

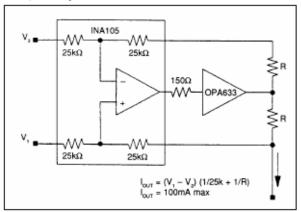

| INA105を使用した電圧制御電流ソース回路                              | 25 |

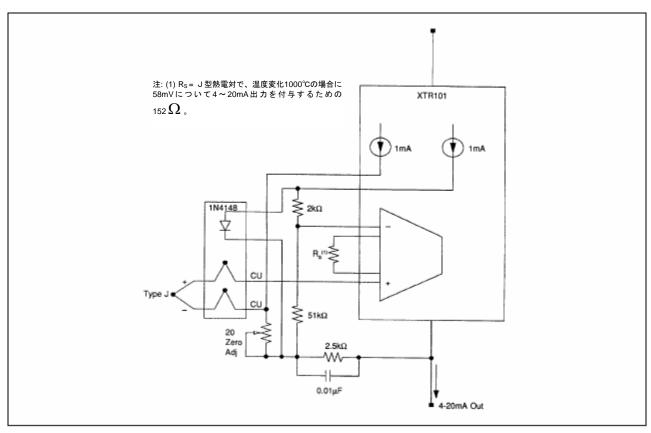

| 計測アンプ入力のある電圧制御電流ソース回路 XTR101                        | 26 |

| 単電源電圧制御電流ソース回路 XTR110                               | 26 |

| INA105を使用した、正負の電源レールに対するコンプライアンス電圧のある電流レシーバ回路       | 26 |

| INA105または INA117を使用したパワー・アンプ負荷電流監視回路                | 28 |

| RCV420を使用した、0~5V出力のある4 ~20mA電流ループ・レシーバ回路            | 29 |

| 仮想グラウンド電流 - 電圧変換回路                                  | 29 |

| 仮想グラウンドI/V変換回路を使用したフォトダイオード ・アンプ                    | 30 |

| 用語集                                                 | 33 |

| <b>窓</b> 苺と完美                                       | 33 |

#### 固定電流ソース回路の設計

#### IC 製品 REF200 の電流ソース回路の記述

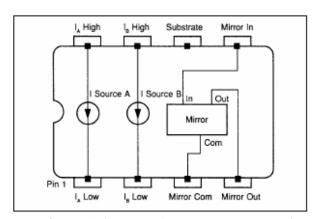

デュアル電流ソース回路REF200は、電流ソース回路 (current source) 2つとカレント・ミラー回路1つを8ピンのプラスチックDIPに収めた製品です(図1)。REF200の回路はBurr-BrownのDifet®(Dielectrically Isolated(誘電的に絶縁された)FET)プロセスを使用して製造されているため、3つの回路ブロックは互いに完全に独立しています。チップに電源を接続する必要はありません。2.5V以上の電圧を電流ソース回路に印加するだけで、定電流 $100~\mu$  Aが出力されます。標準的なドリフトは25ppm/°Cよりも小さく、出力インピーダンスは500M  $\Omega$  を超えます。

**※Difet**®は、Burr-Brown Corp.の商標です。

図 1. デュアル電流ソース回路REF200には、3つの完全に独立した回路ブロック(100 $\mu$ Aの電流ソース回路2つと、カレント・ミラー回路1つ)が含まれる。

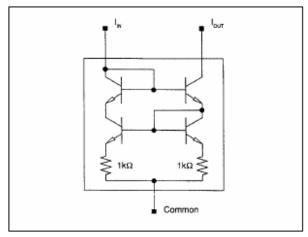

カレント・ミラー回路は多くの応用例で有効に利用できます。図2に示すように完全ウィルソン型のアーキテクチャを使用しており、高精度の抵抗を確実に実現するためにレーザトリミングを使用しています。

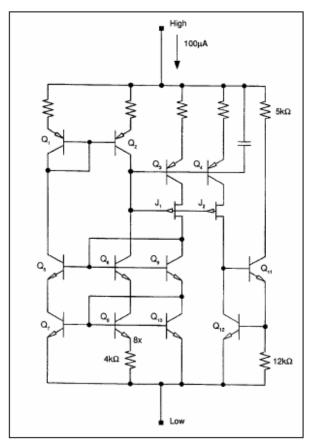

2つの電流ソース回路はそれぞれ、図3のように設計されています。正の温度係数の電流と負の温度係数の電流を結合することにより、ゼロ温度係数が実現されています。 正の温度係数の電流は、バンドギャップ回路で生成されます。

図 2. REF200のカレント・ミラー回路では、完全ウィルソン型アーキテクチャにより高精度を実現している。

カレント・ミラー回路 $Q_1-Q_2$ が、エミッタ面積比1:8の $Q_7$  と $Q_8$  に等しい電流を印加します。エミッタ間で絶対温度に比例した電圧差  $\cdots$  ( $\mathbf{k}\cdot\mathbf{t}/\mathbf{q}$ )・ $\mathbf{ln}(8)$  -が4 $\mathbf{k}$   $\Omega$  抵抗 に強制印加される結果、絶対温度に比例した電流約13  $\mu$  Aが抵抗に流れます。 $Q_{10}$  が  $Q_7$  とマッチし、また $Q_3$  が  $Q_4$  とマッチするため、絶対温度に比例した等しい電流が $Q_1-Q_4$  の4つのパスそれぞれに流れます。 $Q_4$  パスを流れる電流は、 $Q_{11}$  と  $Q_{12}$ によって形成される電流生成回路Vbe/ $12\mathbf{k}$   $\Omega$  にバイアスをかけます。 $Q_{11}$  からの負の温度係数の電流は、出力で合計されます。

抵抗 $4k\Omega$  と抵抗 $12k\Omega$  の温度係数についてウエーハ・レベルのアクティブ・レーザ・トリミングを施すことにより、精確なゼロ温度係数出力が実現されます。NPNトランジスタ $Q_5$ 、 $Q_6$ 、 $Q_9$  では $Q_7$  と $Q_8$  をカスコード接続して確度と出力インピーダンスを向上させます。同様に、 $J_1$  と $J_2$  では $Q_3$  と  $Q_4$ をカスコード接続します。PNPでなくFETのカスコード接続を使用すると、ベース電流に起因するノイズを除去できます。また、コンデンサによりループ補償が提供されます。

大多数のアプリケーションで使用するための実用的な値として、 $100~\mu$  Aが選ばれています。これは、多くのケースでセンサ励起に直接使用できるほど十分に高い値であると同時に、それより高い電流値は使用できないような低消費電力アプリケーションやバッテリ駆動アプリケーションでも使用できるほど低い値でもあります。また、出力電流がそれより高い場合は、チップ上の温度フィードバックと自己発熱により、出力インピーダンスが低減されます。

図 3. 電流ソース回路REF200のセルに、入力端子から電力が供給される。バンドギャップ・セルからの正の温度係数と、負の温度係数の電流を合計することにより、ゼロ温度係数を実現する。

#### REF200 のピン接続: 50 μ A 電流シンク回路

電流ソース回路 $100~\mu$  Aを基準として、どのような値の電流ソース回路でも簡単に構築できます。REF200はピン接続方法により、 $100~\mu$  Aに加えて、 $50~\mu$  A、 $200~\mu$  A、 $300~\mu$  A、 $400~\mu$  Aにすることが可能です。

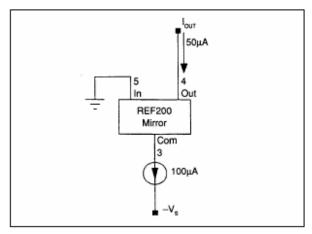

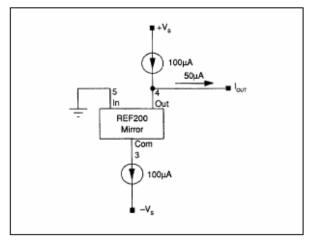

$50~\mu$  A 電流シンク回路には、図4の回路を使用します。  $100~\mu$  A 電流ソース回路は、カレント・ミラー回路のコモンに接続されています。カレント・ミラー回路の出力はその入力と同じであるため、 $50~\mu$  Aが入力からグラウンドまで流れ、出力は電流シンク回路  $50~\mu$  Aになります。

図 4. グラウンド基準のコンプライアンス電圧(compliance) の取れた電流シンク回路50  $\mu$  Aは、 $100~\mu$  A 電流ソース回路のひとつとREF200からのミラー回路を使用して作成できる。

#### REF200 のピン接続: 50 μ A 電流ソース回路

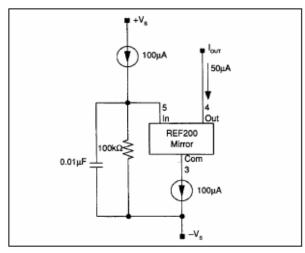

$50~\mu$  A電流ソース回路には、図5の回路を使用します。この回路は、電流シンク回路により第二の $100~\mu$  Aソース回路から $50~\mu$  Aが引かれて、ソース回路 $50~\mu$  Aが残った結果です。動作可能電圧は、グラウンドより低い値~正のレール2.5V以内の範囲の値となります。

図 5. グラウンド~+Vs-2.5Vの範囲の動作可能電圧を持つ 電流ソース回路50  $\mu$  Aは、電流ソース回路100  $\mu$  Aと REF200からのミラー回路を使用して作成できる。

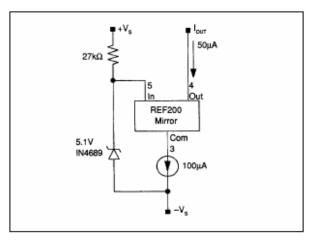

より負のレールに近い動作可能電圧が $50 \mu$ Aのシンク回路またはソース回路用に必要な場合は、図6か図7の回路を使用します。ここでは、抵抗1つと電流ソース回路、または抵抗バイアスを付加したツェナーダイオードを使用して、ミラー回路の入力は負のレールを基準としています。

図 6. もう一方の $100~\mu$  A電流と抵抗ひとつを使用してバイアス・ポイントの基準を負の電源レールに取ることにより、電流シンク回路  $50~\mu$  A(図 5)の動作可能電圧を-Vs+5Vに拡張できる。

図 7. 余分な電流ソース回路がない場合は、ツェナーダイオードを使用して、 $-V_s+5V$ への動作可能電圧を持つ電流シンク回路 $50~\mu$  Aにバイアスをかけることが可能。

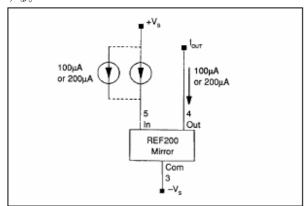

#### REF200 のピン接続: 200 μ A フローティング電流 ソース回路

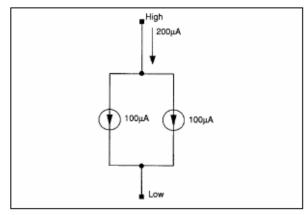

浮遊電流ソース回路  $200 \mu$  Aは、2つの電流ソース回路を図8に示すように並列に接続しただけのものです。負のレールにより近い動作可能電圧が必要な場合は、図9のミラー回路を使用します。ミラー回路の出力の振幅は、電流ソース回路単独の場合よりも1ボルト負のレールに近い値になります。

図 8. 浮遊電流ソース回路 200  $\mu$  Aの場合は単純に、REF200からの電流ソース回路 100  $\mu$  A2つを並列に配置する。

図 9. REF200からの電流ソース回路 100  $\mu$  Aまたは 200  $\mu$  Aをミラー化(mirror)して、コンプライアンス電圧 を向上させた電流シンク回路 100  $\mu$  Aまたは 200  $\mu$  Aを作成できる。

図 10.電流ソース回路100  $\mu$  A2つおよびREF200のミラー 回路を接続して、浮遊電流ソース回路300  $\mu$  Aを形成できる。

図 11. 電流ソース回路100  $\mu$  A2つと、REF200のミラー回路を接続して、浮遊電流ソース回路400  $\mu$  Aを形成する。

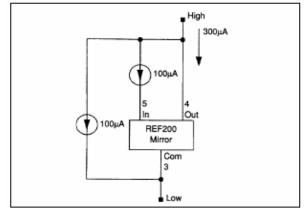

#### REF200 のピン接続: 300 µ A フローティング電流 ソース回路

浮遊電流ソース回路300  $\mu$  Aは、図10のように併せてストラッピングできます。この回路は、ソース回路100  $\mu$  Aとミラー回路から構成される電流ソース回路 200  $\mu$  Aを、他方の電流ソース回路100  $\mu$  Aと並列させることで形成されます。電流ソース回路 200  $\mu$  Aは、電流ソース回路100  $\mu$  Aをミラー回路の入力に接続して作られるため、100  $\mu$  Aがミラーの出力に流れ、200  $\mu$  Aがミラー・コモン回路を流れます。

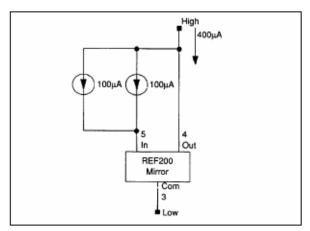

#### REF200 のピン接続: 400 μ A フローティング電流 ソース回路

$400~\mu$  A 浮遊電流ソース回路は、図11のように併せてストラッピングできます。これは基本的に図10の電流ソース回路  $200~\mu$  Aと同じですが、ミラー回路の入力に供給される電流が $200~\mu$  Aである点が異なります。この $200~\mu$  Aと、ミラー回路の出力を流れる $200~\mu$  Aが合計されて、 $400~\mu$  Aになります。

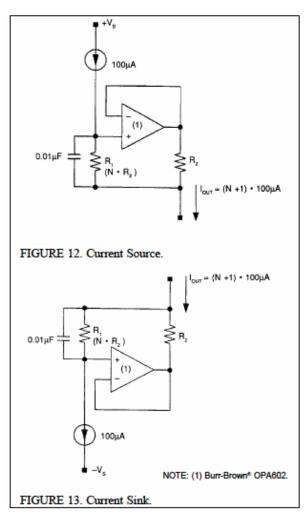

# REF200 と外部オペアンプ1 つを使用した抵抗プログラマブル電流ソース回路およびシンク回路:電源レールおよび 100 $\mu$ A よりも大きい出力電流)へのコンプライアンス電圧を持つ電流ソース回路またはシンク回路

抵抗2つ、オペアンプひとつ、リファレンスとしての電流 ソース回路 $100~\mu$  Aひとつを使用して、事実上どのような 値にもプログラム可能な電流ソース回路を構築することが できます。

図12の電流ソース回路は、リファレンス電流 $100 \mu$  Aより高いどのような値にもプログラム可能です。また、負の電源レール最大限までの幅広い動作可能電圧を持っていま

す。リファレンス電流 $100~\mu$  Aにより、オペアンプの非反転入力で電圧 $100~\mu$  A・ $R_1$ が強制印加されます。図のように $\mathbf{Difet}^{\otimes}$  オペアンプを使用すると、入力バイアス電流は無視できるほど小さくなります。オペアンプは、同じ電圧を $R_2$ に強制印加します。 $R_1$  が $\mathbf{N}$ ・ $R_2$ である場合、出力電流は  $(\mathbf{N}+1)$ ・ $100~\mu$  Aになります。オペアンプの入力同相電圧範囲とその出力が、 $R_1$ の電圧降下範囲内の負レールまでスイング可能である限りは、電流ソース回路は負のレール最大限までスイング可能です。 $R_1$ の電圧降下が十分大きければ、どのようなオペアンプでもこの要件を満たすことができます。図13は、同じ回路をひっくり返して、電流シンク回路として機能するようにしたものです。この回路は、正のレールへの動作可能電圧を持っています。

図12と13. 100  $\mu$  Aよりも大きい任意の出力電流と、+Vs または $-V_s$ までの動作可能電圧を持つプログラマブル電流 ソース回路の場合は、外部オペアンプ1つとプログラミング抵抗2つとともに、電流ソース回路100  $\mu$  Aをリファレンスとして使用する。

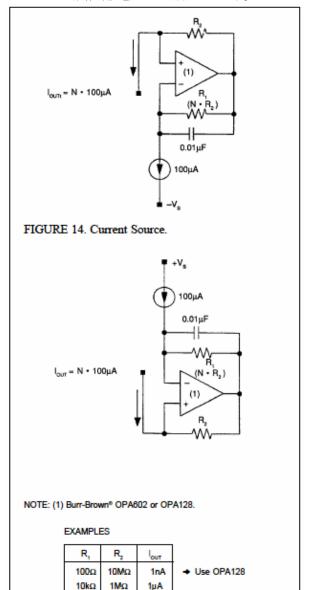

#### 電流出力のある電流ソース回路またはシンク回路

$100~\mu$  Aよりも低い電流の場合は、図14と15の回路を使用します。これらの回路は、事実上どのような値の電流にも  $(100~\mu$  Aより上の値にも下の値にも)プログラム可能です。この場合、電流ソース回路100 $\mu$  Aはオペアンプの反転入力で $R_1$  にリファレンスを形成します。このリファレンスは出力には接続されないため、その電流は電流出力信号には付加されません。したがって、 $R_1$  が $N\cdot R_2$ の場合には、出力電流は $N\cdot 100~\mu$  Aになります。電流ソース回路  $100~\mu$  Aの動作可能電圧が2.5Vであるため、図14の電流ソース回路の動作可能電圧は、負のレール範囲内で02.5V にしかなりません・オペアンプではそれ以上の電圧が可能な場合でも。同様に、図15の電流シンク回路は、正の電源レールまでの動作可能電圧2.5Vを持っています。

1mA

10ko

図14と15. 電源レールまでの動作可能電圧が必要ない場合は、外部オペアンプひとつとプログラミング抵抗2つとともに電流ソース回路100  $\mu$  Aをリファレンスとして使用するこの回路では、事実上どのような値の出力電流でも供給可能になる。

#### リファレンス電圧を使用した電流ソース回路とシ ンク回路

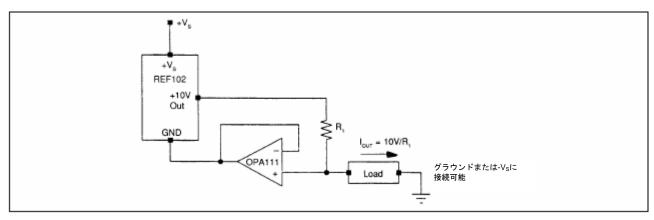

可能なかぎり確度の高い電流ソース回路を作るには、ツェナー・ベース(zener-based)のリファレンス電圧を使用します。REF200ではバンドギャップ型のリファレンスを使用しており、低電圧の二端子動作を可能にしています。多目的部品であるこちらの方が柔軟性は高く、優れたパフォーマンスを持ちますが、根本的な温度ドリフトや安定性については、TIの高精度の10Vリファレンス電圧、REF102に埋め込まれたツェナー・リファレンス電圧とは比べ物になりません。

図15Aに示す回路を使用したリファレンス電圧から、電流ソース回路を作成します。電圧フォロワ接続のオペアンプにより、リファレンス電圧のグラウンド接続が負荷電圧と等価にされます。次にリファレンス出力により、 $R_1$  に精確な10.0Vが強制印加され、電流ソース回路の出力が $10V/R_1$  になります。

電流ソース回路の負の出力での動作可能電圧は、オペアンプ入力のコモンモード電圧範囲または出力電圧範囲(2つのうち悪い方)によって制限されます。 $\pm 15$ V電源でOPA111を使用する場合は、負の動作可能電圧が-10Vになります。動作可能電圧がほぼ負の電源レール近くになる場合は、OPA1013のような単電源オペアンプを使用します。正の出力での動作可能電圧は、リファレンス電圧の最小+Vs の要件に制限されます。 $\pm 15$ V電源でREF102を使用する場合は、正のコンプライアンス電圧が+3.5Vになります。

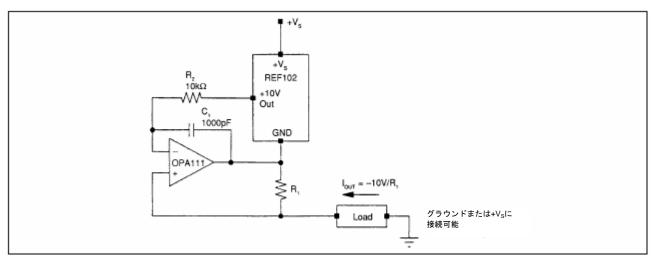

図15Bに示す回路を使用したリファレンス電圧で、電流シンク回路を作成します。オペアンプではリファレンス電圧のグラウンド接続と電流スケーリング抵抗 $R_1$ の両方を駆動して、リファレンス電圧の出力が負荷電圧と等価になるようにします。これにより、-10.0Vが $R_1$ に強制印加されて、電流シンク回路の出力が-10V/ $R_1$ になります。 $R_2$ ,  $C_1$ ネットワークによりオペアンプの周囲に局部帰還が供給され、ループの安定性を確保します。またこれにより、ノイズのフィルタリングも可能になります。ここに示された値では、リファレンス・ノイズのフィルタリングは、単極でf-3dB =  $1/(2 \cdot \pi \cdot R_2 \cdot C_1)$ により行われます。

電流シンク回路の負の出力動作可能電圧はオペアンプによって制限され、さらに $R_1$ の電圧低下10Vにより低減します。

図 15A. リファレンス電圧とオペアンプを使用した電流ソース回路

図 15B. リファレンス電圧とオペアンプを使用した電流シンク回路

±15V電源でOPA111を使用する場合は、負の動作可能電圧はグラウンドに対してのみ保証されます。単電源オペアンプOPA1013を使用する場合は、 負の動作可能電圧は-5V近くになります。

正の動作可能電圧はREF102に制限されますが、 $R_1$ にかかる 10V により改善されます。  $\pm 15V$  電源で動作する REF102の場合は、正の動作可能電圧は $\pm 10V$  (オペアンプの同相電圧入力範囲により制限される)です。

念頭に置いておかなければならないのは、リファレンス電圧をベースにした電流ソース回路の根本的な確度は、電流スケーリング抵抗の絶対的な確度に依存するということです。抵抗の絶対抵抗温度係数と安定性は、電流ソース回路の温度ドリフトと確度に直接影響します。これは、確度が抵抗比のみに依存する、図12~15に示す電流ソース回路リファレンスを使用した回路とは対照的です。抵抗ネットワークを使用する場合は特に、良好な絶対確度を得るよりも、良好な抵抗レシオ確度を得る方がはるかに容易です。リファレンス電圧を使用したこれらの電流ソース回路には、前述の回路のような動作可能電圧範囲がありません

が、最大限の確度が必須とされる場合には最適な選択となる可能性もあります。

#### 出力電流が 100 μ A より大きいフローティング電 流ソース回路

完全にフローティング状態のプログラマブル電流ソース回路が必要な場合は、図16に示す回路を使用します。図12の電流ソース回路と基本的に同じですが、 $R_2$ がMOSFETに駆動されている点が異なります。MOSFETのゲート、つまりオペアンプの入力には電流が流れないため、抵抗に流れ込んだ電流(そしてその電流のみ)はすべて残ります。したがって、電流ソース回路は完全にフローティング状態になります。

この回路でのオペアンプの電源は、他の回路でと同様、 ±Vsに接続する必要があります。また、オペアンプの入力 と出力の同相電圧の制限も遵守する必要があります。

図16. プログラマブル・フローティング電流ソース回路には、リファレンス1つ、外部オペアンプ1つ、プログラミング抵抗2つ、直列のパス・エレメント(a series pass element)1つからなる $100~\mu$  A 電流ソース回路を使用する。

#### アンプ1 つと直列パス・エレメントを使用した電 流ソース回路/シンク回路、およびカレント・ミ ラー回路

アプリケーションによっては、オペアンプの他に直列パス・エレメントを使用して電流ソース回路またはシンク回路を作成することが望ましい場合もあります。このアプローチを使用すると、カスケーディングという長所があるばかりでなく、電流出力を任意の高さにできます。

使用される回路は、図16のプログラマブル・フローティング電流ソース回路用のものと同じです。違いは、オペアンプの電源接続とリファレンス入力が両方とも固定電位に戻るようになっていることです。その結果は、電流ソース回路かシンク回路のどちらかになりますが、フローティング電流ソース回路にはなりません。長所は、出力が任意の値でよいことです。入力リファレンスより高い値でも低い値でも、あるいは同じ値でも構いません。

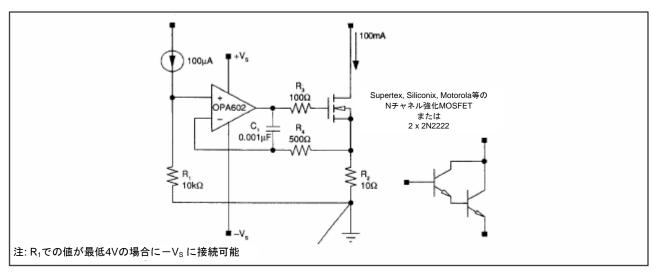

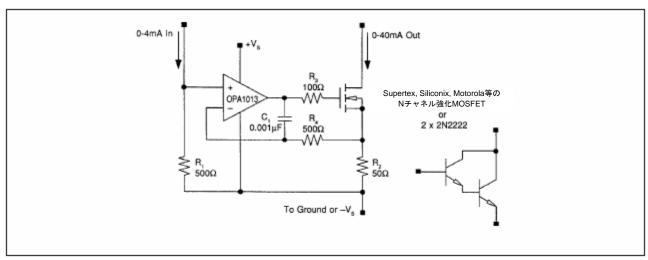

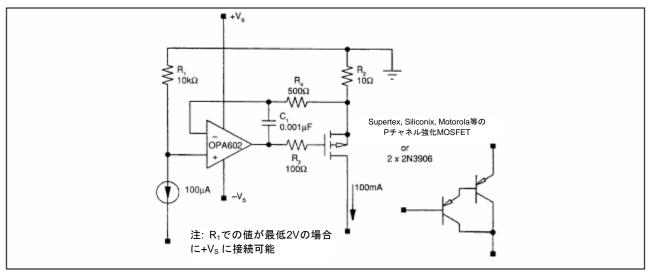

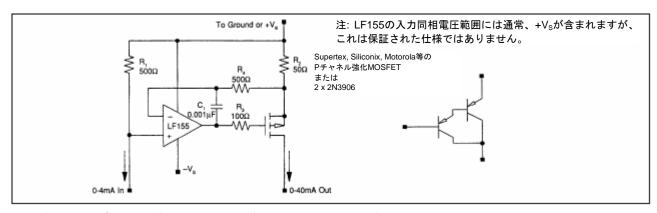

また、電圧ソースや、可変電圧入力さえもリファレンスとして使用できます。図17~20の例では、リファレンスとして使用される $100~\mu$  A 電流ソース回路を示しています。なお、電流ソース回路がリファレンスとして使用されているために、高精度カレント・ミラー回路としてこの回路を使用することもできます。マッチしたトランジスタ同士を使用しているミラー回路とは違い、このミラー回路ではミラー・レシオがどのような値でも高精度が維持されます。

パス・エレメントはバイポーラ、JFET、MOSFETのどれか、またはそれらの組み合わせになります。ここに挙げる例では、MOSFETが推奨されます。MOSFETのゲート電流は低いため、出力誤差が最小限にできるためです。また、非常に高い電流レーティングを持つMOSFETが使用可能であり、追加のドライバも必要としません。

多くの場合、バイポーラ・デバイスで十分であり、価格の低さと選択肢からも望ましい選択になります。バイポーラ・デバイスを使用すると、カスコーディングのセクションで説明しているように、ベース電流により、出力信号に新たな誤差が追加されます。ダーリントン接続されたバイポーラ・デバイスを使用すると、エラー電流が信号パスにフィードバックされ、入力トランジスタの順方向電流ゲイン  $(\beta)$  による誤差が低減されます。

ある種の高温アプリケーションでは、ダーリントン接続のバイポーラ・トランジスタの誤差がFETの誤差よりも低くなることもあります。経験則では、FETまたはMOSFETのゲート電流は温度が8°C上昇するごとに倍加しますが、これに対してバイポーラ・デバイスのベータの増加率はほぼ0.5%/°Cです。したがって、125°Cで動作する場合、FETのゲート電流は25°Cで動作する場合よりも約6000倍高くなりますが、バイポーラのベース電流は1.5倍も低くなります。

このアプリケーションのためオペアンプを選択する場合は、入力 バイアス電流、入力同相電圧範囲、出力電圧範囲 に特に注意を払う必要があります。

オペアンプのバイアス電流は入力電流に加算され、出力電流から減算されます。1:1のミラー回路アプリケーションの場合、誤差はバイアス電流のミスマッチか、アンプのIosだけです。 その他のレシオについては、誤差はアンプのバイアス電流全体と等価であると仮定します。 大多数のアプリケーションでは、Burr-BrownのOPA602等のDifet®低バイアス電流アンプを使用すれば、誤差は無視できるほど小さくなります。OPA602のIB は最大IpAです。

オペアンプの入力同相電圧範囲の限界は、必ず遵守する必要があります。例えば、電流シンク回路アプリケーションにおいてOPA602を使用する場合、オペアンプの負電源とその入力間の電圧は最低でも4Vである必要があります。多電源アプリケーションでは、 $R_1$  と  $R_2$  をグラウンドに接続しても、オペアンプの負電源を-5V または-15Vに接続しても問題はありません。単電源アプリケーション、または、 $R_1$ 、 $R_2$ 、およびオペアンプの $-V_8$  がすべて負電源に接続されている場合は、最低でも4Vの電圧低下が $R_1$ で維持される必要があります。

図 17. 直列パス・デバイスを使用したプログラマブル電流シンク回路

図 18. 直列パス・デバイスを使用したシンキング・カレント・ミラー回路

図 19. 直列パス・デバイスを使用したプログラマブル電流ソース回路

図 20. 直列パス・デバイスを使用したソーシング・カレント・ミラー回路

単電源オペアンプを使用すると、入力同相電圧範囲をOVにすることができます。特に単電源カレント・ミラー回路アプリケーションでは、入力と出力がゼロになることが望ましい場合がよくあります。OPA1013の入力同相電圧範囲はその負電源にまで及び、その出力範囲は負電源範囲の数mV以内になります。OPA1013はバイポーラ入力ですが、そのバイアス電流は十分低いため、大多数のアプリケーションで使用可能です。

部品 $R_3$ 、 $R_4$ 、および $C_1$  は、駆動するMOSFETの入力の容量性が高い場合に、補償ネットワーク(補償回路)を形成してアンプの安定性を確保します。多くの場合、これらの部品は省略できます。

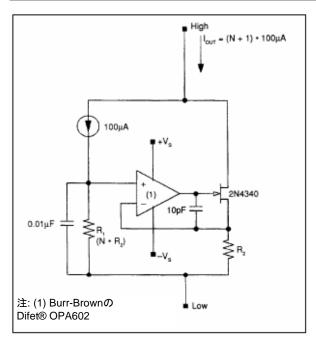

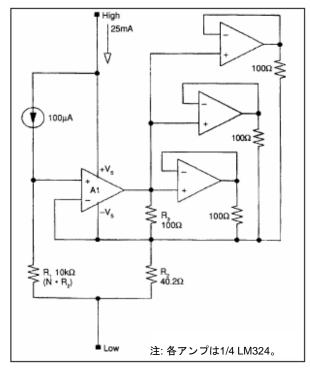

# 100 μ A より大きい電流と非分離型電源を使用したフローティング電流ソース回路

プログラマブル電流ソース回路が必要であり、かつ非分離型電源が使用可能な場合は、図21のフローティング電流ソース回路について考慮してください。ここでは、オペアンプの電源が電流ソース回路の入力端子に接続されています。オペアンプの静止電流は、出力電流の一部です。

特別な要件が2つあります。第1の要件は、単電源オペアンプ(負の電源レールを含む入力同相電圧範囲を持つオペアンプ)を使用しなければならないということです。また、出力電流がオペアンプの静止電流よりも大きくなければなりません。

回路は基本的に図12と同じです。 $R_1$  を通って流れる  $100~\mu$  A電流により、 $A_1$ の非反転入力にフローティング状態のリファレンス電圧が生成されます。負の電源ピンから流れるオペアンプの静止電流は、 $R_2$ に流れ込む電流に合流します。オペアンプの出力は $R_2$  に必要な付加電流を駆動するため、 $R_2$ の電圧低下は $R_1$ の電圧低下にマッチします。 $R_1$ が $N\cdot R_2$ の場合は、出力電流は  $(N+1)\cdot 100~\mu$  Aです。示された値で計算すると、出力電流は25mAになります。

図 21. クワッド型単電源オペアンプを使用した25mAフローティング電流ソース回路には、外部電源の必要がない。

オペアンプの出力は、 $100\,\Omega$  抵抗を通して $R_2$ に接続されます。 $A_1$  に駆動される電流により、0.5V近くの電圧低下が $R_3$ で発生します。他の3つのオペアンプは電圧フォロワとして接続され、同じ値の電圧低下が他の3つの $100\,\Omega$  抵抗で発生するようにされます。したがって、各オペアンプからの出力電流は等価となり、負荷も等分に割り当てられます。この技法を使用すると、任意の数の出力オペアンプ10mAを並列させて、高出力電流を得ることができます。

## 出カインピーダンスの向上、高周波数パフォーマンス、高コンプライアンス電圧を目的とする電流 ソース回路のカスコーディング

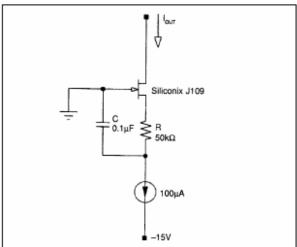

#### FET を使用したカスコーディング

カスコーディングを使用すれば、どのような電流ソース回路でも、出力インピーダンスと高周波数パフォーマンスを向上させることができます。REF200等の高精度電流ソース回路や、これまで紹介した各種回路のどれかを使用して始めれば、どのような用途にも十分に使用できる電流ソース回路を構築することも比較的容易に行えます。

カスコーディングは、動作可能電圧の増加にも使用できます。カスコード接続された電流ソース回路の動作可能電圧は、カスケーディング・デバイスの電圧レーティングのみに制限されます。100ボルト単位、または1000ボルト単位もの動作可能電圧が可能です。

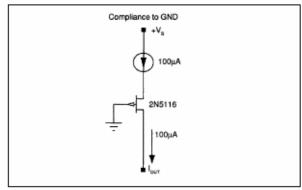

カスコーディングとは、図 22に示すように、直列パス・エレメントを使用して負荷から電流ソース回路をバッファリングすることです。ここでは、NチャネルのJFET出力が電流ソース回路を出力からカスコーディングしています。JFETのゲートはグラウンドに接続されており、そのソースは電流ソース回路に、そのドレインは負荷に接続されています。負荷電圧の変動はJFETのドレインで拾われますが、ソース電圧は比較的安定した状態を保ちます。このようにして、負荷の電圧変化とは無関係に、電流ソース回路の電圧は変化せず、JFETドレインで失われる電流はありません。カスコード接続された電流シンク回路のACパフォーマンスは、JFETのACパフォーマンスに近くなります。

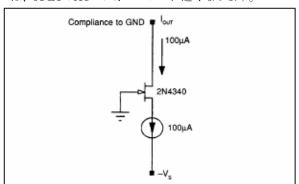

図22. カスコード接続型電流シンク回路(動作可能電圧はグラウンド基準)

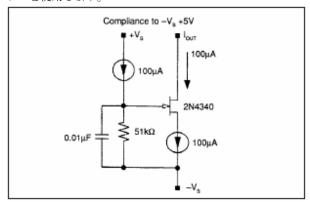

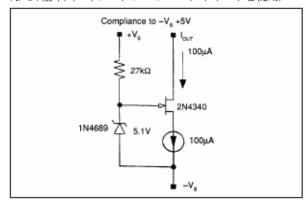

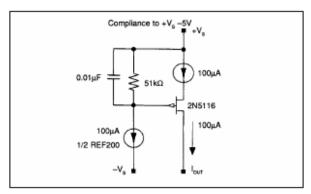

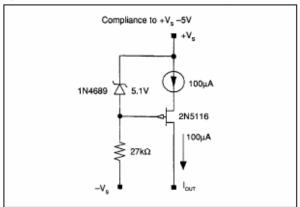

JFETのゲートはグラウンド接続のため、出力動作可能電圧はグラウンド電圧付近で制限されます。電流シンク回路に必要な動作可能電圧がそれより大きい場合は、図23と24に示すように、JFETのゲート電圧の基準を負のレールより数ボルト上にすることができます。図23では、ゲートの電圧は第2の電流ソース回路からバイアスをかけられた抵抗から導出されています。電流ソース回路が使用できない

場合は、図 **24**のように抵抗からバイアスをかけられたツェナーを使用します。

図 23. カスコード接続型電流シンク回路(動作可能電圧は-Vs+5V基準) (バイアスにツェナー・ダイオードを使用)

図 24. カスコード接続型電流シンク回路(動作可能電圧は-Vs+5V基準) (バイアスにツェナー・ダイオードを使用)

図 25. カスコード接続型電流ソース回路 (コンプライアンス電圧はグラウンド基準)

電流ソース回路に実装するには、図25  $\sim$ 図27に示すように、回路の上下を反転させてPチャネルのJFETを使用します。

大多数のアプリケーションでは、JFETを使用すると最良のカスコーディング・デバイスができますが、バイポーラ・トランジスタとMOSFETを使用することもできます。

MOSFETを使用すると、JFETに等しいACおよびDCパフォーマンスを提供できます。バイポーラ・デバイスを使用すると、高周波特性が向上する可能性がありますが、DC出力インピーダンスについては制限があります。バイポーラでカスコード接続された電流ソース回路の出力インピーダンスは、コレクタ電圧と連動したベース電流の変化によって制限されます。バイポーラでカスコード接続された電流ソース回路の最大出力インピーダンスはb・Roです。ここでbはバイポーラ・デバイスの電流ゲイン、Roはその出力インピーダンスです。

図 26. カスコード接続型電流ソース回路(動作可能電圧は-Vs+5V基準) (バイアスに電流ソース回路と抵抗 を使用).

図 27. カスコード接続型電流ソース回路(動作可能電圧は-Vs+5V基準) (バイアスにツェナー・ダイオードを使用)

#### REF200 を使用したフローティング・カスコード 接続型電流ソース回路 200 μ A

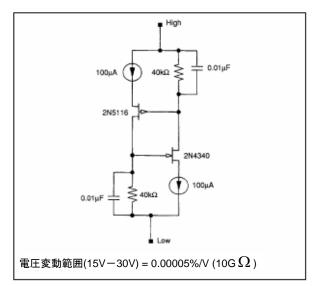

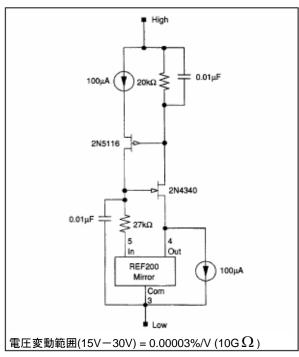

10G  $\Omega$  を超える標準出力インピーダンスを持つフローティング・カスコード接続型電流ソース回路も容易に実装することが可能です。REF200と外部デバイス数個を使用すれば、 $200~\mu$  A、 $300~\mu$  A、 $400~\mu$  Aの各ソースをまとめて接続できます。

200  $\mu$  Aのフローティング・カスコード接続型流ソース回路を図28に示します。相互にバイアス電圧をかけるカスコード接続型電流ソース回路1つと、カスコード接続型電流シンク回路1つを使用して構成されています。動作可能電圧の下限は、ゲートのリファレンス電圧の和によって約

8Vに制限されています。動作可能電圧の上限は、FETのより低いほうの電圧定格によって制限されます。

図 28. カスコード接続型 200  $\mu$  A 浮遊電流ソース回路

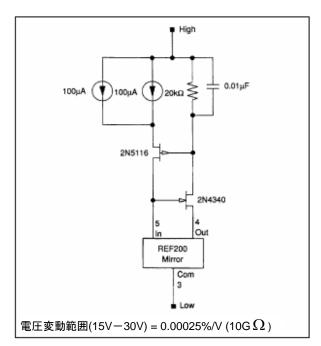

#### REF200 を使用したフローティング・カスコード 接続型電流ソース回路 300 μ A

フローティング電流ソース回路300  $\mu$  Aを図29に示します。図28の電流ソース回路200  $\mu$  Aに似ていますが、カスコード接続型シンク部の電流ソース回路がミラー回路から導出されている点が異なります。シンク回路のカスコード接続用のゲート・リファレンス電圧は、ミラー入力と27k  $\Omega$  抵抗の直列結合から導出されます。追加の100  $\mu$  Aは、もうひとつの100  $\mu$  A電流ソース回路をシンク回路のカスコード接続デバイスに組み込むことで得られます。動作可能電圧の制限は、200  $\mu$  Aカスコード接続型ソース回路と同じです。

#### REF200 を使用したフローティング・カスコード 接続型電流ソース回路 400 μ A

フローティング・カスコード接続型電流ソース回路  $400~\mu$  Aを図30に示します。 $300~\mu$  A カスコード接続型電流ソース回路に似ていますが、REF200の2つの電流ソース回路の並列結合によって導出されたカスコード接続型電流ソース回路 $200~\mu$  Aにミラー回路が駆動される点が異なります。ミラー回路の動作可能電圧が約1V良いため、この回路の動作可能電圧の下限は、前の2つの回路よりも1V向上しています。

動作可能電圧の上限は、より低い定格電圧のFETの絶縁破壊によってのみ制限されます。

図 29. カスコード接続型 300 µA 浮遊電流ソース回路.

図 30. カスコード接続型 400  $\mu$  A 浮遊電流ソース回路. W)

#### 電流ソース回路のノイズの低減

現在のシステムの多くでは、ノイズが確度の最終的な制限となっています。またシステムによっては、低ノイズ電流ソース回路を使用することでパフォーマンスを向上させることもできます。電流ソース回路のノイズは、リファレンス電圧のノイズ低減に使用されるのと同じ原理を使用したフィルタリングによって低減可能です。フィルタリングに

よるノイズ帯域幅の削減により、帯域幅削減量の平方根分だけノイズ総量を低減することが可能です。

図31は、ノイズ低減型電流ソース回路の一例です。FET カスコード接続型回路をベースに、RCノイズ・フィルタ 回路を追加しています。FETには電流ソース $100~\mu$ Aから バイアス電圧がかかるため、正確なDC電圧が回路に強制 印加されます。

コンデンサが無いと、電流ソース回路からのノイズは直接出力に供給されます。コンデンサでは、 $1/(2 \cdot \pi \cdot R \cdot C)$ の-3dBの周波数、つまりこの例では約30Hzでノイズをフィルタリングします。この周波数より低い値でのフィルタリングでは、それ以上ノイズが低減されなくなります。30Hzという極がすでに電流ソース回路の1/fコーナー周波数よりも低く、また1/f領域ではフィルタリングによるノイズの低減は不可能だからです。同様に、FETと抵抗のノイズもフィルタリングされません。それでもこの回路を使用すると、標準的な $20pAl\sqrt{Hz}$ から $1pAl\sqrt{Hz}$ より低い値にまでノイズを低減できます。

図 31. 電流ソース回路からの電流ノイズはこの回路を使用してフィルタリング可能。

ノイズ低減回路で使用する抵抗の値により、最終的なパフォーマンスが決定されます。抵抗のノイズはその値の平方根とともに増加しますが、そのノイズ劣化効果により、ノイズのリニアリティが低下します。したがって、抵抗増分の平方根の分だけノイズが低減されることになります。ノイズ低減の実質的な限界は、抵抗に課される可能性のある電圧低下です。

数学的には、抵抗が原因の電流ノイズは、抵抗のサーマル・ノイズを抵抗値で除算した値になります。

$$I_{R \, NOISE} = \frac{\left(1.3 \cdot 10^{-10}\right) \sqrt{R}}{R} = \left(1.3 \cdot 10^{-10}\right) / \sqrt{R}$$

50k  $\Omega$  抵抗を使用した場合、理論上のノイズ最小値は 0.6pA/ $\sqrt{Hz}$  になり、10k  $\Omega$  抵抗では1.3pA/ $\sqrt{Hz}$  になります。10k  $\Omega$  抵抗と50k  $\Omega$  抵抗の両方、および

Siliconix J109 FETを使用した回路でのノイズ測定値は、20%以内の誤差でこれらの理論値と合致します。

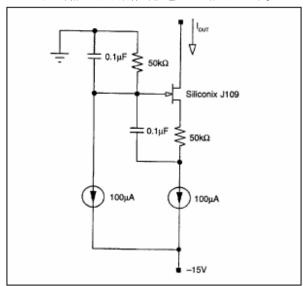

図31のノイズ低減回路では、動作可能電圧の下限がグラウンド電圧付近になっています。動作可能電圧の下限電圧がグラウンド電圧より低くする場合は、図32の回路を使用します。

ノイズ低減の他にも、これらの回路にはいくつかFETのカスコード接続型電流シンク回路の長所があります。 $G\Omega$ 領域の出力インピーダンス、ACパフォーマンスの向上、FETのみに制限される動作可能電圧の上限などです。

図 32. 電流ノイズフィルタリング回路(動作可能電圧はグランドより低い)

#### 固定電流ソース回路のアプリケーション

#### 電流ソース回路を使用したリファレンス電圧

REF200のような安価で使いやすい電流ソース回路を使用すれば、設計上の問題の多くを容易に解決できます。アプリケーションの範囲は無限ですが、これから紹介する回路のコレクションはいくつかの幅広いカテゴリで設計者の思考を刺激することを目的としています。そのカテゴリとは、固定リファレンス電圧、フローティング・リファレンス電圧、電流励起、固定リファレンス電流、リファレンス電流のステアリング、バイアスなどです。

電流ソース回路は、さまざまな方法でリファレンス電圧を形成する手段として機能します。単にリファレンス電圧を使用するだけではない理由とは?電流ソース回路を使用すると、抵抗がひとつしかなくても任意の値のプログラマブル電圧源を提供できるためです。リファレンス電圧を低くする必要はしばしば生じますが、このアプローチを使用すれば、リファレンス電圧1mVを得ることが、リファレンス電圧10Vを得るのと同じくらい容易になります。同様に、電圧の基準をどこからでも — 正のレールからも、

負のレールからも、回路の中間にある任意の点の浮遊電圧 からも取れるようになります。

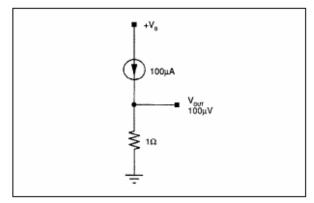

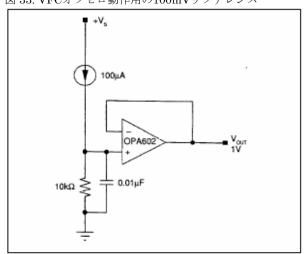

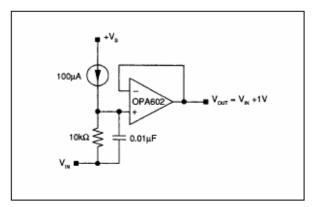

リファレンス電圧に駆動されるインピーダンスが高い場合は、抵抗から導出されたリファレンス電圧からの出力電圧を直接使用できます。図33のリファレンス電圧100  $\mu$  Vは、オフ・ゼロ(off-zero)基準電圧を必要とする電圧・周波数コンバータ(VFC)のオートゼロ(auto-zero)・アプリケーションで直接使用できます(ゼロ周波数を測定するには大変な時間がかかるため、オフ・ゼロ技法はVFCの較正によく使用されます)。出力インピーダンスを低くする必要がある場合は、図34に示すように単純なバッファを追加することもできます。

図 33. VFCオフゼロ動作用の100mVリファレンス

図 34. バッファリングされたリファレンス電圧

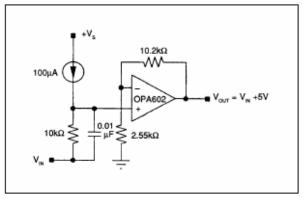

フローティング・リファレンス電圧の場合は、図34Aに示すように、単純にリファレンスのローサイド(電圧設定抵抗のグラウンド接続側)を駆動します。オペアンプの入力の同相電圧範囲と出力範囲によって課せられたスイング限界に加えて、リファレンスのハイサイドのスイングもREF200の動作可能電圧の下限によって、正のポジティブ・レールから2.5Vまでに制限されていることに注意してください。ローサイドのスイングはオペアンプのみに制限されます。リファレンス電圧が約3Vより上の場合は、図34Bのようにゲインを追加することでこの限界は取り除けます。この例

では、リファレンスの設定抵抗の1Vが出力側で5Vに増幅 されます。

出力とオペアンプの入力の間には常に4Vが存在するため、 ハイサイドのスイングは電流ソース回路の動作可能電圧や オペアンプ入力の同相電圧範囲の制限を受けません。オペ アンプの出力スイングの能力によってのみ制限されます。 リファレンス電圧が約3Vよりも低い場合、ハイサイドの動 作可能電圧は電流ソース回路の動作可能電圧によって制限 されます。このような状況では、図34Cの回路を使用する ことを考慮します。この場合、オペアンプの非反転入力 は、もう一方のオペアンプ入力と、他方の端子を(オペアン プの)出力に接続した電圧設定抵抗に電流ソース回路が接続 された状態で駆動されます。ハイサイドの動作可能電圧 は、オペアンプにのみ制限されます。この回路のもうひと つの長所は、入力インピーダンスが高いことです。短所 は、ローサイドの動作可能電圧に限界があることです。オ ペアンプ入力の同相電圧範囲とは無関係に、電流ソース回 路の動作可能電圧により、負のレールまでのスイング電圧 が2.5Vに制限されます。

図 34A. フローティング・リファレンス電圧.

図 34B. フローティング・リファレンス電圧。ハイサイドの動作可能電圧の限界はオペアンプの出力スイング能力のみで決まる。

図 34C. フローティング低リファレンス電圧。ハイ・インピーダンス入力駆動電圧とハイサイド動作可能電圧の限界は、オペアンプの出力スイング能力のみで決まる。

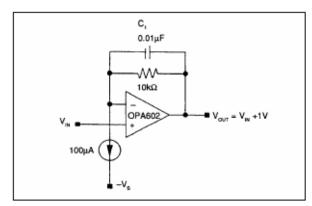

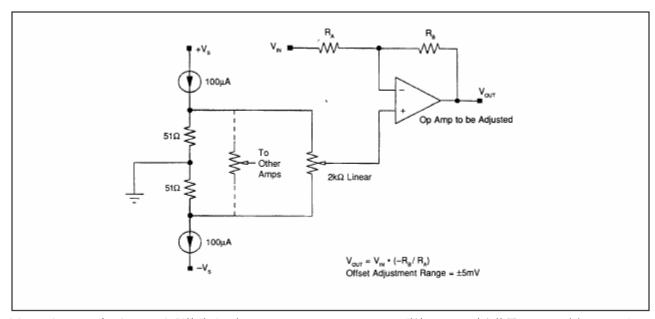

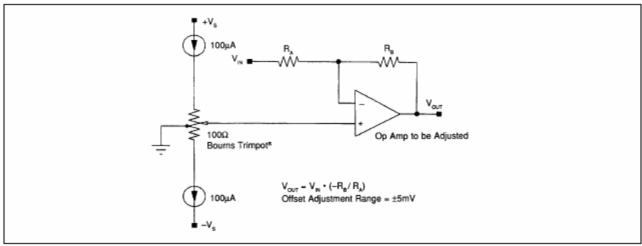

# リファレンス 5mV を使用した、オペアンプのオフセット調整電圧回路(OFFSET ADJUSTMENT)

オペアンプのオフセット調整電圧回路も、ミリボルトレベルのリファレンス電圧用のアプリケーションです。多くのオペアンプ、特にデュアル型およびクワッド型には、オフセット調整電圧ピンが備わっている場合でさえ、それを使用するとオフセット電圧ドリフトと安定性が劣化するおそれがあります(たとえば、標準的なバイポーラ入力オペアンプのドリフトは、オフセット調整電圧1ミリボルトごとに $3\mu$   $V/^{\circ}$ C 増加します)。外部オフセット調整電圧回路は、これらの問題を解決するために一般的に使用されています。

図 35. オペアンプのオフセット調整電圧回路では、REF200の2つの100  $\mu$  A電流ソース回路を使用して、正確な $\pm 5 \text{mV}$  リファレンスを提供する。

図 36. Bourns社のTrimpotRを使用した、オペアンプのオフセット調整電圧回路

従来の外部オフセット調整電圧回路を使用すると、独特の問題が発生する可能性があります。これらの回路の多くは、オペアンプの電源をリファレンスとして使用しています。電源の変動は、オペアンプの入力に直接供給されます。この誤差は、電源変動除去比の劣化として表れます。同様に、電源からのノイズはオペアンプの入力換算ノイズとなって表れます。

図35~36の回路を使用すると、このような問題を解決できます。REF200の電流ソース回路では、安定したオフセット電圧の調整用に、±5mVリファレンス電圧を提供しています。このアプローチにより、電源の変動やノイズ、ドリフトに関連する問題のない、真に高精度のオフセット調整電圧が得られます。

図35の回路では、グラウンドに接続された1対の51 $\Omega$ 抵抗を使用して、リファレンス $\pm 5$ mを設置しています。このリファレンスに接続したトリマーポットにより、 $\pm 5$ mVのオ

フセット調整電圧範囲が得られます。追加のポットを接続することもできますが、 $\pm 5 \mathrm{mV}$ より大きな範囲を得るためには、並列抵抗が必ず $50\,\Omega$  より大きくなるようにしてください。

図36に示す2番目の回路では、Bourns社の特殊なポテンショメータをひとつ使用しています。これはオペアンプのオフセット調整電圧用に設計されたものです。素子の中央に付いているタップは、グラウンドに接続できます。この接続を使用すると、最初の回路で必要だった抵抗51 $\Omega$ を使用せずにすみます。

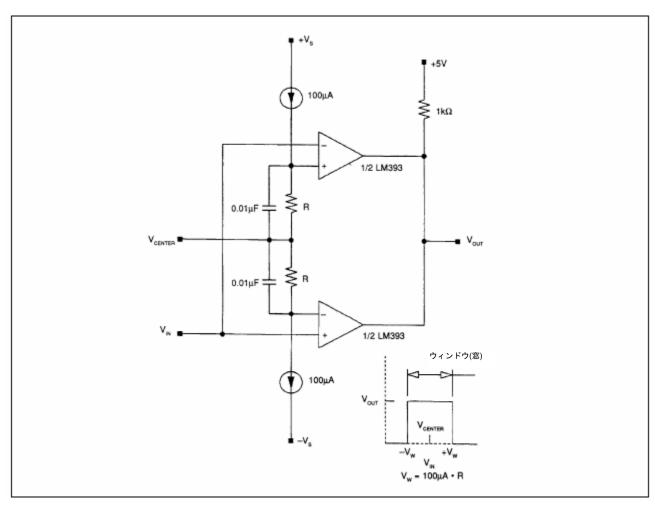

#### フローティング・リファレンス電圧を使用した ウィンドウ比較回路

ウィンドウ・コンパレータ (図37)は、フローティング・リファレンス電圧アプリケーションの一例です。ここでは、1対の電流ソース回路を使用して、 $V_{CENTER}$ 入力によって駆

動されるフローティング・バイポーラ・ウィンドウ電圧を提供します。 $V_{\rm I}$  が $V_{\rm CENTER}$  + 100  $\mu$  A ・Rよりも上か、 $V_{\rm CENTER}$  - 100  $\mu$  A・Rよりも下の場合には、 $V_{\rm O}$  がLowになります。

それ以外の場合は、 $V_{O}$  の値はHighになります。プログラミング抵抗の値をさまざまに変えて使用することにより、必要であれば、 $V_{CENTER}$  値の前後の閾値を非対称に設定できます。

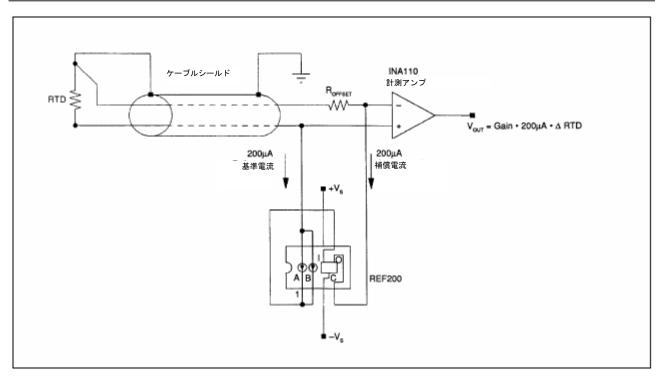

#### リファレンス電流を使用した RTD 励起回路

電流ソース回路は、RTD(測温抵抗体)などの抵抗型センサの電流励起回路によく使用されます。RTDの位置は遠い場合が多いのですが、その場合は、接続配線による電圧低下

により過剰な誤差(errors)が発生する可能性があります。 通常、この問題を解決するには、4線ケルビン接続を使用 します。4線のうち2線は、電流励起信号をRTDに搬送する ために使用します。残りの2線は、RTDの電圧のセンシン グに使用します。センス接続には電流が流れないため、配 線抵抗が原因のエラーは発生しません。

問題は、配線追加のコストが非常に高くなるということです。図38に示す3線回路ならば、配線を1つ節約できます。RTD 1k $\Omega$ の励起には200  $\mu$ Aが使用され、カレント・ミラー回路からのマッチング電流がグラウンド接続で強制印加されます。その結果、2線での電圧低下が起こるため、エラー電流がキャンセルされます。

もうひとつ注目すべきことは、(シールドとして示されている)共通配線をひとつ使用すれば、複数のセンサを提供できるということです。追加されるRTD ひとつにつき必要な追加配線ペアはひとつだけです。

図 37. 電圧プログラマブル・ウィンドウ・センターのあるウィンドウ・コンパレータ、および抵抗のプログラマブル・ウィンドウの幅

図 38. 3線抵抗補償を使用したRTD励起

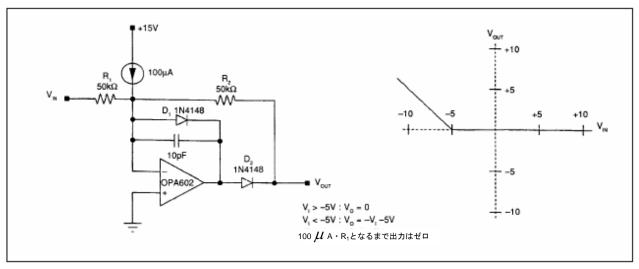

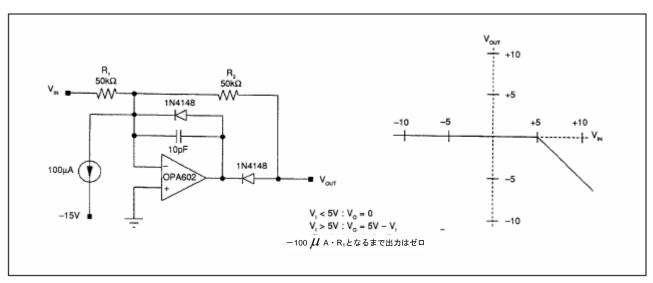

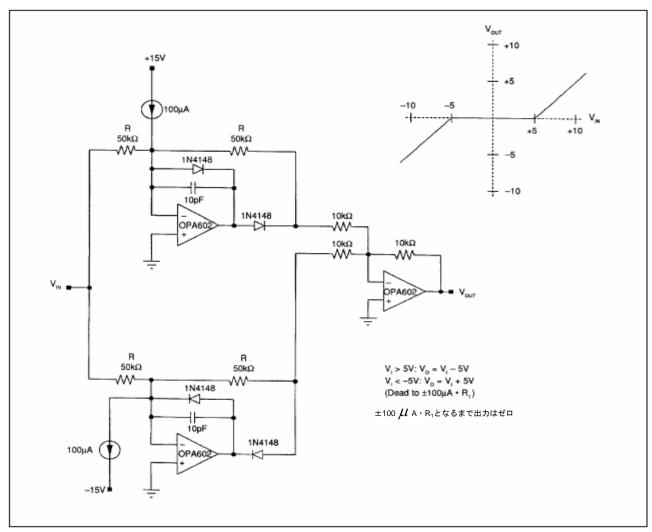

#### リファレンス電流を使用したデッドバンド回路

サーボ制御システムでは、デッドバンド回路と電圧制限回路がよく使用されます。図39と図40に示す高精度デッドバンド回路では、固定リファレンスとして電流ソース回路を使用する方法を紹介しています。これがどのように動作するかを理解するために、リファレンス電流がなければ、回路は反転半波整流回路になるということに注目してください。正の入力によりオペアンプの出力が負側に駆動され、帰還電流が順バイアス電圧のかかった $D_1$ を流れます。逆バイアス電圧のかかった $D_2$ には電流が流れないため、出力は $R_2$ によって仮想グラウンドで保持されます。

負の入力により、 $D_2$ に順バイアス電圧がかけられ、出力が正側に駆動されます。出力への帰還電流が $R_2$ を通ることにより、ダイオード・ドロップ電圧が原因のエラー電流が除去され、回路は高精度ユニティ・ゲイン・インバータ( $V_0 = -V_I$ )として機能します。(リファレンス電流を付加すると入力に事前バイアスがかかり、 $R_1$ を流れる入力電流が $100~\mu$  Aを超えるまで出力が仮想グラウンドのままになります。)

$V_I < \pm 100~\mu$  A・ $R_I$ となるまで出力はゼロ(デッド)になります。またリファレンス電圧に接続した高精度抵抗を通して入力に事前バイアスをかけるという方法もありますが、この方法ではノイズ・ゲインが付加されるため、出力でオフセット、ドリフト、ノイズが増加するおそれがあります。

図 39. 高精度の正のデッドバンド回路.

図 40. 高精度の負のデッドバンド回路

図 41. 高精度二重デッドバンド回路.

負のデッドバンド回路用としては、図40の回路を使用しま す。これはダイオードを反転させた回路と同じです。

二重デッドバンド回路用としては、図41に示す回路を使用 します。正負両方のデッドバンド回路を第三のアンプでつ ないで使用します。

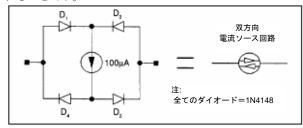

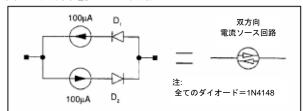

#### 双方向電流ソース回路

電流を扱う長所のひとつは、電流はダイオードやスイッチを用いれば誤動作なくステアリングできるということです。漏れによって電流が失われることのない限り、電流信号と直列に発生する電圧降下が電流の確度を減少させることはありません。

図42の双方向電流ソース回路は、様々な用途に使える回路構築ブロックであり、ダイオード・ステアリングの優れた一例です。基本的には、この二端子素子は、DC端子間に接続された電流ソース回路を持つ全波ブリッジ整流回路です。左の端子の正信号は、右の端子について、 $D_3$ と $D_4$ に逆バイアスをかけ、 $D_1$ と $D_2$ を通る電流を正確にステアリングします。負の信号はこの状態を逆転させ、同じ電流を逆方向に正確にステアリングします。

動作可能電圧が1ダイオード・ドロップ電圧分高くする場合は、図43の双方向電流ソース回路を使用します。この回路の短所は、電流ソース回路が最低でも2つ必要になることと、前述の回路には備わっていた電流マッチングが失われることです。

図 42. 双方向電流ソース回路.

図 43. コンプライアンス電圧を向上させた双方向電流ソース回路

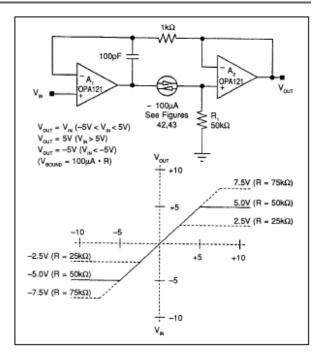

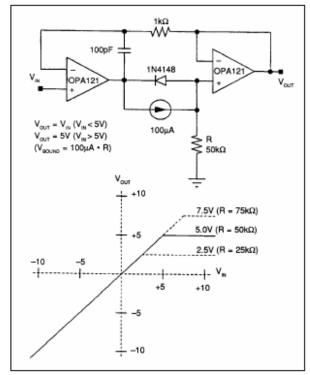

#### 双方向電流ソース回路を使用した電圧制限回路

図44の高精度二重電圧制限回路では、双方向電流ソース回路を使用します。この回路の動作を理解するには、 $R_1$ がなければ、この回路は高精度ユニティゲイン・アンプとして機能するということに着目してください。入力信号は $A_1$ の非反転端子に接続されています。反転端子への帰還電流は、双方向電流ソース回路、 $A_2$ による電圧フォロワ、 $1k\Omega$  抵抗を通ります。電流ソース回路からの電流が $100\mu$  Aより低い必要がある場合は飽和状態になり、双方向電流ソース回路全体の総電圧低下量は、約2V+2ダイオード・ドロップ電圧よりも低くなります。

図 44. 高精度二重電圧制限回路.

図 45. 高精度電圧制限回路.

1k **(2)** 抵抗には電流が流れないため、回路の出力電圧は入力電圧と等しくなる必要があり、A<sub>2</sub> が原因の誤差および電流ソース回路の電圧低下が解消されます。1k-100pFネットワークにより、帰還ループでの余分な位相ずれに対する補償が行われます。

$\mathbf{R}_1$  を追加しても、回路は依然として、 $\mathbf{R}_1$  を通る電流が  $100~\mu$  Aよりも低くなるような小信号用のフォロワとして 機能します。

電流が $100 \mu$  Aに達すると電流ソース回路がアクティブになり、出力電圧が制限されます。双方向電流ソース回路を使用すると回路は両方向で対称的に電圧制限を行います。

一方向のみに電圧制限が必要な場合は、図45に示すように、双方向電流ソース回路を電流ソース回路とダイオード1つに置き換えます。反対方向の制限が必要な場合は、電流ソース回路とダイオードの極性を反転させます。

#### 双方向電流ソース回路を使用した高精度三角波形 発生回路

図46の高精度三角波形発生回路では、2つの双方向電流ソース回路を利用します。一方の回路では、高精度電流信号をステアリングしてオペアンプの反転入力に接続した積分コンデンサに流れ込ませます。もう一方の回路では、高精度電流をステアリングしてオペアンプの正の端子に接続した $10k\Omega$  抵抗に流れ込ませ、 $\pm 1V$ のヒステリシスを提供します。その結果、高精度三角波出力 $\pm 1V$ と方形波出力  $\pm 1V$ を生成する弛張発振器が形成されます。

図 46. 高精度三角波形発生回路

図 47. 高精度デューティ・サイクル変調回路.

#### 双方向電流ソース回路を使用したデューティ・サ イクル変調回路

図47の高精度デューティ・サイクル変調回路は、三角波形発生回路の変形です。ここでは、積分コンデンサの代わりに $A_1$ とCを使った真の積分回路を使用します。これにより、入力抵抗100k $\Omega$ を通るグラウンド基準の信号の加算が可能になります。入力信号がない時の出力は、デューティ・サイクル50%の方形波になります。入力信号は、100k $\Omega$ 抵抗を通って積分回路に合流します。積分回路はその後、一方向には高速で、その反対方向には低速でスルーを行います。その結果、出力信号のデューティ・サイクルがリニアに変調されます。入力信号によって出力周波数に多少ばらつきが出るため、変調はパルス幅ではなくデューティ・サイクルであるといわれます。デューティ・サイクル変調回路で扱う周波数が一定している場合は、 $A_2$ の反転入力と直列に抵抗をひとつ追加して、その入力を抵抗結合クロック信号で駆動します。

デューティ・サイクル変調回路の中に、真の積分入力があることに注目してください。これは、入力信号と高精度三角波の間に接続された比較回路(コンパレータ)を使用するだけの、従来の変調回路とは対照的です。従来のアプローチでは、交差部で入力ノイズが比較回路の帯域幅で通過するため、ジッタが発生していました。積分入力を使用すると、入力ノイズを除去するだけでなく、積分入力を入力ノイズ(例えば60Hz)と同期させて、ノイズの影響を完全にノッチアウトすることも可能になります。ひとつ以上の完全なノイズ信号サイクルに対して積分を発生させた場合、ノイズ信号の振動が正確に平均化されます。

図 48. レート制限回路.

図 49. 単電源計測アンプ.

#### スルー・レート制限回路

インダクタを駆動している場合には特に、信号のスルー・ レートを制限する必要のあるアプリケーションもありま す。図48のレート制限回路では、電流のステアリング用 に、別の方法でダイオード・ブリッジ回路を使用していま す。ここでは、2つの電流ソース回路の一方をブリッジ回 路の正の端子、もう一方を負の端子に接続しています。コ ンデンサがなければ、回路はユニティゲイン反転アンプと して動作します。 $10k\Omega\sim10k\Omega$ 抵抗ネットワークを通 る帰還電流は、ブリッジ回路の左側を駆動します。それに 続くブリッジ回路の右側では、オペアンプの反転入力を駆 動します。ダイオードのミスマッチが原因の電圧オフセッ トは、図中に指定のあるようなモノリシックのブリッジ回 路を使用すれば軽減できます。積分コンデンサを追加する と、仮想グラウンド電圧を維持するために充電電流と放電 電流を流す必要が生じます。しかしその電流が $100 \mu$  Aを 超えると、ブリッジ反転回路によりバイアスがかけられ、 入力信号レートに関係なく、出力スルー・レートが  $100 \mu A/^{\circ}$ Cまでに制限されます。

#### 単電源計測アンプ

単電源のシステムはよく使用されるため、この環境で動作 する計測アンプを用意することは非常に重要です。単電源 オペアンプはずいぶん前から入手可能でしたが、単電源計 測アンプはそうではありませんでした。その上、従来の方 法では、単電源オペアンプだけを使用して単電源計測アン プを作ることはできません。従来の計測アンプトポロジー では、出力も入力と同様に、負のレールまでスイングする 必要がありました。オペアンプによっては電源レール近く までスイングできるものもありましたが、電源レールいっ ぱいまでスイングできるようなアンプ出力はありませんで した。負荷を駆動している場合は特にそうでした。

図49の単電源計測アンプ回路を使用すると、PNP入力トランジスタのマッチドペアを使用して、入力信号をレベルシフトしてVbeの分だけ上げるというシンプルな方法で、この問題を解決できます。

トランジスタは、REF200の中の電流ソース回路100  $\mu$  A によって、エミッタ・フォロワとしてバイアスされます。 続く回路は、従来のオペアンプ3つの計測アンプです。 OPA1013は単電源動作用に設計されており、その出力は負のレール近くまでスイング可能であるため、入力アンプとして使用されます。

Burr-BrownのINA105は、差動アンプとして使用されます。すべての重要な抵抗マッチングは、INA105の管理下にあります。

通常、単電源IAの同相電圧範囲は、86dBよりも良い標準的なCMRの場合には、負のレールより0.5V低い電圧までになります。

#### INA105 を使用した電圧制御電流ソース回路

Howland電流ポンプに修正を加えると(図50~52)、非常に多くの用途に使用できる電圧制御電流ソース回路になります。差動入力を備えているため、ひとつの入力をグラウンドに接続し、もう一方を駆動して反転または非反転伝達関数を得ることも可能です。入力を両方とも駆動した場合、出力電流は入力間の電圧差に比例します。

さらに、シンク電流またはソース電流どちらか一方の電流 ソース回路とは異なり、この電流ソース回路はバイポーラ 出力となり、シンク電流にもソース電流にもなります。

クリティカルな抵抗マッチング要件と抵抗温度係数トラッキング要件のために、今まではこの回路が使用できる場合は限られていましたが、差動アンプ製品INA105を使用すれば、1%抵抗2つを追加して、この回路を容易に実装することができます。

外部抵抗のマッチングが重要となりますが、外部抵抗2つは内部抵抗25k $\Omega$ に追加されるため、マッチング要件は抵抗の比率により軽減されます。

電流ソース回路の出力インピーダンスは、差動アンプの同相電圧除去比 (CMR)に比例します。外部抵抗によって発生する差動アンプの帰還抵抗のミスマッチはCMRを劣化させ、電流ソース回路の出力インピーダンスを低下させます。ユニティゲイン差動アンプでは、100dBのCMRに対して抵抗マッチ0.002%が必須です。外部抵抗の値と出力インピーダンス要件によっては、外部抵抗のトリミングが必要になることもあります。

外部抵抗の値が大きくなる場合は、図51の代替回路の使用 を考慮してください。

図 50. 差動入力とバイポーラ 出力を使用した電圧制御電流ソース回路

図 51. 差動入力、バイポーラ出力、帰還抵抗のエラー電流を除去するための回路の付いた電圧制御電流ソース回路

差動アンプの帰還抵抗を駆動するには追加のアンプがひと つ必要になりますが、必要な外部抵抗はひとつだけであ り、マッチングやトリミングの必要もありません。 どの場合でも、電流ソース回路の出力インピーダンスは次

どの場合でも、電流ソース回路の出力インピーダンスはかの関係によって近似できます。

$$Z_0 = R_X \cdot 10^{[CMRR/20]}$$

ここで、

$Z_0$  =電流ソース回路の等価出力インピーダンス  $[\Omega]$  CMRR = 差動アンプの同相電圧除去比 [dB] (図50)

$R_X = 外部抵抗と25k\Omega$ 抵抗の並列結合

$$R_{X} = \frac{R \cdot 25k\Omega}{R + 25k\Omega}$$

(図51)

$R_X =$ 外部抵抗 [ $\Omega$ ]

INA105では、20mAを吐き出し、5mAを吸い込むことが可能です。出力電流を高くする必要がある場合は、図52のように電流バッファを追加します。図に示すOPA633により、出力電流が±100mAの範囲になります。バッファは帰還ループの内側にあるため、そのDC誤差(エラー)が電流ソース回路の確度に影響することはありません。他のバッファを使用する場合は、バッファの帯域幅が十分に大きく、回路の安定性を低下させるおそれのないことを確かめてください。

電圧・電流変換回路内に電圧ゲインが必要な場合は、ゲイン10の差動アンプとしてINA106を使用します。

覚えておく必要があるのは、ソース・インピーダンスは差動アンプの入力抵抗に直接追加されるため、差動アンプのパフォーマンスが低下するおそれがあるということです。 ソース・インピーダンスに $5\Omega$ のミスマッチがあると、 INA105のCMRRが80dBにまで低下します。アンプまたはその他の低インピーダンス・ソースから回路を駆動してい

る場合は問題がありませんが、電源インピーダンスが高めの場合は、差動アンプの駆動入力をバッファリングするか、差動アンプの代わりにINA110等の計測アンプを使用してください。

図 52. 差動入力と電流増加バイポーラ出力を使用した電圧制御電流ソース回路

#### 計測アンプ入力のある電圧制御電流ソース回路 --XTR101

XTR101は、2線式4~20mA電流ループ・アプリケーション用に設計されたフローティング電流ソース回路であり、高精度計装アンプ入力のある電圧制御電流ソース回路です。また1mAマッチド電流ソース回路も2つ含まれており、これによりXTR101は、熱電対、RTD(測温抵抗体)、サーミスタ、歪みゲージ・ブリッジ回路等の様々なトランスデューサのリモート信号処理に適した製品になっています。

図53では、XTR101が温度制御電流ソース回路として接続 されています。温度検知素子は熱電対であり、また冷接点 補償はダイオードにより提供されます。

XTR101の製品データ・シート(PDS-627)にはこのデバイスの動作の詳細が記載されており、また他のアプリケーションもいくつか紹介されています。

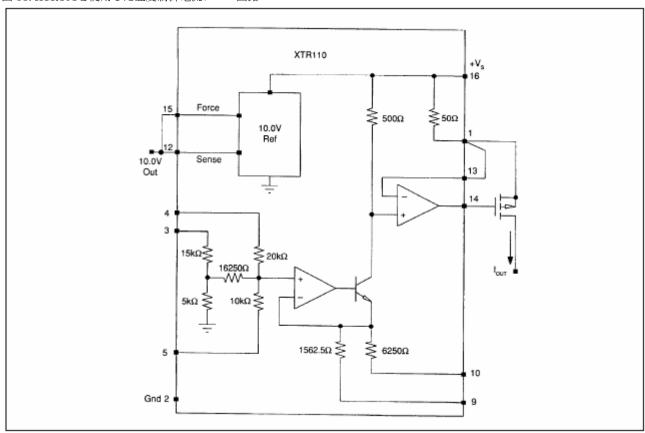

#### 単電源電圧制御電流ソース回路 -- XTR110

XTR110は、単電源の高精度電流 - 電圧変換回路です。3線式4~20mA電流伝送用に設計された製品ではありますが、アプリケーションとしてはより一般的な、電圧 - 電流ソース回路に使用することもできます。図54に示すように、XTR110に含まれるのは、スパン・オフセット(0V入力時4mA出力)用の高精度10.0Vリファレンスおよび入力抵抗ネットワーク、グラウンド基準の入力信号を出力電流シンク回路に向けるための電圧 - 電流変換回路、電流シンク回路の出力を電流ソース回路に向けるためのカレント・ミラー回路です。

カレント・ミラー回路のゲイン比は10:1であり、外部トランジスタを使用して内部熱帰還を最小限に抑え、確度を向上させます。ミラー回路のトランジスタは外付けであるため、外部ミラー・レシオ設定抵抗をひとつ追加して、任意の高出力電流を実現できます。

入力信号と出力信号がゼロになることができるよう電圧 - 電流変換回路でもカレント・ミラー回路でも単電源オペアンプを使用します。ミラー回路のオペアンプの場合は、同相電圧の範囲が正の電源レールまでになります。

次の表は、XTR110を端子接続だけで可能になる入力スパン〜出力スパンの範囲を示しています。

| 入力範囲                                              | 出力範囲                                                         | ピン                                                   | ピン                                           | ピン                                                    | ピン                                     | ピン                                                     |

|---------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|-------------------------------------------------------|----------------------------------------|--------------------------------------------------------|

| <b>(V)</b>                                        | <b>(mA)</b>                                                  | <b>3</b>                                             | <b>4</b>                                     | <b>5</b>                                              | <b>9</b>                               | <b>10</b>                                              |

| 0-10<br>2-10<br>0-10<br>0-10<br>0-5<br>1-5<br>0-5 | 0-20<br>4-20<br>4-20<br>5-25<br>0-20<br>4-20<br>4-20<br>5-25 | Com<br>Com<br>+10<br>+10<br>Com<br>Com<br>+10<br>+10 | Input<br>Input<br>Input<br>Com<br>Com<br>Com | Com<br>Com<br>Com<br>Input<br>Input<br>Input<br>Input | Com<br>Com<br>Com<br>Com<br>Com<br>Com | Com<br>Com<br>Open<br>Com<br>Com<br>Com<br>Open<br>Com |

詳細な説明とアプリケーションについては、製品データ・シートPDS-555をお求めください。

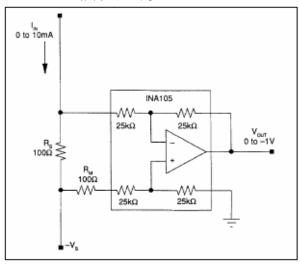

#### INA105 を使用した、正負の電源レールに対する コンプライアンス電圧のある電流レシーバ回路

高精度抵抗 $(V = I \cdot R)$ に電流を供給するだけで、電流信号の計測を行うことができます。必要であれば、抵抗で形成された電圧をオペアンプでバッファリングしたり、増幅したりすることもできます。

同相信号がセンス抵抗の電流リターン端部に現れる場合は、計装アンプ(IA)を使用して同相信号を除去し、出力信号の基準をグラウンドに取ります。ただし、従来のIAの限界は、同相電圧入力範囲が10Vより低い値に限られているという点にあります。

センス抵抗の電流リターンの基準をより高い同相電圧に取る必要のある場合は、次に挙げる差動アンプのどれかの使用について考慮してください。

| モデル    | 入力同相電圧範囲             | その他の機能 |

|--------|----------------------|--------|

|        | (1)                  |        |

| INA105 | $\pm 20 \mathrm{V}$  |        |

| INA117 | $\pm 200 \mathrm{V}$ |        |

| RCV420 | ±40V                 | (2)    |

注: (1) 標準的な±15V 電源での動作について指定された同 相雷圧入力範囲

(2) 4~20mA入力で0~5V出力を得るための高精度リファレンスとオフセット回路も含まれる

図 53. XTR101を使用した温度制御電流ソース回路

図54. 高精度単電源電圧 - 電流ソーストランスミッタ回路 -- XTR110

図55は、INA105を使用した電流レシーバ回路です。入力電流信号は、負の電源レールに接続された $100\Omega$  抵抗 $R_s$ で検知されます。センス抵抗をグラウンドでなく電源レールに接続することにより、電流トランスミッタ回路で得られる電圧低下が最大限になります。

INA105内の帰還抵抗が分圧回路として働き、同相電圧入力が二分圧されます。 したがって、最大±20Vの同相電圧入力信号が、オペアンプの入力で±10V以下という許容可能なレベルにまで減衰されます。

図 55. 電流・電圧変換回路(負の電源レール基準) マッチング抵抗 $R_M$ ではINA105の抵抗マッチを保持し、高い同相電圧除去比(CMR)を維持します。  $100\,\Omega$  という値は 差動抵抗 $25k\,\Omega$  と比べると小さいため、 $86dB\sigma$ CMRを維持するには許容差1%で十分です。

INA105では、ゲイン1で出力信号の基準をグラウンドに取ります。入力が $0\sim10$ mAの場合は、出力は $0\sim-1$ V(-100V/Aの伝達関数)になります。正の伝達関数が必要な場合は、差動アンプの入力ピンを入れ替えます。電流信号の基準を正のレールに取る場合は、センス抵抗とその他の差動アンプ入力をそのポイントに接続するだけですみます。

差動アンプの入力インピーダンス25k $\Omega$ は、入力電流信号の一部の分流によりわずかな誤差の原因となります。非反転構成では、マッチング抵抗により差動アンプのゲインが低下しますが、非反転入力の分流入力インピーダンスが

50k  $\Omega$  であるため、ユニティゲイン差動アンプの場合は、誤差が同じであることが分かります。センス抵抗100  $\Omega$  の場合、誤差は0.4%近くになります。確度を上げるためには、もう少し高い値のセンス抵抗を選択して、次の式に従って誤差を補償します。

$$R_{S} = R_{M} = \frac{25k \cdot X}{25k - X}$$

ここで、

X=所要の伝達関数 [V/A]

例:

図55の1V/10mA (100V/A)の場合:

$R_S = R_M = 100.4 \Omega$

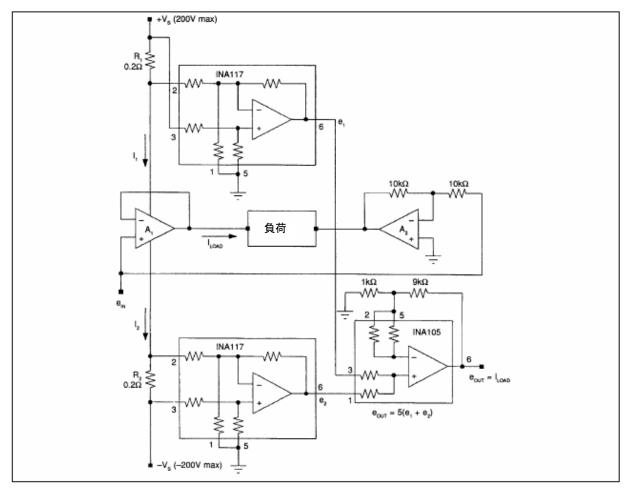

#### INA105 または INA117 を使用したパワー・アン プ負荷電流監視回路

INA117はINA105と同様の差動アンプですが、±200V同相電圧入力範囲を可能にする20/1入力分圧回路を持つ点が異なります。 また内部ゲイン20を持ち、全体のゲインは1となっています。短所は、アンプのDC誤差、および抵抗とアンプのノイズが20だけ増幅されることです。それでも、ガルバニック絶縁を必ずしも必要としない200Vのアプリケーションの場合ならば、INA117のパフォーマンスは絶縁アンプよりも良好であり、絶縁電源を使用する必要もありません。

図56は、ブリッジ・アンプのアプリケーションでINA117を使用して負荷電流を測定するための回路です。低い周波数の場合は、センス抵抗を負荷に直列に挿入することができ、計装アンプで負荷電流を直接監視できます。ただし、周波数が高い場合や過渡状態の場合は、CMRの誤差により確度が制限されます。このアプローチでは、アンプの電源電流の測定値から負荷電流を探り出すことにより、この問題を解消しています。

ブリッジ・オペアンプの電源電流は、INA117と電源に接続されたセンス抵抗 $0.2\,\Omega$ を使用して測定されます。  $0.2\,\Omega$ センス抵抗により、INA117の $380\mathrm{k}\,\Omega$  入力抵抗に付加される抵抗誤差は無視できる程度であるため、マッチング抵抗を付加する必要はありません。

図 56. INA117を使用した、ブリッジ・アンプ負荷電流監視回路

回路がどのように動作するかを理解するには、A<sub>1</sub>の入力に は電流が流れ込まないため、次のようになることに注目し てください。

$$\begin{split} \mathbf{I}_{\text{LOAD}} &= \mathbf{I}_1 - \mathbf{I}_2 \\ \mathbf{If} \\ \mathbf{R}_1 &= \mathbf{R}_2 = \mathbf{R} \\ \mathbf{Then} \\ \mathbf{e}_1 &= \mathbf{I}_1 \bullet \mathbf{R}, \\ \mathbf{e}_2 &= -\mathbf{I}_2 \bullet \mathbf{R}, \\ \mathbf{and} \\ \mathbf{e}_1 &+ \mathbf{e}_2 = \mathbf{I}_{\text{LOAD}} \bullet \mathbf{R} \end{split}$$

INA105は、ゲイン5を持つ非反転加算アンプとして接続さ れます。(2つの入力抵抗25k $\Omega$ の正確なマッチングによ り、非常に精度の高い加算アンプが実現されます) 次に、以下のようになります。

$$e_0 = 5(e_1 + e_2) = 5(I_{LOAD} \cdot R),$$

これは、次のことによります。

$$R = 0.2\Omega,$$

$$e_{O} = I_{LOAD} [1V/A]$$

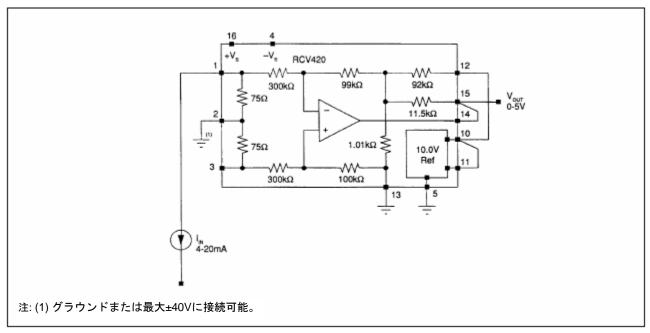

#### RCV420 を使用した、0~5V 出力のある 4 ~ 20mA 電流ループ・レシーバ回路

RCV420は、入力電流4~20mAを出力0~5Vに変換するた めに特に設計された電流・電圧変換回路です。内蔵された 高精度センス抵抗 $75\,\Omega$  のペアにより、反転および非反転 伝達関数の両方が使用可能になります。内部に4/1入力減衰 回路があるため、最大±40Vの入力同相電圧信号に対応可能 です。また、設計者の選択により、スパン・オフセットに 使用される高精度10.0V基準電圧も使用可能です。

図57は標準的なアプリケーションです。詳細および別のア プリケーション例を見る場合は、製品データ・シート PDS-837をお求めください。

#### 仮想グラウンド電流 - 電圧変換回路

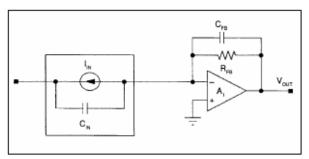

電圧の荷重のない電流 - 電圧変換を行う必要がある場合 は、図58~61のトランスインピーダンス・アンプを使用し ます。この回路では、帰還抵抗RFBを通してIIN と等価の電 流を印加することにより、オペアンプが電流入力ノードを 仮想グラウンドへ駆動します。次に示すように、伝達関数 が反転されていることに注意してください。

$$V_{OUT} = -I_{IN} \cdot R_{FB}$$

29

図 57. RCV420を使用した、4-20mA 電流ループレシーバ回路

図 58. 仮想グラウンド電流 - 電圧変換回路

回路の安定性のために、帰還コンデンサ $C_{FB}$ が必要になることもあります。その理由を理解するには、図58を描き直したものである図59の回路について考察してください。 $C_{IN}$ は回路の入力キャパシタンスです。これには、入力ソース・キャパシタンスとオペアンプ入力のキャパシタンスも含まれています。 $R_{FB}$ と $C_{IN}$ が、オペアンプ入力への帰還パスに単極フィルタを形成していることに注目してください。この回路全体の位相遅延により、オペアンプから位相余裕が差し引かれるため、不安定さが生じる可能性もあります。これらの回路でよく使用される大きな値の $R_{FB}$ は、特に不安定になりやすくなります。 $C_{FB} \geq 3$   $C_{IN}$ であれば、位相遅延は20°より小さくなるため、ユニティゲイン・アンプの大多数で安定性が保証されます。

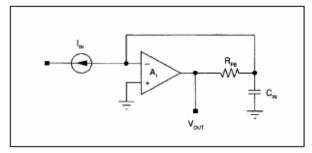

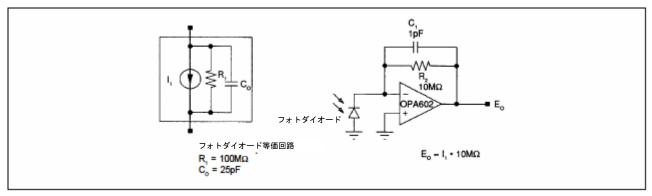

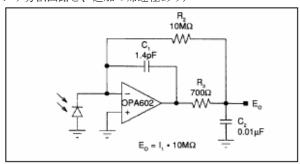

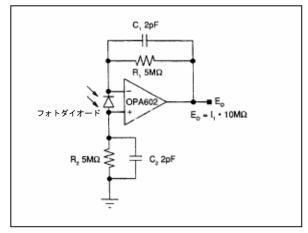

#### 仮想グラウンド I/V 変換回路を使用したフォトダ イオード・アンプ

図60のフォトダイオード・アンプは、よく見られるトランスインピーダンス(電流・電圧)アンプのアプリケーション

図 59. 仮想グラウンド電流 - 電圧変換回路 (入力容量と帰還抵抗が原因の位相遅延を図解するために描き直したもの

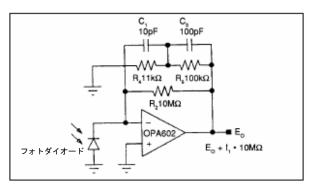

例です。このアプリケーションでは、フォトダイオードの並列容量成分と、比較的大きな値の帰還抵抗との組み合わせにより過剰なノイズ・ゲインが発生します。帰還コンデンサ1pFを使用すると、前述のようにピーキングが最小限に抑えられ、安定性が向上します。必要とされることの多い小さな値のコンデンサは入手が難しい場合もあります。図60Aのコンデンサ分割回路を使用すれば、より大きな値のコンデンサを使用することもできます。この例では10/1分割回路 $R_4$ 、 $R_5$ により、10pFコンデンサ $C_1$ が1pFという有効値に低減されています。100pFコンデンサ $C_3$ では、分割回路(divider)のインピーダンスを $C_1$ ,  $R_4$  ||  $R_5$  ゼロよりも低くして、 $C_1$ の効果を維持しています。また、 $C_1/10$ 、 $R_2$  極りも1ディケード近く離れた2次(40dB/ディケード)ロールオフを生成します。

図 60. 標準的なトランスインピーダンス・フォトダイオード・アンプ.

図 60A. 標準的なトランスインピーダンス・アンプ(コンデンサ分割回路と、追加の帰還極あり)

図 61.トランスインピーダンス・フォトダイオード・アン プを改良したもの

図61のように、標準的な構成に2つの受動素子を追加することにより、ノイズを大幅に低減する2次極が導入されます。この修正には、別の長所もあります。

改良後の回路に追加された極は、 $R_3$  と $C_2$ からなります。極は帰還ループ内に置かれるため、アンプでは低出力インピーダンスが保持されます。極を帰還ループの外に置く場合は、バッファをひとつ追加する必要があります。バッファがひとつ増えると、ノイズとDC誤差も付加されることになります。

次に示すように、両方の回路の信号帯域幅は16kHzです。

$$\mathbf{f}_{-3d\mathbf{B}} = \frac{1}{2 \cdot \pi \cdot \mathbf{R}_2 \cdot \mathbf{C}_1}$$

[Hz]  $\rightarrow$  標準回路

$$\mathbf{f}_{-3d\mathbf{B}} = \frac{1}{2 \cdot \pi \cdot (\mathbf{R}_2 \cdot \mathbf{C}_1 \cdot \mathbf{R}_3 \cdot \mathbf{C}_2)^{1/2}}$$

[Hz]  $\rightarrow$  改良後の回路

ここで、改良後の回路では

$$C_1 \cdot R_2 = 2(C_2 \cdot R_3)$$

and  $R_2 >> R_3$

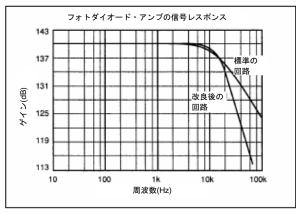

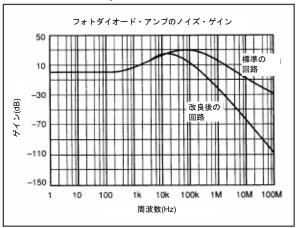

標準的な回路では、帰還ループ内のキャパシタンス1pFによって単一の16kHz極が形成されます。改良後の回路では、2極応答を示します。 $C_1 \cdot R_2 = 2 \cdot C_2 \cdot R_3$ の場合は、伝達関数は2次バタワース型(通過帯域の大部分が平坦)になります。図62は、2つの回路のトランスインピーダンス周波数レスポンスです。直流(DC)でのゲインは140dB、つまり10V/ $\mu$ Aです。どちらの回路でも、周波数応答が16kHzで3dB低下しています。従来の回路では20dB/ディケードでロールオフしますが、改良後の回路では40dB/ディケードでロールオフします。

図 62. 標準的/改良後のフォトダイオード ・アンプのトランスインピーダンス信号応答

図63は、両方の回路のノイズ・ゲインです。ノイズの問題は、比較的高い値のフォトダイオードの並列容量 $C_0$ が高い値の帰還抵抗 $10M\Omega$ と反応して形成されるノイズ・ゲイ

ン・ゼロが原因で起こります。 ノイズ・ゼロは次の場合に起こります。

$$\mathbf{f}_{\mathrm{Z}} = \frac{(\mathbf{R}_{1} + \mathbf{R}_{3})}{2 \cdot \pi \cdot \mathbf{R}_{1} \cdot \mathbf{R}_{3} \cdot (\mathbf{C}_{0} + \mathbf{C}_{1})}$$

~673Hz (この例では)

どちらの曲線も、フォトダイオードの並列容量により形成されたゼロが原因の、約673Hzでのノイズ・ゲインのピーキングを示しています。改良された回路の追加極では、それより低い周波数でノイズ・ゲインをロールオフさせ、20kHzより上のノイズを低減します。信号帯域幅が16kHzであるため、20kHzより上のスペクトルの領域にはノイズのみが含まれ、信号はありません。示されている値を使用すれば、改良後の回路のノイズは3分の1になります。OPA602(電圧ノイズ =  $12nV/\sqrt{Hz}$ )を使用した場合、抵抗ノイズも含めると、改良後の回路の $1Hz\sim100MHz$ 範囲のノイズは $68~\mu$  Vrmsになります。これに対して、標準的な回路のノイズは $205~\mu$  Vrmsです。

図 **63**. 標準的/改良後のフォトダイオード ・アンプのノイズ ゲイン

改良後の回路のもうひとつの長所は、容量負荷を駆動する能力です。回路の出力は大容量コンデンサ $C_2$ に接続されているため、追加の小さなキャパシタンスを駆動しても、安定性には何の問題もありません。この回路のDCインピーダンスは低くいですが、AC伝達関数は負荷の影響を受けます。負荷が適当であれば、影響は最小限ですみます。示された値を使用すれば、100pFと並列の負荷10k  $\Omega$  が回路のレスポンスに影響することはほとんどありません。

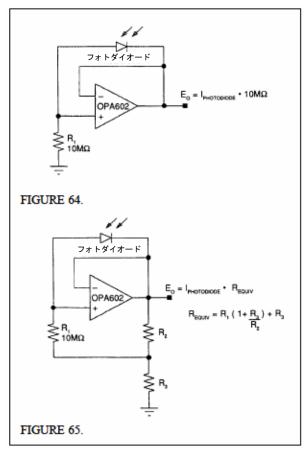

フォトダイオードがフローティング状態になる可能性のあるアプリケーションについては、図64と図65に示された非反転 I/V変換回路の使用を考慮してください。従来のトランスインピーダンス・アンプの構成と同様に、バッファ・アンプにより、フォトダイオードに0ボルトが印加されることに注意してください。

FET入力アンプは、入力バイアス電流が低いため、フォトダイオード・アンプのアプリケーションによく使用されます。

ただし、FETアンプのバイアス電流は高温になると劇的に増加します( $8\sim10^{\circ}$ C上がるごとに倍増)。つまり、 $25^{\circ}$ Cの時に入力バイアス電流が小さいように見えたとしても、高温になれば許容範囲を超えるおそれがあります。例えばあるアンプで、 $25^{\circ}$ Cでのバイアス電流がわずか1pAだったとしても、 $125^{\circ}$ Cでのバイアス電流は6nA近くになるかもしれません。

入力バイアス電流間の差異であるオフセット電流は、絶対バイアス電流よりも良いことが多くなっています。例えば、OPA156の標準的なバイアス電流は30pAですが、そのオフセット電流は3pAです。

アンプのバイアス電流が問題になる場合は、図66の回路の使用を検討してください。バイアス電流キャンセル抵抗 $R_2$ を付加すると、オペアンプ入力のバイアス電流間のマッチング効果が打ち消されます。これにより、10対1またはそれ以上の比率でパフォーマンスが向上します。電圧オフセットの原因は5M  $\Omega$  と反応する $I_{OS}$  (オフセット電流)のみであるためです。

最後に、ひとつ注意していただきたいことがあります。多くのアンプ、特にバイポーラ入力アンプでは、内部バイアス電流キャンセル回路を使用することで低バイアス電流を実現しています。その $I_B$  と $I_{OS}$  の違いはほとんどないか、全く存在しないこともあります。このような場合、外部バイアス電流をキャンセルしてもパフォーマンスは向上しません。

図 64および65.フローティング仮想グラウンド電流・電圧変換回路を使用したフォトダイオード・アンプ

図 66. バイアス電流打ち消しを可能にする差動式フォトダイオード・トランスインピーダンス・アンプ

#### 用語集

#### 略語と定義

**双方向電流ソース回路** --印加された電圧バイアスの極性とは無関係に、一定の電流を提供するフローティング電流 ソース回路。

**電流ソース回路** ・・あらゆる電流ソース回路、電流シンク回路、あるいはフローティング電流ソース回路の総称。ただしこのアプリケーション・レポートでは、電源の+Vs等の正の固定電位を基準に取る電流生成デバイスを指すことが多い。負荷は、電流ソース回路と、それより負の側に大きい値の電位の間に接続する必要がある。

**電流シンク回路** - 電源の-V<sub>s</sub>等の負の固定電位を基準に取る電流生成デバイス。負荷は、電流シンク回路と、それより正の側に大きい電位の間に接続する必要がある。

Difet® --、逆バイアス接合(JI)の代わりに誘電体(DI)を使用してデバイスを絶縁したBurr-Brownの集積回路プロセスの商標。この技法により、JIプロセスに特有の基板漏れ電流が解消される。その結果、FET入力アンプの入力バイアス電流が低下し、より高温下での動作と耐放射性が実現可能になる。

フローティング電流ソース回路 - 両端がグラウンドから独立してフローティング状態になった電流生成デバイス。負荷をどちらかの端に接続することも、また2つの負荷の間に浮遊電流ソース回路を接続することもできる。フローティング電流ソース回路は、REF200の電流ソース回路として使用されている。フローティング電流ソース回路では、外部電源が必要になることもある。REF200のフローティング電流ソース回路は電源内蔵タイプであるため、外部電源は必要としない。

IA - 計装アンプ。IAはオペアンプとは別物である。オペアンプとは異なり、IAでは入力のところで、固定ゲインにより信号を増幅するが、同相電圧信号は除去する。オペアンプでは入力のところで、(理想的には無限大の)開ループ・ゲインにより信号を増幅する。したがって、オペアンプを有用な増幅器として動作させるには、帰還部品を使用する必要がある。通常、ひとつのIAを構成するにはオペアンプが3つ、高精度抵抗が7つ必要になる。

**L**<sub>B</sub> ·· バイアス電流。アンプの入力端子に流れ込んだり、入力端子から流れ出たりする直流電流。

IC -- 集積回路。シングルチップの電子回路である「モノリシック集積回路」を指すことが多い。

$oldsymbol{I_{OS}}$  -- オフセット電流。ひとつのアンプにある $oldsymbol{2}$ つの入力の、 $oldsymbol{I_B}$ 間の差。

**オペアンプ** - 演算増幅器。オペアンプは、ゲインの非常に高い、差動入力方式の直流アンプである。伝達関数が外部帰還部品によって決まるアプリケーションでの使用が意図されている。

RTD(**測温抵抗体**) … 抵抗性温度デバイス。高精度温度トランスデューサであり、アクティブ・エレメントとしてプラチナが使用されている。0°Cで100 $\Omega$ 、500 $\Omega$ 、1000 $\Omega$ という値が標準的である。プラチナが高価であるため、1k $\Omega$ のRTDの方が一般的になりつつある。

TCR – 抵抗温度係数。抵抗の温度変化に伴う、直流抵抗値の変化。通常、"parts per million per °C [ppm/°C]"という単位で表される。

**TCRトラッキング** -- 2つ以上の抵抗のTCRの温度についてのマッチングあるいはトラッキング。

**トランスコンダクタンス増幅回路 --** 電圧 - 電流変換回路のこと。

**トランスインピーダンス増幅回路** -- 電流 - 電圧変換回路のこと。(トランスアドミッタンス回路とも呼ばれる)

### ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上