# Point-to-Point Serial Communications Using the SPI Module of the TMS320F240 DSP Controller

APPLICATION REPORT: SPRA451

Authors: Jeff Crankshaw Jeff Stafford

Digital Signal Processing Solutions May 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### CONTACT INFORMATION

| US TMS320 HOTLIN | JE (281) 274-2320 |

|------------------|-------------------|

| US TMS320 FAX    | (281) 274-2324    |

| US TMS320 BBS    | (281) 274-2323    |

| US TMS320 email  | dsph@ti.com       |

| Product Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| World Wide Web       8         Email       8         Introduction       9         SPI Overview       10         Internal Interface between the SPI Module and 'C2xx CPU       12         System Clock       12         SPI Register Accesses       13         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt Conditions       17         SPI Interrupt Conditions       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         Interface Topologies       22         Specific Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       28         Implementation       30         Software Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46     <           |

| Email                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Introduction       9         SPI Overview       10         Internal Interface between the SPI Module and 'C2xx CPU.       12         System Clock       12         SPI Register Accesses       13         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Priority Bit       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       28         Implementation       30         Hardware Description       30         Software Description       31         'F240 Slave Code       31         'F240 Slave Code       31         'F240 Slave Code       31         'F240 Slave Code       31     <           |

| SPI Overview       10         Internal Interface between the SPI Module and 'C2xx CPU.       12         System Clock       12         SPI Register Accesses       13         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Slave Code       31         'F240 Master Test Code       46         Running the Programs |

| SPI Overview       10         Internal Interface between the SPI Module and 'C2xx CPU.       12         System Clock       12         SPI Register Accesses       13         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Slave Code       31         'F240 Master Test Code       46         Running the Programs |

| Internal Interface between the SPI Module and 'C2xx CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| System Clock       12         SPI Register Accesses       13         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt Conditions       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together.       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Slave Code       31         'F240 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                      |

| SPI Register Accesses       13         SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt Conditions       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Slave Code       31         'F240 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                              |

| SPI Interrupt       16         TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt Conditions       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Software Description       31         'F240 Slave Code       31         'F240 Slave Code       44         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                            |

| TMS320x240 Interrupt Architecture Overview       16         SPI Interrupt Conditions       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Software Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                                                     |

| SPI Interrupt Conditions       17         SPI Priority Bit       17         Transmit/Receive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                                                                                                                 |

| SPI Priority Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Transmit/Řeceive Interrupt       18         Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together.       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                                                                                                                                                                                            |

| Receiver Overrun Interrupt       18         Reading the Interrupt Vector       19         Putting It All Together.       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                                                                                                                                                                                                                                        |

| Reading the Interrupt Vector       19         Putting It All Together       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                                                                                                                                                                                                                                                                                     |

| Putting It All Together.       20         Interrupt Initialization       20         General Interrupt Service Routine (GISR)       22         Specific Interrupt Service Routine (SISR)       23         Interface Topologies       25         Point-to-Point       25         Addressed Multi-Node       26         Chip-Enabled Multi-Node       28         Implementation       30         Hardware Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167       52                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupt Initialization20General Interrupt Service Routine (GISR)22Specific Interrupt Service Routine (SISR)23Interface Topologies25Point-to-Point25Addressed Multi-Node26Chip-Enabled Multi-Node28Implementation30Hardware Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 EVMs51Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| General Interrupt Service Routine (GISR)22Specific Interrupt Service Routine (SISR)23Interface Topologies25Point-to-Point25Addressed Multi-Node26Chip-Enabled Multi-Node28Implementation30Hardware Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 EVMs51Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Specific Interrupt Service Routine (SISR)23Interface Topologies25Point-to-Point25Addressed Multi-Node26Chip-Enabled Multi-Node28Implementation30Hardware Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 EVMs51Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interface Topologies25Point-to-Point25Addressed Multi-Node26Chip-Enabled Multi-Node28Implementation30Hardware Description30Software Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 EVMs51Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Point-to-Point25Addressed Multi-Node26Chip-Enabled Multi-Node28Implementation30Hardware Description30Software Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 EVMs51Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Addressed Multi-Node26Chip-Enabled Multi-Node28Implementation30Hardware Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 and 'C167 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chip-Enabled Multi-Node28Implementation30Hardware Description30Software Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 EVMs51Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Implementation30Hardware Description30Software Description31'F240 Slave Code31'F240 Master Test Code43'C167 Master Test Code46Running the Programs50Implementing Point-to-Point Communication between Two 'F240 EVMs51Implementing Point-to-Point Communication between the 'F240 and 'C167 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Hardware Description       30         Software Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Software Description       31         'F240 Slave Code       31         'F240 Master Test Code       43         'C167 Master Test Code       46         Running the Programs       50         Implementing Point-to-Point Communication between Two 'F240 EVMs       51         Implementing Point-to-Point Communication between the 'F240 and 'C167 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

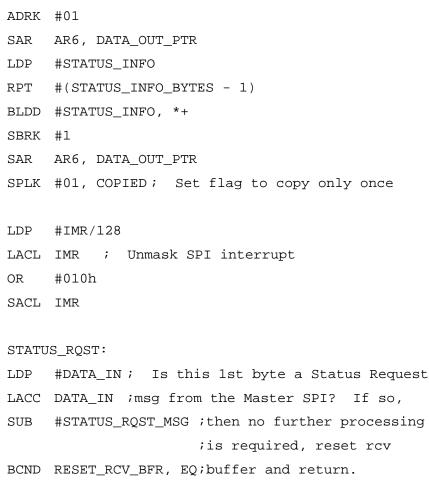

| <ul> <li>'F240 Slave Code</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>'F240 Master Test Code</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C167 Master Test Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Running the Programs50<br>Implementing Point-to-Point Communication between Two 'F240 EVMs51<br>Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Implementing Point-to-Point Communication between Two 'F240 EVMs51<br>Implementing Point-to-Point Communication between the 'F240 and 'C16752                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Implementing Point-to-Point Communication between the 'F240 and 'C167 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ADDEIIUIX A. TAQ JUIIIIIAIV VI JETTEALUIEJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix B. 'C167 Master Mode Program Files56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPI.C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SPI.H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SYS INIT.C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix C. 'F240 Master Mode Program Files63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example 'C2xx Debugger Command Line Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Emulator Initialization Command File -'F240evm.cmd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SPI.ASM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPI.CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# Contents

| SPI1.TAK                                   | 74 |

|--------------------------------------------|----|

| F240REGS.H                                 | 76 |

| Appendix D. 'F240 Slave Mode Program Files |    |

| SPI.ASM                                    |    |

| SPI1.TAK                                   | 91 |

# Figures

|            | 5                                                                            |      |

|------------|------------------------------------------------------------------------------|------|

| Figure 1.  | SPI Block Diagram                                                            | . 10 |

| Figure 2.  | Representation of Relationship between the CPUCLK and the SYSCLK for         |      |

| C          | (a) Divide-by-2 Mode and (b) Divide-by-4 Mode                                | .14  |

| Figure 3.  | SPI Interrupt Priority within 'F240 Interrupt Hierarchy                      | .16  |

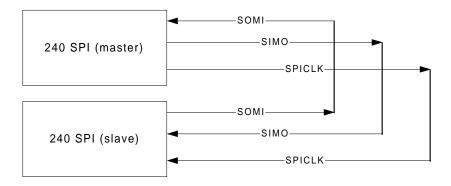

| Figure 4.  | High-Level Block Diagram of Point-to-Point Topology                          | .25  |

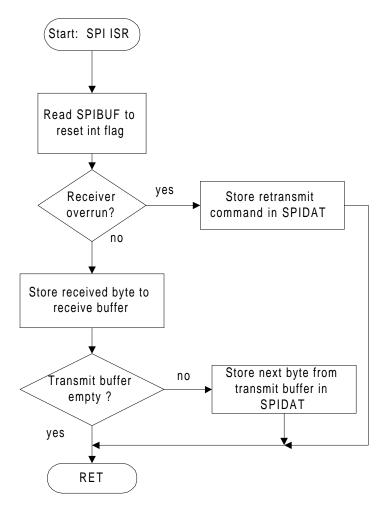

| Figure 5.  | Flow Chart for Point-to-Point Topology                                       | .26  |

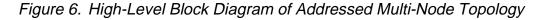

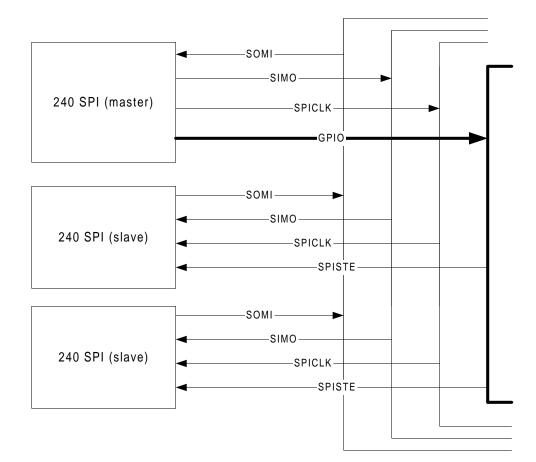

| Figure 6.  | High-Level Block Diagram of Addressed Multi-Node Topology                    | .27  |

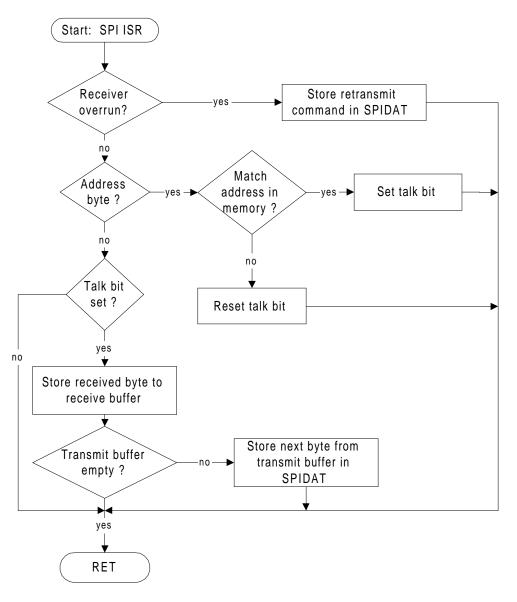

| Figure 7.  | Flow Chart for Addressed Multi-Node Topology                                 | .28  |

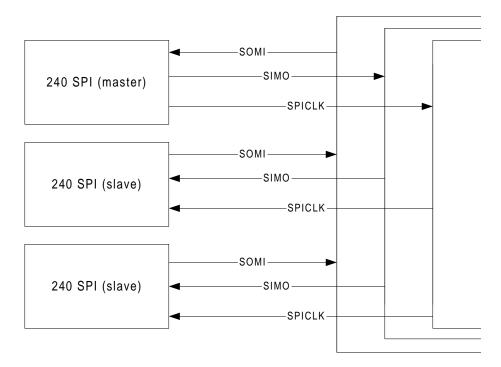

| Figure 8.  | High-Level Block Diagram of Chip-Enabled Multi-Node Topology                 | . 29 |

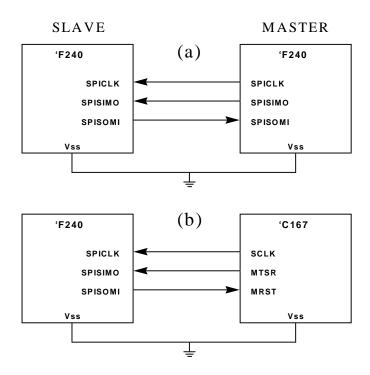

| Figure 9.  | High-Level Block Diagram of Point-to-Point Interconnections for (a) 'F240 to |      |

|            | 'F240 and (b) 'C167 to 'F240                                                 | .30  |

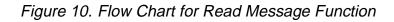

| Figure 10. | Flow Chart for Read Message Function                                         | .40  |

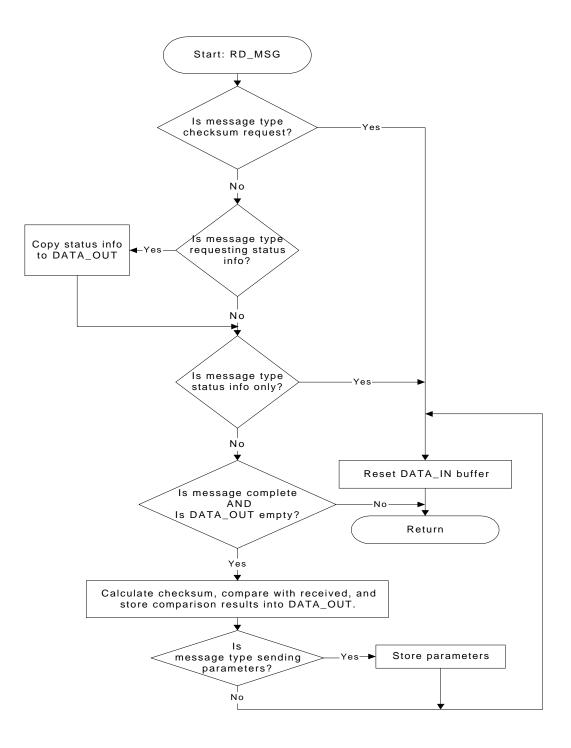

| Figure 11. | 'C167 Master Event Time Line for Three Message Sequence                      | . 47 |

| Figure 12. | Memory Image of 'F240 Master after Successful Program Run                    | .51  |

| Figure 13. | Memory Image of 'F240 Slave after Successful Program Run                     | .53  |

# Tables

| Table 1. | SPI Control Register Memory Map                                   | 11 |

|----------|-------------------------------------------------------------------|----|

|          | Instruction Word and Cycle Counts for Peripheral Accesses         |    |

| Table 3. | SPI Interrupt Configuration and Status Bits                       | 17 |

| Table 4. | Interrupt Level 1 (INT1) Interrupt Sources and Overall Priorities | 19 |

| Table 5. | Interrupt Level 5 (INT5) Interrupt Sources and Overall Priorities | 20 |

| Table 6. | 'F240 EVM to 'F240 EVM Board Connections                          | 31 |

| Table 7. | 'F240 EVM to MCB-167 Board Connections                            | 31 |

| Table 8. | Master Mode SPI Register Initialization Sequence for Falling Edge |    |

| Table 9. | Expected Results for All Three Message Types                      | 52 |

|          |                                                                   |    |

# Point-to-Point Serial Communications Using the SPI Module of the TMS320F240 DSP Controller

# Abstract

This application report discusses serial communications using the Serial Peripheral Interface (SPI) synchronous serial port of the Texas Instruments (TI<sup>™</sup>) TMS320F240 digital signal processor (DSP) controller. A general description of SPI features is provided for necessary background information. The CPU/SPI interface description includes a discussion of the bus interface and interrupt architecture.

An overview of inter-processor communication topologies describes how the SPI module is used in several applications. A hardware implementation example of a point-to-point communication scheme uses the 'F240 SPI in slave mode connected to a Seimens 'C167 SSC configured as the SPI master.

All 'F240 code is generated using TI assembly language tools and validated on the 'F240 EVM hardware. All 'C167 code is generated using the Keil demonstration tools and validated on the Keil MCB-167 evaluation board. Source code for both processors, as well as the necessary header, build, and link files, and tools options are provided as appendices so that the reader can modify this solution to suit a specific need.

# **Product Support**

## **Related Documentation**

The following list specifies product names, part numbers, and literature numbers of corresponding TI documentation.

- TMS320C24x DSP Controllers CPU, System, and Instruction Set Reference Set, Volume 1, September 1997, Literature number SPRU160B

- TMS320C24X DSP Controllers Peripheral Library and Specific Devices Reference Set, Volume 2, December 1997, Literature number SPRU161B

- XDS51x Emulator Installation Guide, January 1996, Literature number SPNU070A

### World Wide Web

Our World Wide Web site at **www.ti.com** contains the most up to date product information, revisions, and additions. Users registering with TI&ME can build custom information pages and receive new product updates automatically via email.

### Email

For technical issues or clarification on switching products, please send a detailed email to **dsph@ti.com**. Questions receive prompt attention and are usually answered within one business day.

# Introduction

The TI TMS320 family of DSP controllers is designed with special features to facilitate serial communications between multiple processors. In particular, the TMS320x240<sup>1</sup> DSP controller incorporates an SPI module specifically for this purpose. The external hardware and software overhead for inter-processor communication is reduced by the flexibility and programmability of this module.

The SPI is a high-speed synchronous serial I/O port that allows a serial bit stream of programmed length (one to eight bits) to be shifted into and out of the device at a programmable bit transfer rate. The SPI is normally used for communications between the DSP controller and external peripherals or another controller. Typical applications include external I/O or peripheral expansion via devices such as shift registers, display drivers, and analog-to-digital (A/D) converters. Multi-processor communications are supported by the master/slave operation of the SPI. The focus of this application report is the master/slave operation of the SPI, which supports multi-processor communication.

This application report is organized into two main parts.

- The first part consists of a general description of the 'F240 SPI, its interface with the 'C2xx DSP core, and an overview of different serial communication topologies enabled by the SPI.

- The second part describes the implementation of a point-topoint interface between the 'F240 and a Seimens 'C167. This section presents a detailed description of the hardware and software used to implement the communication scheme. All relevant source code and build options are provided in the appendices.

<sup>&</sup>lt;sup>1</sup> The "x" indicates either 'F" for flash EEPROM or "C" for masked ROM. For the purposes of this application report, 'F240 is used to represent both flash and ROM devices since the internal program memory type has no effect on the SPI.

### SPI Overview

This brief overview of the SPI describes key features with respect to the topic application of inter-processor communications. (A complete description of the SPI module is offered in Chapter 5, of the *TMS320C24X DSP Controllers Peripheral Library and Specific Devices Reference Set, Volume 2.*)

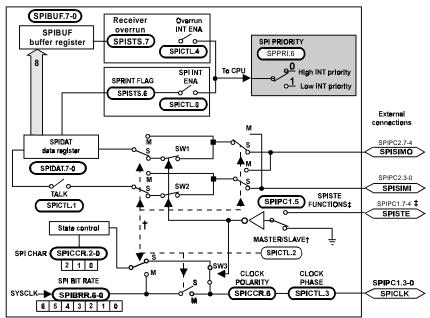

Figure 1 shows the key features of the SPI.

Figure 1. SPI Block Diagram

<sup>†</sup>The diagram is shown in slave mode.

‡The SPISTE pin is shown as being disabled, meaning the data can be transmitted or received in this mode. Note that switches SW1, SW2, and SW3 are closed in this configuration.

The SPI has four external pins, *SPISOMI, SPISTE, SPISIMO*, and *SPICLK*, providing the interface to external devices. The SPI is a full-duplex communication port, with the simultaneous transmit and receive taking place on the *SPISOMI* and *SPISIMO* pins. The SPICLK pin provides the time base for communications. This pin is bi-directional to allow the time base to be generated in master mode and received in slave mode.

The fourth pin, *SPISTE*, has the capability to act as the slave enable. This operation is conditional, based on the status of the SPISTE FUNCTION bit. When this bit is set and the *SPISTE* input is active low, the SPI sends and receives data from the master. When the *SPISTE* pin is inactive high, the SPI serial shift register is disabled and the *SPISOMI* output pin is placed in the high impedance state. However, when the SPISTE FUNCTION bit is cleared, the SPI receives all data and transmits data based on the status of the TALK bit.

The key features of the SPI are software programmable, which make it extremely flexible and capable of communicating with many types of serial ports. Some of the key programmable features are:

- Operation mode: master or slave

- Character length: 1-8 bits

- Interrupt priority: level 1 or 5

- Serial bit transfer clock rate

- Serial clock phase and polarity

All of the SPI features are controlled by the ten control registers, which are mapped into the internal data space of the 'F240. Table 1 summarizes these ten control registers, including their symbols and addresses.

| Table 1. | SPI Control | Register | Memory | Мар |

|----------|-------------|----------|--------|-----|

|----------|-------------|----------|--------|-----|

| ADDRESS     | SYMBOL | NAME                           |

|-------------|--------|--------------------------------|

| 7040h       | SPICCR | Configuration control register |

| 7041h       | SPICTL | Operation control register     |

| 7042h       | SPISTS | Status register                |

| 7043h       | _      | Reserved                       |

| 7044h       | SPIBRR | Baud rate register             |

| 7045h–7046h | —      | Reserved                       |

| 7047h       | SPIBUF | Serial input buffer register   |

| 7048h       | _      | Reserved                       |

| 7049h       | SPIDAT | Serial data register           |

| 704Ah–704Ch | _      | Reserved                       |

| 704Dh       | SPIPC1 | Port control register 1        |

| 704Eh       | SPIPC2 | Port control register 2        |

| 704Fh       | SPIPRI | Priority control register      |

# Internal Interface between the SPI Module and 'C2xx CPU

The TMS320x240 DSP controllers represent a new approach to peripheral integration for the TMS320 series. The flexible and easy-to-use peripherals found in the TMS370 family of MCUs have been integrated with the low cost 'C2xx DSP. This new approach differs from the other members in the 'C2xx family (such as the 'C203 and 'F206) in that the peripherals are located in data space and operate in a different clock domain based on the system clock.

To better understand the peripheral architecture of the TMS320x240, this section covers some of the basic interface characteristics that are important from a programming point of view. A solid understanding of the architecture helps the programmer to take advantage of this architecture.

Two factors concern the programmer:

- System clock speed

- Register reads/writes

The next two sections describe each factor and its relationship to application development.

#### System Clock

The first and most important factor to consider when beginning application development is system clock frequency selection. The SPI is clocked by the system clock, SYSCLK, which can be configured to run at either one half or one fourth the frequency of the 'C2xx CPU clock, CPUCLK. The actual SYSCLK pre-scale ratio is determined by the PLL pre-scale bit, PLLPS, in Clock Control Register 0, CKCR0, at address 0x702B in data space.

In most applications, it makes sense to configure SYSCLK to run at its highest frequency, which is one half the CPU clock frequency. This minimizes the number of clock cycles necessary to perform peripheral register accesses. A divide-by-2 ratio is accomplished by setting bit PLLPS to 1 during the initialization sequence following a power-on reset condition.

Once selected, the frequency of SYSCLK remains set to one half of CPUCLK until another power on reset condition occurs. Normal system resets do not affect the PLLPS bit. Example 1 shows a typical code sequence used to configure the clock control register.

#### Example 1. PLL initialization code

- \* Set Data Page pointer to page 1 of the peripheral frame LDP #DP\_PF1 ; Page DP\_PF1 includes WET through EINT frames

- \* Configure PLL for 10MHz osc, 10MHz SYSCLK and 20MHz CPUCLK

- SPLK #00B1h,CKCR1 ; CLKIN (OSC)=10MHz,CPUCLK=20MHz

```

SPLK #00C3h,CKCR0 ; CLKMD=PLL Enable, SYSCLK=CPUCLK/2,

```

#### **SPI Register Accesses**

It is necessary to understand which CPU instructions can be used to access the peripheral registers of the TMS320x240 in order to understand peripheral register accesses. All of the peripherals, including the SPI, are located in data space. Thus, any instruction that operates on data space can be used to access the SPI control registers.

For the 'C2xx CPU, the simplest form of a read is the 16-bit load accumulator instruction, or LACL. Likewise, the simplest form of a write is the 16-bit store accumulator instruction, or SACL. Both are single-cycle instructions when executed from zero wait-state program memory (e.g. internal Flash EEPROM) and the operand is located in zero wait-state data memory (e.g. on-chip Dual Access RAM). The SPI is interfaced to the CPU through the peripheral bus. This internal bus acts as a bridge between the CPU and SPI. To maintain high performance for complex algorithms, the CPU is clocked at a higher clock frequency. The SPI, which has been designed to minimize CPU loading, does not require the faster clock frequency. The peripheral bus acts as a "bridge" between these two clock domains.

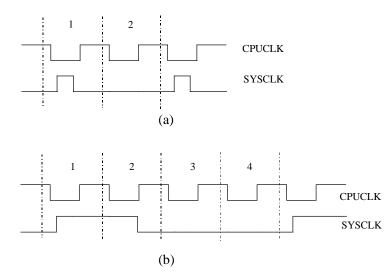

Accesses to the slower peripheral bus require the addition of wait states. There are two reasons for the wait states: first, the access has to be synchronized with the peripheral bus. At any given time, the CPUCLK could be in one of two ( $\div$ 2), or one of four ( $\div$ 4), phases with respect to the SYSCLK. Peripheral bus accesses will not begin until the SYSCLK is in the correct phase. This relationship is demonstrated in Figure 2.

Figure 2. Representation of Relationship between the CPUCLK and the SYSCLK for (a) Divide-by-2 Mode and (b) Divide-by-4 Mode

The second reason for wait states is the slower peripheral latency or access time. The SPI, and other eight-bit peripherals, require one SYSCLK period for reads and one and a half SYSCLK periods for writes. Thus, single writes to the peripheral bus require one more clock cycle than single reads.

Table 2. Instruction Word and Cycle Counts for Peripheral Accesses

|             |                                            |         | # Cy   | vcles  |

|-------------|--------------------------------------------|---------|--------|--------|

| Instruction |                                            | # Words | ÷2     | ÷4     |

| Reads       |                                            |         |        |        |

| LACL        |                                            | 1       | 3 or 4 | 5 - 8  |

| BIT         |                                            | 1       | 3 or 4 | 5 - 8  |

| Writes      |                                            |         |        |        |

| SACL        | 1 <sup>st</sup> access                     | 1       | 4 or 5 | 6 - 9  |

| SACL        | 2 <sup>nd</sup> or more consecutive access | 1       | 4      | 8      |

| SPLK        | 1 <sup>st</sup> access                     | 2       | 5 or 6 | 7 - 10 |

| SPLK        | 2 <sup>nd</sup> or more consecutive access | 2       | 6      | 8      |

The net effect of the wait states is shown in Table 2. The number of cycles for instructions commonly used to access the SPI registers are shown for both divide-by-2 and divide-by-4 SYSCLK settings. Based on these facts, the following general guidelines can be followed to minimize register access times:

15

□ Configure the SYSCLK for divide-by-2.

The reset state of the 'F240 sets the SYSCLK divide-by-ratio to 4. The default divide-by-4 mode ensures that the system peripherals would function correctly on power up. The divideby-ratio can be set to 2 during the initialization routines after reset to minimize the number of cycles required for register reads and writes.

Use direct addressing with immediate operand for SPI register initialization.

Since initialization is generally performed once and at least four registers need to be written to configure the SPI, it makes sense to modify the data page pointer and use the direct addressing mode. The store long constant (SPLK) instruction is recommended.

# **SPI Interrupt**

16

From an application point of view, one of the critical design decisions involves selection of the interrupt strategy. The 'F240 is designed to provide maximum flexibility in the use of interrupts. This section will describe the 'F240 interrupt architecture as it relates to the SPI. In addition, the programmable priority and receive-error detection capabilities of the SPI module are discussed. Finally, examples of interrupt initialization and service code are provided to illustrate these important features.

# TMS320x240 Interrupt Architecture Overview

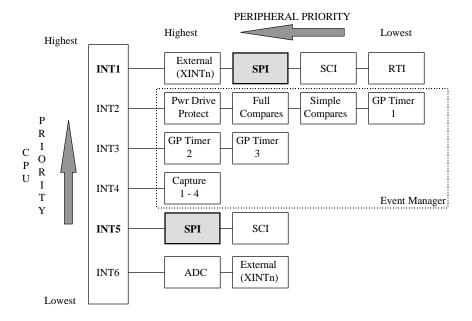

In order to select the correct SPI interrupt strategy for a given design, it is necessary to understand how the SPI interrupt fits into the overall interrupt architecture of the 'F240. An overview of the 'F240 interrupt hierarchy is presented in block diagram form in Figure 3. The DSP core provides six maskable interrupt levels, INT1 through INT6, with INT1 given highest priority and INT6 being the lowest. Since the 'F240 device has more than six maskable interrupts, each of the six interrupt levels are shared by multiple interrupt sources. These interrupt sources are generated from on-chip peripherals and external interrupt pins.

This grouping of peripheral interrupts makes it possible to isolate a particular peripheral to efficiently prioritize its use.

Figure 3. SPI Interrupt Priority within 'F240 Interrupt Hierarchy

17

# **SPI Interrupt Conditions**

The SPI can initiate an interrupt after the occurrence of either of two events. The first event is defined as occurring after a character has been transmitted or received. The second event is defined as occurring after a receiver overrun condition is encountered. Both of these conditions can be independently enabled and both share a common interrupt vector. Five control bits are used to configure and determine the status of SPI interrupts. Table 3 summarizes their register locations, names, and descriptions.

| Control<br>Register | Bit Name            | Bit<br>Type | Description                                                                                                                                                   |

|---------------------|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPIPRI.6            | spi<br>Priority     | Control     | Determines interrupt level of an SPI interrupt. When<br>set, SPI interrupts are sent on level 5. When cleared,<br>SPI interrupts are sent on level 1.         |

| SPICTL.0            | SPI INT<br>ENA      | Control     | Enables the SPI to request an interrupt when the last<br>bit in a transmit/receive operation has been<br>sent/received. When set, SPI interrupts are enabled. |

| SPISTS.6            | SPI INT<br>FLAG     | Status      | Indicates the SPI has transmitted/received the last bit in a transmit/receive operation.                                                                      |

| SPICTL.4            | OVERRUN<br>INT ENA  | Control     | Enables the SPI to request an interrupt when a<br>transmit/receive operation is completed before the<br>previous character has been read from the buffer.     |

| SPISTS.7            | RECEIVER<br>OVERRUN | Status      | Indicates the SPI has completed a transmit/receive<br>operation before the previous character has been<br>read from the buffer.                               |

Table 3. SPI Interrupt Configuration and Status Bits

# **SPI Priority Bit**

The first bit that must be configured is the SPI PRIORITY bit. This bit determines the interrupt level of the SPI interrupt request. If this bit is cleared to 0, the interrupt request is seen by the DSP core as a high priority and is received on interrupt level 1 (INT1). If this bit is set to 1, the interrupt request is seen by the DSP core as a low priority and is received on interrupt level 5 (INT5). This allows the designer to have software control over the priority of the SPI interrupt. For example, in some multi-processor applications, it may be desirable to send or receive large amounts of data at a high baud rate.

One common application is to use the SPI to receive flash programming code and data. Other on-chip resources, such as the Event Manager, would be inactive in such a case, and a high priority interrupt would be desirable. Then, after this initial burst of data has been transferred, the SPI interrupt priority can be lowered to allow other interrupts to take priority. This flexibility can be used in other situations where the SPI communications need to take high priority in particular situations, but then can be reduced to a background task with lower priority.

#### **Transmit/Receive Interrupt**

The main method to determine completion of an SPI transmit/receive operation is the SPI interrupt. Setting the SPI INT ENA bit enables this interrupt. This event is indicated by the SPI INT FLAG bit. Anytime the SPI completes sending or receiving, this bit is set and the SPI is ready to be serviced. This event causes an interrupt to be requested if the SPI interrupt is enabled.

The user must clear the SPI INT FLAG bit during the SPI interrupt service routine by reading the SPIBUF register. If this register is not read, the SPI INT FLAG remains set and no additional SPI TX/RX interrupts will be generated. This bit is also automatically cleared by writing a 1 to the SPI software reset (SPICCR.7) bit and by any device reset.

#### **Receiver Overrun Interrupt**

The SPI can be configured to detect a receiver overrun condition, which occurs anytime the previous character has not been read from the SPI buffer register before a new character is received. Setting the OVERRUN INT ENA bit to a 1 enables this error detection feature. The RECEIVER OVERRUN flag bit is set by the SPI hardware when a receive or transmit operation completes before the previous character has been read from the buffer. This flag indicates that the last received character has been overwritten and therefore lost. When the overrun interrupt is enabled, the SPI requests an interrupt each time this flag is set.

The RECEIVER OVERRUN flag bit must be cleared before another overrun interrupt will be generated by the SPI. It is up to the user to clear this bit, which is most easily done by writing a 0 to it in the SPI interrupt service routine. Other actions that clear the RECEIVER OVERRUN flag bit are an SPI software reset or a device reset, both of which require reconfiguration of the SPI control registers.

# **Reading the Interrupt Vector**

After an interrupt request leaves the SPI peripheral, it is sent to arbitration logic, which compares the priority level of competing interrupt requests and passes the highest priority interrupt request to the DSP core. The corresponding interrupt flag is set in the DSP core's interrupt flag register (IFR). If the corresponding bit in the interrupt mask register (IMR) is set and the INTM bit is 0, the DSP core will acknowledge the interrupt and branch to the interrupt service routine (ISR). The DSP core services any remaining interrupt requests in order of priority.

As described in Figure 3, the 'C2xx CPU has six interrupt levels, but there are multiple requests per level. The 'F240 implements a vector offset scheme to distinguish between the peripheral interrupt requests within each level. Table 4 and Table 5 summarize the peripherals, their interrupt vector offsets, and priorities for both SPI interrupt levels one and five.

Table 4. Interrupt Level 1 (INT1) Interrupt Sources and Overall Priorities

| Overall<br>Priority | Interrupt<br>Name | Vector<br>Offset | 'F240<br>Module  | Interrupt Function                      |

|---------------------|-------------------|------------------|------------------|-----------------------------------------|

| 4                   | XINT1             | 0001h            | System<br>Module | High-priority external user interrupt   |

| 5                   | XINT2             | 0011h            | System<br>Module | High-priority external user interrupt   |

| 6                   | XINT3             | 001Fh            | System<br>Module | High-priority external user interrupt   |

| 7                   | SPIINT            | 0005h            | SPI              | High-priority SPI interrupt             |

| 8                   | RXINT             | 0006h            | SCI              | High-priority SCI receiver interrupt    |

| 9                   | TXINT             | 0007h            | SCI              | High-priority SCI transmitter interrupt |

| 10                  | RTINT             | 0010h            | WDT              | Real-time interrupt                     |

The SPI shares interrupt level one with interrupts from three external pins (XINT1-3), the SCI receive and transmit interrupts, and the WDT real time interrupt. The level five interrupt is shared between the SPI and SCI modules.