## TPA3116D2, TPA3118D2, TPA3130D2

SLOS708G -APRIL 2012-REVISED DECEMBER 2017

# TPA3116D2 15-W, 30-W, 50-W Filter-Free Class-D Stereo Amplifier Family With AM **Avoidance**

#### **Features**

- Supports Multiple Output Configurations

- 2 x 50 W Into a 4- $\Omega$  BTL Load at 21 V (TPA3116D2)

- 2 x 30 W Into a 8- $\Omega$  BTL Load at 24 V (TPA3118D2)

- 2 x 15 W Into a 8- $\Omega$  BTL Load at 15 V (TPA3130D2)

- Wide Voltage Range: 4.5 V to 26 V

- Efficient Class-D Operation

- >90% Power Efficiency Combined With Low Idle Loss Greatly Reduces Heat Sink Size

- Advanced Modulation Schemes

- Multiple Switching Frequencies

- AM Avoidance

- Master and Slave Synchronization

- Up to 1.2-MHz Switching Frequency

- Feedback Power-Stage Architecture With High PSRR Reduces PSU Requirements

- **Programmable Power Limit**

- Differential and Single-Ended Inputs

- Stereo and Mono Mode With Single-Filter Mono Configuration

- Single Power Supply Reduces Component Count

- Integrated Self-Protection Circuits Including Overvoltage, Undervoltage, Overtemperature, DC-Detect, and Short Circuit With Error Reporting

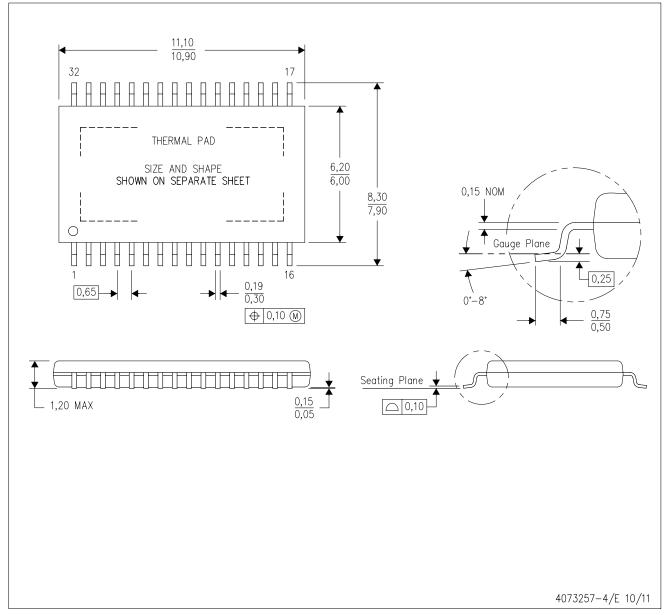

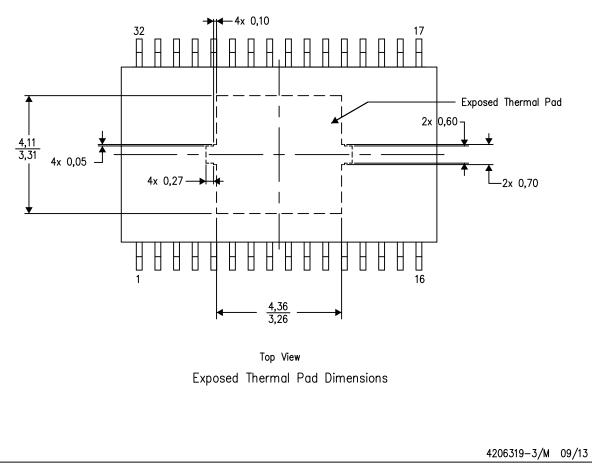

- Thermally Enhanced Packages

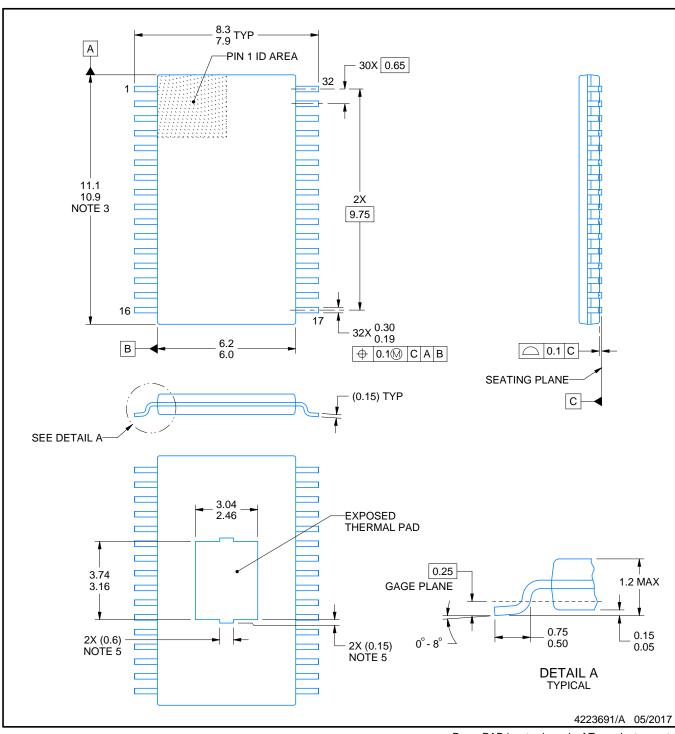

- DAD (32-Pin HTSSOP Pad Up)

- DAP (32-Pin HTSSOP Pad Down)

- -40°C to 85°C Ambient Temperature Range

## Applications

- Mini-Micro Component, Speaker Bar, Docks

- After-Market Automotive

- **CRT TV**

- **Consumer Audio Applications**

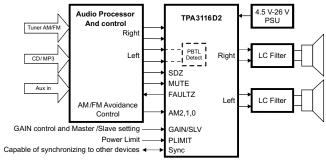

## 3 Description

The TPA31xxD2 series are stereo efficient, digital amplifier power stage for driving speakers up to 100 W / 2  $\Omega$  in mono. The high efficiency of the TPA3130D2 allows it to do 2 x 15 W without external heat sink on a single layer PCB. The TPA3118D2 can even run 2 x 30 W / 8  $\Omega$  without heat sink on a dual layer PCB. If even higher power is needed the TPA3116D2 does 2  $\times$  50 W / 4  $\Omega$  with a small heatsink attached to its top side PowerPAD. All three devices share the same footprint enabling a single PCB to be used across different power levels.

The TPA31xxD2 advanced oscillator/PLL circuit employs a multiple switching frequency option to avoid AM interferences; this is achieved together with an option of either master or slave option, making it possible to synchronize multiple devices.

The TPA31xxD2 devices are fully protected against faults with short-circuit protection and thermal protection as well as overvoltage, undervoltage, and DC protection. Faults are reported back to the processor to prevent devices from being damaged during overload conditions.

## Device Information<sup>(1)</sup>

| PART NUMBER            | PACKAGE  | BODY SIZE (NOM)    |

|------------------------|----------|--------------------|

| TPA3116D2              | DAD (32) | 11.00 mm × 6.20 mm |

| TPA3118D2<br>TPA3130D2 | DAP (32) | 11.00 mm × 6.20 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

## **Simplified Application Circuit**

Copyright © 2016, Texas Instruments Incorporated

2

Features ...... 1

Applications ...... 1

7.4 Device Functional Modes.......24

Application and Implementation ...... 25

| T: | aŀ | ٦la | 9 ( | ٦ſ | F ( | $\Box$ | n | n | t | ar | ١ts |

|----|----|-----|-----|----|-----|--------|---|---|---|----|-----|

|    | αк | ,,, |     | _  |     | _      | _ |   | Ľ | _  |     |

|    | 3 Des          | scription                                                                          |                                  |                 | 6.1 Application information                                                                                                |         |

|----|----------------|------------------------------------------------------------------------------------|----------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|---------|

|    |                | vision History                                                                     |                                  |                 | 8.2 Typical Application                                                                                                    |         |

|    |                | Configuration and Functions                                                        |                                  | 9               | Power Supply Recommendations                                                                                               | 28      |

|    |                | ecifications                                                                       |                                  | 10              | Layout                                                                                                                     | 28      |

|    | 6.1            |                                                                                    |                                  |                 | 10.1 Layout Guidelines                                                                                                     | 28      |

|    | 6.2            |                                                                                    |                                  |                 | 10.2 Layout Example                                                                                                        | 29      |

|    | 6.3            |                                                                                    |                                  |                 | 10.3 Heat Sink Used on the EVM                                                                                             | 31      |

|    | 6.4            |                                                                                    |                                  | 11              | Device and Documentation Support                                                                                           | 32      |

|    | 6.5            | DC Electrical Characteristics                                                      | 6                                |                 | 11.1 Related Links                                                                                                         | 32      |

|    | 6.6            | AC Electrical Characteristics                                                      | <del>7</del>                     |                 | 11.2 Receiving Notification of Documentation Upd                                                                           | ates 32 |

|    | 6.7            | Typical Characteristics                                                            | 8                                |                 | 11.3 Community Resources                                                                                                   | 32      |

|    | 7 Det          | tailed Description                                                                 | 13                               |                 | 11.4 Trademarks                                                                                                            |         |

|    | 7.1            | Overview                                                                           | 13                               |                 | 11.5 Electrostatic Discharge Caution                                                                                       |         |

|    | 7.2            | Functional Block Diagram                                                           | 13                               |                 | 11.6 Glossary                                                                                                              | 32      |

|    | 7.3            | Feature Description                                                                | 13                               | 12              | 3, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4,                                                                                  |         |

|    |                |                                                                                    |                                  |                 | Information                                                                                                                | 32      |

| •  | Chang          |                                                                                    | t" To: "Open" i                  |                 | 3e 3                                                                                                                       |         |

| Ch |                | from Revision E (September 2015) to                                                |                                  |                 |                                                                                                                            | Page    |

| •  | _              |                                                                                    |                                  |                 | ic cap to OUTNL in the Pin Functions table                                                                                 |         |

| •  | Chang          | jed pin 24 Description From: ceramic cap                                           | to OUTNL To                      | o: ceran        | ic cap to OUTPL in the Pin Functions table                                                                                 | 4       |

| •  | Chang          | ed 2.3 Hz To 1.9 Hz for HIGH-PASS FIL                                              | TER in Table                     | 2               |                                                                                                                            | 14      |

| Ch | anges          | from Revision D (January 2015) to Re                                               | vision E                         |                 |                                                                                                                            | Page    |

| •  | Delete         | d Package DAP (32) from Part Number                                                | TPA3116D2 ir                     | n the <i>De</i> | vice Information table                                                                                                     | 1       |

|    |                |                                                                                    |                                  |                 |                                                                                                                            |         |

| Ch | anges          | from Revision C (April 2012) to Revisi                                             | ion D                            |                 |                                                                                                                            | Page    |

| •  | Modes          | s, Application and Implementation section                                          | n, <i>Power Supp</i>             | oly Reco        | Feature Description section, Device Functional mmendations section, Layout section, Device d Orderable Information section |         |

| Ch | anges          | from Revision B (May 2012) to Revision                                             | on C                             |                 |                                                                                                                            | Page    |

|    |                |                                                                                    |                                  |                 |                                                                                                                            | 6       |

| •  | Chang          | ied Notes 2 and 3 of the <i>Thermal Inform</i>                                     | ation Table                      |                 |                                                                                                                            |         |

| •  | _              |                                                                                    |                                  |                 |                                                                                                                            |         |

| •  | Chang          | ed the Gain (BTL) Test Condition values                                            | for R1 and R                     | 2               |                                                                                                                            | 6       |

| •  | Chang<br>Chang | ed the Gain (BTL) Test Condition values<br>ed the Gain (SLV) Test Condition values | s for R1 and R<br>s for R1 and R | 2               |                                                                                                                            | 6<br>6  |

Submit Documentation Feedback

Copyright © 2012–2017, Texas Instruments Incorporated

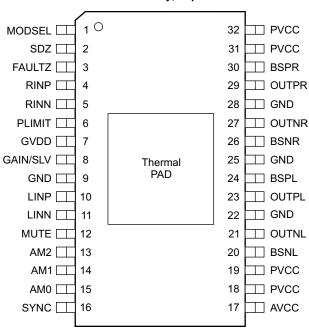

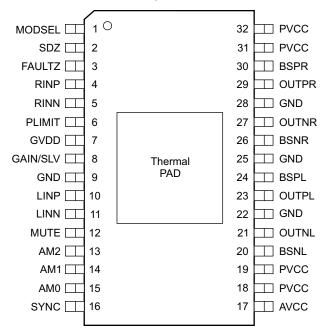

## 5 Pin Configuration and Functions

DAD Package 32-Pin HTSSOP With PowerPAD Up TPA3116D2 Only, Top View

DAP Package 32-Pin HTSSOP With PowerPAD Down Top View

## **Pin Functions**

|     | PIN      |                     | Fili Fulictions                                                                                                                                                                                           |

|-----|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                               |

| 1   | MODSEL   | I                   | Mode selection logic input (LOW = BD mode, HIGH = 1 SPW mode). TTL logic levels with compliance to AVCC.                                                                                                  |

| 2   | SDZ      | I                   | Shutdown logic input for audio amp (LOW = outputs Hi-Z, HIGH = outputs enabled). TTL logic levels with compliance to AVCC.                                                                                |

| 3   | FAULTZ   | DO                  | General fault reporting including Over-temp, DC Detect. Open drain.  FAULTZ = High, normal operation  FAULTZ = Low, fault condition                                                                       |

| 4   | RINP     | I                   | Positive audio input for right channel. Biased at 3 V.                                                                                                                                                    |

| 5   | RINN     | I                   | Negative audio input for right channel. Biased at 3 V.                                                                                                                                                    |

| 6   | PLIMIT   | I                   | Power limit level adjust. Connect a resistor divider from GVDD to GND to set power limit. Connect directly to GVDD for no power limit.                                                                    |

| 7   | GVDD     | PO                  | Internally generated gate voltage supply. Not to be used as a supply or connected to any component other than a 1 $\mu$ F X7R ceramic decoupling capacitor and the PLIMIT and GAIN/SLV resistor dividers. |

| 8   | GAIN/SLV | I                   | Selects Gain and selects between Master and Slave mode depending on pin voltage divider.                                                                                                                  |

| 9   | GND      | G                   | Ground                                                                                                                                                                                                    |

| 10  | LINP     | I                   | Positive audio input for left channel. Biased at 3 V. Connect to GND for PBTL mode.                                                                                                                       |

| 11  | LINN     | I                   | Negative audio input for left channel. Biased at 3 V. Connect to GND for PBTL mode.                                                                                                                       |

| 12  | MUTE     | I                   | Mute signal for fast disable/enable of outputs (HIGH = outputs Hi-Z, LOW = outputs enabled). TTL logic levels with compliance to AVCC.                                                                    |

| 13  | AM2      | I                   | AM Avoidance Frequency Selection                                                                                                                                                                          |

| 14  | AM1      | I                   | AM Avoidance Frequency Selection                                                                                                                                                                          |

| 15  | AM0      | I                   | AM Avoidance Frequency Selection                                                                                                                                                                          |

| 16  | SYNC     | DIO                 | Clock input/output for synchronizing multiple class-D devices. Direction determined by GAIN/SLV terminal.                                                                                                 |

| 17  | AVCC     | Р                   | Analog Supply                                                                                                                                                                                             |

| 18  | PVCC     | Р                   | Power supply                                                                                                                                                                                              |

| 19  | PVCC     | Р                   | Power supply                                                                                                                                                                                              |

| 20  | BSNL     | BST                 | Boot strap for negative left channel output, connect to 220 nF X5R, or better ceramic cap to OUTNL                                                                                                        |

| 21  | OUTNL    | PO                  | Negative left channel output                                                                                                                                                                              |

| 22  | GND      | G                   | Ground                                                                                                                                                                                                    |

| 23  | OUTPL    | PO                  | Positive left channel output                                                                                                                                                                              |

| 24  | BSPL     | BST                 | Boot strap for positive left channel output, connect to 220 nF X5R, or better ceramic cap to OUTPL                                                                                                        |

| 25  | GND      | G                   | Ground                                                                                                                                                                                                    |

| 26  | BSNR     | BST                 | Boot strap for negative right channel output, connect to 220 nF X5R, or better ceramic cap to OUTNR                                                                                                       |

| 27  | OUTNR    | PO                  | Negative right channel output                                                                                                                                                                             |

| 28  | GND      | G                   | Ground                                                                                                                                                                                                    |

| 29  | OUTPR    | PO                  | Positive right channel output                                                                                                                                                                             |

| 30  | BSPR     | BST                 | Boot strap for positive right channel output, connect to 220 nF X5R or better ceramic cap to OUTPR                                                                                                        |

| 31  | PVCC     | Р                   | Power supply                                                                                                                                                                                              |

| 32  | PVCC     | Р                   | Power supply                                                                                                                                                                                              |

| 33  | PowerPAD | G                   | Connect to GND for best system performance. If not connected to GND, leave floating.                                                                                                                      |

(1) **TYPE**: DO = Digital Output, I = Analog Input, G = General Ground, PO = Power Output, BST = Boot Strap.

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                 |                                     | MIN  | MAX      | UNIT |

|-------------------------------------------------|-------------------------------------|------|----------|------|

| Supply voltage, V <sub>CC</sub>                 | PV <sub>CC</sub> , AV <sub>CC</sub> | -0.3 | 30       | V    |

|                                                 | INPL, INNL, INPR, INNR              | -0.3 | 6.3      | V    |

| Input voltage, V <sub>I</sub>                   | PLIMIT, GAIN / SLV, SYNC            | -0.3 | GVDD+0.3 | V    |

|                                                 | AM0, AM1, AM2, MUTE, SDZ, MODSEL    | -0.3 | PVCC+0.3 | V    |

| Slew rate, maximum <sup>(2)</sup>               | AM0, AM1, AM2, MUTE, SDZ, MODSEL    |      | 10       | V/ms |

| Operating free-air temper                       | rature, T <sub>A</sub>              | -40  | 85       | °C   |

| Operating junction temperature , T <sub>J</sub> |                                     | -40  | 150      | °C   |

| Storage temperature, T <sub>st</sub>            | g                                   | -40  | 125      | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                             |                                                                        |                                               | MIN | NOM | MAX | UNIT |

|-----------------------|-----------------------------|------------------------------------------------------------------------|-----------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>       | Supply voltage              | PV <sub>CC</sub> , AV <sub>CC</sub>                                    |                                               | 4.5 |     | 26  | V    |

| V <sub>IH</sub>       | High-level input voltage    | AM0, AM1, AM2, MUTE, SDZ, SYNC, MO                                     | DSEL                                          | 2   |     |     | V    |

| V <sub>IL</sub>       | Low-level input voltage     | AM0, AM1, AM2, MUTE, SDZ, SYNC, MO                                     | DSEL                                          |     |     | 8.0 | V    |

| V <sub>OL</sub>       | Low-level output voltage    | FAULTZ, $R_{PULL-UP} = 100 \text{ k}\Omega$ , $PV_{CC} = 26 \text{ V}$ |                                               |     |     | 8.0 | V    |

| I <sub>IH</sub>       | High-level input current    | AM0, AM1, AM2, MUTE, SDZ, MODSEL (                                     | V <sub>I</sub> = 2 V, V <sub>CC</sub> = 18 V) |     |     | 50  | μΑ   |

| D (DTL)               |                             | Output filter I 10 ull C 600 pF                                        | TPA3116D2, TPA3118D2                          | 3.2 | 4   |     |      |

| R <sub>L</sub> (BTL)  | Minimum load                | Output filter: L = 10 μH, C = 680 nF                                   | TPA3130D2                                     | 5.6 | 8   |     | 0    |

| D (DDTI)              | Impedance                   | Output filters I 40 vIII C 4 vF                                        | TPA3116D2, TPA3118D2                          | 1.6 |     |     | Ω    |

| R <sub>L</sub> (PBTL) |                             | Output filter: L = 10 μH, C = 1 μF                                     | TPA3130D2                                     | 3.2 | 4   |     |      |

| Lo                    | Output-filter<br>Inductance | Minimum output filter inductance under sho                             | ort-circuit condition                         | 1   |     |     | μΗ   |

Copyright © 2012–2017, Texas Instruments Incorporated

<sup>(2)</sup>  $100 \text{ k}\Omega$  series resistor is needed if maximum slew rate is exceeded.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. .

#### 6.4 Thermal Information

|                 | THERMAL METRIC <sup>(1)</sup>                | TPA3130D2<br>DAP <sup>(2)</sup> | TPA3118D2<br>DAP <sup>(3)</sup> | TPA3116D2<br>DAD <sup>(4)</sup> | UNIT |

|-----------------|----------------------------------------------|---------------------------------|---------------------------------|---------------------------------|------|

|                 |                                              | 32 PINS                         | 32 PINS                         | 32 PINS                         |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 36                              | 22                              | 14                              |      |

| ΨЈТ             | Junction-to-top characterization parameter   | 0.4                             | 0.3                             | 1.2                             | °C/W |

| ΨЈВ             | Junction-to-board characterization parameter | 5.9                             | 4.7                             | 5.7                             |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

- For the PCB layout please see the TPA3130D2EVM user guide. For the PCB layout please see the TPA3118D2EVM user guide.

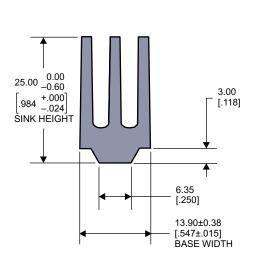

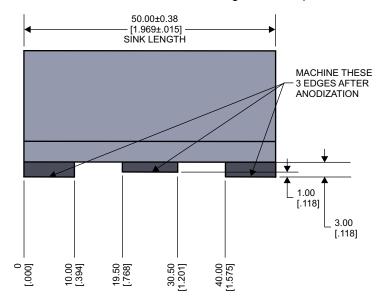

- (4) The heat sink drawing used for the thermal model data are shown in the application section, size: 14mm wide, 50mm long, 25mm high.

#### 6.5 DC Electrical Characteristics

$T_A = 25$ °C,  $AV_{CC} = PV_{CC} = 12$  V to 24 V,  $R_L = 4$   $\Omega$  (unless otherwise noted)

| PARAMETER           |                                                         | TEST CONDITIONS                                                           | MIN  | TYP  | MAX  | UNIT     |  |

|---------------------|---------------------------------------------------------|---------------------------------------------------------------------------|------|------|------|----------|--|

| Vos                 | Class-D output offset voltage (measured differentially) | V <sub>I</sub> = 0 V, Gain = 36 dB                                        |      | 1.5  | 15   | mV       |  |

|                     | Outros and outros to the comment                        | SDZ = 2 V, No load or filter, PV <sub>CC</sub> = 12 V                     |      | 20   | 35   | A        |  |

| I <sub>CC</sub>     | Quiescent supply current                                | SDZ = 2 V, No load or filter, PV <sub>CC</sub> = 24 V                     |      | 32   | 50   | mA       |  |

|                     | Quiescent supply current in shutdown                    | SDZ = 0.8 V, No load or filter, $PV_{CC}$ = 12 V                          |      | <50  |      |          |  |

| I <sub>CC(SD)</sub> | mode                                                    | SDZ = 0.8 V, No load or filter, $PV_{CC}$ = 24 V                          |      | 50   | 400  | μA       |  |

| r <sub>DS(on)</sub> | Drain-source on-state resistance, measured pin to pin   | PV <sub>CC</sub> = 21 V, I <sub>out</sub> = 500 mA, T <sub>J</sub> = 25°C |      | 120  |      | mΩ       |  |

|                     |                                                         | R1 = 5.6 kΩ, R2 = Open                                                    | 19   | 20   | 21   | 10       |  |

| 0                   | Gain (BTL)                                              | R1 = 20 k $\Omega$ , R2 = 100 k $\Omega$                                  | 25   | 26   | 27   | dB<br>dB |  |

| G                   |                                                         | R1 = 39 k $\Omega$ , R2 = 100 k $\Omega$                                  | 31   | 32   | 33   |          |  |

|                     |                                                         | R1 = 47 k $\Omega$ , R2 = 75 k $\Omega$                                   |      | 36   | 37   | ub       |  |

|                     |                                                         | R1 = 51 k $\Omega$ , R2 = 51 k $\Omega$                                   | 19   | 20   | 21   | 40       |  |

| 0                   | Caia (CLV)                                              | R1 = 75 k $\Omega$ , R2 = 47 k $\Omega$                                   | 25   | 26   | 27   | dB       |  |

| G                   | Gain (SLV)                                              | R1 = 100 kΩ, R2 = 39 kΩ                                                   | 31   | 32   | 33   | i.       |  |

|                     |                                                         | R1 = 100 kΩ, R2 = 16 kΩ                                                   | 35   | 36   | 37   | dB       |  |

| t <sub>on</sub>     | Turn-on time                                            | SDZ = 2 V                                                                 |      | 10   |      | ms       |  |

| t <sub>OFF</sub>    | Turn-off time                                           | SDZ = 0.8 V                                                               |      | 2    |      | μs       |  |

| GVDD                | Gate drive supply                                       | IGVDD < 200 μA                                                            | 6.4  | 6.9  | 7.4  | V        |  |

| V <sub>O</sub>      | Output voltage maximum under PLIMIT control             | V(PLIMIT) = 2 V; V <sub>I</sub> = 1 V <sub>rms</sub>                      | 6.75 | 7.90 | 8.75 | V        |  |

Product Folder Links: TPA3116D2 TPA3118D2 TPA3130D2

## 6.6 AC Electrical Characteristics

$T_A$  = 25°C,  $AV_{CC}$  =  $PV_{CC}$  = 12 V to 24 V,  $R_L$  = 4  $\Omega$  (unless otherwise noted)

|                  | PARAMETER                         | TEST CONDITIONS                                                               | MIN      | TYP  | MAX  | UNIT |

|------------------|-----------------------------------|-------------------------------------------------------------------------------|----------|------|------|------|

| KSVR             | Power supply ripple rejection     | 200 mV <sub>PP</sub> ripple at 1 kHz, Gain = 20 dB, Inputs AC-coupled to GND  |          | -70  |      | dB   |

| D                | Continuous sutput nouser          | THD+N = 10%, f = 1 kHz, PV <sub>CC</sub> = 14.4 V                             |          | 25   |      | W    |

| P <sub>O</sub>   | Continuous output power           | THD+N = 10%, f = 1 kHz, PV <sub>CC</sub> = 21 V                               |          | 50   |      | VV   |

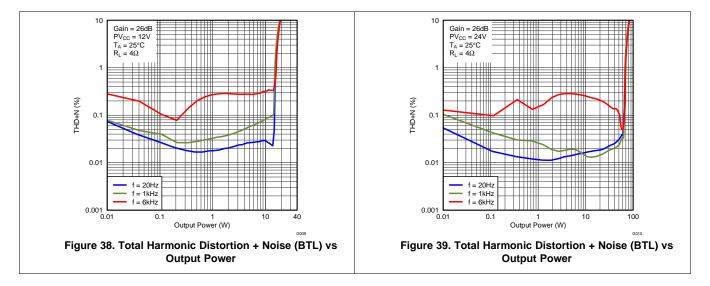

| THD+N            | Total harmonic distortion + noise | $V_{CC} = 21 \text{ V, f} = 1 \text{ kHz, P}_{O} = 25 \text{ W (half-power)}$ |          | 0.1% |      |      |

| Vn               | Output integrated noise           | 20 Hz to 22 kHz, A-weighted filter, Gain = 20 dB                              |          | 65   |      | μV   |

| VII              | Output integrated noise           | 20 FIZ to 22 KHZ, A-weighted liner, Gain = 20 db                              |          | -80  |      | dBV  |

|                  | Crosstalk                         | $V_O = 1 V_{rms}$ , Gain = 20 dB, f = 1 kHz                                   |          | -100 |      | dB   |

| SNR              | Signal-to-noise ratio             | Maximum output at THD+N < 1%, f = 1 kHz, Gain = 20 dB, A-weighted             |          | 102  |      | dB   |

|                  |                                   | AM2=0, AM1=0, AM0=0                                                           | 376      | 400  | 424  |      |

|                  |                                   | AM2=0, AM1=0, AM0=1                                                           | 470      | 500  | 530  |      |

|                  |                                   | AM2=0, AM1=1, AM0=0                                                           | 564      | 600  | 636  |      |

|                  | Oscillator fraguescy              | AM2=0, AM1=1, AM0=1                                                           | 940      | 1000 | 1060 | kHz  |

| f <sub>OSC</sub> | Oscillator frequency              | AM2=1, AM1=0, AM0=0                                                           | 1128     | 1200 | 1278 | KHZ  |

|                  |                                   | AM2=1, AM1=0, AM0=1                                                           |          |      |      |      |

|                  |                                   | AM2=1, AM1=1, AM0=0                                                           | Reserved |      |      |      |

|                  |                                   | AM2=1, AM1=1, AM0=1                                                           |          |      |      |      |

|                  | Thermal trip point                |                                                                               |          | 150+ |      | °C   |

|                  | Thermal hysteresis                |                                                                               |          | 15   |      | °C   |

|                  | Out a summant to a sint           | TPA3130D2                                                                     | 4.5      |      |      |      |

|                  | Over current trip point           | TPA3118D2, TPA3116D2                                                          | 7.5      |      | Α    |      |

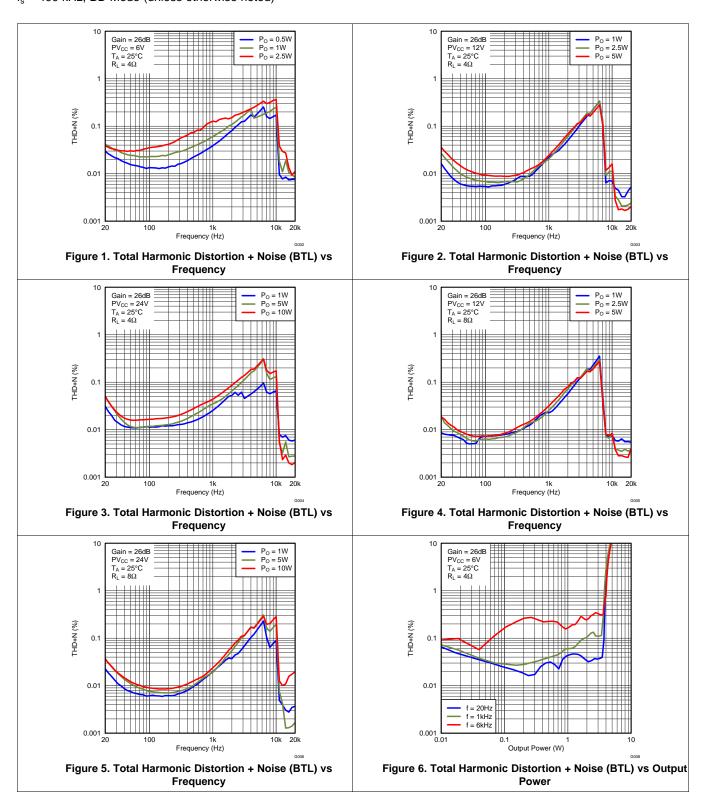

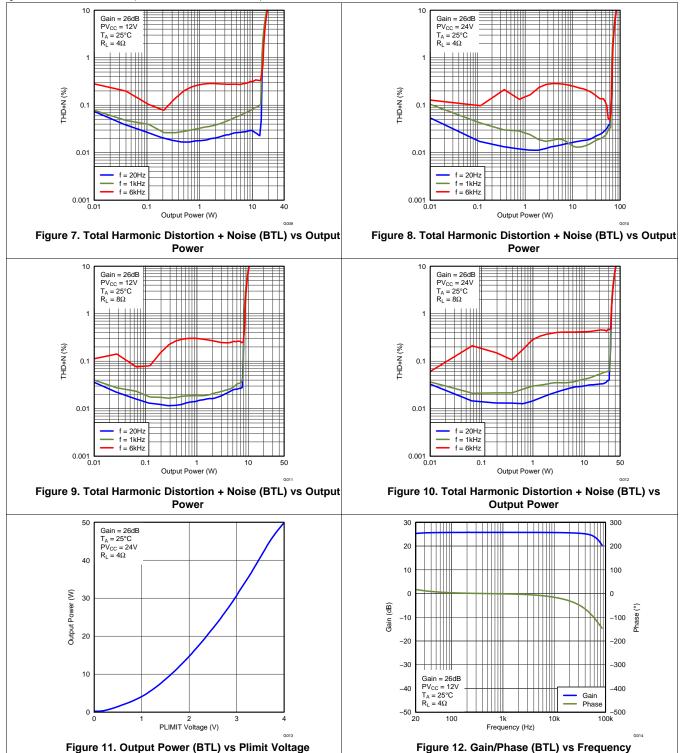

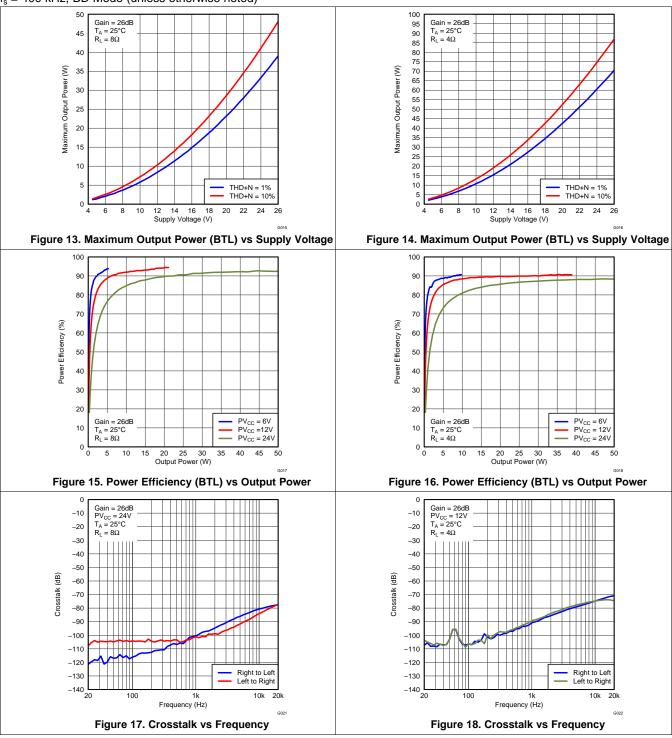

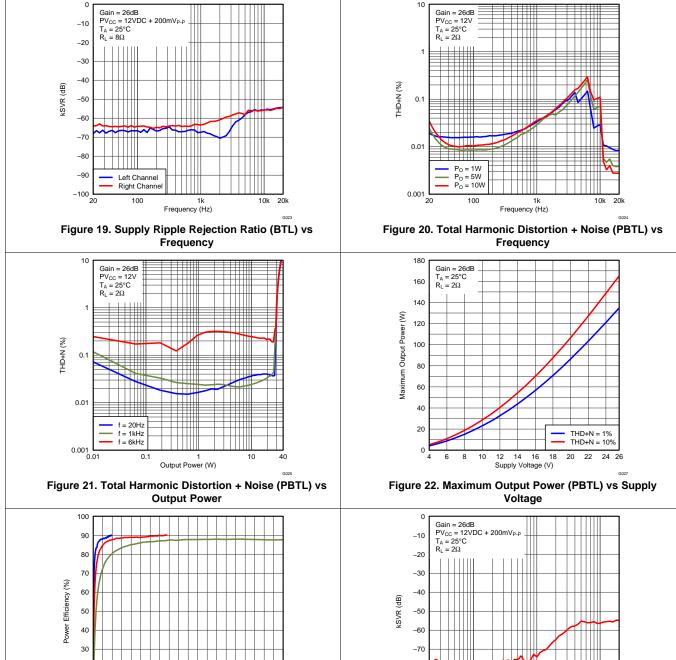

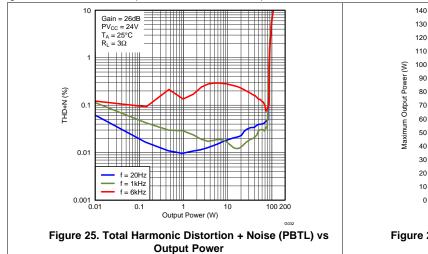

## 6.7 Typical Characteristics

$f_s = 400 \text{ kHz}$ , BD Mode (unless otherwise noted)

f<sub>s</sub> = 400 kHz, BD Mode (unless otherwise noted)

f<sub>s</sub> = 400 kHz, BD Mode (unless otherwise noted)

Submit Documentation Feedback

Copyright © 2012–2017, Texas Instruments Incorporated

f<sub>s</sub> = 400 kHz, BD Mode (unless otherwise noted)

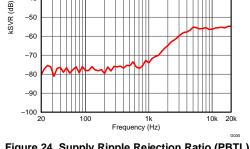

Figure 23. Power Efficiency (PBTL) vs Output Power

40 50 60

70 80 90

PV<sub>CC</sub> = 6V PV<sub>CC</sub> = 12V PV<sub>CC</sub> =24V

Figure 24. Supply Ripple Rejection Ratio (PBTL) vs Frequency

20

10

Gain = 26dB

$T_A = 25^{\circ}C$  $R_L = 2\Omega$

10 20 30

f<sub>s</sub> = 400 kHz, BD Mode (unless otherwise noted)

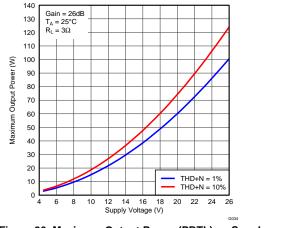

Figure 26. Maximum Output Power (PBTL) vs Supply Voltage

Submit Documentation Feedback

Copyright © 2012–2017, Texas Instruments Incorporated

## 7 Detailed Description

#### 7.1 Overview

The TPA31xxD2 device is a highly efficient Class D audio amplifier with integrated 120m Ohms MOSFET that allows output currents up to 7.5 A. The high efficiency allows the amplifier to provide an excellent audio performance without the need for a bulky heat sink.

The device can be configured for either master or slave operation by using the SYNC pin. This helps to prevent audible beats noise.

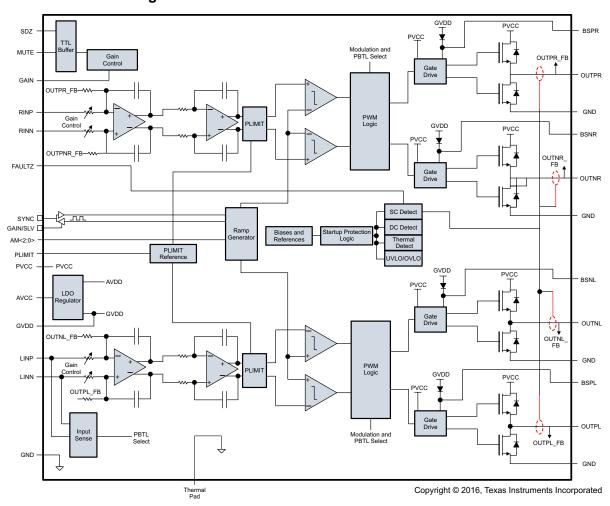

## 7.2 Functional Block Diagram

## 7.3 Feature Description

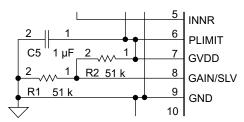

## 7.3.1 Gain Setting and Master and Slave

The gain of the TPA31xxD2 family is set by the voltage divider connected to the GAIN/SLV control pin. Master or Slave mode is also controlled by the same pin. An internal ADC is used to detect the 8 input states. The first four stages sets the GAIN in Master mode in gains of 20, 26, 32, 36 dB respectively, while the next four stages sets the GAIN in Slave mode in gains of 20, 26, 32, 36 dB respectively. The gain setting is latched during power-up and cannot be changed while device is powered. Table 1 lists the recommended resistor values and the state and gain:

Copyright © 2012–2017, Texas Instruments Incorporated

#### **Feature Description (continued)**

Table 1. Gain and Master/Slave

| MASTER / SLAVE<br>MODE | GAIN  | R1 (to GND) <sup>(1)</sup> | R2 (to GVDD) <sup>(1)</sup> | INPUT IMPEDANCE |

|------------------------|-------|----------------------------|-----------------------------|-----------------|

| Master                 | 20 dB | 5.6 kΩ                     | OPEN                        | 60 kΩ           |

| Master                 | 26 dB | 20 kΩ                      | 100 kΩ                      | 30 kΩ           |

| Master                 | 32 dB | 39 kΩ                      | 100 kΩ                      | 15 kΩ           |

| Master                 | 36 dB | 47 kΩ                      | 75 kΩ                       | 9 kΩ            |

| Slave                  | 20 dB | 51 kΩ                      | 51 kΩ                       | 60 kΩ           |

| Slave                  | 26 dB | 75 kΩ                      | 47 kΩ                       | 30 kΩ           |

| Slave                  | 32 dB | 100 kΩ                     | 39 kΩ                       | 15 kΩ           |

| Slave                  | 36 dB | 100 kΩ                     | 16 kΩ                       | 9 kΩ            |

(1) Resistor tolerance should be 5% or better.

Figure 27. Gain, Master/Slave

In Master mode, SYNC terminal is an output, in Slave mode, SYNC terminal is an input for a clock input. TTL logic levels with compliance to GVDD.

#### 7.3.2 Input Impedance

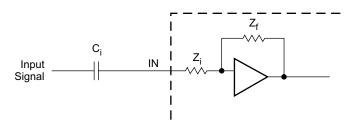

The TPA31xxD2 family input stage is a fully differential input stage and the input impedance changes with the gain setting from 9 k $\Omega$  at 36 dB gain to 60 k $\Omega$  at 20 dB gain. Table 1 lists the values from min to max gain. The tolerance of the input resistor value is ±20% so the minimum value will be higher than 7.2 k $\Omega$ . The inputs need to be AC-coupled to minimize the output dc-offset and ensure correct ramping of the output voltages during power-ON and power-OFF. The input ac-coupling capacitor together with the input impedance forms a high-pass filter with the following cut-off frequency:

$$f = \frac{1}{2\pi Z_i C_i} \tag{1}$$

If a flat bass response is required down to 20 Hz the recommended cut-off frequency is a tenth of that, 2 Hz. Table 2 lists the recommended ac-couplings capacitors for each gain step. If a -3 dB is accepted at 20 Hz 10 times lower capacitors can used – for example, a 1 µF can be used.

**Table 2. Recommended Input AC-Coupling Capacitors**

| GAIN  | INPUT IMPEDANCE | INPUT CAPACITANCE | HIGH-PASS FILTER |

|-------|-----------------|-------------------|------------------|

| 20 dB | 60 kΩ           | 1.5 μF            | 1.8 Hz           |

| 26 dB | 30 kΩ           | 3.3 µF            | 1.6 Hz           |

| 32 dB | 15 kΩ           | 5.6 μF            | 1.9 Hz           |

| 36 dB | 9 kΩ            | 10 μF             | 1.8 Hz           |

Figure 28. Input Impedance

The input capacitors used should be a type with low leakage, like quality electrolytic, tantalum or ceramic. If a polarized type is used the positive connection should face the input pins which are biased to 3 Vdc.

#### 7.3.3 Startup and Shutdown Operation

The TPA31xxD2 family employs a shutdown mode of operation designed to reduce supply current (Icc) to the absolute minimum level during periods of nonuse for power conservation. The SDZ input terminal should be held high (see specification table for trip point) during normal operation when the amplifier is in use. Pulling SDZ low will put the outputs to mute and the amplifier to enter a low-current state. It is not recommended to leave SDZ unconnected, because amplifier operation would be unpredictable.

For the best power-off pop performance, place the amplifier in the shutdown mode prior to removing the power supply. The gain setting is selected at the end of the start-up cycle. At the end of the start-up cycle, the gain is selected and cannot be changed until the next power-up.

## 7.3.4 PLIMIT Operation

The TPA31xxD2 family has a built-in voltage limiter that can be used to limit the output voltage level below the supply rail, the amplifier simply operates as if it was powered by a lower supply voltage, and thereby limits the output power. Add a resistor divider from GVDD to ground to set the voltage at the PLIMIT pin. An external reference may also be used if tighter tolerance is required. Add a 1 µF capacitor from pin PLIMIT to ground to ensure stability. It is recommended to connect PLIMIT to GVDD when using 1SPW-modulation mode.

Figure 29. Power Limit Example

The PLIMIT circuit sets a limit on the output peak-to-peak voltage. The limiting is done by limiting the duty cycle to a fixed maximum value. This limit can be thought of as a "virtual" voltage rail which is lower than the supply connected to PVCC. This "virtual" rail is approximately 4 times the voltage at the PLIMIT pin. This output voltage can be used to calculate the maximum output power for a given maximum input voltage and speaker impedance.

$$P_{OUT} = \frac{\left( \left( \frac{R_L}{R_L + 2 \times R_S} \right) \times V_P \right)^2}{2 \times R_I}$$

for unclipped power

where

- $P_{OUT}$  (10% THD) = 1.25 x  $P_{OUT}$  (unclipped)

- R<sub>I</sub> is the load resistance.

- R<sub>S</sub> is the total series resistance including R<sub>DS(on)</sub>, and output filter resistance.

- V<sub>P</sub> is the peak amplitude

- $V_P = 4 \times PLIMIT \text{ voltage if PLIMIT} < 4 \times V_P$

(2)

**Table 3. Power Limit Example**

| PV <sub>CC</sub> (V) | PLIMIT VOLTAGE (V) <sup>(1)</sup> | R to GND | R to GVDD | OUTPUT VOLTAGE (V <sub>rms</sub> ) |  |  |

|----------------------|-----------------------------------|----------|-----------|------------------------------------|--|--|

| 24 V                 | GVDD                              | Open     | Short     | 17.9                               |  |  |

| 24 V                 | 3.3                               | 45 kΩ    | 51 kΩ     | 12.67                              |  |  |

| 24 V                 | 2.25                              | 24 kΩ    | 51 kΩ     | 9                                  |  |  |

| 12 V                 | GVDD                              | Short    | Open      | 10.33                              |  |  |

| 12 V                 | 2.25                              | 24 kΩ    | 51 kΩ     | 9                                  |  |  |

| 12 V                 | 1.5                               | 18 kΩ    | 68 kΩ     | 6.3                                |  |  |

<sup>(1)</sup> PLIMIT measurements taken with EVM gain set to 26 dB and input voltage set to 1  $V_{rms}$ .

#### 7.3.5 GVDD Supply

The GVDD Supply is used to power the gates of the output full bridge transistors. It can also be used to supply the PLIMIT and GAIN/SLV voltage dividers. Decouple GVDD with a X5R ceramic 1  $\mu$ F capacitor to GND. The GVDD supply is not intended to be used for external supply. It is recommended to limit the current consumption by using resistor voltage dividers for GAIN/SLV and PLIMIT of 100 k $\Omega$  or more.

#### 7.3.6 BSPx AND BSNx Capacitors

The full H-bridge output stages use only NMOS transistors. Therefore, they require bootstrap capacitors for the high side of each output to turn on correctly. A 220 nF ceramic capacitor of quality X5R or better, rated for at least 16 V, must be connected from each output to its corresponding bootstrap input. (See the application circuit diagram in Figure 37.) The bootstrap capacitors connected between the BSxx pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry. During each high-side switching cycle, the bootstrap capacitors hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on.

## 7.3.7 Differential Inputs

The differential input stage of the amplifier cancels any noise that appears on both input lines of the channel. To use the TPA31xxD2 family with a differential source, connect the positive lead of the audio source to the RINP or LINP input and the negative lead from the audio source to the RINN or LINN input. To use the TPA31xxD2 family with a single-ended source, ac ground the negative input through a capacitor equal in value to the input capacitor on positive and apply the audio source to either input. In a single-ended input application, the unused input should be ac grounded at the audio source instead of at the device input for best noise performance. For good transient performance, the impedance seen at each of the two differential inputs should be the same.

The impedance seen at the inputs should be limited to an RC time constant of 1 ms or less if possible. This is to allow the input dc blocking capacitors to become completely charged during the 10 ms power-up time. If the input capacitors are not allowed to completely charge, there will be some additional sensitivity to component matching which can result in pop if the input components are not well matched.

#### 7.3.8 Device Protection System

The TPA31xxD2 family contains a complete set of protection circuits carefully designed to make system design efficient as well as to protect the device against any kind of permanent failures due to short circuits, overload, over temperature, and under-voltage. The FAULTZ pin will signal if an error is detected according to Table 4:

TRIGGERING CONDITION LATCHED/SELF-**FAULT FAULTZ ACTION** (typical value) **CLEARING** Over Current Output short or short to PVCC or GND Latched I ow Output high impedance Over Temperature  $T_i > 150$ °C Low Output high impedance Latched Too High DC Offset Latched DC output voltage I ow Output high impedance Under Voltage on PVCC < 4.5V Output high impedance Self-clearing **PVCC** Over Voltage on PVCC > 27V Output high impedance Self-clearing **PVCC**

**Table 4. Fault Reporting**

#### 7.3.9 DC Detect Protection

The TPA31xxD2 family has circuitry which will protect the speakers from DC current which might occur due to defective capacitors on the input or shorts on the printed circuit board at the inputs. A DC detect fault will be reported on the FAULT pin as a low state. The DC Detect fault will also cause the amplifier to shutdown by changing the state of the outputs to Hi-Z.

If automatic recovery from the short circuit protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the DC Detect protection latch.

A DC Detect Fault is issued when the output differential duty-cycle of either channel exceeds 60% for more than 420 msec at the same polarity. Table x below shows some examples of the typical DC Detect Protection threshold for several values of the supply voltage. This feature protects the speaker from large DC currents or AC currents less than 2Hz. To avoid nuisance faults due to the DC detect circuit, hold the SD pin low at power-up until the signals at the inputs are stable. Also, take care to match the impedance seen at the positive and negative inputs to avoid nuisance DC detect faults.

Table 5 lists the minimum output offset voltages required to trigger the DC detect. The outputs must remain at or above the voltage listed in the table for more than 420 ms to trigger the DC detect.

| PV <sub>CC</sub> (V) | V <sub>OS</sub> - OUTPUT OFFSET VOLTAGE (V) |  |  |

|----------------------|---------------------------------------------|--|--|

| 4.5                  | 0.96                                        |  |  |

| 6                    | 1.3                                         |  |  |

| 12                   | 2.6                                         |  |  |

| 18                   | 3.9                                         |  |  |

**Table 5. DC Detect Threshold**

#### 7.3.10 Short-Circuit Protection and Automatic Recovery Feature

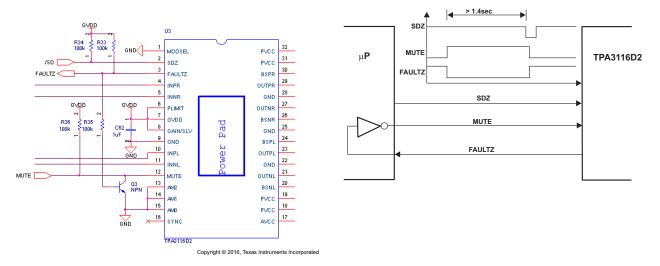

The TPA31xxD2 family has protection from over current conditions caused by a short circuit on the output stage. The short circuit protection fault is reported on the FAULTZ pin as a low state. The amplifier outputs are switched to a high impedance state when the short circuit protection latch is engaged. The latch can be cleared by cycling the SDZ pin through the low state.

If automatic recovery from the short circuit protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the short-circuit protection latch.

In systems where a possibility of a permanent short from the output to PVDD or to a high voltage battery like a car battery can occur, pull the MUTE pin low with the FAULTZ signal with a inverting transistor to ensure a high-Z restart, like shown in the figure below:

Copyright © 2012–2017, Texas Instruments Incorporated

Figure 30. MUTE Driven by Inverted FAULTZ

Figure 31. Timing Requirement for SDZ

#### 7.3.11 Thermal Protection

Thermal protection on the TPA31xxD2 family prevents damage to the device when the internal die temperature exceeds 150°C. There is a ±15°C tolerance on this trip point from device to device. Once the die temperature exceeds the thermal trip point, the device enters into the shutdown state and the outputs are disabled. This is a latched fault.

Thermal protection faults are reported on the FAULTZ terminal as a low state.

If automatic recovery from the thermal protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the thermal protection latch.

#### 7.3.12 Device Modulation Scheme

The TPA31xxD2 family has the option of running in either BD modulation or 1SPW modulation; this is set by the MODSEL pin.

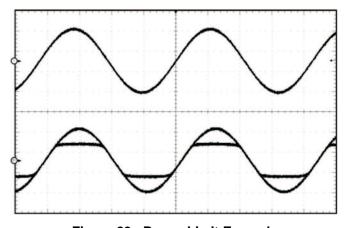

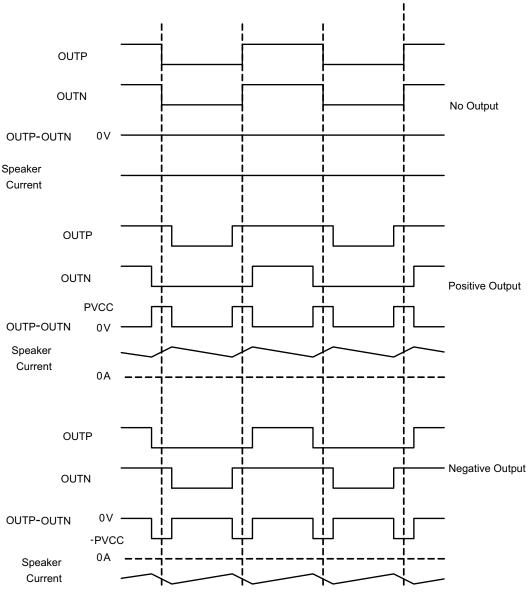

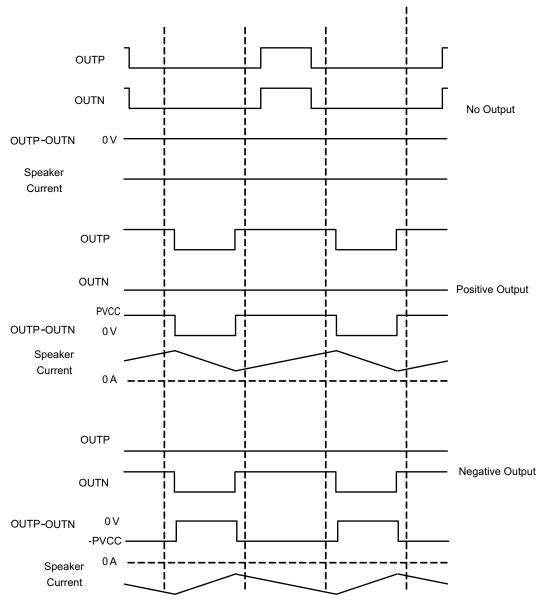

#### 7.3.12.1 MODSEL = GND: BD-Modulation

This is a modulation scheme that allows operation without the classic LC reconstruction filter when the amp is driving an inductive load with short speaker wires. Each output is switching from 0 volts to the supply voltage. The OUTPx and OUTNx are in phase with each other with no input so that there is little or no current in the speaker. The duty cycle of OUTPx is greater than 50% and OUTNx is less than 50% for positive output voltages. The duty cycle of OUTPx is less than 50% and OUTNx is greater than 50% for negative output voltages. The voltage across the load sits at 0V throughout most of the switching period, reducing the switching current, which reduces any I<sup>2</sup>R losses in the load.

Figure 32. BD Mode Modulation

#### 7.3.12.2 MODSEL = HIGH: 1SPW-modulation

The 1SPW mode alters the normal modulation scheme in order to achieve higher efficiency with a slight penalty in THD degradation and more attention required in the output filter selection. In 1SPW mode the outputs operate at ~15% modulation during idle conditions. When an audio signal is applied one output will decrease and one will increase. The decreasing output signal will quickly rail to GND at which point all the audio modulation takes place through the rising output. The result is that only one output is switching during a majority of the audio cycle. Efficiency is improved in this mode due to the reduction of switching losses. The THD penalty in 1SPW mode is minimized by the high performance feedback loop. The resulting audio signal at each half output has a discontinuity each time the output rails to GND. This can cause ringing in the audio reconstruction filter unless care is taken in the selection of the filter components and type of filter used.

Figure 33. 1SPW Mode Modulation

## 7.3.13 Efficiency: LC Filter Required with the Traditional Class-D Modulation Scheme

The main reason that the traditional class-D amplifier-based on AD modulation needs an output filter is that the switching waveform results in maximum current flow. This causes more loss in the load, which causes lower efficiency. The ripple current is large for the traditional modulation scheme, because the ripple current is proportional to voltage multiplied by the time at that voltage. The differential voltage swing is 2 x VCC, and the time at each voltage is half the period for the traditional modulation scheme. An ideal LC filter is needed to store the ripple current from each half cycle for the next half cycle, while any resistance causes power dissipation. The speaker is both resistive and reactive, whereas an LC filter is almost purely reactive.

The TPA3116D2 modulation scheme has little loss in the load without a filter because the pulses are short and the change in voltage is VCC instead of 2 x VCC. As the output power increases, the pulses widen, making the ripple current larger. Ripple current could be filtered with an LC filter for increased efficiency, but for most applications the filter is not needed.

An LC filter with a cutoff frequency less than the class-D switching frequency allows the switching current to flow through the filter instead of the load. The filter has less resistance but higher impedance at the switching frequency than the speaker, which results in less power dissipation, therefore increasing efficiency.

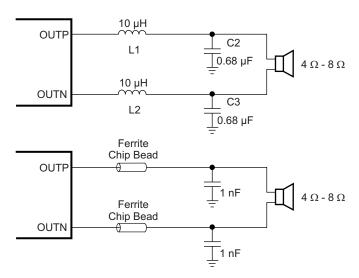

#### 7.3.14 Ferrite Bead Filter Considerations

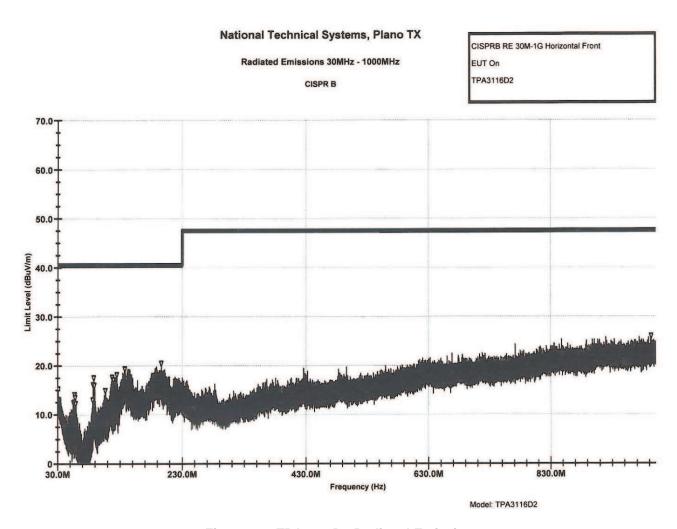

Using the Advanced Emissions Suppression Technology in the TPA3116D2 amplifier it is possible to design a high efficiency class-D audio amplifier while minimizing interference to surrounding circuits. It is also possible to accomplish this with only a low-cost ferrite bead filter. In this case it is necessary to carefully select the ferrite bead used in the filter. One important aspect of the ferrite bead selection is the type of material used in the ferrite bead. Not all ferrite material is alike, so it is important to select a material that is effective in the 10 to 100 MHz range which is key to the operation of the class-D amplifier. Many of the specifications regulating consumer electronics have emissions limits as low as 30 MHz. It is important to use the ferrite bead filter to block radiation in the 30 MHz and above range from appearing on the speaker wires and the power supply lines which are good antennas for these signals. The impedance of the ferrite bead can be used along with a small capacitor with a value in the range of 1000 pF to reduce the frequency spectrum of the signal to an acceptable level. For best performance, the resonant frequency of the ferrite bead/ capacitor filter should be less than 10 MHz.

Also, it is important that the ferrite bead is large enough to maintain its impedance at the peak currents expected for the amplifier. Some ferrite bead manufacturers specify the bead impedance at a variety of current levels. In this case it is possible to make sure the ferrite bead maintains an adequate amount of impedance at the peak current the amplifier will see. If these specifications are not available, it is also possible to estimate the bead current handling capability by measuring the resonant frequency of the filter output at low power and at maximum power. A change of resonant frequency of less than fifty percent under this condition is desirable. Examples of ferrite beads which have been tested and work well with the TPA3130D2 can be seen in the TPA3130D2EVM user guide SLOU341.

A high quality ceramic capacitor is also needed for the ferrite bead filter. A low ESR capacitor with good temperature and voltage characteristics will work best.

Additional EMC improvements may be obtained by adding snubber networks from each of the class-D outputs to ground. Suggested values for a simple RC series snubber network would be 18  $\Omega$  in series with a 330 pF capacitor although design of the snubber network is specific to every application and must be designed taking into account the parasitic reactance of the printed circuit board as well as the audio amp. Take care to evaluate the stress on the component in the snubber network especially if the amp is running at high PVCC. Also, make sure the layout of the snubber network is tight and returns directly to the GND pins on the IC.

Product Folder Links: TPA3116D2 TPA3118D2 TPA3130D2

Figure 34. TPA311xD2 Radiated Emissions

## 7.3.15 When to Use an Output Filter for EMI Suppression

The TPA3116D2 has been tested with a simple ferrite bead filter for a variety of applications including long speaker wires up to 125 cm and high power. The TPA3116D2 EVM passes FCC class-B specifications under these conditions using twisted speaker wires. The size and type of ferrite bead can be selected to meet application requirements. Also, the filter capacitor can be increased if necessary with some impact on efficiency.

There may be a few circuit instances where it is necessary to add a complete LC reconstruction filter. These circumstances might occur if there are nearby circuits which are sensitive to noise. In these cases a classic second order Butterworth filter similar to those shown in the figures below can be used.

Some systems have little power supply decoupling from the AC line but are also subject to line conducted interference (LCI) regulations. These include systems powered by "wall warts" and "power bricks." In these cases, LC reconstruction filters can be the lowest cost means to pass LCI tests. Common mode chokes using low frequency ferrite material can also be effective at preventing line conducted interference.

22 Submit Documentation Feedback

Copyright © 2012–2017, Texas Instruments Incorporated

Figure 35. TPA31xxD2 Output Filters

## 7.3.16 AM Avoidance EMI Reduction

To reduce interference in the AM radio band, the TPA3116D2 has the ability to change the switching frequency via AM<2:0> pins. The recommended frequencies are listed in Table 6. The fundamental frequency and its second harmonic straddle the AM radio band listed. This eliminates the tones that can be present due to the switching frequency being demodulated by the AM radio.

Table 6. AM Frequencies

| US                 | EUROPEAN           | CMITCHING EDECLIENCY (LU-) | AM2 | AM1 | AM0 |

|--------------------|--------------------|----------------------------|-----|-----|-----|

| AM FREQUENCY (kHz) | AM FREQUENCY (kHz) | SWITCHING FREQUENCY (kHz)  |     | AWI | AWU |

|                    | 522-540            |                            |     |     |     |

| 540-917            | 540-914            | 10-914 500                 |     | 0   | 1   |

| 047.4405           | 044.4400           | COO (nr. 400)              | 0   | 1   | 0   |

| 917-1125           | 914-1122           | 600 (or 400)               | 0   | 0   | 0   |

| 1125-1375          | 1122-1373          | 500                        | 0   | 0   | 1   |

| 4075 4547          | 4070 4540          | COO (nr. 400)              | 0   | 1   | 0   |

| 1375-1547          | 1373-1548          | 600 (or 400)               | 0   | 0   | 0   |

| 4547.4700          | 4540 4704          | 4540.4704                  |     | 1   | 0   |

| 1547-1700          | 1548-1701          | 600 (or 500)               | 0   | 0   | 1   |

#### 7.4 Device Functional Modes

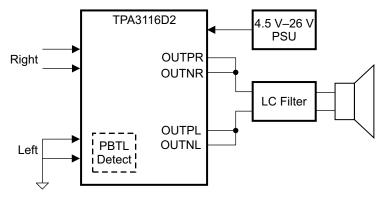

## 7.4.1 Mono Mode (PBTL)

The TPA31xxD2 family can be connected in MONO mode enabling up to 100W output power. This is done by:

- Connect INPL and INNL directly to Ground (without capacitors) this sets the device in Mono mode during power up.

- Connect OUTPR and OUTNR together for the positive speaker terminal and OUTNL and OUTPL together for the negative pin.

- Analog input signal is applied to INPR and INNR.

Figure 36. Mono Mode

Submit Documentation Feedback

Copyright © 2012-2017, Texas Instruments Incorporated

## 8 Application and Implementation

#### **NOTE**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

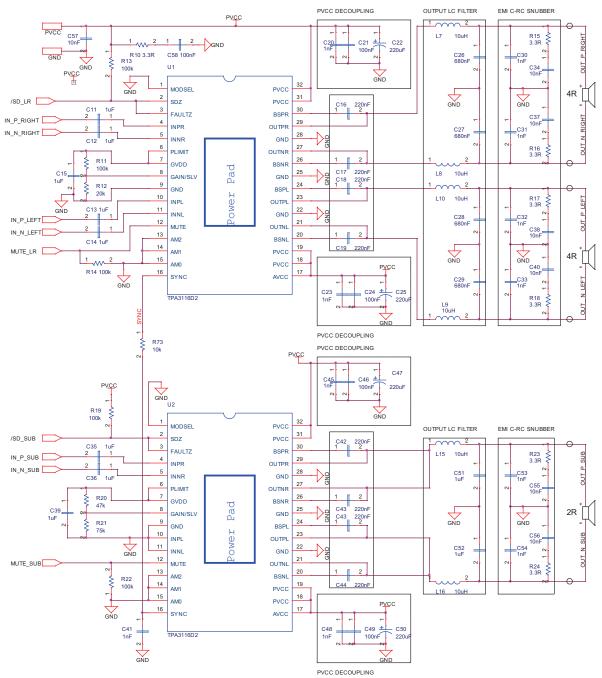

This section describes a 2.1 Master and Slave application. The Master is configured as stereo outputs and the Slave is configured as mono PBTL output.

## 8.2 Typical Application

A 2.1 solution, U1 TPA3116D2 in Master mode 400 kHz, BTL, gain if 20 dB, power limit not implemented. U2 in Slave, PBTL mode gain of 20 dB. Inputs are connected for differential inputs.

Product Folder Links: TPA3116D2 TPA3118D2 TPA3130D2

## **Typical Application (continued)**

Copyright © 2016, Texas Instruments Incorporated

Figure 37. Schematic

## **Typical Application (continued)**

#### 8.2.1 Design Requirements

| DESIGN PARAMETERS        | EXAMPLE VALUE                               |  |  |  |  |

|--------------------------|---------------------------------------------|--|--|--|--|

| Input voltage range PVCC | 4.5 V to 26 V                               |  |  |  |  |

| PWM output frequencies   | 400 kHz, 500 kHz, 600 kHz, 1 MHz or 1.2 MHz |  |  |  |  |

| Maximum output power     | 50 W                                        |  |  |  |  |

#### 8.2.2 Detailed Design Procedure

The TPA31xxD2 family is a very flexible and easy to use Class D amplifier; therefore the design process is straightforward. Before beginning the design, gather the following information regarding the audio system.

- · PVCC rail planned for the design

- Speaker or load impedance

- Maximum output power requirement

- Desired PWM frequency

#### 8.2.2.1 Select the PWM Frequency

Set the PWM frequency by using AM0, AM1 and AM2 pins.

#### 8.2.2.2 Select the Amplifier Gain and Master/Slave Mode

In order to select the amplifier gain setting, the designer must determine the maximum power target and the speaker impedance. Once these parameters have been determined, calculate the required output voltage swing which delivers the maximum output power.

Choose the lowest analog gain setting that corresponds to produce an output voltage swing greater than the required output swing for maximum power. The analog gain and master/slave mode can be set by selecting the voltage divider resistors (R1 and R2) on the Gain/SLV pin.

#### 8.2.2.3 Select Input Capacitance

Select the bulk capacitors at the PVCC inputs for proper voltage margin and adequate capacitance to support the power requirements. In practice, with a well-designed power supply, two  $100-\mu F$ , 50-V capacitors should be sufficient. One capacitor should be placed near the PVCC inputs at each side of the device. PVCC capacitors should be a low ESR type because they are being used in a high-speed switching application.

#### 8.2.2.4 Select Decoupling Capacitors

Good quality decoupling capacitors need to be added at each of the PVCC inputs to provide good reliability, good audio performance, and to meet regulatory requirements. X5R or better ratings should be used in this application. Consider temperature, ripple current, and voltage overshoots when selecting decoupling capacitors. Also, these decoupling capacitors should be located near the PVCC and GND connections to the device in order to minimize series inductances.

#### 8.2.2.5 Select Bootstrap Capacitors

Each of the outputs require bootstrap capacitors to provide gate drive for the high-side output FETs. For this design, use 0.22-μF, 25-V capacitors of X5R quality or better.

#### 8.2.3 Application Curves

## 9 Power Supply Recommendations

The power supply requirements for the TPA3116D2 consist of one higher-voltage supply to power the output stage of the speaker amplifier. Several on-chip regulators are included on the TPA3116D2 to generate the voltages necessary for the internal circuitry of the audio path. It is important to note that the voltage regulators which have been integrated are sized only to provide the current necessary to power the internal circuitry. The external pins are provided only as a connection point for off-chip bypass capacitors to filter the supply. Connecting external circuitry to these regulator outputs may result in reduced performance and damage to the device. The high voltage supply, between 4.5 V and 26 V, supplies the analog circuitry (AVCC) and the power stage (PVCC). The AVCC supply feeds internal LDO including GVDD. This LDO output are connected to external pins for filtering purposes, but should not be connected to external circuits. GVDD LDO output have been sized to provide current necessary for internal functions but not for external loading.

#### 10 Layout

## 10.1 Layout Guidelines

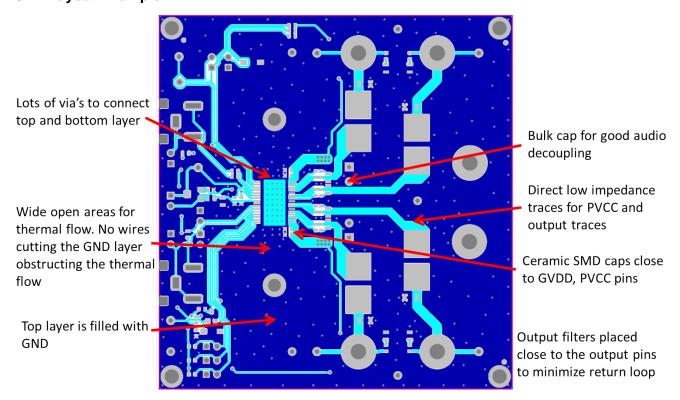

The TPA3116D2 can be used with a small, inexpensive ferrite bead output filter for most applications. However, since the class-D switching edges are fast, it is necessary to take care when planning the layout of the printed circuit board. The following suggestions will help to meet EMC requirements.

- Decoupling capacitors The high-frequency decoupling capacitors should be placed as close to the PVCC and AVCC terminals as possible. Large (100 μF or greater) bulk power supply decoupling capacitors should be placed near the TPA3116D2 on the PVCC supplies. Local, high-frequency bypass capacitors should be placed as close to the PVCC pins as possible. These caps can be connected to the IC GND pad directly for an excellent ground connection. Consider adding a small, good quality low ESR ceramic capacitor between 220 pF and 1 nF and a larger mid-frequency cap of value between 100 nF and 1 μF also of good quality to the PVCC connections at each end of the chip.

- Keep the current loop from each of the outputs through the ferrite bead and the small filter cap and back to GND as small and tight as possible. The size of this current loop determines its effectiveness as an antenna.

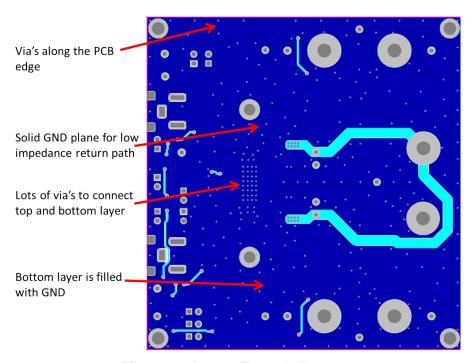

- Grounding The PVCC decoupling capacitors should connect to GND. All ground should be connected at the IC GND, which should be used as a central ground connection or star ground for the TPA3116D2.

- Output filter The ferrite EMI filter (see Figure 35) should be placed as close to the output terminals as

possible for the best EMI performance. The LC filter should be placed close to the outputs. The capacitors

used in both the ferrite and LC filters should be grounded.

Submit Documentation Feedback

Copyright © 2012–2017, Texas Instruments Incorporated

## **Layout Guidelines (continued)**

For an example layout, see the TPA3116D2 Evaluation Module (TPA3116D2EVM) User Guide (SLOU336). Both the EVM user manual and the thermal pad application reports, SLMA002 and SLMA004, are available on the TI Web site at http://www.ti.com.

## 10.2 Layout Example

Figure 40. Layout Example Top

Copyright © 2012–2017, Texas Instruments Incorporated

## **Layout Example (continued)**

Figure 41. Layout Example Bottom

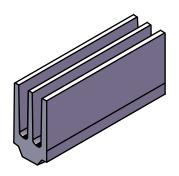

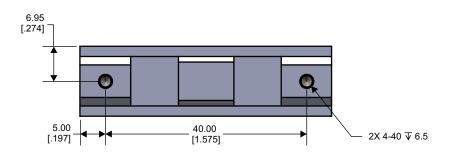

#### 10.3 Heat Sink Used on the EVM

The heat sink (part number ATS-TI 10 OP-521-C1-R1) used on the EVM is an 14x25x50 mm extruded aluminum heat sink with three fins (see drawing below). For additional information on the heat sink, go to www.qats.com.

Figure 42. EVM Heatsink

This size heat sink has shown to be sufficient for continuous output power. The crest factor of music and having airflow will lower the requirement for the heat sink size and smaller types can be used.

## 11 Device and Documentation Support

#### 11.1 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 7. Related Links

| PARTS     | PRODUCT FOLDER  | ORDER NOW  | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |  |

|-----------|-----------------|------------|---------------------|---------------------|---------------------|--|

| TPA3116D2 | Click here      | Click here | Click here          | Click here          | Click here          |  |

| TPA3118D2 | 18D2 Click here |            | Click here          | Click here          | Click here          |  |

| TPA3130D2 | Click here      | Click here | Click here          | Click here          | Click here          |  |

## 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates — go to the product folder for your device on ti.com. In the upper right-hand corner, click the *Alert me* button to register and receive a weekly digest of product information that has changed (if any). For change details, check the revision history of any revised document.

## 11.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 11.4 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## 11.6 Glossary

SLYZ022 — TI Glossarv.

This glossary lists and explains terms, acronyms, and definitions.

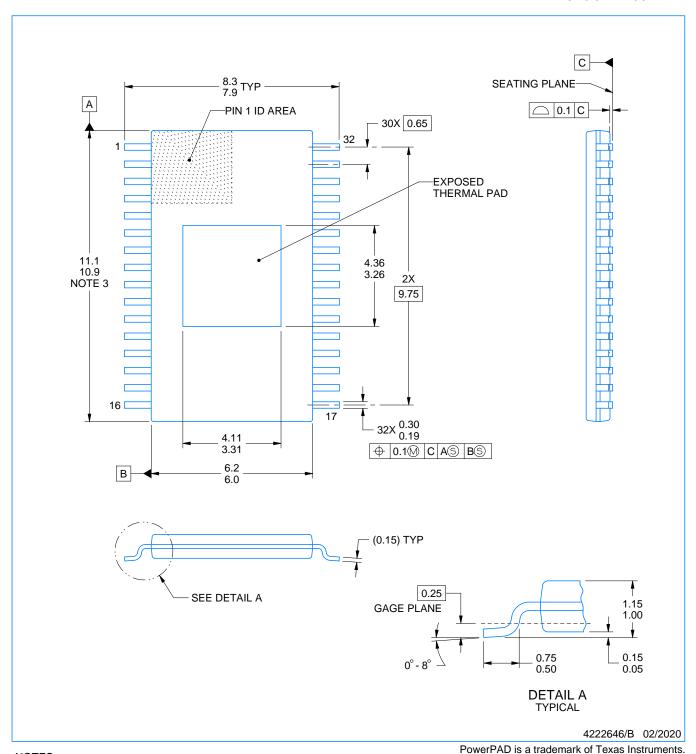

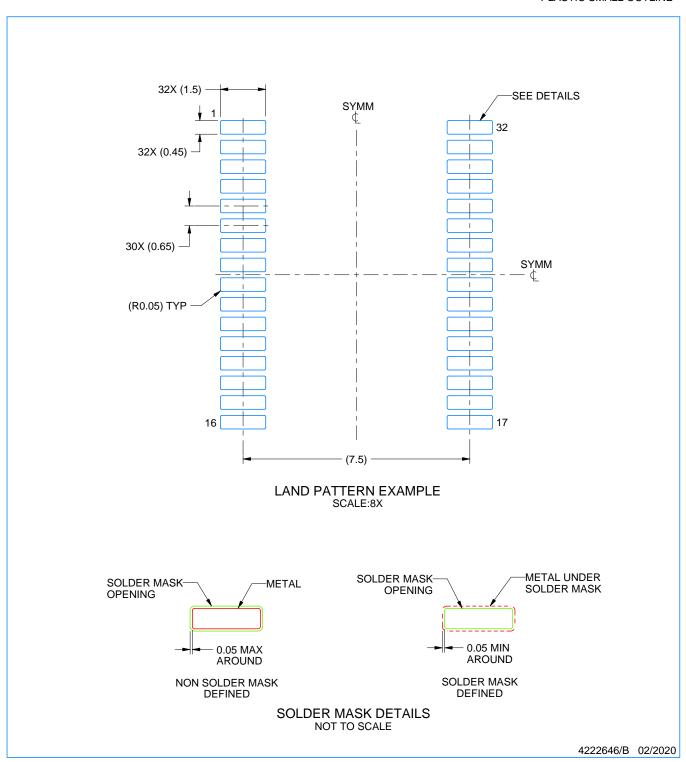

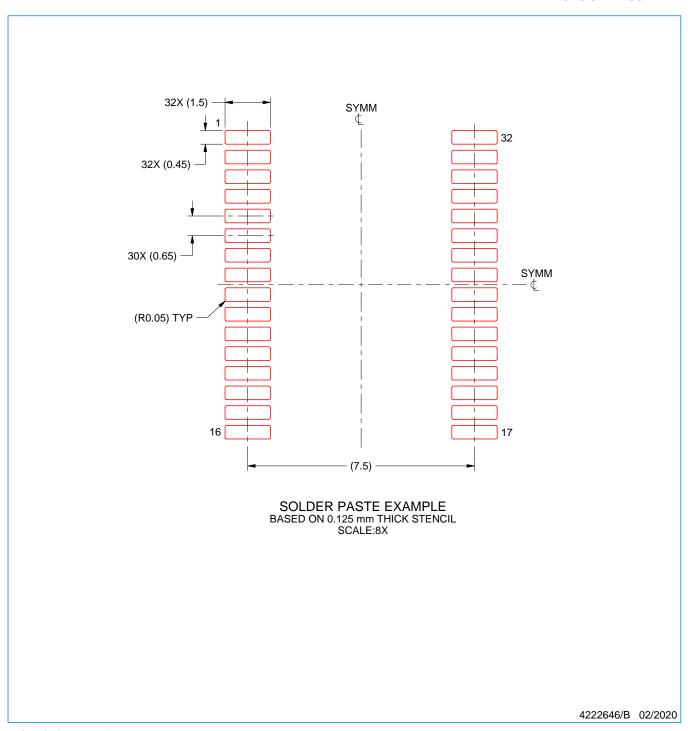

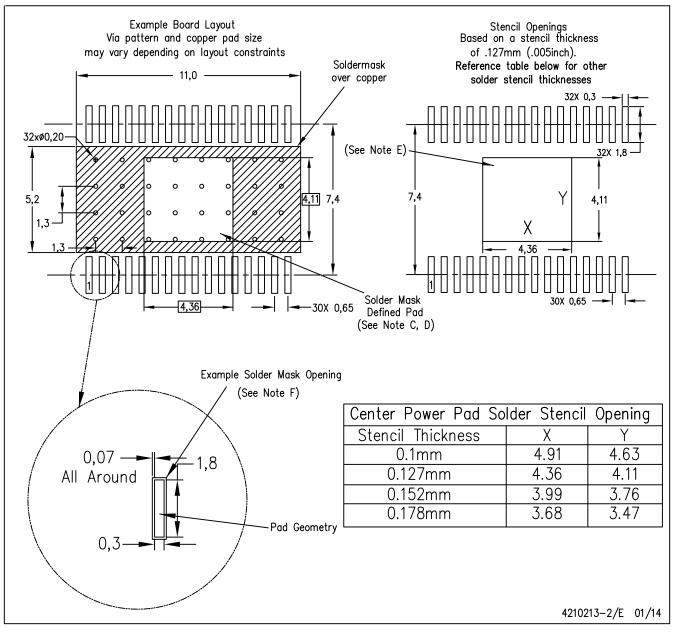

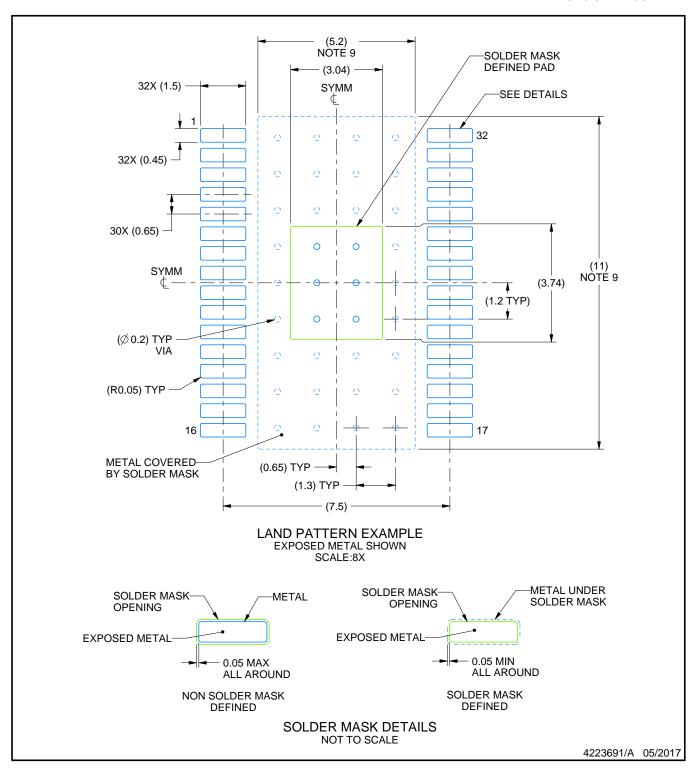

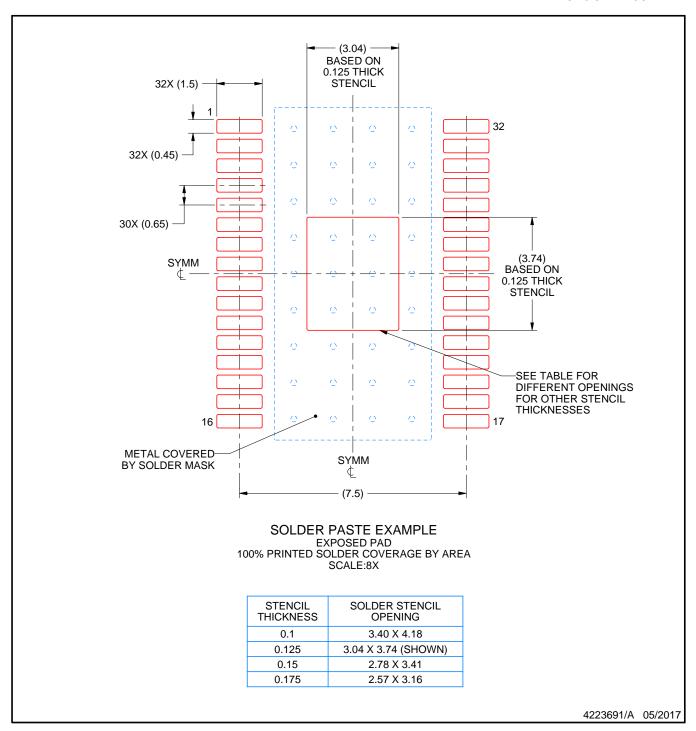

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: TPA3116D2 TPA3118D2 TPA3130D2

www.ti.com

23-May-2025

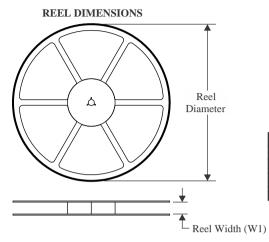

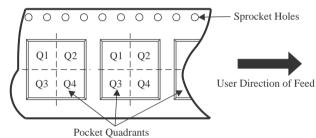

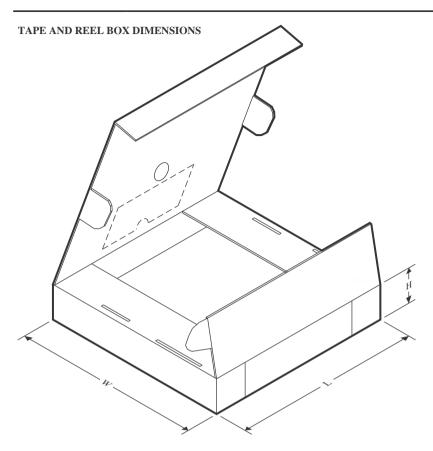

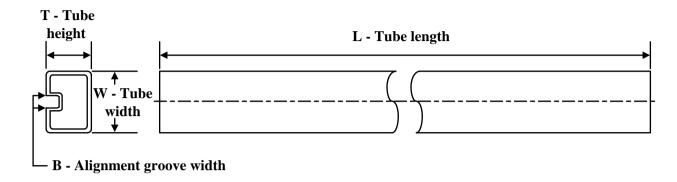

## **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins    | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)  |

|-----------------------|------------|---------------|-------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|-------------------|

| TPA3116D2DAD          | Active     | Production    | HTSSOP (DAD)   32 | 46   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA<br>3116<br>D2 |

| TPA3116D2DAD.A        | Active     | Production    | HTSSOP (DAD)   32 | 46   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA<br>3116<br>D2 |

| TPA3116D2DADR         | Active     | Production    | HTSSOP (DAD)   32 | 2000   LARGE T&R      | Yes             | NIPDAU   NIPDAU               | Level-3-260C-168 HR        | -40 to 85    | TPA<br>3116<br>D2 |

| TPA3116D2DADR.A       | Active     | Production    | HTSSOP (DAD)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA<br>3116<br>D2 |

| TPA3118D2DAP          | Active     | Production    | HTSSOP (DAP)   32 | 46   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3118           |

| TPA3118D2DAP.A        | Active     | Production    | HTSSOP (DAP)   32 | 46   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3118           |

| TPA3118D2DAPG4.A      | Active     | Production    | HTSSOP (DAP)   32 | 46   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3118           |

| TPA3118D2DAPR         | Active     | Production    | HTSSOP (DAP)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3118           |

| TPA3118D2DAPR.A       | Active     | Production    | HTSSOP (DAP)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3118           |

| TPA3130D2DAP          | Active     | Production    | HTSSOP (DAP)   32 | 46   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3130           |

| TPA3130D2DAP.A        | Active     | Production    | HTSSOP (DAP)   32 | 46   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3130           |

| TPA3130D2DAPR         | Active     | Production    | HTSSOP (DAP)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3130           |

| TPA3130D2DAPR.A       | Active     | Production    | HTSSOP (DAP)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3130           |

| TPA3130D2DAPRG4.A     | Active     | Production    | HTSSOP (DAP)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TPA3130           |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

## PACKAGE OPTION ADDENDUM