**TPS23755** JAJSGY5B - DECEMBER 2018 - REVISED NOVEMBER 2020

## TPS23755 フォトカプラなしのフライバック DC/DC コントロー ラ搭載 IEEE 802.3at PoE PD

# 1 特長

- タイプ 1 PoE 用の包括的な IEEE 802.3at PD ソリ ューション

- Ethernet Alliance (EA) ロゴ認証設計を利用可能

- 堅牢な 100V、0.36Ω (標準値) ホットスワップ **MOSFET**

- プログラム可能な分類レベル

- PWM コントローラと 0.77Ω (標準値) 150V パワー MOSFET を内蔵

- PSR 付きフライバック・コントローラ

- 2次側ダイオード整流器により CCM 動作を サポート

- ±3% (標準値、12V 出力) の負荷レギュレー ション (5%~100%の範囲)

- ローサイド・スイッチ降圧トポロジをサポート

- 同期可能な可変スイッチング周波数

- 高度なスタートアップ

- プログラム可能なスルーレートと周波数ディザ リングにより EMI 低減を強化

- スムーズな遷移で2次側アダプタを優先制御

- 接合部温度範囲:-40℃~125℃

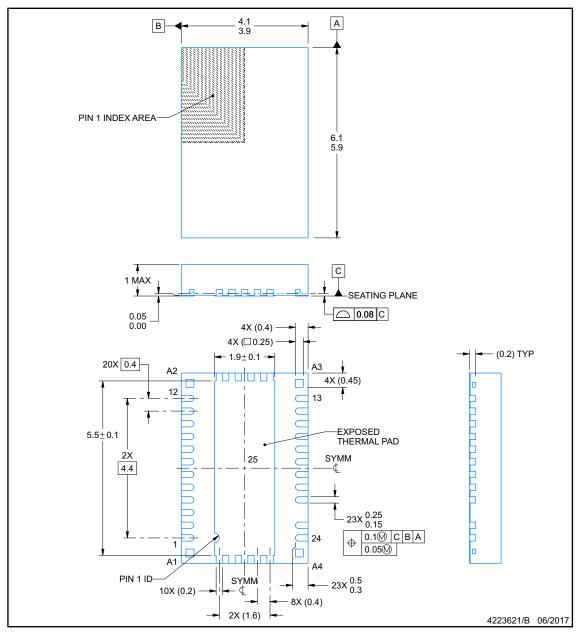

- 小型の 6mm×4mm VSON パッケージ

## 2 アプリケーション

- IEEE 802.3at 準拠の受電機器

- セキュリティ・カメラ

- IP 電話

- アクセス・ポイント

# 3 概要

TPS23755 は、Power over Ethernet (PoE) 受電機器 (PD) インターフェイス、150V スイッチング・パワー FET、およびフライバック・トポロジ用に最適化され た電流モード DC/DC コントローラを組み合わせたも のです。1 次側レギュレーション (PSR)、スペクトラ ム拡散周波数ディザリング (SSFD)、高度なスタート アップなどの機能を備え高度に統合された TPS23755 は小型の機器に最適なソリューションです。PoE の 実装は、13W、タイプ 1 の PD として IEEE 802.3at 規格に対応しています。

DC/DC コントローラの PSR 機能は、補助巻線か らの帰還により出力電圧を制御するため、外部シャン ト・レギュレータおよびフォトカプラは不要です。2 次側ダイオード整流器を使った動作 (通常 12V 以上 の出力) 用に最適化されています。通常、コンバータ はスイッチング周波数 250kHz 時に連続導通モード (CCM) で動作します。

SFFD およびスルーレート制御により、EMI フィル タのサイズとコストを最小限に抑えることができ、高 度なスタートアップにより、コンバータの起動および ヒカップ設計を簡素化すると同時に、使用するバイア ス・コンデンサを最小限にできます。

2次補助電源検出機能により、効率または熱的性能を 犠牲にすることなく PoE 入力電力との間でスムーズ な遷移を確保しながら、2次側電源アダプタを優先し ます。

この DC/DC コントローラは内部ソフトスタート、ス ロープ補償、ブランキング機能を備えています。非絶 縁用途の場合、TPS23755 は降圧トポロジもサポート しています。

# 製品情報(1)

| 部品番号     | パッケージ     | 本体サイズ (公称)      |

|----------|-----------|-----------------|

| TPS23755 | VSON (24) | 6.00mm × 4.00mm |

利用可能なすべてのパッケージについては、このデータシー トの末尾にある注文情報を参照してください。

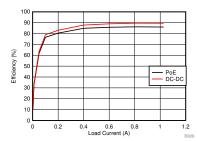

効率と負荷電流との関係、12V 出力

# **Table of Contents**

|                                       | 22<br>30 |

|---------------------------------------|----------|

| 1 8 Application and Implementation    |          |

|                                       |          |

| 2 0.1 Application intornation         | υſ       |

| 3 8.2 Typical Application             |          |

| 5 9 Power Supply Recommendations      | 38       |

| 5 10 Layout                           | 38       |

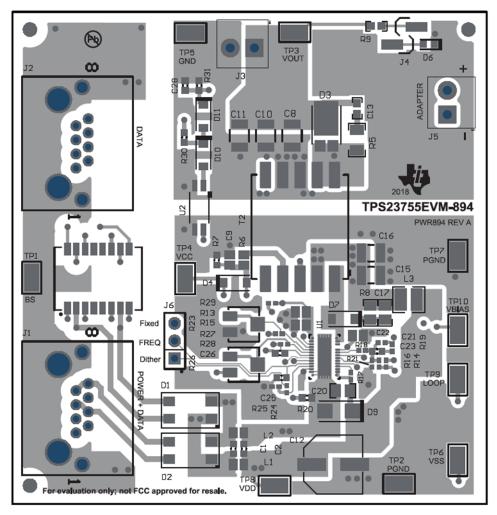

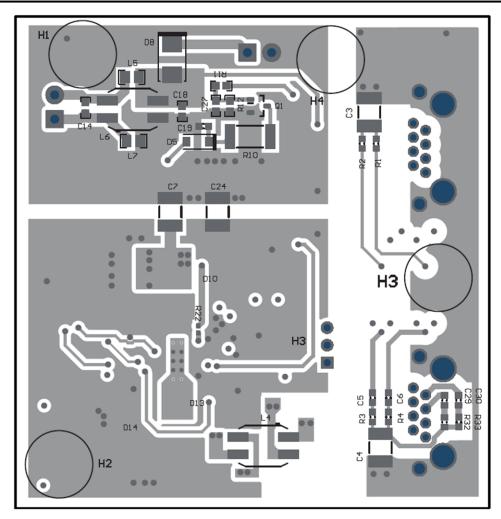

| 5 10.1 Layout Guidelines              |          |

| 6 10.2 Layout Example                 |          |

| 6 11 Device and Documentation Support | 41       |

| er 11.1 Related documentation         | 41       |

|                                       | 41       |

| ol9 11.3 Trademarks                   |          |

| 10 11.4 静電気放電に関する注意事項                 | 41       |

|                                       | 41       |

|                                       |          |

| 15 Information                        | 41       |

|                                       |          |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (January 2019) to Revision B (November 2020) | Page |

|----------------------------------------------------------------------|------|

| 文書全体にわたって表、図、相互参照の採番方法を更新                                            | 1    |

| • アプリケーション概略を更新 (Dvb を追加)                                            |      |

| Added, "and 6.2-V Zener diode"                                       |      |

| Added paragraph, "VB is the 5-V bias rail"                           | 17   |

| Updated 図 8-1 and 図 8-2 to include Dvb                               |      |

| Added section, "Bias Voltage, CVB and DVB"                           |      |

| Changes from Revision * (December 2018) to Revision A (January 2019) | Page |

| • デバイスのステータスを「量産データ」に変更                                              | 1    |

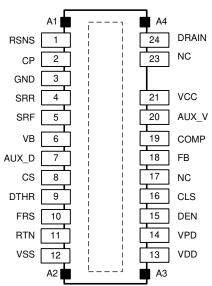

# **5 Pin Configuration and Functions**

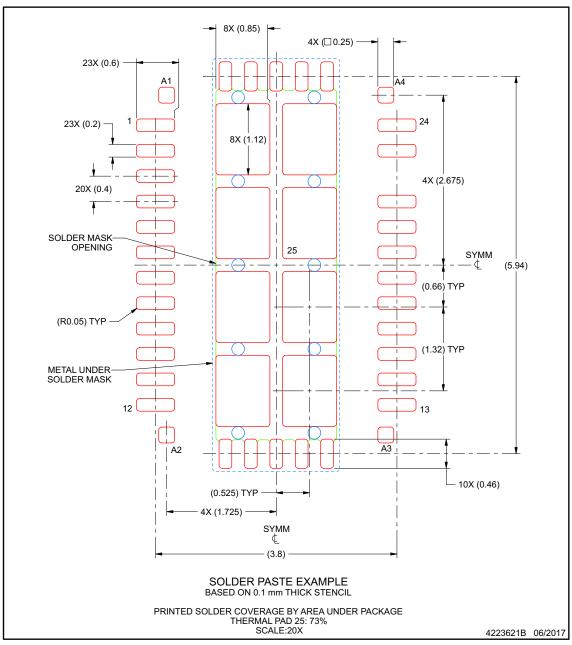

図 5-1. RJJ Package 24-Pin VSON Top View

表 5-1. Pin Functions

|     | PIN   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                  |

|-----|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME  | I/O | DESCRIPTION                                                                                                                                                                                                                                                  |

| 1   | RSNS  | 0   | Switching Power FET source connection. Connect to the external power current sense resistor.                                                                                                                                                                 |

| 2   | СР    | 0   | CP provides the clamp for the primary side regulation loop. Connect this pin to the lower end of the second primary side winding of the transformer.                                                                                                         |

| 3   | GND   | _   | Power ground used by the flyback power FET gate driver and CP. Connect to RTN.                                                                                                                                                                               |

| 4   | SRR   | 1   | Switching FET Gate sinking current input, used for EMI control. Connect a resistance from SRR to GND to control the Vds rate of rise.                                                                                                                        |

| 5   | SRF   | 1   | Switching FET Gate sourcing current input, used for EMI control. Connect a resistance from SRF to VB to control the Vds rate of fall.                                                                                                                        |

| 6   | VB    | 0   | 5-V bias rail for the switching FET gate driver circuit. For internal use only. Bypass with a 0.1-μF ceramic capacitor and 6.2-V Zener diode to GND pin.                                                                                                     |

| 7   | AUX_D | ı   | Auxiliary supply detect, internally pulled-up to approximately 5 V. Pull this pin low, typically through an optocoupler from the secondary side, to step down the output voltage of the DC-DC converter when a secondary side auxiliary supply is connected. |

| 8   | CS    | I   | DC-DC controller current sense input. Connect directly to the external power current sense resistor.                                                                                                                                                         |

| 9   | DTHR  | 0   | Used for spread spectrum frequency dithering. Connect a capacitor from DTHR to RTN and a resistor from DTHR to FRS. If dithering is not used, short DTHR to VB pin.                                                                                          |

| 10  | FRS   | I/O | This pin controls the switching frequency of the DC-DC converter. Tie a resistor from this pin to RTN to set the frequency.                                                                                                                                  |

| 11  | RTN   | _   | RTN is the output of the PoE hotswap and the reference ground for the DC-DC controller.                                                                                                                                                                      |

| 12  | VSS   | _   | Negative power rail derived from the PoE source.                                                                                                                                                                                                             |

| 13  | VDD   | _   | Source of DC-DC converter start-up current. Connect to VPD for most applications.                                                                                                                                                                            |

| 14  | VPD   | _   | Positive input power rail for PoE interface circuit. Derived from the PoE source. Bypass with a 0.1 µF to VSS and protect with a TVS.                                                                                                                        |

| 15  | DEN   | I/O | Connect a 24.9-k $\Omega$ resistor from DEN to VPD to provide the PoE detection signature. Pulling this pin to VSS during powered operation causes the internal hotswap MOSFET to turn off.                                                                  |

| 16  | CLS   | 0   | Connect a resistor from CLS to VSS to program the classification current.                                                                                                                                                                                    |

| 17  | NC    | _   | No connect pin. Leave open.                                                                                                                                                                                                                                  |

| 18  | FB    | 1   | Converter error amplifier inverting (feedback) input. It is typically driven by a voltage divider from the auxiliary winding. Also connect to the COMP compensation network.                                                                                 |

# 表 5-1. Pin Functions (continued)

|       | PIN     | I/O | DESCRIPTION                                                                                                                                                                                                         |

|-------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.   | NAME    | 1/0 | DESCRIPTION                                                                                                                                                                                                         |

| 19    | COMP    | 0   | Compensation output of the DC-DC convertor error amplifier. Connect the compensation networks from this pin to the FB pin to compensate the converter.                                                              |

| 20    | AUX_V   | 0   | AUX_V works with AUX_D to step down the output voltage setting of the DC-DC converter when an auxiliary supply is detected. Typically connected to FB pin through a resistor which defines the new voltage setting. |

| 21    | VCC     | I/O | DC/DC converter bias voltage. The internal startup current source and converter bias winding output power this pin. Connect a 1-µF minimum ceramic capacitor to RTN.                                                |

| 23    | NC      | _   | No connect pin. Leave open.                                                                                                                                                                                         |

| 24    | DRAIN   | 0   | Drain connection to the internal switching power MOSFET of the DC/DC controller.                                                                                                                                    |

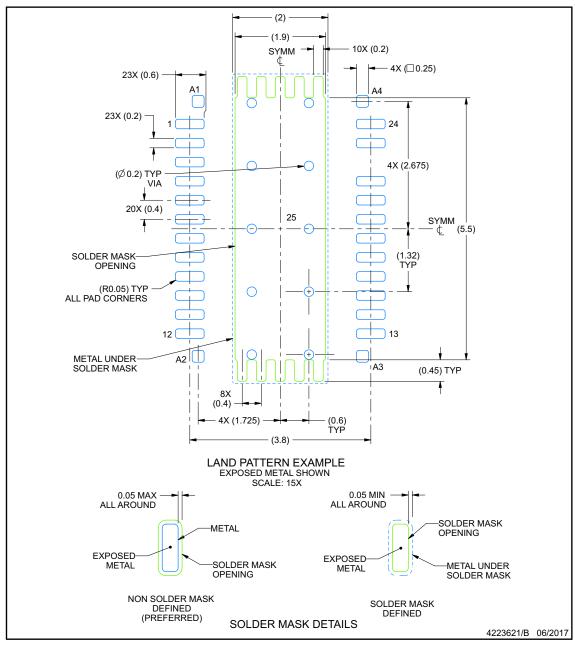

| -     | PAD     | _   | The exposed thermal pad must be connected to VSS. A large fill area is required to assist in heat dissipation.                                                                                                      |

| A1-A4 | ANCHORS | _   | Should be soldered to PCB for mechanical performance. These pins are not connected internally.                                                                                                                      |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

Voltage are with respect to  $V_{VSS}$  (unless otherwise noted)<sup>(1)</sup>

|                       | ,                                                                                                                                                                 | MIN                               | MAX       | UNIT   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|--------|

|                       | VDD, VPD, DEN, GND, RTN <sup>(2)</sup>                                                                                                                            | -0.3                              | 100       |        |

| Input voltage         | VDD to RTN                                                                                                                                                        | -0.3                              | 100       | V      |

| Input voitage         | AUX_D, FB, CS, all to RTN                                                                                                                                         | -0.3                              | 6.5       | V      |

|                       | SRF to GND                                                                                                                                                        | -0.3                              | 6.5       |        |

|                       | CLS <sup>(3)</sup>                                                                                                                                                | -0.3                              | 6.5       |        |

| Voltage               | FRS <sup>(3)</sup> , COMP <sup>(3)</sup> , VB <sup>(3)</sup> , SRR <sup>(3)</sup> , DTHR <sup>(3)</sup> , RSNS <sup>(3)</sup> , AUX_V <sup>(3)</sup> , all to RTN | -0.3                              | 6.5       |        |

|                       | VCC to RTN                                                                                                                                                        | -0.3                              | 19        | V      |

|                       | DRAIN to GND                                                                                                                                                      | -0.3                              | 150       |        |

|                       | CP to GND                                                                                                                                                         | -0.3                              | 60        |        |

|                       | GND to RTN                                                                                                                                                        | -0.3                              | 0.3       |        |

|                       | VB, VCC                                                                                                                                                           | Internally limited 35             |           |        |

| Sourcing current      | CLS                                                                                                                                                               |                                   |           | mA     |

|                       | COMP                                                                                                                                                              | Internally limited                |           |        |

|                       | RTN                                                                                                                                                               | Internally limited                |           |        |

| Sinking current       | DEN                                                                                                                                                               |                                   |           | mA     |

| Siriking current      | AUX_V                                                                                                                                                             |                                   | 5         | - IIIA |

|                       | COMP                                                                                                                                                              | Internally limited                |           |        |

|                       | Switching DRAIN peak current limit                                                                                                                                |                                   | 2         |        |

| I <sub>DRAIN</sub>    | Switching DRAIN peak current limit, Buck topology with 16% duty-cycle                                                                                             | nit, Buck topology with 16% duty- |           | А      |

| Peak sourcing current | СР                                                                                                                                                                |                                   | 1.5       | А      |

| T <sub>J(max)</sub>   | Maximum junction temperature                                                                                                                                      | Internall                         | y Limited | °C     |

| T <sub>stg</sub>      | Storage temperature                                                                                                                                               | -65                               | 150       | °C     |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                            |                                                |                                                                                | VALUE  | UNIT         |

|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------|--------|--------------|

|                                            |                                                | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000  |              |

| V <sub>(ESD)</sub> Electrostatic discharge | Electrostatic discharge                        | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500   | \ \ <u>\</u> |

|                                            | IEC 61000-4-2 contact discharge <sup>(3)</sup> | ±8000                                                                          | \ \ \  |              |

|                                            |                                                | IEC 61000-4-2 air-gap discharge <sup>(3)</sup>                                 | ±15000 |              |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

Copyright © 2021 Texas Instruments Incorporated

<sup>(2)</sup>  $I_{RTN} = 0$  for  $V_{RTN} > 80$  V.

<sup>(3)</sup> Do not apply voltage to these pins.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> ESD per EN61000-4-2, applied between RJ-45 and output ground of the TPS23755EVM-894 evaluation module. These were the test levels, not the failure threshold.

# **6.3 Recommended Operating Conditions**

Voltage with respect to V<sub>VSS</sub> (unless otherwise noted)

|                                               |                                                | MIN  | NOM | MAX | UNIT |

|-----------------------------------------------|------------------------------------------------|------|-----|-----|------|

|                                               | VDD, VPD, RTN, GND                             | 0    |     | 57  |      |

| Input voltage range                           | VCC to RTN                                     | 0    |     | 16  |      |

|                                               | AUX_D to RTN                                   | 0    |     | VB  | ٧    |

|                                               | CS to RTN                                      | 0    |     | 2   | V    |

|                                               | DRAIN to GND                                   | 0    |     | 125 |      |

|                                               | CP to GND                                      | 0    |     | 45  |      |

| Sinking current                               | RTN                                            |      |     | 350 | mA   |

| Peak current limit                            | DRAIN, RSNS                                    |      |     | 1.6 | Α    |

|                                               | DRAIN, RSNS, Buck topology with 16% duty-cycle |      |     | 2.5 | ^    |

| Peak sourcing current                         | СР                                             |      |     | 500 | mA   |

| Canacitanas                                   | VB <sup>(1)</sup>                              | 0.08 | 0.1 |     | E    |

| Capacitance                                   | vcc                                            | 0.8  | 1   |     | μF   |

|                                               | CLS <sup>(1)</sup>                             | 30   |     |     |      |

| Resistance                                    | SRF to VB                                      |      |     | 100 | Ω    |

|                                               | SRR to GND                                     |      |     | 15  |      |

| Synchronization pulse width input (when used) | FRS                                            | 35   |     |     | ns   |

| T <sub>J</sub>                                | Operating junction temperature                 | -40  |     | 125 | °C   |

<sup>(1)</sup> Voltage should not be externally applied to this pin.

# **6.4 Thermal Information**

|                       |                                              | TPS23755   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RJJ (VSON) | UNIT |

|                       |                                              | 24 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 34.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.5       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 14.5       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 6.4        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 14.5       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.4        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Product Folder Links: TPS23755

## 6.5 Electrical Characteristics: DC-DC Controller Section

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 24.9 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ; CLS, AUX\_V, RSNS and DRAIN open; CS, AUX\_D, and GND connected to RTN; SRR connected to GND; SRF, FB and DTHR connected to VB;  $C_{VB}$  = 0.1  $\mu$ F;  $C_{CC}$  = 1  $\mu$ F; 8.5 V  $\leq$   $V_{VCC} \leq$  16 V;  $-40^{\circ}$ C  $\leq$   $T_{J} \leq$  125°C. Positive currents are into pins unless otherwise noted. Typical values are at 25°C.  $T_{VVSS}$  =  $V_{RTN}$  and  $V_{CND}$  or  $T_{VVSS}$  =  $T_{VRD}$  and  $T_{VCD}$  and  $T_{CND}$  unless otherwise noted.

|                    | PARAMETER                              | TEST CONDITIONS                                                                               | MIN   | TYP                  | MAX   | UNIT |

|--------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|-------|----------------------|-------|------|

| DC-DC SL           | JPPLY (VCC)                            |                                                                                               |       |                      |       |      |

| V <sub>CUVR</sub>  |                                        | V <sub>VCC</sub> rising                                                                       | 8     | 8.25                 | 8.6   | V    |

| V <sub>CUVF</sub>  | Undervoltage lockout                   | V <sub>VCC</sub> falling                                                                      | 5.85  | 6.1                  | 6.25  | V    |

| V <sub>CUVH</sub>  |                                        | Hysteresis <sup>(1)</sup>                                                                     | 2     | 2.15                 | 2.5   | V    |

| I <sub>RUN</sub>   | Operating current, converter switching | $V_{VCC}$ = 10 V, $V_{FB}$ = $V_{RTN}$ = $V_{RSNS}$ , DRAIN with 2-k $\Omega$ pull up to 95 V |       | 2.0                  | 2.35  | mA   |

|                    |                                        | V <sub>DD</sub> = 10.2 V, V <sub>VCC</sub> (0) = 0 V                                          | 0.5   | 1.0                  | 2.5   | ms   |

| t <sub>ST</sub>    | Start-up time, $C_{CC} = 1 \mu F$      | V <sub>DD</sub> = 35 V, V <sub>VCC</sub> (0) = 0 V                                            | 0.5   | 0.80                 | 1.5   | ms   |

| V <sub>VC_ST</sub> | VCC startup voltage                    | Measure V <sub>VCC</sub> during startup, I <sub>VCC</sub> = 0 mA                              | 11    | 13                   | 15.5  | V    |

| DC-DC TII          | MING (FRS)                             |                                                                                               |       |                      | l     |      |

| f <sub>SW</sub>    | Switching frequency                    | $V_{FB} = V_{RSNS} = V_{RTN}$ , Measure at DRAIN                                              | 223   | 248                  | 273   | kHz  |

| D <sub>MAX</sub>   | Duty cycle                             | $V_{FB} = V_{RSNS} = V_{RTN}$ , Measure at DRAIN                                              | 75%   | 77.5%                | 80%   |      |

| V <sub>SYNC</sub>  | Synchronization                        | Input threshold                                                                               | 2     | 2.2                  | 2.4   | V    |

|                    | ICY DITHERING RAMP GENERATOR           | (DTHR)                                                                                        |       |                      | -     |      |

|                    | 0, , , , , , ,                         | 0.51/ .1/                                                                                     |       | 3 x I <sub>FRS</sub> |       | μA   |

| I <sub>DTRCH</sub> | Charging (sourcing) current            | 0.5 V < V <sub>DTHR</sub> < 1.38 V                                                            | 47.2  | 49.6                 | 52.1  | μA   |

|                    | B: 1 : (:1: )                          | 2011                                                                                          |       | 3 x I <sub>FRS</sub> |       | μA   |

| I <sub>DTRDC</sub> | Discharging (sinking) current          | 0.6 V < V <sub>DTHR</sub> < 1.5 V                                                             | 47.2  | 49.6                 | 52.1  | μA   |

| V <sub>DTUT</sub>  | Dithering upper threshold              | V <sub>DTHR</sub> rising until I <sub>DTHR</sub> > 0                                          | 1.41  | 1.513                | 1.60  | V    |

| V <sub>DTLT</sub>  | Dithering lower threshold              | V <sub>DTHR</sub> falling until I <sub>DTHR</sub> < 0                                         | 0.43  | 0.487                | 0.54  | V    |

| VDTPP              | Dithering pk-pk amplitude              |                                                                                               | 1.005 | 1.026                | 1.046 | V    |

| ERROR A            | MPLIFIER (FB, COMP)                    | -                                                                                             |       |                      |       |      |

| V <sub>REFC</sub>  | Feedback regulation voltage            |                                                                                               | 1.723 | 1.75                 | 1.777 | V    |

| I <sub>FB_LK</sub> | FB leakage current (source or sink)    | V <sub>FB-RTN</sub> = 1.75 V                                                                  |       |                      | 0.5   | μA   |

| G <sub>BW</sub>    | Small signal unity gain bandwidth      |                                                                                               | 0.9   | 1.2                  |       | MHz  |

| A <sub>OL</sub>    | Open loop voltage gain                 |                                                                                               | 70    | 90                   |       | dB   |

| V <sub>ZDC</sub>   | 0% duty-cycle threshold                | V <sub>COMP</sub> falling until DRAIN switching stops                                         | 1.35  | 1.5                  | 1.65  | V    |

| I <sub>COMPH</sub> | COMP source current                    | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>COMP</sub> = 3 V                                  | 1     |                      |       | mA   |

| I <sub>COMPL</sub> | COMP sink current                      | V <sub>FB</sub> = V <sub>VB</sub> , V <sub>COMP</sub> = 1.25 V                                | 2.1   | 6                    |       | mA   |

| V <sub>COMPH</sub> | COMP high voltage                      | $V_{FB}$ = $V_{VB}$ , 15 k $\Omega$ from COMP to RTN                                          | 4     |                      | 5     | V    |

| V <sub>COMPL</sub> | COMP low voltage                       | $V_{FB} = V_{VB}$ , 15 k $\Omega$ from COMP to VB                                             |       |                      | 1.1   | V    |

|                    | COMP to CS gain                        | $\Delta V_{CS} / \Delta V_{COMP}$ , 0 V < $V_{CS}$ < 0.5 V                                    | 0.475 | 0.5                  | 0.525 | V/V  |

| SOFT-STA           | ART                                    |                                                                                               |       |                      |       |      |

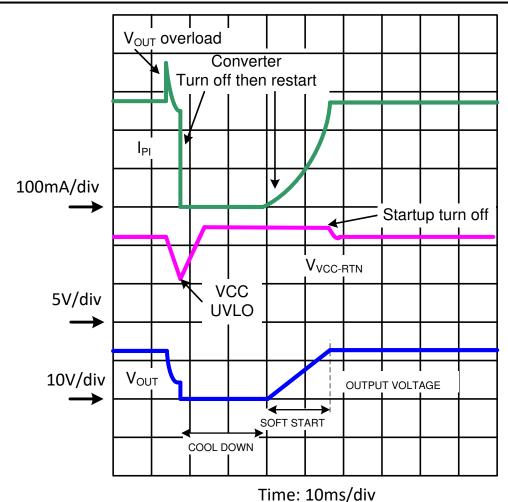

| t <sub>ss</sub>    | Soft-start period                      |                                                                                               | 8     | 16                   | 24    | ms   |

| t <sub>CD</sub>    | Cool-down period                       |                                                                                               | 15    | 20                   | 26    | ms   |

|                    | SENSE (CS)                             |                                                                                               |       |                      |       |      |

| V <sub>CSMAX</sub> | Maximum threshold voltage              | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>CS</sub> rising                                   | 0.5   | 0.55                 | 0.6   | V    |

# 6.5 Electrical Characteristics: DC-DC Controller Section (continued)

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 24.9 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ; CLS, AUX\_V, RSNS and DRAIN open; CS, AUX\_D, and GND connected to RTN; SRR connected to GND; SRF, FB and DTHR connected to VB;  $C_{VB}$  = 0.1  $\mu$ F;  $C_{CC}$  = 1  $\mu$ F; 8.5 V  $\leq$   $V_{VCC}$   $\leq$  16 V;  $-40^{\circ}$ C  $\leq$   $T_{J}$   $\leq$  125 $^{\circ}$ C. Positive currents are into pins unless otherwise noted. Typical values are at 25 $^{\circ}$ C. [ $V_{VSS}$  =  $V_{RTN}$  and  $V_{VPD}$  =  $V_{VDD}$ ] or [ $V_{VSS}$  =  $V_{RTN}$  =  $V_{VPD}$ ], all voltages referred to  $V_{RTN}$  and  $V_{GND}$  unless otherwise noted.

|                         | PARAMETER                             | TEST CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNIT |

|-------------------------|---------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>OFFDEL_ILM</sub> | Current limit turnoff delay           | V <sub>CS</sub> = 0.65 V                                                                  | 25   | 41   | 60   | 20   |

| t <sub>OFFDEL_PW</sub>  | PWM comparator turnoff delay          | V <sub>CS</sub> = 0.4 V                                                                   | 25   | 41   | 60   | ns   |

|                         | Blanking delay                        | In addition to t <sub>OFFDEL</sub>                                                        | 56.5 | 75   | 93.5 | ns   |

| V <sub>SLOPE</sub>      | Internal slope compensation voltage   | Peak voltage at maximum duty cycle, referred to CS                                        | 120  | 155  | 185  | mV   |

| I <sub>SL_EX</sub>      | Peak slope compensation current       | V <sub>FB</sub> = V <sub>RTN</sub> , I <sub>CS</sub> at maximum duty cycle (ac component) | 30   | 42   | 54   | μΑ   |

|                         | Bias current                          | DC component of CS current                                                                | -6.7 | -5   | -3.3 | μA   |

| SWITCHING               | POWER FET (DRAIN, RSNS)               |                                                                                           |      |      |      |      |

| BV <sub>DSS</sub>       | Power FET break-down voltage          |                                                                                           | 150  |      |      | V    |

| R <sub>DS(ON)</sub>     | Power FET on resistance               |                                                                                           |      | 0.77 | 1.28 | Ω    |

| V <sub>SD</sub>         | Source-to-drain diode forward voltage | I <sub>RSNS</sub> = 500 mA                                                                | 0.6  | 1    | 1.1  | V    |

| SECONDAI                | RY SIDE AUXILIARY POWER (AUX_I        | D, AUX_V)                                                                                 |      |      | 1    |      |

| V <sub>AUXEN</sub>      | ALIX Data and sold walks are          | V <sub>AUX_D</sub> rising                                                                 | 1.7  | 2    | 2.3  | V    |

| V <sub>AUXH</sub>       | AUX_D threshold voltage               | Hysteresis (1)                                                                            |      | 0.15 |      | V    |

| I <sub>pullup</sub>     | AUX_D pullup current                  |                                                                                           | 70   | 100  | 130  | μA   |

| V <sub>AVL</sub>        | AUX_V output low voltage              | $V_{AUX\_D}$ = $V_{VB}$ , 5 K $\Omega$ from AUX_V to VB                                   |      |      | 50   | mV   |

| THERMAL                 | SHUTDOWN                              |                                                                                           |      |      | '    |      |

|                         | Turnoff temperature                   |                                                                                           | 145  | 159  | 165  | °C   |

|                         | Hysteresis <sup>(2)</sup>             |                                                                                           |      | 13   |      | °C   |

<sup>(1)</sup> The hysteresis tolerance tracks the rising threshold for a given device.

Product Folder Links: TPS23755

<sup>(2)</sup> These parameters are provided for reference only, and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

### 6.6 Electrical Characteristics: PoE and Control

Unless otherwise noted,  $V_{VPD}$  = 48 V;  $R_{DEN}$  = 24.9 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ; CLS, AUX\_V, RSNS and DRAIN open; CS, AUX\_D, and GND connected to RTN; SRR connected to GND; SRF, FB and DTHR connected to VB;  $C_{VB}$  = 0.1  $\mu$ F;  $C_{CC}$  = 1  $\mu$ F;  $-40^{\circ}$ C  $\leq$   $T_{J}$   $\leq$  125 $^{\circ}$ C. Positive currents are into pins unless otherwise noted. Typical values are at 25 $^{\circ}$ C.

Unless otherwise noted,  $V_{VPD} = V_{VDD}$ ,  $V_{VCC} = V_{RTN}$ . All voltages referred to  $V_{VSS}$  unless otherwise noted.

|                      | PARAMETER                               | TEST CONDITIONS                                                                                              |                                                                         | MIN  | TYP  | MAX   | UNIT |

|----------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|-------|------|

| PD DETEC             | TION (DEN)                              |                                                                                                              |                                                                         |      |      |       |      |

|                      | Detection bias current                  | DEN open, V <sub>VPD</sub> = 10 V, Measure I <sub>VPD</sub> + I <sub>VDD</sub> + I <sub>DEN</sub>            | N + I <sub>RTN</sub>                                                    | 3.5  | 8.3  | 13.9  | μA   |

| I <sub>lkg</sub>     | DEN leakage current                     | V <sub>DEN</sub> = V <sub>VPD</sub> = 57 V, Measure I <sub>DEN</sub>                                         |                                                                         |      | 0.1  | 5     | μA   |

|                      |                                         | Measure I <sub>VPD</sub> + I <sub>VDD</sub> + I <sub>DEN</sub> + I <sub>RTN</sub> , V <sub>VPD</sub> = 1.4 V |                                                                         | 55.5 | 56.3 | 60    | μA   |

|                      | Detection current                       | Measure I <sub>VPD</sub> + I <sub>VDD</sub> + I <sub>DEN</sub> + I <sub>RTN</sub> , V <sub>VPD</sub> = 10 V  |                                                                         | 400  | 407  | 414.5 | μA   |

| V <sub>PD_DIS</sub>  | Hotswap disable threshold               |                                                                                                              |                                                                         | 3    | 4    | 5     | V    |

|                      | FICATION (CLS)                          |                                                                                                              |                                                                         | ı    |      |       |      |

|                      |                                         | R <sub>CLS</sub> = 649 Ω                                                                                     |                                                                         | 1.8  | 2.14 | 2.4   |      |

|                      | 01 15 11                                | R <sub>CLS</sub> = 121 Ω                                                                                     | 13 V ≤ V <sub>DD</sub> ≤ 21 V, Measure                                  | 9.9  | 10.6 | 11.3  |      |

| I <sub>CLS</sub>     | Classification current                  |                                                                                                              | <sub>VPD</sub> + I <sub>VDD</sub> + I <sub>DEN</sub> + I <sub>RTN</sub> | 17.6 | 18.6 | 19.4  | mA   |

|                      |                                         | R <sub>CLS</sub> = 45.3 Ω                                                                                    |                                                                         | 26.5 | 27.9 | 29.3  |      |

| V <sub>CL_ON</sub>   | Classification regulator lower          | Regulator turns on, V <sub>VPD</sub> rising                                                                  |                                                                         | 10.7 | 12.1 | 13    | V    |

| V <sub>CL_HYS</sub>  | threshold                               | Hysteresis <sup>(1)</sup>                                                                                    |                                                                         |      | 1.1  | 1.55  | V    |

| V <sub>CU_OFF</sub>  | Classification regulator upper          | Regulator turns off, V <sub>VPD</sub> rising                                                                 |                                                                         |      | 22   | 23    | V    |

| V <sub>CU_HYS</sub>  | threshold                               | Hysteresis <sup>(1)</sup>                                                                                    |                                                                         | 0.5  | 0.77 | 1     | V    |

| I <sub>lkg</sub>     | Leakage current                         | $V_{VPD}$ = 57 V, $V_{CLS}$ = 0 V, $V_{DEN}$ = $V_{VSS}$ , Measure $I_{CLS}$                                 | S                                                                       |      |      | 1     | μA   |

| RTN (PASS            | DEVICE)                                 |                                                                                                              |                                                                         |      | -    |       |      |

|                      | ON-resistance                           |                                                                                                              |                                                                         |      | 0.36 | 0.68  | Ω    |

|                      | Current limit                           | V <sub>RTN</sub> = 1.5 V, pulsed measurement                                                                 |                                                                         | 405  | 550  | 800   | mA   |

|                      | Inrush current limit                    | $V_{RTN}$ = 2 V, $V_{VPD}$ : 0 V $\rightarrow$ 48 V, pulsed measuremen                                       | t                                                                       | 100  | 140  | 220   | mA   |

|                      | Foldback voltage threshold              | V <sub>RTN</sub> rising                                                                                      |                                                                         | 11   | 12.3 | 13.6  | V    |

|                      | Foldback deglitch time                  | V <sub>RTN</sub> rising to when current limit changes to inrush o                                            | current limit                                                           | 150  | 387  | 600   | μs   |

| I <sub>lkg</sub>     | Leakage current                         | V <sub>VPD</sub> = V <sub>RTN</sub> = 100 V, V <sub>DEN</sub> = V <sub>VSS</sub>                             |                                                                         |      |      | 40    | μΑ   |

| PD INPUT             | SUPPLY (VPD, VDD)                       |                                                                                                              |                                                                         |      |      |       |      |

| UVLO_R               | I landomicito de la cica est three hold | V <sub>VPD</sub> rising                                                                                      |                                                                         | 34.7 | 35.5 | 36.7  | V    |

| UVLO_H               | Undervoltage lockout threshold          | Hysteresis (1)                                                                                               |                                                                         | 4.1  | 4.5  | 4.7   | V    |

|                      | Operating current                       | VCC open, 40 V ≤ V <sub>VPD</sub> = V <sub>VDD</sub> ≤ 57 V, Startup com                                     | pleted, Measure I <sub>VPD</sub> + I <sub>VDD</sub>                     |      | 300  | 580   |      |

| I <sub>VPD_VDD</sub> | Off-state current                       | RTN, GND and VCC open, V <sub>VPD</sub> = 30 V, Measure I <sub>VPD</sub>                                     |                                                                         |      |      | 330   | μA   |

| THERMAL              | SHUTDOWN                                |                                                                                                              |                                                                         |      |      |       |      |

|                      | Turnoff temperature                     |                                                                                                              |                                                                         | 145  | 159  | 165   | °C   |

|                      | Hysteresis <sup>(2)</sup>               |                                                                                                              |                                                                         |      | 13   |       | °C   |

<sup>(1)</sup> The hysteresis tolerance tracks the rising threshold for a given device.

<sup>(2)</sup> These parameters are provided for reference only.

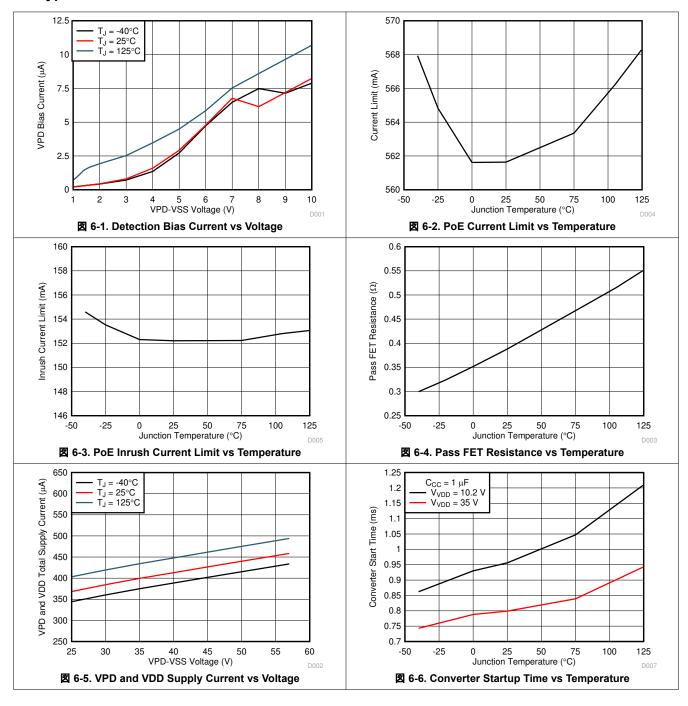

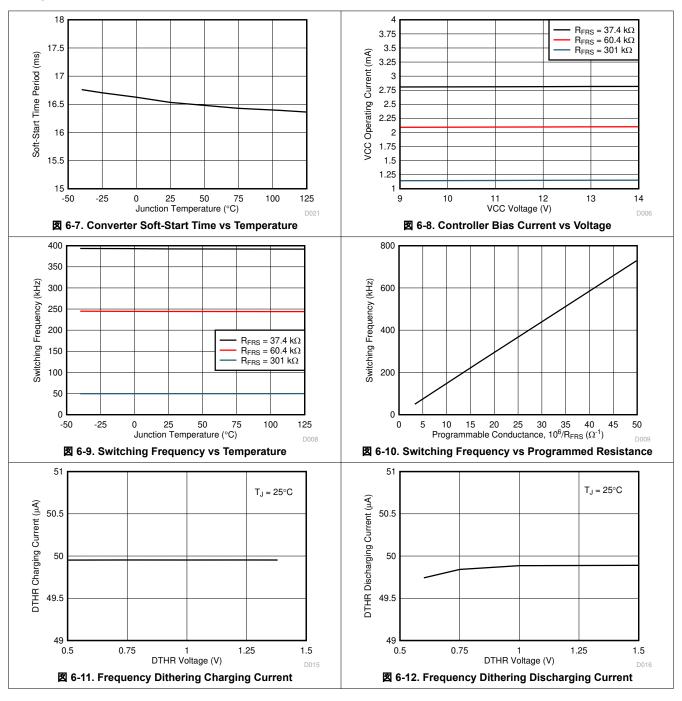

# 6.7 Typical Characteristics

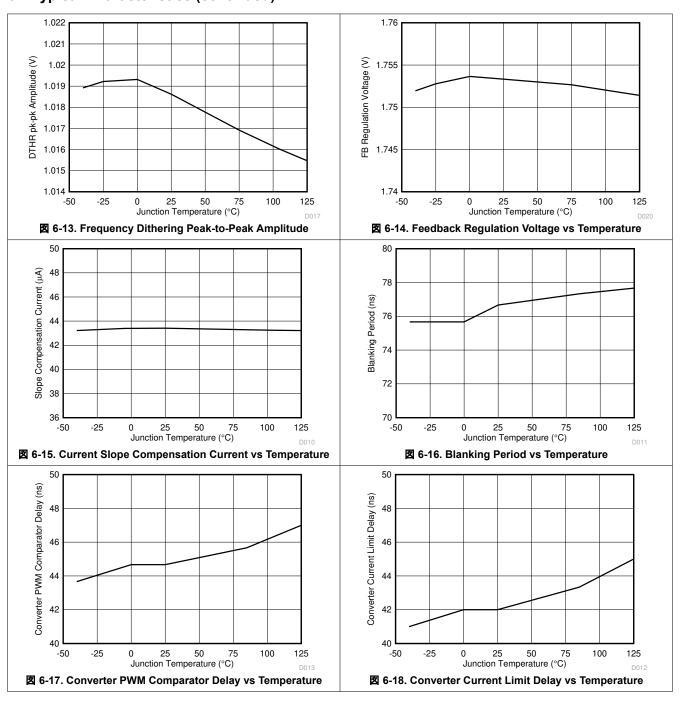

# **6.7 Typical Characteristics (continued)**

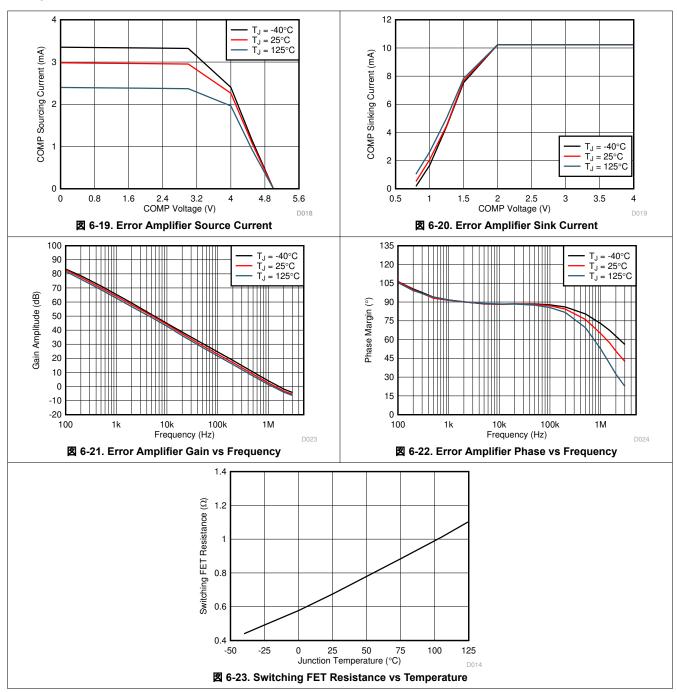

# **6.7 Typical Characteristics (continued)**

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# **6.7 Typical Characteristics (continued)**

# 7 Detailed Description

# 7.1 Overview

The TPS23755 device is a 24-pin integrated circuit that contains all of the features needed to implement an IEEE802.3at Type-1 powered device (PD), combined with a fully integrated 150-V switching power FET and a current-mode DC-DC controller optimized for flyback switching regulator designs using primary side control. The TPS23755 applies to single-output flyback converter applications where a secondary side diode rectifier is used.

Basic PoE PD functionality supported includes detection, hardware classification, and inrush current limit during startup. DC-DC converter features include startup function and current mode control operation. The TPS23755 device integrates a low  $0.36-\Omega$  internal switch to support Type-1 applications.

The TPS23755 features secondary auxiliary power detect (AUX\_D) capability, providing priority for a secondary side power adapter, while ensuring smooth transition (via AUX\_V) to and from the PoE power input.

The TPS23755 device contains several protection features such as f, current limit foldback, and a robust 100-V internal return switch.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

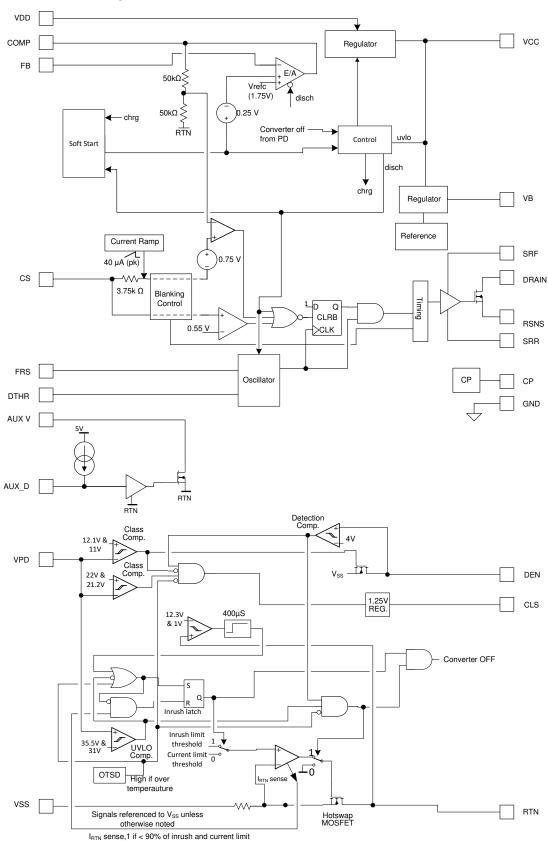

# 7.2 Functional Block Diagram

## 7.3 Feature Description

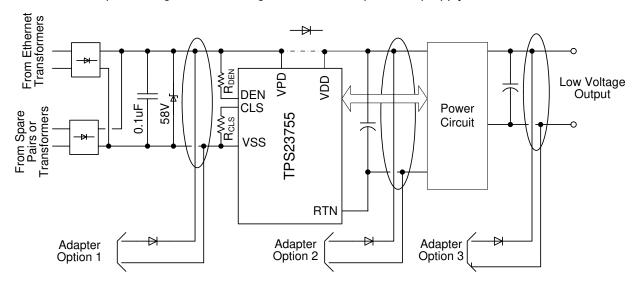

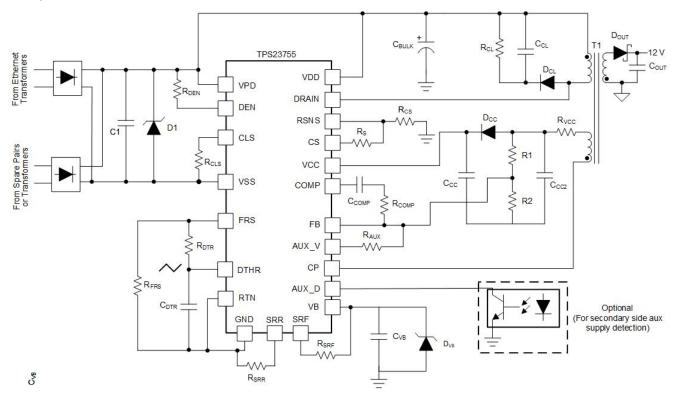

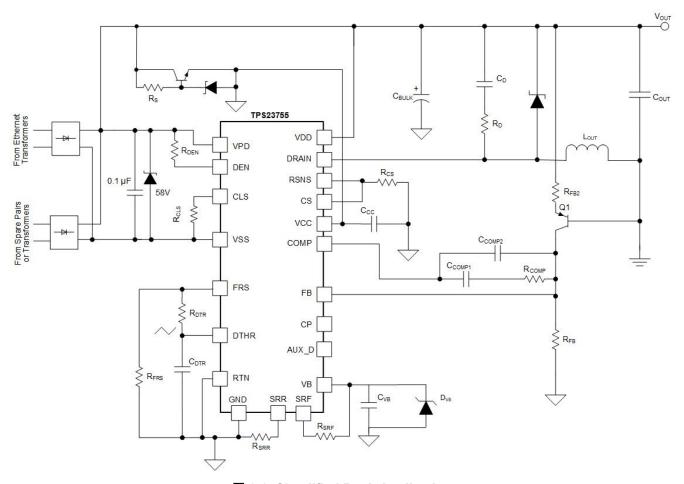

See  $\boxtimes$  8-1 for component reference designators (R<sub>CS</sub> for example ), and *Electrical Characteristics: DC-DC Controller Section* for values denoted by reference (V<sub>CSMAX</sub> for example). Electrical Characteristic values take precedence over any numerical values used in the following sections.

#### 7.3.1 CLS Classification

An external resistor ( $R_{CLS}$  in  $\boxtimes$  8-1) connected between the CLS pin and VSS provides a classification signature to the PSE. The controller places a voltage of approximately 1.25 V across the external resistor whenever the voltage differential between VPD and VSS lies from about 11 V to 22 V. The current drawn by this resistor, combined with the internal current drain of the controller and any leakage through the internal pass MOSFET, creates the classification current.  $\frac{1}{5}$  7-1 lists the external resistor values required for each of the PD power ranges defined by IEEE802.3at. The maximum average power drawn by the PD, plus the power supplied to the downstream load, should not exceed the maximum power indicated in Table 7-1. The TPS23755 supports class 0 – 3 power levels.

| CLASS | POWER AT PD PI |             | RESISTOR (Ω)  |  |  |  |

|-------|----------------|-------------|---------------|--|--|--|

|       | MINIMUM (W)    | MAXIMUM (W) | RESISTOR (12) |  |  |  |

| 0     | 0.44           | 12.95       | 649           |  |  |  |

| 1     | 0.44           | 3.84        | 121           |  |  |  |

| 2     | 3.84           | 6.49        | 68.1          |  |  |  |

| 3     | 6.49           | 12.95       | 45.3          |  |  |  |

表 7-1. Class Resistor Selection

#### 7.3.2 DEN Detection and Enable

DEN pin implements two separate functions. A resistor ( $R_{DEN}$  in  $\boxtimes$  8-1) connected between VPD and DEN generates a detection signature whenever the voltage differential between VPD and VSS lies from approximately 1.4 to 11 V. Beyond this range, the controller disconnects this resistor to save power. The IEEE 802.3at standard specifies a detection signature resistance,  $R_{DEN}$  from 23.75 k $\Omega$  to 26.25 k $\Omega$ , or 25 k $\Omega$  ± 5%. TI recommends a resistor of 24.9 k $\Omega$  ± 1% for  $R_{DEN}$ .

Pulling DEN to VSS during powered operation causes the internal hotswap MOSFET and class regulator to turn off. If the resistance connected between VDD and DEN is divided into two roughly equal portions, then the application circuit can disable the PD by grounding the tap point between the two resistances, while simultaneously spoiling the detection signature which prevents the PD from properly re-detecting.

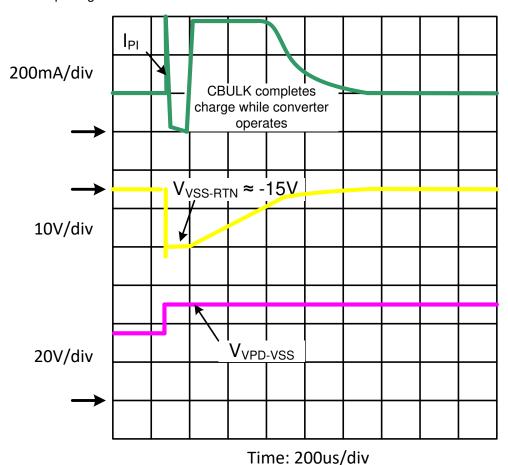

#### 7.3.3 Internal Pass MOSFET

RTN pin provides the negative power return path for the load. It is internally connected to the drain of the PoE hotswap MOSFET, and the DC-DC controller return. RTN must be treated as a local reference plane (ground plane) for the DC-DC controller and converter primary to maintain signal integrity.

Once  $V_{VPD}$  exceeds the UVLO threshold, the internal pass MOSFET pulls RTN to VSS. Inrush limiting prevents the RTN current from exceeding a nominal value of about 140 mA until the bulk capacitance ( $C_{BULK}$  in  $\boxtimes$  8-1) is fully charged. Inrush ends when the RTN current drops below about 125 mA. The RTN current is subsequently limited to about 0.45 A.

If RTN ever exceeds about 12.3 V for longer than 400 μs, then the PD returns to inrush limiting.

### 7.3.4 DC-DC Controller Features

The TPS23755 device DC-DC controller implements a typical current-mode control as shown in *Functional Block Diagram*. Features include oscillator, overcurrent and PWM comparators, current-sense blanker, soft start, gate driver and switching power FET. In addition, an internal current-compensation ramp generator, frequency synchronization logic, built-in frequency dithering functionality, thermal shutdown, and start-up current source with control are provided.

The TPS23755 is optimized for isolated converters, and it includes an internal error amplifier. The voltage feedback is from the bias winding. The COMP output of the error amplifier is directly fed to a 2:1 internal resistor divider and an offset of  $V_{ZDC}/2$  (approximately 0.75 V) which defines a current-demand control for the pulse width modulator (PWM). A  $V_{COMP}$  below  $V_{ZDC}$  stops converter switching, while voltages above ( $V_{ZDC} + 2 \times (V_{CSMAX} + V_{SLOPE})$ ) does not increase the requested peak current in the switching MOSFET.

The internal start-up current source and control logic implement a bootstrap-type startup. The startup current source charges  $C_{CC}$  from VDD and maintain its voltage when the converter is disabled or during the soft-start period, while operational power must come from a converter (bias winding) output.

The bootstrap source provides reliable start-up from widely varying input voltages, and eliminates the continual power loss of external resistors.

The peak current limit does not have duty cycle dependency unless  $R_S$  is used as shown in  $\boxtimes$  7-2 to increase slope compensation. This makes it easier to design the current limit to a fixed value.

The DC-DC controller has an OTSD that can be triggered by heat sources including the power switching FET and GATE driver. The controller OTSD turns off the switching FET and resets the soft-start generator.

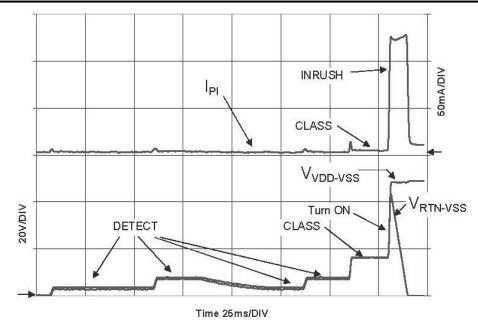

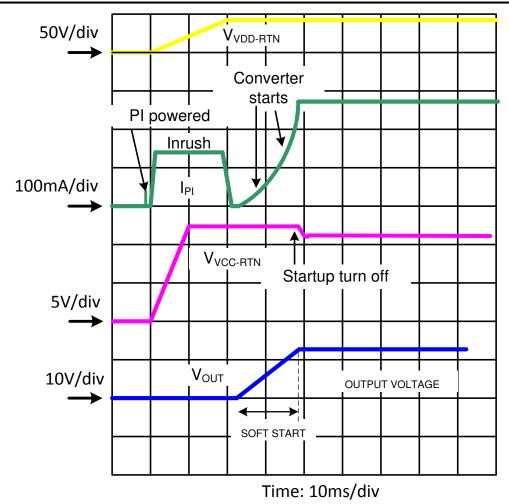

## 7.3.4.1 VCC, VB and Advanced PWM Startup

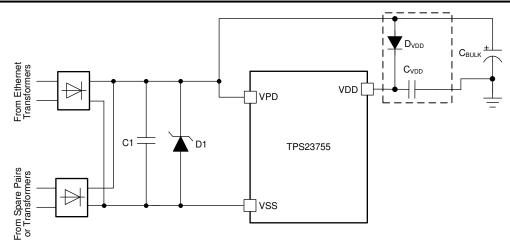

The VCC pin connects to the auxiliary bias supply for the DC-DC controller. The switching MOSFET gate driver draws current directly from the VB pin, which is the output of an internal 5-V regulator fed from VCC. A startup current source from VDD to VCC implements the converter bootstrap startup. VCC must receive power from an auxiliary source, such as an auxiliary winding on the flyback transformer, to sustain normal operation after startup.

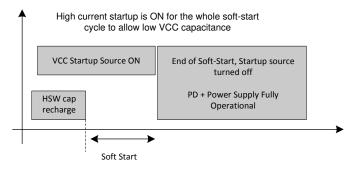

The startup current source is turned on during the inrush phase, charging  $C_{CC}$  and maintaining its voltage, and it is turned off only after the DC-DC soft-start cycle has been completed, which occurs when the DC-DC converter has ramped up its output voltage, as shown in  $\boxed{2}$  7-1. Internal loading on VCC and VB is initially minimal while  $C_{CC}$  charges, to allow the converter to start. Due to the high current capability of the startup source, the recommended capacitance at VCC is relatively small, typically 1  $\mu$ F in most applications.

VB is the 5-V bias rail for the switching FET gate driver circuit. A 0.1-µF bypass capacitor between VB and RTN is required. Additionally, a 6.2-V Zener diode from VB to RTN is required.

Once  $V_{VCC}$  falls below its UVLO threshold, the converter shuts off and the startup current source is turned back on, initiating a new PWM startup cycle.

図 7-1. Advanced Startup

# 7.3.4.2 CS, Current Slope Compensation and Blanking

The current-sense input for the DC-DC converter should be connected to the high side of the current-sense resistor of the switching MOSFET. The current-limit threshold,  $V_{CSMAX}$ , defines the voltage on CS above which the switching FET ON-time is terminated regardless of the voltage on COMP output.

Routing between the current-sense resistor and the CS pin must be short to minimize cross-talk from noisy traces such as DRAIN and CP, and to a lower degree to SRR and SRF.

Current-mode control requires addition of a compensation ramp to the sensed inductor (flyback transformer) current for stability at duty cycles near and over 50%. The TPS23755 has a maximum duty cycle limit of 78.5%,

Copyright © 2021 Texas Instruments Incorporated

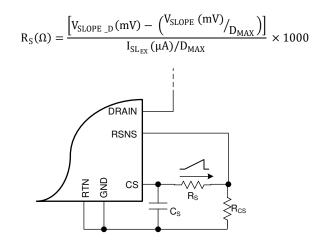

permitting the design of wide input-range flyback converters with a lower voltage stress on the output rectifiers. While the maximum duty cycle is 78.5%, converters may be designed that run at duty cycles well below this for a narrower, 36-V to 57-V range. The TPS23755 provides a fixed internal compensation ramp that suffices for most applications.  $R_S$  (see  $\boxtimes$  7-2) may be used if the internally provided slope compensation is not enough. It works with ramp current ( $I_{PK} = I_{SL-EX}$ , approximately 40  $\mu$ A) that flows out of the CS pin when the MOSFET is on. The  $I_{PK}$  specification does not include the approximately 5- $\mu$ A fixed current that flows out of the CS pin.

Most current-mode control papers and application notes define the slope values in terms of  $V_{PP}/T_S$  (peak ramp voltage / switching period); however, *Electrical Characteristics: DC-DC Controller Section* specifies the slope peak ( $V_{SLOPE}$ ) based on the maximum duty cycle. Assuming that the desired slope,  $V_{SLOPE-D}$  (in mV/period), is based on the full period, compute  $R_S$  per  $\pm$  1 where  $V_{SLOPE}$ ,  $D_{MAX}$ , and  $I_{SL-EX}$  are from *Electrical Characteristics: DC-DC Controller Section* with voltages in mV, current in  $\mu A$ , and the duty cycle is unitless (for example,  $D_{MAX} = 0.78$ ).

図 7-2. Additional Slope Compensation

Blanking provides an interval between the FET gate drive going high and the current comparator on CS actively monitoring the input. This delay allows the normal turnon current transient (spike) to subside before the comparator is active, preventing undesired short duty cycles and premature current limiting.

The TPS23755 blanker timing is precise enough that the traditional R-C filters on CS can be eliminated. This avoids current-sense waveform distortion, which tends to get worse at light output loads. There may be some situations or designers that prefer an R-C approach, for example if the presence of  $R_S$  causes increased noise, due to adjacent noisy signals, to appear at CS pin. The TPS23755 provides a pulldown on CS (approximately 400  $\Omega$ ) during the GATE OFF-time to improve sensing when an R-C filter must be used, by reducing cycle-to-cycle carry-over voltage on  $C_S$ .

#### 7.3.4.3 COMP, FB, CP and Opto-less Feedback

The TPS23755 DC-DC controller implements current-mode control, using a voltage control loop error amplifier (pins FB and COMP) to define the input reference voltage of the current mode control comparator which determines the switching MOSFET peak current. Loop compensation components are connected between COMP and FB.

$V_{COMP}$  below  $V_{ZDC}$  causes the converter to stop switching. The maximum (peak) current is requested at approximately ( $V_{ZDC}$  + 2 × ( $V_{CSMAX}$  +  $V_{SLOPE}$ )). The AC gain from COMP to the PWM comparator is 0.5.

The TPS23755 DC-DC controller can operate with feedback from an auxiliary winding of the flyback power transformer, eliminating the need for external shunt regulator and optocoupler. It also operates with continuously connected feedback, enabling better optimization of the power supply, and resulting in significantly lower noise sensitivity.

(1)

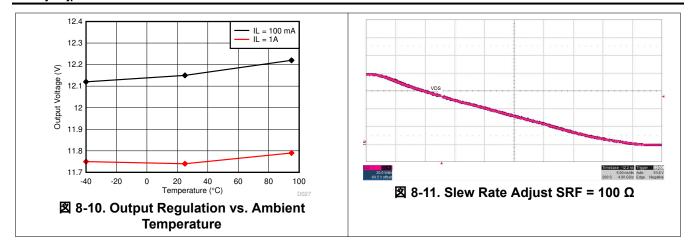

The TPS23755 applies to single-output flyback converter applications where a secondary side diode rectifier is used. In typical 12 V output application and when combined with a correctly designed power transformer, ±5% load regulation over a wide (5% to 100%) output current range can be achieved.

### 7.3.4.4 FRS Frequency Setting and Synchronization

The FRS pin programs the (free-running) oscillator frequency, and may also be used to synchronize the TPS23755 converter to a higher frequency. The internal oscillator sets the maximum duty cycle and controls the current-compensation ramp circuit, making the ramp height independent of frequency.  $R_{FRS}$  must be selected per  $\pm$  2.

$$R_{FRS}(k\Omega) = \frac{15000}{f_{SW}(kHz)}$$

(2)

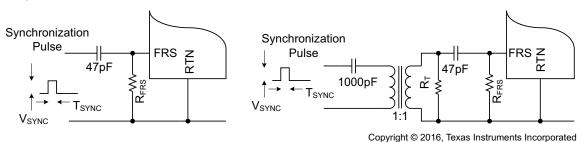

The TPS23755 may be synchronized to an external clock to eliminate beat frequencies from a sampled system, or to place emission spectrum away from an RF input frequency. Synchronization may be accomplished by applying a short pulse ( > 35 ns) of magnitude  $V_{SYNC}$  to FRS as shown in  $\boxtimes$  7-3.  $R_{FRS}$  must be chosen so that the maximum free-running frequency is just below the desired synchronization frequency. The synchronization pulse terminates the potential ON-time period, and the OFF-time period does not begin until the pulse terminates. A short pulse is preferred to avoid reducing the potential ON-time.

Figure 7-3 shows examples of nonisolated and transformer-coupled synchronization circuits.  $R_T$  reduces noise susceptibility for the isolation transformer implementation. The FRS node must be protected from noise because it is high impedance.

図 7-3. Synchronization

#### 7.3.4.5 Frequency Dithering for Spread Spectrum Applications

The international standard CISPR 22 (and adopted versions) is often used as a requirement for conducted emissions. Ethernet cables are covered as a telecommunication port under section 5.2 for conducted emissions. Meeting EMI requirements is often a challenge, with the lower limits of Class B being especially hard. Circuit board layout, filtering, and snubbing various nodes in the power circuit are the first layer of control techniques. A more detailed discussion of EMI control is presented in *Practical Guidelines to Designing an EMI Compliant PoE Powered Device With Isolated Flyback*, SLUA469. Additionally, IEEE 802.3at sections 33.3 and 33.4 have requirements for noise injected onto the Ethernet cable based on compatibility with data transmission.

A technique referred to as frequency dithering can also be used to provide additional EMI measurement reduction. The switching frequency is modulated to spread the narrowband individual harmonics across a wider bandwidth, thus lowering peak measurements.

Frequency dithering is a built-in feature of the TPS23755. The oscillator frequency can be dithered by connecting a capacitor from DTHR to RTN and a resistor from DTHR to FRS. An external capacitor,  $C_{DTR}$  ( $\boxtimes$  8-1), is selected to define the modulation frequency  $f_m$ . This capacitor is being continuously charged and discharged between slightly less than 0.5 V and slightly above 1.5 V by a current source/sink equivalent to approximately 3x the current through FRS pin.  $C_{DTR}$  value is defined according to:

$$C_{DTR} = \frac{3/R_{FRS} (\Omega)}{2.052 \times f_{m} (Hz)}$$

(3)

$f_m$  should always be higher than 9 kHz, which is the resolution bandwidth applied during conducted emission measurement. Typically,  $f_m$  should be set to around 11 kHz to account for component variations.

The resistor  $R_{DTR}$  is used to determine  $\Delta f$ , which is the amount of dithering, and its value is determined according to:

$$R_{DTR}(\Omega) = \frac{0.513 \times R_{FRS}(\Omega)}{\%DTHR}$$

(4)

For example, a 13.2% dithering with a nominal switching frequency of 250 kHz results in frequency variation of ±33 kHz.

## 7.3.4.6 SST and Soft-Start of the Switcher

Converters require a soft-start on the voltage error amplifier to prevent output overshoot on startup. In PoE applications, the PD also needs soft-start to limit its input current at turnon below the limit allocated by the power source equipment (PSE).

The TPS23755 provides primary side closed loop controlled soft-start, which applies a slowly rising ramp voltage to a second control input of the error amplifier. The lower of the reference input and soft-start ramps controls the error amplifier, allowing the output voltage to rise in a smooth monotonic fashion.

The soft-start period of the TPS23755 is internally set to a nominal value of 16 ms.

### 7.3.4.7 AUX V, AUX D and Secondary Adapter Or'ing

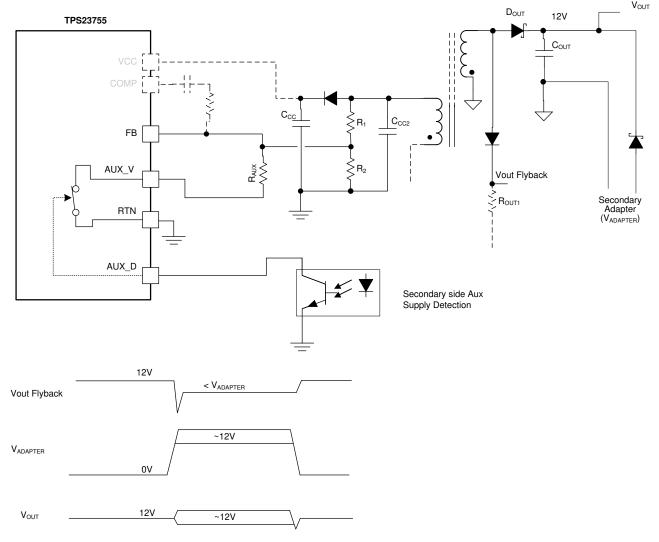

When the auxiliary is present, a signal (AUX\_D) tells the PD PWM to lower its output voltage slightly below the auxiliary voltage to ensure the auxiliary has priority to power the main output. When the auxiliary power goes away, the DC-DC converter increases back its output voltage, to ensure seamless transition. One significant advantage of this approach is that the efficiency of the PoE-powered flyback power stage can be optimized independently of the need for seamless transition. The adjustability of the lower voltage level allows the use of highly inaccurate auxiliary voltage sources. Such feature eases the thermal design, in particular when secondary diode rectification is used, since when PoE powered, the flyback stage can deliver power at a higher output voltage, and hence at a lower output current.

In  $\boxtimes$  7-4 below, R<sub>OUT1</sub> ensures that the PSE maintains power while the auxiliary is present, ensuring there will be no power interruption when the auxiliary power is removed.

The lower voltage level is programmable with the  $R_{AUX}$  resistor, which impacts the feedback network division ratio. Note however that the flyback power transformer design and resistor selection must be such that  $V_{VCC}$  will remain above nominally 6.1 V ( $V_{CUVF}$ ) while the auxiliary power is present.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

図 7-4. Secondary Side Priority Control with Smooth Transition

#### 7.3.5 Internal Switching FET - DRAIN, RSNS, SRF and SRR

The DRAIN and RSNS provide connection to the drain and source of the integrated switching power FET. RSNS pin is a high current pin and it must have a short connection to the current sense resistor which other end is directly tied to a plane referenced to the GND pin. Current sensing is done with CS pin, which should be connected directly to the high side of the current sense resistor.

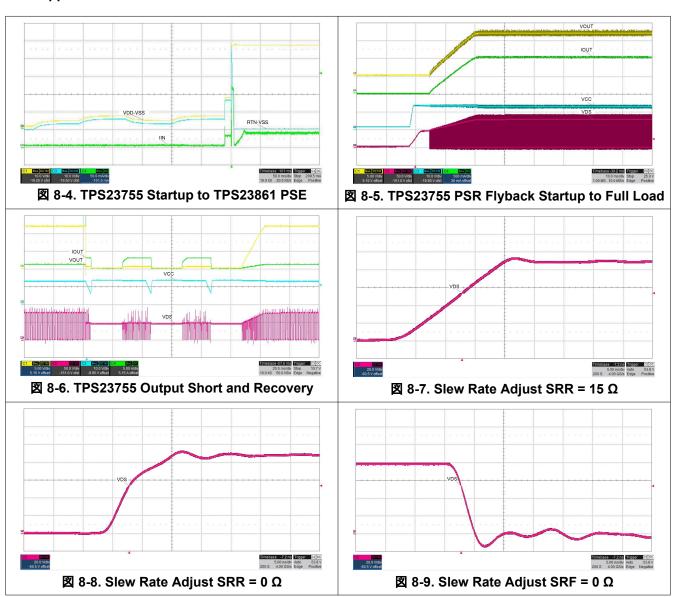

The internal FET gate driver is powered from VB voltage rail and the return path is through the GND pin. SRF and SRR pins provide slew rate control of the switching FET. The gate sourcing current is drawn through the SRF pin which is tied to VB pin through a resistor (0-100  $\Omega$ ). The gate sinking current circulates through the SRR pin which is externally tied to the GND pin either via a low-value resistor (0-15  $\Omega$ ) or a direct connection.

## 7.3.6 VPD Supply Voltage

VPD pin connects to the positive side of the input supply. It provides operating power to the PD controller and allows monitoring of the input line voltage. If  $V_{VPD}$  falls below its UVLO threshold and goes back above it, or if a thermal shutdown resumes while  $V_{VPD}$  is already above its UVLO threshold, the TPS23755 returns to inrush limiting.

### 7.3.7 VDD Supply Voltage

VDD connects to the source of DC-DC converter startup current. It is connected to VPD for most applications. It may also be isolated by a diode from VPD to support some PoE priority operation.

#### 7.3.8 GND

GND is the power ground used by the flyback power FET gate driver and CP pin. Connect to the RTN plane. VB bypassing capacitor should be directly connected to the GND pin.

#### 7.3.9 VSS

VSS is the PoE input-power return side. It is the reference for the PoE interface circuits, and has a current-limited hotswap switch that connects it to RTN. VSS is clamped to a diode drop above RTN by the hotswap switch. The exposed thermal PAD must be connected to this pin to ensure proper operation.

## 7.3.10 Exposed Thermal PAD

The exposed thermal PAD is internally connected to VSS pin. It should be tied to a large VSS copper area on the PCB to provide a low resistance thermal path to the circuit board. TI recommends maintaining a clearance of 0.025" between VSS and high-voltage signals such as VPD and VDD.

#### 7.4 Device Functional Modes

#### 7.4.1 PoE Overview

The following text is intended as an aid in understanding the operation of the TPS23755, but it is not a substitute for the actual IEEE 802.3at standard. The IEEE 802.3at standard is an update to IEEE 802.3-2008 clause 33 (PoE), adding high-power options and enhanced classification.

Generally speaking, a device compliant to IEEE 802.3-2008 is referred to as a Type 1 device, and devices with high power or enhanced classification is referred to as Type 2 devices. The TPS23755 is intended to power Type 1 devices (up to 13 W), and is fully compliant to IEEE 802.3at for hardware classes 0 - 3. Standards change and must always be referenced when making design decisions.

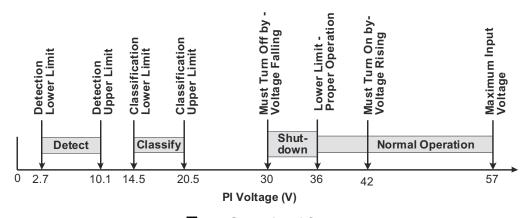

図 7-5. Operational States

The PD input is typically an RJ-45 eight-lead connector which is referred to as the power interface (PI). PD input requirements differ from PSE output requirements to account for voltage drops in the cable and operating margin. The IEEE 802.3at standard uses a cable resistance of 20  $\Omega$  for Type 1 devices to derive the voltage limits at the PD based on the PSE output voltage requirements. Although the standard specifies an output power of 15.4 W at the PSE, only 13 W is available at the PI due to the worst-case power loss in the cable. The PSE can apply voltage either between the RX and TX pairs (pins 1-2 and 3-6 for 10baseT or 100baseT), or between the two spare pairs (4-5 and 7-8). Power application to the same pin combinations in 1000baseT systems is recognized in IEEE 802.3at. 1000baseT systems can handle data on all pairs, eliminating the spare pair terminology. The PSE may only apply voltage to one set of pairs at a time. The PD uses input diode bridges to accept power from any of the possible PSE configurations. The voltage drops associated with the input bridges create a difference between the standard limits at the PI and the TPS23755 specifications.

The PSE is permitted to disconnect a PD if it draws more than its maximum class power over a one second interval. A Type 1 PSE compliant to IEEE 802.3at is required to limit current to between 400 mA and 450 mA during powered operation, and it must disconnect the PD if it draws this current for more than 75 ms. Class 0 and 3 PDs may draw up to 400-mA peak currents for up to 50 ms. The PSE may set lower output current limits based on the declared power requirements of the PD.

## 7.4.2 Threshold Voltages

The TPS23755 has a number of internal comparators with hysteresis for stable switching between the various states as shown in 🗵 7-5. 🗵 7-6 relates the parameters in *Electrical Characteristics: DC-DC Controller Section* and Electrical Characteristics: PoE and Control to the PoE states. The mode labeled idle between classification and operation implies that the DEN, CLS, and RTN pins are all high impedance.

Note: Variable names refer to Electrical Characteristic Table parameters

図 7-6. Threshold Voltages

#### 7.4.3 PoE Start-Up Sequence

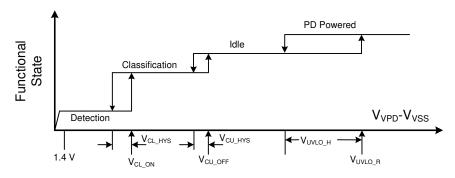

The waveforms of Z 7-7 demonstrate detection, classification, and start-up from a Type 1 PSE. The key waveforms shown are  $V_{VPD-VSS}$ ,  $V_{RTN-VSS}$ , and  $I_{Pl}$ . IEEE 802.3at requires a minimum of two detection levels; however, four levels are shown in this example. Four levels guard against misdetection of a device when plugged in during the detection sequence.

Copyright © 2021 Texas Instruments Incorporated

図 7-7. PoE Start-Up Sequence

#### 7.4.4 Detection

The TPS23755 is in detection mode whenever  $V_{VPD-V~SS}$  is below the lower classification threshold. When the input voltage rises above  $V_{CL\_ON}$ , the DEN pin goes to an open-drain condition to conserve power. While in detection, RTN is high impedance, almost all the internal circuits are disabled, and the DEN pin is pulled to  $V_{SS}$ . An  $R_{DEN}$  of 24.9 k $\Omega$  (1%), presents the correct signature. It may be a small, low-power resistor because it only sees a stress of about 5 mW. A valid PD detection signature is an incremental resistance between 23.75 k $\Omega$  and 26.25 k $\Omega$  at the PI.

The detection resistance seen by the PSE at the PI is the result of the input bridge resistance in series with the parallel combination of  $R_{DEN}$  and the TPS23755 bias loading. The incremental resistance of the input diode bridge may be hundreds of ohms at the very low currents drawn when 2.7 V is applied to the PI. The input bridge resistance is partially cancelled by the effective resistance of the TPS23755 during detection.

#### 7.4.5 Hardware Classification

Hardware classification allows a PSE to determine the power requirements of a PD before starting, and helps with power management once power is applied. The maximum power entries in 表 7-1 determine the class the PD must advertise. A Type 1 PD may not advertise Class 4. The PSE may disconnect a PD if it draws more than its stated Class power. The standard permits the PD to draw limited current peaks; however, the average power requirement always applies.

Voltage from 14.5 V to 20.5 V is applied to the PD for up to 75 ms during hardware classification. A fixed output voltage is sourced by the CLS pin, causing a fixed current to be drawn from VPD through  $R_{CLS}$ . The total current drawn from the PSE during classification is the sum of bias and  $R_{CLS}$  currents. PD current is measured and decoded by the PSE to determine which of the five available classes is advertised (see Table 7-1). The TPS23755 disables classification above  $V_{CU\_OFF}$  to avoid excessive power dissipation. CLS voltage is turned off during PD thermal limit or when DEN is active. The CLS output is inherently current-limited, but should not be shorted to VSS for long periods of time.

### 7.4.6 Maintain Power Signature (MPS)

The MPS is an electrical signature presented by the PD to assure the PSE that it is still present after operating voltage is applied. A valid MPS consists of a minimum DC current of 10 mA (at a duty cycle of at least 75 ms on every 225 ms) and an AC impedance lower than 26.25 k $\Omega$  in parallel with 0.05  $\mu$ F. The AC impedance is usually accomplished by the minimum  $C_{BULK}$  requirement of 5  $\mu$ F. When DEN is used to force the hotswap switch off,

the DC MPS is not met. A PSE that monitors the DC MPS will remove power from the PD when this occurs. A PSE that monitors only the AC MPS may remove power from the PD.

### 7.4.7 Start-Up and Converter Operation

The internal PoE undervoltage lockout (UVLO) circuit holds the hotswap switch off before the PSE provides full voltage to the PD. This prevents the converter circuits from loading the PoE input during detection and classification. The converter circuits discharges  $C_{DD}$ ,  $C_{CC}$ , and  $C_{VB}$  while the PD is unpowered. Thus  $V_{VDD-RTN}$  will be a small voltage until just after full voltage is applied to the PD, as seen in  $\boxtimes$  7-7.

The PSE drives the PD input voltage to the operating range once it has decided to power up the PD. When  $V_{PD}$  rises above the UVLO turnon threshold ( $V_{UVLO-R}$ , approximately 35.5 V) with RTN high, the TPS23755 enables the hotswap MOSFET with an approximately 140-mA (inrush) current limit. See the waveforms of  $\boxtimes$  7-8 for an example. Converter switching is disabled while  $C_{DD}$  charges and  $V_{RTN}$  falls from  $V_{VDD}$  to nearly  $V_{VSS}$ ; however, the converter start-up circuit is allowed to charge  $C_{CC}$ . Once the inrush current falls about 10% below the inrush current limit, the PD control switches to the operational level (approximately 450 mA) and converter switching is permitted.

Converter switching is allowed if the PD is not in inrush current limit and the VCC under-voltage lockout ( $V_{CUVR}$ ) circuit permits it. Continuing the start-up sequence shown in Figurer 7-7,  $V_{VCC}$  rises as the start-up current source charges  $C_{CC}$  and the converter switching is inhibited by the status of the VCC UVLO. The VB regulator powers the internal converter circuits as  $V_{VCC}$  rises.

Once  $V_{VCC}$  goes above its UVLO (nominally 8.25 V), the converter switching is enabled following the closed loop controlled soft-start sequence. Note that the startup current source capability is such that it can fully maintain  $V_{VCC}$  during the converter soft-start without requiring any significant  $C_{CC}$  capacitance, in 48 V input applications. At the end of the soft-start period, the startup current source is turned off.  $V_{VCC}$  falls as it powers the internal circuits including the switching MOSFET gate. If the converter control-bias output rises to support  $V_{VCC}$  before it falls to  $V_{CUVF}$  (nominally 6.1 V), a successful start-up occurs. Figure 7-7 shows a small droop in  $V_{VCC}$  while the output voltage rises smoothly and a successful start-up occurs.

図 7-8. Power Up and Start

The converter shuts off when  $V_{VCC}$  falls below its lower UVLO. This can happen when power is removed from the PD, or during a fault on a converter output rail. When one output is shorted, all the output voltages fall including the one that powers VCC. The control circuit discharges VCC until it hits the lower UVLO and turns off. A restart initiates if the converter turns off and there is sufficient VDD voltage. This type of operation is sometimes referred to as *hiccup mode*, which when combined with the soft-start provides robust output short protection by providing time-average heating reduction of the output rectifier.