**TPS25810** SLVSCR1C - SEPTEMBER 2015-REVISED JULY 2017

# TPS25810 USB Type-C DFP Controller and Power Switch with Load Detection

#### **Features**

- USB Type-C Rev. 1.2 Compliant DFP Controller

- Connector Attach/Detach Detection

- STD/1.5-A/3-A Capability Advertisement on CC

- Super Speed Polarity Determination

- V<sub>BUS</sub> Application and Discharge

- V<sub>CONN</sub> Application to Electronically Marked Cable

- Audio and Debug Accessory Identification

- 0.7-µA (typ) I<sub>DDQ</sub> When Port Unattached

- Three Input Supply Options

- IN1: USB Charging Supply

- IN2: V<sub>CONN</sub> Supply

- AUX: Device Power Supply

- Power Wake Supports Low Power in System Hibernate (S4) and OFF (S5) Power States

- 34-mΩ (typ) High-Side MOSFET

- 1.7/3.4-A I<sub>Limit</sub> (±7.1%) Programmable

- Port Power Management Enables Power Resource Optimization Across Multi-Ports

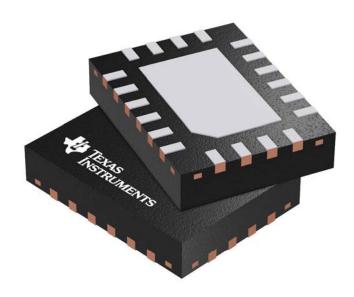

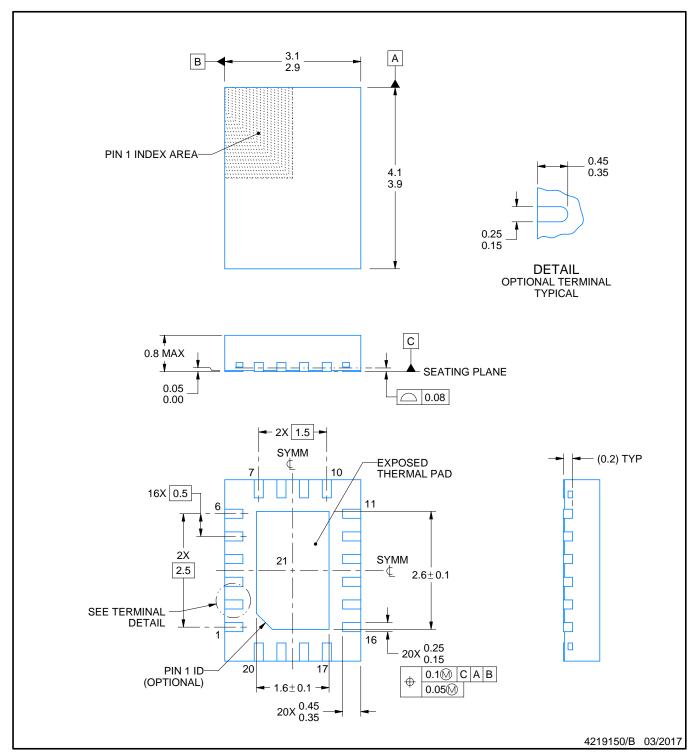

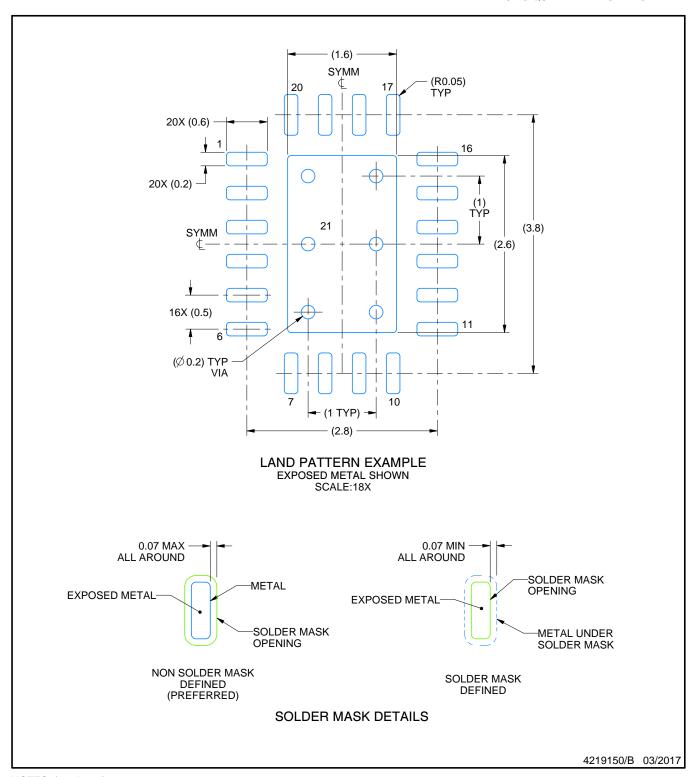

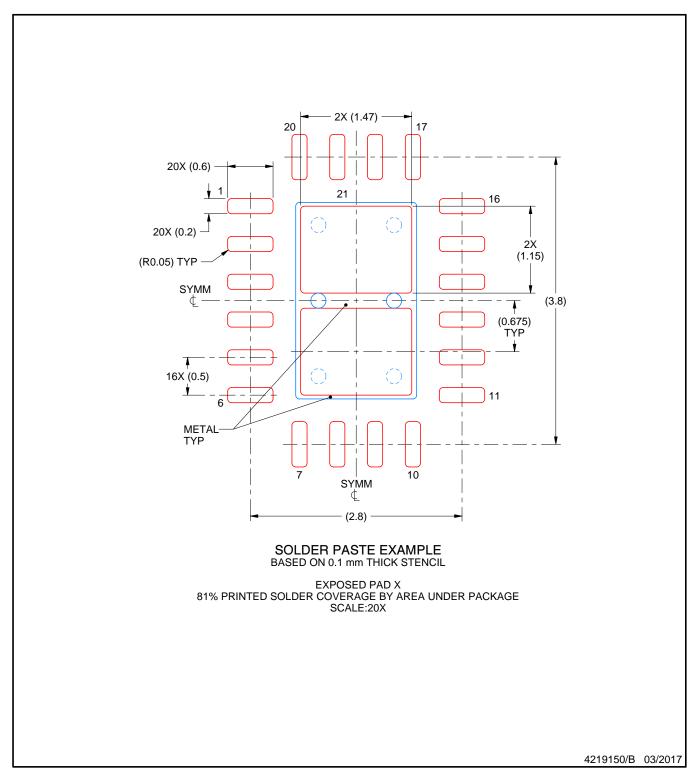

- Package: 20-Pin WQFN (3 x 4) (1)

- UL Listed File No. E169910

# **Applications**

- USB Type C Host Port in Notebook for Sleep Charging

- LCD Monitor/Docking Station and Charging Cradles

- Type C USB Wall Chargers

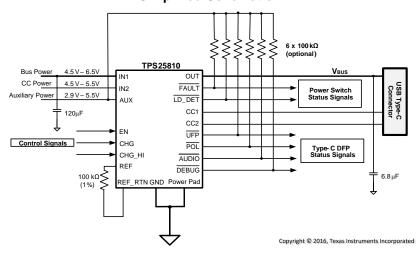

# 3 Description

The TPS25810 is a USB Type-C Downstream Facing Port (DFP) controller with an integrated 3-A rated USB power switch. The TPS25810 monitors the Type-C Configuration Channel (CC) lines to determine when an USB device is attached. If an Upstream Facing Port (UFP) device is attached, the TPS25810 applies power to V<sub>BUS</sub> and communicates the selectable V<sub>BUS</sub> current sourcing capability to the UFP via the passthrough CC line. If the UFP is attached using an electronically marked cable, the TPS25810 also applies V<sub>CONN</sub> power to the cable CC pin. The TPS25810 also identifies when Type-C audio or debug accessories are attached.

The TPS25810 draws less than 0.7 uA (typ) when no device is attached. Additional system power saving is achievable in S4/S5 system power states by using the UFP output to disable the high power 5-V supply when no UFP is attached. In this mode the device is capable of running from an auxiliary supply (AUX) which can be a lower voltage supply (3.3 V), typically powering the system uC in low power states (S4/S5).

The TPS25810 34-m $\Omega$  power switch has two selectable fixed current limits that align with the Type-C current levels. The FAULT output signals when the switch is in an over current or over temperature condition. The LD\_DET output controls power management to multiple high current Type-C ports in an environment where all ports cannot simultaneously provide high current (3 A).

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| TPS25810    | WQFN (20) | 3.00 mm x 4.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### (1) CC pins are IEC-61000-4-2 rated

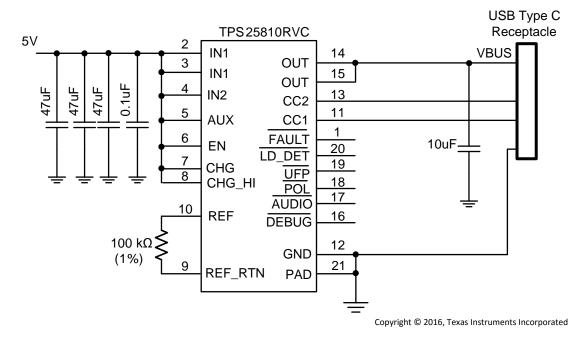

## Simplified Schematic

# **Table of Contents**

| 1 | Features 1                           | 7.4 Device Functional Modes                            | 21 |

|---|--------------------------------------|--------------------------------------------------------|----|

| 2 | Applications 1                       | 8 Application and Implementation 2                     | 22 |

| 3 | Description 1                        | 8.1 Application Information                            | 22 |

| 4 | Revision History2                    | 8.2 Typical Applications                               | 22 |

| 5 | Pin Configuration and Functions      | 9 Power Supply Recommendations                         | 27 |

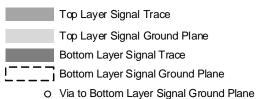

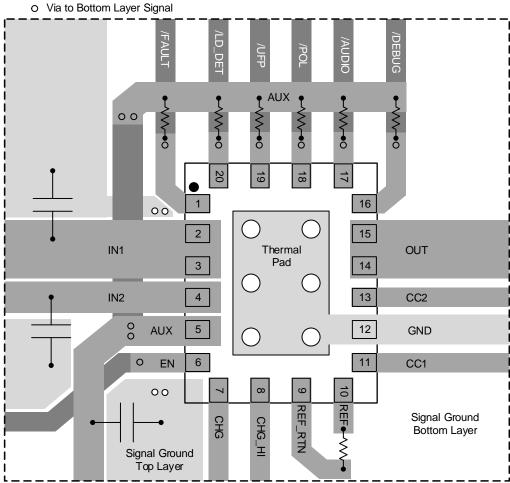

| 6 | Specifications                       | 10 Layout                                              | 28 |

| ٠ | 6.1 Absolute Maximum Ratings         | 10.1 Layout Guidelines                                 | 28 |

|   | 6.2 ESD Ratings                      | 10.2 Layout Example                                    |    |

|   | 6.3 Recommended Operating Conditions | 11 Device and Documentation Support 3                  | 30 |

|   | 6.4 Thermal Information              | 11.1 Device Support                                    |    |

|   | 6.5 Electrical Characteristics       | 11.2 Documentation Support                             | 30 |

|   | 6.6 Switching Characteristics        | 11.3 Receiving Notification of Documentation Updates 3 | 30 |

|   | 6.7 Typical Characteristics9         | 11.4 Community Resources                               | 30 |

| 7 | Detailed Description 11              | 11.5 Trademarks                                        | 30 |

| - | 7.1 Overview                         | 11.6 Electrostatic Discharge Caution                   | 30 |

|   | 7.2 Functional Block Diagram         | 11.7 Glossary                                          | 30 |

|   | 7.3 Feature Description              | 12 Mechanical, Packaging, and Orderable Information    | 30 |

# 4 Revision History

| Changes from Revision B (May 2016) to Revision C                                                      | Page   |

|-------------------------------------------------------------------------------------------------------|--------|

| Changed Feature From: USB Type-C Rev. 1.1 Compliant DFP Controller To: USB Type-C Rev. Controller     |        |

| • Changed text From: Type-C spec revision 1.1 To: Type-C spec revision 1.2 in the Overview sect       | ion 11 |

| Replaced Figure 15                                                                                    | 18     |

| Changes from Revision A (September 2015) to Revision B                                                | Page   |

| Added CC pins IEC-61000-4-2 rated footnote                                                            | 1      |

| <ul> <li>Changed from UL and CB Tests Underway to UL Listed – File No. E169910 in Features</li> </ul> | 1      |

| Changed 10µF to 6.8µF in Simplified Schematic                                                         | 1      |

| Added text to REF description                                                                         | 3      |

| Added IEC information to ESD Ratings                                                                  | 4      |

| Changed IN2 I <sub>I</sub> parameter description in Electrical Characteristics                        | 7      |

| Changed t <sub>res</sub> to t <sub>ios</sub> in Switching Characteristics                             | 8      |

| Added text to Detecting a Connection section                                                          | 12     |

| Changed Rp to Rds in Figure 12                                                                        | 12     |

| Changed loss to drop in Figure 14                                                                     | 16     |

| Added text and Figure 15 to Plug Polarity Detection                                                   | 18     |

| Added last sentence to Input and Output Capacitance                                                   | 23     |

| Added ESD Considerations to Layout Guidelines                                                         | 28     |

| Added Protecting the TPS25810 from High Voltage DFPs to Related Documentation                         | 30     |

| Changes from Original (September 2015) to Revision A                                                  | Page   |

| Changed from Product Preview to Production Data                                                       | 1      |

Submit Documentation Feedback

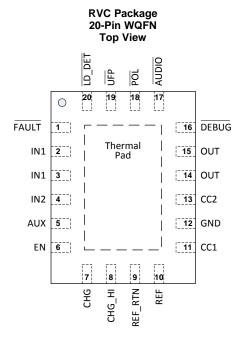

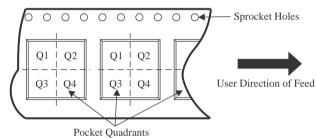

# 5 Pin Configuration and Functions

## **Pin Functions**

| PIN I/O     |        |     |                                                                                                                                                                                                                                |

|-------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NUMBER | 1/0 | DESCRIPTION                                                                                                                                                                                                                    |

| FAULT 1 O   |        | 0   | Fault event indicator. Open-drain logic output that asserts low to indicate current limit or thermal shutdown event due to over temperature.                                                                                   |

| IN1         | 2, 3   | ı   | V <sub>BUS</sub> input supply. Internal power switch connects IN1 to OUT.                                                                                                                                                      |

| IN2         | 4      | 1   | V <sub>CONN</sub> input supply. Internal power switch connects IN2 to CC1 or CC2. Short to IN1 if only one supply is used.                                                                                                     |

| AUX         | 5      | - 1 | Auxiliary input supply. Connect to always alive system rail to use the Power Wake feature. Short to IN1 and IN2 if only one supply is used.                                                                                    |

| EN          | 6      | ı   | Enable logic input to turn the device on and off.                                                                                                                                                                              |

| CHG         | 7      | I   | Charge logic input to select between standard USB (500 mA for a Type C receptacle supporting only USB 2.0 and 900 mA for Type C receptacle supporting USB 3.1) or Type-C current sourcing ability.                             |

| CHG_HI      | 8      | I   | High-charge logic input to select between 1.5-A and 3-A Type-C current sourcing capability. Valid when CHG is set to Type-C current.                                                                                           |

| REF_RTN     | 9      | ı   | Precision signal reference return. Connect to REF pin via 100-kΩ, 1% resistor.                                                                                                                                                 |

| REF         | 10     | I   | Analog input used to generate internal current reference. Connect a 1% or better, 100 ppm, 100-kΩ resistor between this pin and REF_RTN.                                                                                       |

| CC1         | 11     | I/O | Analog input/output that connects to the Type-C receptacle CC1 pin                                                                                                                                                             |

| GND         | 12     | _   | Power ground                                                                                                                                                                                                                   |

| CC2         | 13     | I/O | Analog input/output that connects to the Type-C receptacle CC2 pin.                                                                                                                                                            |

| OUT         | 14,15  | 0   | Power switch output.                                                                                                                                                                                                           |

| DEBUG       | 16     | 0   | Open-drain logic output that asserts when a Type-C Debug accessory is identified on the CC lines.                                                                                                                              |

| AUDIO       | 17     | 0   | Open-drain logic output that asserts when a Type-C Audio accessory is identified on the CC lines.                                                                                                                              |

| POL 18 O    |        | 0   | Polarity open-drain logic output that signals which Type-C CC pin is connected to the CC line. This gives the information needed to mux the super speed lines. Asserted when the CC2 pin is connected to the CC line in cable. |

| <u>UFP</u>  | 19     | 0   | Open-drain logic output that asserts when a Type-C UFP is identified on the CC lines.                                                                                                                                          |

| LD_DET 20 O |        | 0   | Load-detect open-drain logic output that signals when a device set to source Type-C 3 A current is sourcing over 1.95 A nominal.                                                                                               |

| Thermal Pad | -      | -   | Thermal pad on bottom of package.                                                                                                                                                                                              |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range, voltages are respect to GND (unless otherwise noted) (1)

|                                                |                                                                                           | MIN                                                             | MAX                                                                           | UNIT |

|------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------|------|

|                                                | IN1, IN2, AUX, EN, CHG, CHG_HI, REF, OUT, LD_DET, FAULT, CC1, CC2, UFP, POL, AUDIO, DEBUG | -0.3                                                            | 7                                                                             | V    |

| Pin voltage, V                                 | REF_RTN                                                                                   |                                                                 | Internally connected to GND                                                   | V    |

| Pin positive source current, I <sub>SRC</sub>  | OUT, REF, CC1, CC2                                                                        |                                                                 | Internally<br>limited                                                         | Α    |

|                                                | OUT (while applying VBUS)                                                                 |                                                                 | 5                                                                             | Α    |

| Pin positive sink current, I <sub>SNK</sub>    | CC1, CC2 (while applying V <sub>CONN</sub> )                                              | LD_DET, -0.3 7  Internally connected to GND  Internally limited | Α                                                                             |      |

| THE POSITIVE SHIRL COLLECT, ISNK               | LD_DET, FAULT, UFP, POL, AUDIO, DEBUG                                                     |                                                                 | Internally connected to GND Internally limited  5 1 Internally limited 40 180 | mA   |

| Operating junction temperature, T <sub>J</sub> |                                                                                           | -40                                                             | 180                                                                           | °C   |

| Storage temperature range, T <sub>stg</sub>    |                                                                                           | -65                                                             | 150                                                                           | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                        |                                                                                                                  |                                             |                                                             | VALUE  | UNIT |

|------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------|--------|------|

|                        |                                                                                                                  | Human-bo                                    | ody model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)             | ±2000  |      |

| V (1)                  | Electrostatic                                                                                                    | Charged-o                                   | device model (CDM), per JEDEC specification JESD22-C101 (3) | ±500   | V    |

| V <sub>(ESD)</sub> (1) | discharge IEC <sup>(4)</sup> IEC61000-4-2 contact discharge, CC1 and CC2 IEC61000-4-2 air discharge, CC1 and CC2 | IEC61000-4-2 contact discharge, CC1 and CC2 | ±8000                                                       | V      |      |

|                        |                                                                                                                  | IEC ( /                                     | IEC61000-4-2 air discharge, CC1 and CC2                     | ±15000 |      |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity/immunity to damage caused by assembly line electrostatic discharges into the device.

- (2) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (4) Surges per IEC61000-402, 1999 applied between CC1/CC2 and output ground of the TPS25810EVM-745.

## 6.3 Recommended Operating Conditions

Voltages are with respect to GND (unless otherwise noted)

|                        |                                              |                                               | MIN  | NOM MA              | UNIT |

|------------------------|----------------------------------------------|-----------------------------------------------|------|---------------------|------|

|                        |                                              | IN1                                           | 4.5  | 6.                  | 5    |

| VI                     | Supply voltage                               | IN2                                           | 4.5  | 5.                  | 5 V  |

|                        |                                              | AUX                                           | 2.9  | 5.                  | 5    |

| VI                     | Input voltage                                | EN, CHG, CHG_HI                               | 0    | 5.                  | 5 V  |

| $V_{IH}$               | High-level input voltage                     | EN, CHG, CHG_HI                               | 1.17 |                     | V    |

| $V_{IL}$               | Low-level voltage                            | EN, CHG, CHG_HI                               |      | 0.6                 | 3 V  |

| V <sub>PU</sub>        | Pull-up voltage                              | Used on LD_DET, FAULT, UFP, POL, AUDIO, DEBUG | 0    | 5.                  | 5 V  |

|                        | Decitive covered comment                     | OUT                                           |      | ;                   | 3 A  |

| I <sub>SRC</sub>       | Positive source current                      | CC1 or CC2 when supplying VCONN               |      | 25                  | ) mA |

| I <sub>SNK</sub>       | Positive sink current (10 ms moving average) | LD_DET, FAULT, UFP, POL, AUDIO, DEBUG         |      | 1                   | ) mA |

| I <sub>SNK_PULSE</sub> | Positive repetitive pulse sink current       | LD_DET, FAULT, UFP, POL, AUDIO, DEBUG         |      | Internall<br>Limite |      |

| R <sub>REF</sub>       | Reference Resistor                           |                                               | 98   | 100 10              | 2 kΩ |

| TJ                     | Operating junction temperature               |                                               | -40  | 12                  | °C   |

#### 6.4 Thermal Information

|                        |                                              | TPS25810   |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RVC (WQFN) | UNIT |

|                        |                                              | 20 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 39.3       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 43.4       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 13         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.7        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 13         | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 4.2        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN1}} \le 6.5 \text{ V}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN2}} \le 5.5 \text{ V}$ ,  $2.9 \text{ V} \le \text{V}_{\text{AUX}} \le 5.5 \text{ V}$ ;  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{CHG}\_{\text{HI}}} = \text{V}_{\text{AUX}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                     | PARAMETER                                              | TEST CONDITIONS                                                                                                                                              | MIN  | TYP  | MAX  | UNIT      |

|---------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| OUT - PO            | WER SWITCH                                             |                                                                                                                                                              |      |      | '    |           |

|                     |                                                        | T <sub>J</sub> = 25°C, I <sub>OUT</sub> = 3 A                                                                                                                |      | 34   | 37   |           |

| R <sub>DS(on)</sub> | On resistance <sup>(1)</sup>                           | -40°C ≤ T <sub>J</sub> ≤ 85°C, I <sub>OUT</sub> = 3 A                                                                                                        |      | 34   | 46   | $m\Omega$ |

|                     |                                                        | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}, \text{I}_{\text{OUT}} = 3 \text{ A}$                                                   |      | 34   | 55   |           |

| I <sub>REV</sub>    | OUT to IN reverse leakage current                      | $V_{OUT} = 6.5 \text{ V}, V_{IN1} = V_{EN} = 0 \text{ V},$<br>$-40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C},$<br>$I_{REV}$ is current out of IN1 pin |      | 0    | 3    | μΑ        |

| OUT - CU            | RRENT LIMIT                                            |                                                                                                                                                              |      |      |      |           |

|                     | 40                                                     | V <sub>CHG</sub> = 0 V or V <sub>CHG</sub> = V <sub>AUX</sub> and V <sub>CHG_HI</sub> = 0                                                                    | 1.58 | 1.7  | 1.82 |           |

| los                 | Short circuit current limit (1)                        | V <sub>CHG</sub> = V <sub>AUX</sub> and V <sub>CHG_HI</sub> = V <sub>AUX</sub>                                                                               | 3.16 | 3.4  | 3.64 | Α         |

|                     |                                                        | $R_{REF} = 10 \Omega$                                                                                                                                        |      |      | 7    |           |

| OUT - DIS           | CHARGE                                                 |                                                                                                                                                              |      |      |      |           |

|                     | Discharge resistance                                   | $V_{OUT}$ = 4 V, UFP signature removed from CC lines, time < $t_{w_{DCHG}}$                                                                                  | 400  | 500  | 600  | Ω         |

|                     | Bleed discharge resistance                             | V <sub>OUT</sub> = 4 V, No UFP signature on CC lines, time > t <sub>w_DCHG</sub>                                                                             | 100  | 150  | 250  | kΩ        |

| REF                 |                                                        |                                                                                                                                                              |      |      | *    |           |

| Vo                  | Output voltage                                         |                                                                                                                                                              | 0.78 | 0.8  | 0.82 | V         |

| I <sub>OS</sub>     | Short circuit current                                  | $R_{REF} = 10 \Omega$                                                                                                                                        | 9.5  |      | 15.3 | μΑ        |

| FAULT               |                                                        |                                                                                                                                                              |      |      |      |           |

| $V_{OL}$            | Output low voltage                                     | I <sub>FAULT</sub> = 1 mA                                                                                                                                    |      |      | 350  | mV        |

| I <sub>OFF</sub>    | Off-state leakage                                      | $V_{FAULT} = 5.5 \text{ V}$                                                                                                                                  |      |      | 1    | μΑ        |

| LD_DET              |                                                        |                                                                                                                                                              |      |      |      |           |

| V <sub>OL</sub>     | Output low voltage                                     | I <sub>LD_DET</sub> = 1 mA                                                                                                                                   |      |      | 350  | mV        |

| I <sub>OFF</sub>    | Off-state leakage                                      | $V_{LD\_DET} = 5.5 \text{ V}$                                                                                                                                |      |      | 1    | μΑ        |

| I <sub>TH</sub>     | OUT sourcing, rising threshold current for load detect |                                                                                                                                                              | 1.8  | 1.95 | 2.1  | А         |

|                     | Hysteresis <sup>(2)</sup>                              |                                                                                                                                                              |      | 125  |      | mA        |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

<sup>(2)</sup> These parameters are provided for reference only and do not constitute part of TI's published specifications for purposes of TI's product warranty.

# **Electrical Characteristics (continued)**

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN1}} \le 6.5 \text{ V}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN2}} \le 5.5 \text{ V}$ ,  $2.9 \text{ V} \le \text{V}_{\text{AUX}} \le 5.5 \text{ V}$ ;  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{CHG}\_{\text{HI}}} = \text{V}_{\text{AUX}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                          | PARAMETER                                                                                | TEST CONDITIONS                                                                                                      | MIN  | TYP   | MAX      | UNIT |

|--------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|-------|----------|------|

| CC1/CC2 - V              | CONN POWER SWITCH                                                                        |                                                                                                                      |      |       |          |      |

|                          | -                                                                                        | T <sub>J</sub> = 25°C, I <sub>OUT</sub> = 250 mA                                                                     |      | 365   | 420      |      |

| R <sub>DS(on)</sub>      | On resistance                                                                            | -40°C ≤ T <sub>J</sub> ≤ 85°C, I <sub>OUT</sub> = 250 mA                                                             |      | 365   | 530      | mΩ   |

| -(- /                    |                                                                                          | -40°C ≤ T <sub>J</sub> ≤ 125°C, I <sub>OUT</sub> = 250 mA                                                            |      | 365   | 420      |      |

| CC1/CC2 - V              | CONN POWER SWITCH - CURRENT                                                              | LIMIT                                                                                                                |      |       | *        |      |

|                          | Chart singuit assument limit (1)                                                         |                                                                                                                      | 300  | 355   | 410      | A    |

| l <sub>os</sub>          | Short circuit current limit <sup>(1)</sup>                                               | $R_{REF} = 10 \Omega$                                                                                                |      |       | 800      | mA   |

| CC1/CC2 – C              | ONNECT MANAGEMENT – DANGL                                                                | ING ELECTRONICALLY MARKED CABLE M                                                                                    | ODE  |       |          |      |

| 1                        | Sourcing current on the pass-<br>through CC Line                                         | 0 V ≤ V <sub>CCx</sub> ≤ 1.5 V                                                                                       | 64   | 80    | 96       | μΑ   |

| SRC                      | Sourcing current on the Ra CC line                                                       | 0 V ≤ V <sub>CCx</sub> ≤ 1.5 V                                                                                       | 64   | 80    | 96       | μΑ   |

| CC1/CC2 – C              | ONNECT MANAGEMENT - ACCES                                                                | SORY MODE                                                                                                            |      |       |          |      |

| 1                        | CCx Sourcing current (CC2- Audio, CC1-Debug)                                             | 0 V ≤ V <sub>CCx</sub> ≤ 1.5 V                                                                                       | 64   | 80    | 96       | μΑ   |

| I <sub>SRC</sub>         | CCx Sourcing current (CC1- Audio, CC2-Debug) (2)                                         | 0 V ≤ V <sub>CCx</sub> ≤ 1.5 V                                                                                       |      | 0     |          | μΑ   |

| CC1/CC2 – C              | ONNECT MANAGEMENT – UFP MG                                                               | DDE                                                                                                                  |      |       |          |      |

| I <sub>SRC</sub>         | Sourcing current with either IN1 or IN2 in UVLO                                          | $0 \text{ V} \le V_{CCx} \le 1.5 \text{ V}$<br>$V_{IN1} < V_{TH\_UVLO\_IN1} \text{ or } V_{IN2} < V_{TH\_UVLO\_IN2}$ | 64   | 80    | 96       | μΑ   |

|                          | Sourcing current                                                                         | V <sub>CHG</sub> = 0 V and V <sub>CHG_HI</sub> = 0 V<br>0 V ≤ V <sub>CCx</sub> ≤ 1.5 V                               | 75   | 80    | 85       |      |

| I <sub>SRC</sub>         |                                                                                          | $V_{CHG} = V_{AUX}$ and $V_{CHG\_HI} = 0 \text{ V}$<br>$0 \text{ V} \le V_{CCX} \le 1.5 \text{ V}$                   | 170  | 180   | 190      | μΑ   |

|                          |                                                                                          | $V_{CHG} = V_{AUX}$ and $V_{CHG\_HI} = V_{AUX}$<br>0 V \leq V_{CCX} \leq 2.45 V                                      | 312  | 330   | 348      |      |

| UFP, POL, A              | UDIO, DEBUG                                                                              |                                                                                                                      |      |       |          |      |

| V <sub>OL</sub>          | Output low voltage                                                                       | I <sub>SNK PIN</sub> = 1 mA                                                                                          |      |       | 250      | mV   |

| l <sub>OFF</sub>         | Off-state leakage                                                                        | V <sub>PIN</sub> = 5.5 V                                                                                             |      |       | 1        | μA   |

| EN, CHG, CH              | IG_HI - LOGIC INPUTS                                                                     |                                                                                                                      |      |       |          |      |

| V <sub>TH</sub>          | Rising threshold voltage                                                                 |                                                                                                                      |      | 0.925 | 1.15     | V    |

| V <sub>TH</sub>          | Falling threshold voltage                                                                |                                                                                                                      | 0.65 | 0.875 |          | V    |

|                          | Hysteresis <sup>(2)</sup>                                                                |                                                                                                                      |      | 50    |          | mV   |

| I <sub>IN</sub>          | Input current                                                                            | V <sub>EN</sub> = 0 V or 6.5 V                                                                                       | -0.5 |       | 0.5      | μA   |

|                          | ERATURE SHUT DOWN                                                                        |                                                                                                                      |      |       |          | -    |

| T <sub>TH_OTSD2</sub>    | Rising threshold temperature for device shutdown                                         |                                                                                                                      | 155  |       |          | °C   |

|                          | Hysteresis <sup>(2)</sup>                                                                |                                                                                                                      |      | 20    |          | °C   |

| T <sub>TH_OTSD1</sub>    | Rising threshold temperature for OUT/ V <sub>CONN</sub> switch shutdown in current limit |                                                                                                                      | 135  |       |          | °C   |

|                          | Hysteresis <sup>(2)</sup>                                                                |                                                                                                                      |      | 20    |          | °C   |

| IN1                      |                                                                                          |                                                                                                                      |      |       | <u> </u> |      |

| V <sub>TH_UVLO_IN1</sub> | Rising threshold voltage for UVLO                                                        |                                                                                                                      | 3.9  | 4.1   | 4.3      | V    |

|                          | Hysteresis <sup>(2)</sup>                                                                |                                                                                                                      |      | 100   |          | mV   |

# **Electrical Characteristics (continued)**

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN1}} \le 6.5 \text{ V}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN2}} \le 5.5 \text{ V}$ ,  $2.9 \text{ V} \le \text{V}_{\text{AUX}} \le 5.5 \text{ V}$ ;  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{CHG}} = \text{V}_{\text{AUX}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                     | PARAMETER                                                                                           | TEST CONDITIONS                                                                               | MIN  | TYP  | MAX  | UNIT |

|---------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

|                     | Disabled supply current                                                                             | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                  |      |      | 1    | μA   |

|                     | Enabled supply current with CC lines open                                                           | -40°C ≤ T <sub>J</sub> ≤ 85°C                                                                 |      |      | 1    | μA   |

| l <sub>l</sub>      | Enabled supply current with accessory or dangling electronically marked cable signature on CC lines |                                                                                               |      |      | 2    | μΑ   |

|                     | Enabled supply current with UFP attached                                                            | $V_{CHG}$ = 0 V, or $V_{CHG}$ = $V_{AUX}$ and $V_{CHG\_HI}$ = 0 V                             |      | 75   | 100  | μA   |

|                     | attached                                                                                            |                                                                                               |      | 85   | 110  |      |

| IN2                 |                                                                                                     |                                                                                               |      |      |      |      |

| $V_{TH\_UVLO\_IN2}$ | Rising threshold voltage for UVLO                                                                   |                                                                                               | 3.9  | 4.1  | 4.3  | V    |

|                     | Hysteresis <sup>(2)</sup>                                                                           |                                                                                               |      | 100  |      | mV   |

| I <sub>I</sub>      | Disabled supply current                                                                             | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                  |      |      | 1    | μΑ   |

|                     | Enabled supply current with CC lines open                                                           | -40°C ≤ T <sub>J</sub> ≤ 85°C                                                                 |      |      | 1    | μΑ   |

| I <sub>I</sub>      | Enabled supply current with accessory or dangling electronically marked cable signature on CC lines |                                                                                               |      |      | 2    | μΑ   |

|                     | Enabled supply current with UFP                                                                     | $V_{CHG} = 0 \text{ V}, 0 \text{ V} \le V_{CCx} \le 1.5 \text{ V}$                            |      | 98   | 110  |      |

| I <sub>I</sub>      | signature on CC lines<br>(Includes IN current that provides<br>the CC output current to the UFP     | $V_{CHG} = V_{IN}$ and $V_{CHG\_HI} = 0 \text{ V}, 0 \text{ V} \le V_{CCx} \le 1.5 \text{ V}$ |      | 198  | 215  | μΑ   |

|                     | Rd resistor)                                                                                        | 0 V ≤ V <sub>CCx</sub> ≤ 2.45 V                                                               |      | 348  | 373  |      |

| AUX                 |                                                                                                     |                                                                                               |      |      |      |      |

| $V_{TH\_UVLO\_AUX}$ | Rising threshold voltage for UVLO                                                                   |                                                                                               | 2.65 | 2.75 | 2.85 | V    |

|                     | Hysteresis (2)                                                                                      |                                                                                               |      | 100  |      | mV   |

| l <sub>l</sub>      | Disabled supply current                                                                             | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                  |      |      | 1    | μΑ   |

| I <sub>I</sub>      | Enabled internal supply current with CC lines open                                                  | -40°C ≤ T <sub>J</sub> ≤ 85°C                                                                 |      | 0.7  | 3    | μΑ   |

| I <sub>I</sub>      | Enabled supply current with accessory or dangling active cable signature on CC lines                |                                                                                               |      | 140  | 185  | μΑ   |

| I <sub>I</sub>      | Enabled supply current with UFP termination on CC lines and with either IN1 or IN2 in UVLO          | V <sub>IN1</sub> < V <sub>TH_UVLO_IN1</sub> or V <sub>IN2</sub> < V <sub>TH_UVLO_IN2</sub>    |      | 145  | 190  | μΑ   |

| I <sub>I</sub>      | Enabled supply current with UFP termination on CC lines                                             |                                                                                               |      | 55   | 82   | μA   |

# 6.6 Switching Characteristics

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN1}} \le 6.5 \text{ V}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN2}} \le 5.5 \text{ V}$ ,  $2.9 \text{ V} \le \text{V}_{\text{AUX}} \le 5.5 \text{ V}$ ;  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{CHG}\_{\text{HI}}} = \text{V}_{\text{AUX}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                    | PARAMETER                    | TEST CONDITIONS                                                                                                 | MIN  | TYP  | MAX  | UNIT |  |  |  |

|--------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|

| OUT - POWER SWITCH |                              |                                                                                                                 |      |      |      |      |  |  |  |

| t <sub>r</sub>     | Output voltage rise time     | $V_{\text{IN1}}$ = 5 V, C <sub>L</sub> = 1 μF, R <sub>L</sub> = 100 Ω (measured from 10% to 90% of final value) | 1.2  | 1.8  | 2.5  | ms   |  |  |  |

| t <sub>f</sub>     | Output voltage fall time     |                                                                                                                 | 0.35 | 0.55 | 0.75 | ms   |  |  |  |

| t <sub>on</sub>    | Output voltage turn-on time  | V 5V C 4 F D 400 C                                                                                              | 2.5  | 3.5  | 5    | ms   |  |  |  |

| t <sub>off</sub>   | Output voltage turn-off time | $V_{IN1} = 5 \text{ V}, C_L = 1 \mu\text{F}, R_L = 100 \Omega$                                                  | 2    | 3    | 4.5  | ms   |  |  |  |

# **Switching Characteristics (continued)**

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN1}} \le 6.5 \text{ V}$ ,  $4.5 \text{ V} \le \text{V}_{\text{IN2}} \le 5.5 \text{ V}$ ,  $2.9 \text{ V} \le \text{V}_{\text{AUX}} \le 5.5 \text{ V}$ ;  $\text{V}_{\text{EN}} = \text{V}_{\text{CHG}} = \text{V}_{\text{CHG\_HI}} = \text{V}_{\text{AUX}}$ ,  $\text{R}_{\text{REF}} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $\text{I}_{\text{OUT}}$  and  $\text{I}_{\text{OS}}$  defined positive out of the indicated pin (unless otherwise noted)

|                   | PARAMETER                                                       | TEST CONDITIONS                                                                                          | MIN  | TYP  | MAX      | UNIT |

|-------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|----------|------|

| OUT - CI          | JRRENT LIMIT                                                    |                                                                                                          |      |      | <u> </u> |      |

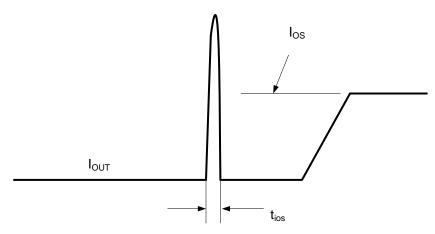

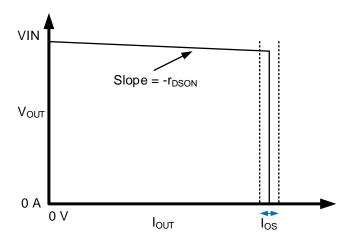

| t <sub>ios</sub>  | Current limit response time to short circuit                    | $V_{IN1}$ - $V_{OUT}$ = 1 V, $R_L$ = 10 m $\Omega$ , see Figure 1                                        |      | 1.5  | 4        | μs   |

| FAULT             |                                                                 |                                                                                                          |      |      |          |      |

| t <sub>DEGA</sub> | Asserting deglitch due to over current                          |                                                                                                          | 5.5  | 8.2  | 10.7     | ms   |

| t <sub>DEGA</sub> | Asserting deglitch due to over temperature in current limit (1) |                                                                                                          |      | 0    |          | ms   |

| t <sub>DEGD</sub> | De-asserting deglitch                                           |                                                                                                          | 5.5  | 8.2  | 10.7     | ms   |

| LD_DET            |                                                                 |                                                                                                          |      |      |          |      |

| t <sub>DEGA</sub> | Asserting deglitch                                              |                                                                                                          | 45   | 65   | 85       | ms   |

| t <sub>DEGD</sub> | De-asserting deglitch                                           |                                                                                                          | 1.45 | 2.15 | 2.9      | S    |

| OUT - DI          | SCHARGE                                                         | ,                                                                                                        |      |      |          |      |

|                   | R <sub>DCHG</sub> discharge time                                | V <sub>OUT</sub> = 1 V, time I <sub>SNK_OUT</sub> > 1 mA<br>after UFP signature removed from<br>CC lines | 39   | 65   | 96       | ms   |

| CC1/CC2           | 2 - V <sub>CONN</sub> POWER SWITCH                              |                                                                                                          |      |      | '        |      |

| t <sub>r</sub>    | Output voltage rise time                                        | $V_{IN2} = 5 \text{ V}, C_L = 1 \mu\text{F}, R_L = 100 \Omega$                                           | 0.15 | 0.25 | 0.35     | ms   |

| t <sub>f</sub>    | Output voltage fall time                                        | (measured from 10% to 90% of final value)                                                                | 0.18 | 0.22 | 0.26     | ms   |

| t <sub>on</sub>   | Output voltage turn-on time                                     | $V_{IN2} = 5 \text{ V, } C_{I} = 1 \mu\text{F, } R_{I} = 100 \Omega$                                     | 1    | 1.5  | 2        | ms   |

| $t_{\text{off}}$  | Output voltage turn-off time                                    | $V_{1N2} = 5 \text{ V}, C_L = 1  \mu\text{F}, R_L = 100  \Omega$                                         | 0.3  | 0.4  | 0.55     | ms   |

| CC1/CC2           | 2 - V <sub>CONN</sub> POWER SWITCH - CURRENT                    | LIMIT                                                                                                    |      |      |          |      |

| t <sub>res</sub>  | Current limit response time to short circuit                    | $V_{IN2} - V_{CONN} = 1 \text{ V, R} = 10 \text{ m}\Omega, \text{ see}$ Figure 1                         |      | 1    | 3        | μs   |

| UFP, PO           | L, AUDIO, DEBUG                                                 |                                                                                                          |      |      |          |      |

| t <sub>DEGR</sub> | Asserting deglitch                                              |                                                                                                          | 100  | 150  | 200      | ms   |

| t <sub>DEGF</sub> | De-asserting deglitch                                           |                                                                                                          | 7.9  | 12.5 | 17.7     | ms   |

(1) These parameters are provided for reference only and do not constitute part of TI's published specifications for purposes of TI's product warranty.

Figure 1. Output Short Circuit Parameter Diagram

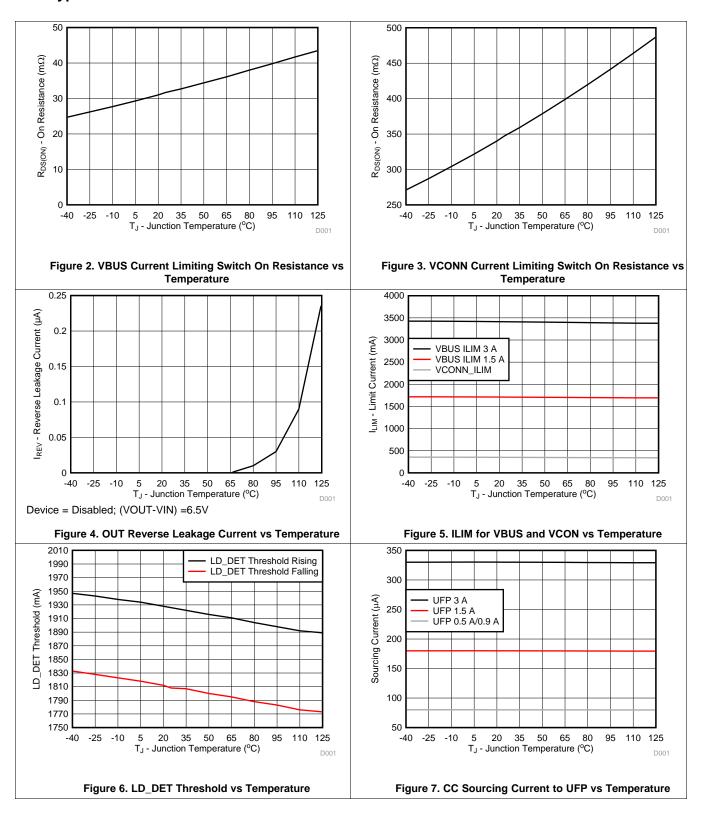

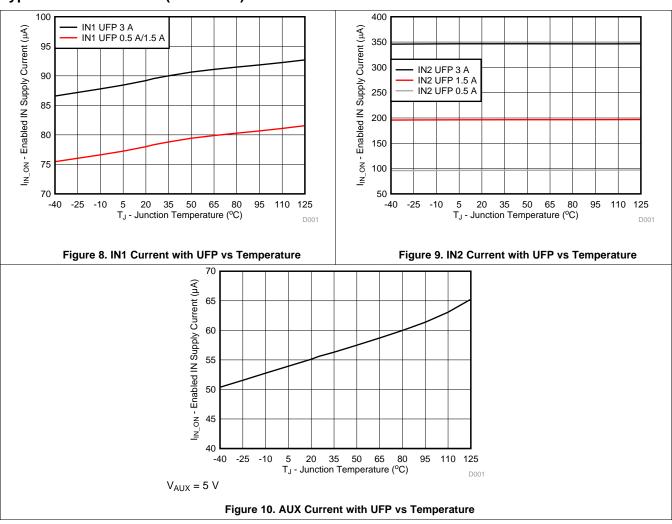

# 6.7 Typical Characteristics

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

# 7 Detailed Description

#### 7.1 Overview

The TPS25810 is a highly integrated USB Type-C Downstream Facing Port (DFP) controller with built-in power switch developed for the new USB Type-C connector and cable. The part provides all functionality needed to support a USB Type C DFP in a system where USB power delivery (PD) source capabilities (for example, VBUS > 5 V) are not implemented. The device is designed to be compliant to Type-C spec revision 1.2.

# 7.1.1 USB Type C Basic

For a detailed description of the Type-C spec refer to the USB-IF website to download the latest released version. Some of the basic concepts of the Type-C spec that pertains to understanding the operation of the TPS25810 (a DFP device) are described as follows.

USB Type-C removes the need for different plug and receptacle types for host and device functionality. The Type-C receptacle replaces both Type-A and Type-B receptacle since the Type-C cable is plug-able in either direction between host and device. A host-to-device logical relationship is maintained via the configuration channel (CC). Optionally hosts and devices can be either providers or consumers of power when USB PD communication is used to swap roles.

All USB Type-C ports operate in one of below three data modes:

- Host mode: the port can only be host (provider of power)

- Device mode: the port can only be device (consumer of power)

- Dual-Role mode: the port can be either host or device

#### Port types:

- DFP (Downstream Facing Port): Host

- · UFP (Upstream Facing Port): Device

- DRP (Dual-Role Port): Host or Device

## Valid DFP-to-UFP connections:

- Table 1 describes valid DFP-to-UFP connections

- · Host to Host or Device to Device have no functions

#### **Table 1. DFP-to-UFP Connections**

|                  | HOST-MODE PORT | DEVICE-MODE<br>PORT | DUAL-ROLE PORT       |

|------------------|----------------|---------------------|----------------------|

| Host-Mode Port   | No Function    | Works               | Works                |

| Device-Mode Port | Works          | No Function         | Works                |

| Dual-Role Port   | Works          | Works               | Works <sup>(1)</sup> |

<sup>(1)</sup> This may be automatic or manually driven.

#### 7.1.2 Configuration Channel

The function of the configuration channel is to detect connections and configure the interface across the USB Type-C cables and connectors.

Functionally the Configuration Channel (CC) is used to serve the following purposes:

- Detect connect to the USB ports

- Resolve cable orientation and twist connections to establish USB data bus routing

- Establish DFP and UFP roles between two connected ports

- Discover and configure power: USB Type-C current modes or USB Power Delivery

- Discovery and configure optional Alternate and Accessory modes

- · Enhances flexibility and ease of use

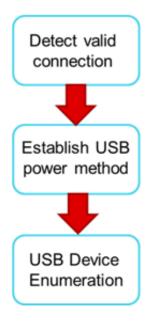

Typical flow of DFP to UFP configuration is shown in Figure 11:

Figure 11. Flow of DFP to UFP Configuration

#### 7.1.3 Detecting a Connection

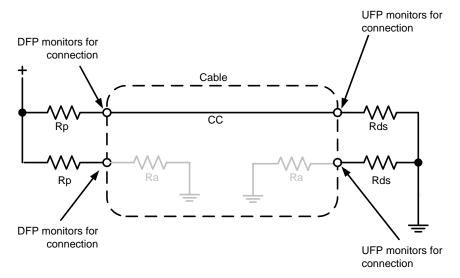

DFPs and DRPs fulfill the role of detecting a valid connection over USB Type-C. Figure 12 shows a DFP to UFP connection made with Type C cable. As shown in Figure 12, the detection concept is based on being able to detect terminations in the product which has been attached. A pull-up and pull-down termination model is used. A pull-up termination can be replaced by a current source.

- In the DFP-UFP connection the DFP monitors both CC pins for a voltage lower than the unterminated voltage.

- An UFP advertises Rd on both its CC pins (CC1 and CC2).

- A powered cable advertises Ra on only one of CC pins of the plug. Ra is used to inform the source to apply VCONN.

- An analog audio device advertises Ra on both CC pins of the plug, which identifies it as an analog audio device. VCONN is not applied on either CC pin in this case.

Figure 12. DFP-UFP Connection

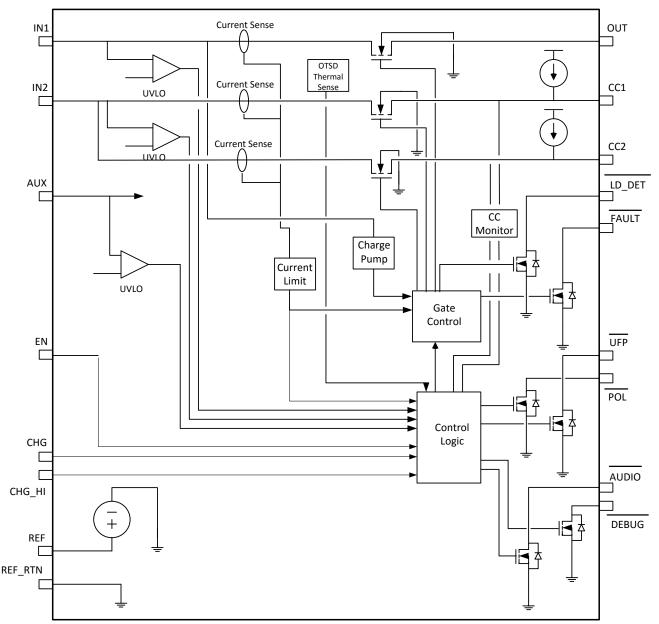

# 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

## 7.3 Feature Description

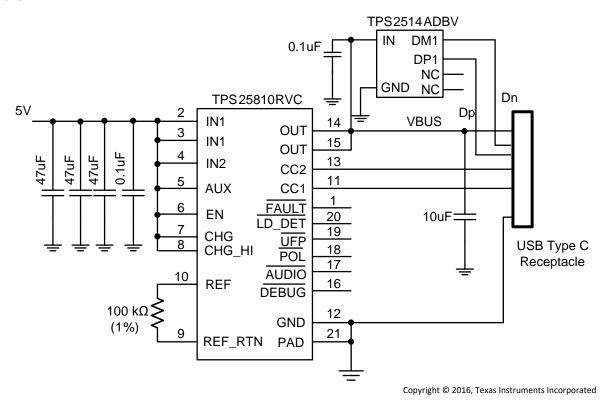

The TPS25810 is a DFP Type C port controller with integrated power switch for VCONN and VBUS. The TPS25810 does not support BC1.2 charging modes since it does not interact with USB D+/D- data lines. It can be used in conjunction with a BC 1.2 device like the TPS2514A, to support BC1.2 and Type C charging modes in a single Type C DFP port. See the TPS25810 EVM user's guide (SLVUAI0) and *Application and Implementation* section of this data sheet for more details. The TPS25810 can be used in a USB 2.0 only or USB 3.1 port implementation. When used in a USB 3.1 port, the TPS25810 can control an external super speed MUX to handle the Type C flippable feature.

# **Feature Description (continued)**

#### 7.3.1 Configuration Channel Pins CC1 and CC2

The TPS25810 has two pins, CC1 and CC2 that serve to detect an attachment to the port and resolve cable orientation. These pins are also used to establish current broadcast to a valid UFP, configure VCONN, and detect Debug or Audio Adapter Accessory attachment.

Table 2 lists TPS25810 response to various attachments to its port.

Table 2. TPS25810 Response

|                                      |      |      | TPS25810 RESPONSE <sup>(1)</sup> |                                       |      |      |       |       |  |  |

|--------------------------------------|------|------|----------------------------------|---------------------------------------|------|------|-------|-------|--|--|

| TPS25810 TYPE C PORT                 | CC1  | CC2  | OUT                              | V <sub>CONN</sub><br>On CC1 or<br>CC2 | POL  | UFP  | AUDIO | DEBUG |  |  |

| Nothing Attached                     | OPEN | OPEN | OPEN                             | NO                                    | Hi-Z | Hi-Z | Hi-Z  | Hi-Z  |  |  |

| UFP Connected                        | Rd   | OPEN | IN1                              | NO                                    | Hi-Z | LOW  | Hi-Z  | Hi-Z  |  |  |

| UFP Connected                        | OPEN | Rd   | IN1                              | NO                                    | LOW  | LOW  | Hi-Z  | Hi-Z  |  |  |

| Powered Cable/No UFP<br>Connected    | OPEN | Ra   | OPEN                             | NO                                    | Hi-Z | Hi-Z | Hi-Z  | Hi-Z  |  |  |

| Powered Cable/No UFP<br>Connected    | Ra   | OPEN | OPEN                             | NO                                    | Hi-Z | Hi-Z | Hi-Z  | Hi-Z  |  |  |

| Powered Cable/UFP<br>Connected       | Rd   | Ra   | IN1                              | CC2                                   | Hi-Z | LOW  | Hi-Z  | Hi-Z  |  |  |

| Powered Cable/UFP<br>Connected       | Ra   | Rd   | IN1                              | CC1                                   | LOW  | LOW  | Hi-Z  | Hi-Z  |  |  |

| Debug Accessory Connected            | Rd   | Rd   | OPEN                             | NO                                    | Hi-Z | Hi-Z | Hi-Z  | LOW   |  |  |

| Audio Adapter Accessory<br>Connected | Ra   | Ra   | OPEN                             | NO                                    | Hi-Z | Hi-Z | LOW   | Hi-Z  |  |  |

<sup>(1)</sup> POL, UFP, AUDIO, and DEBUG are open drain outputs; pull high with 100 kΩ to AUX when used. Tie to GND or leave open when not used.

#### 7.3.2 Current Capability Advertisement and Overload Protection

The TPS25810 supports all three Type-C current advertisements as defined by the USB Type C standard. Current broadcast to a connected UFP is controlled by the CHG and CHG\_HI pins. For each broadcast level the device protects itself from a UFP that draws current in excess of the port's USB Type-C Current advertisement by setting the current limit as shown in Table 3.

Table 3. USB Type-C Current Advertisement

| CHG | CHG_HI | CC CAPABILITY<br>BROADCAST | CURRENT LIMIT (typ) | LOAD DETECT<br>THRESHOLD (typ) |

|-----|--------|----------------------------|---------------------|--------------------------------|

| 0   | 0      | STD                        | 1.7 A               | NA                             |

| 0   | 1      | STD                        | 1.7 A               | NA                             |

| 1   | 0      | 1.5 A                      | 1.7 A               | NA                             |

| 1   | 1      | 3 A                        | 3.4 A               | 1.95 A                         |

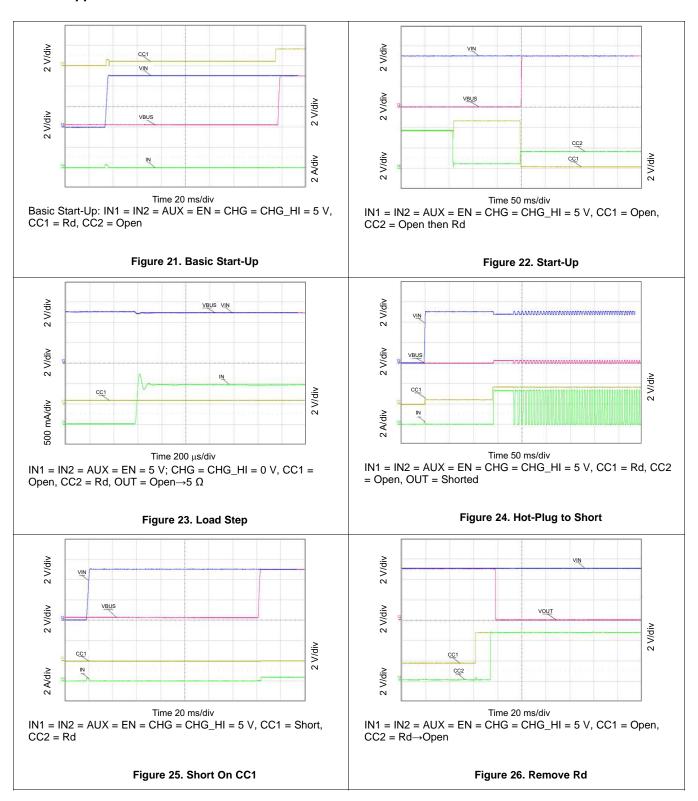

Under overload conditions, the internal current-limit regulator limits the output current to selected ILIM for OUT and fixed internal VCONN current limit as shown in the *Electrical Characteristics*. When an overload condition is present, the device maintains a constant output current, with the output voltage determined by ( $i_{OS}$  x RLOAD). Two possible overload conditions can occur. The first overload condition occurs when either: 1) input voltage is first applied, enable is true, and a short circuit is present (load which draws IOUT >  $i_{OS}$ ), or 2) input voltage is present and the TPS25810 is enabled into a short circuit. The output voltage is held near zero potential with respect to ground and the TPS25810 ramps the output current to  $i_{OS}$ . The TPS25810 limits the current to  $i_{OS}$  until the overload condition is removed or the device begins to thermal cycle. This is demonstrated in Figure 24 where the device was enabled into a short, and subsequently cycles current off and on as the thermal protection engages.

The second condition is when an overload occurs while the device is enabled and fully turned on. The device responds to the overload condition within time  $i_{OS}$  (see Figure 1) when the specified overload (per *Electrical Characteristics*) is applied. The response speed and shape vary with the overload level, input circuit, and rate of application. The current-limit response varies between simply settling to  $i_{OS}$  or turnoff and controlled return to  $i_{OS}$ . Similar to the previous case, the TPS25810 limits the current to  $i_{OS}$  until the overload condition is removed or the device begins to thermal cycle.

The TPS25810 thermal cycles if an overload condition is present long enough to activate thermal limiting in any of the above cases. This is due to the relatively large power dissipation [(VIN - VOUT) x i<sub>OS</sub>] driving the junction temperature up. The device turns off when the junction temperature exceeds 135°C (min) while in current limit. The device remains off until the junction temperature cools 20°C and then restarts. The TPS25810 current limit profile is shown in Figure 13.

Figure 13. Current Limit Profile

#### 7.3.3 Undervoltage Lockout (UVLO)

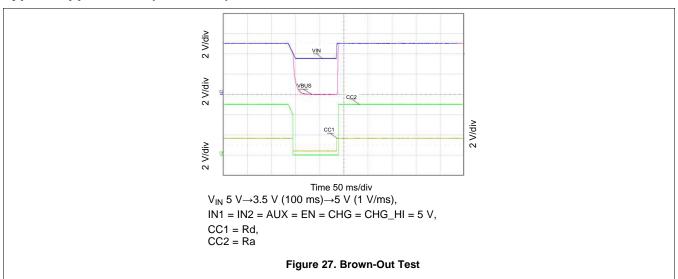

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted on/off cycling due to input voltage droop during turn on.

#### 7.3.3.1 Device Power Pins (IN1, IN2, AUX, OUT, and GND)

The device has multiple input power pins; IN1, IN2 and AUX. IN1 is connected to OUT by the internal power FET and serves the supply for the Type-C charging current. IN2 is the supply for VCONN and ties directly between the VCONN power switch on its input and CC1 or CC2 on its output. AUX or auxiliary input supply provides power to the chip. Refer to *Functional Block Diagram*.

In the simplest implementation where multiple supplies are not available; IN1, IN2, and AUX can be tied together. However in mobile systems (battery powered) where system power savings is paramount, IN1 and IN2 can be powered by the high power DC-DC supply (>3-A capability) while AUX can be connected to the low power supply that typically powers the system uC when the system is in hibernate or sleep power state. Unlike IN1 and IN2, AUX can operate directly from a 3.3-V supply commonly used to power the uC when the system is put in low power mode. A ceramic bypass capacitor close to the device from IN/AUX to GND is recommended to alleviate bus transients.

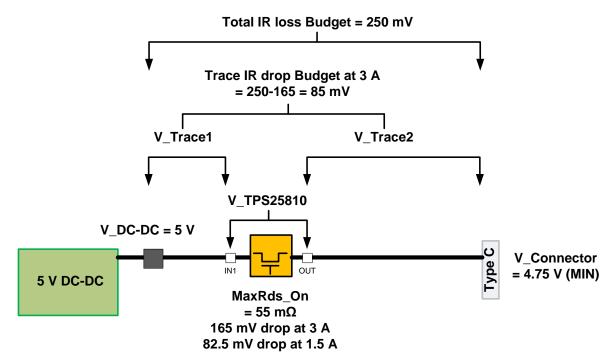

The recommended operating voltage range for IN1/IN2 is 4.5 V to 5.5 V while AUX can be operated from 2.9 V to 5.5 V. However IN1, the high power supply, can operate up to 6.5 V. This higher input voltage affords a larger IR drop budget in systems where a long cable harness is used and results in high IR drops with 3-A charging current. Increasing IN1 beyond 5.5 V enables longer cable/board trace lengths between the device and Type C receptacle while meeting the USB spec for VBUS at connector ≥ 4.75 V.

Figure 14 illustrates the point. In this example IN1 is at 5 V which restricts the IR drop budget from DC-DC to connector to 250 mV.

Figure 14. Total IR Loss Budget

### 7.3.3.2 FAULT Response

The FAULT pin is an open drain output that asserts (active low) when device OUT current exceeds its programmed value and the over temperature threshold is crossed (T<sub>TH\_OTSD1</sub>). Refer to the *Electrical Characteristics* for over current and temperature values. The FAULT signal remains asserted until the fault condition is removed and the device resumes normal operation. The TPS25810 is designed to eliminate false overcurrent fault reporting by using an internal deglitch circuit.

Connect FAULT with a pull-up resistor to AUX. FAULT can be left open or tied to GND when not used.

#### 7.3.3.3 Thermal Shutdown

The device has two internal over temperature shutdown thresholds,  $T_{TH\_OTSD1}$  and  $T_{TH\_OTSD2}$ , to protect the internal FET from damage and overall safety of the system.  $T_{TH\_OTSD2} > T_{TH\_OTSD1}$ . FAULT is asserted low to signal a fault condition when device temperature exceeds  $T_{TH\_OTSD1}$  and the current limit switch is disabled. However when  $T_{TH\_OTSD2}$  is exceeded all open drain outputs are left open and the device is disabled such that minimum power/heat is dissipated. The device attempts to power-up when die temperature decreases by 20°C.

#### 7.3.3.4 REF

A 100-k $\Omega$  (1% or better recommended) resistor is connected from this pin to REF\_RTN. This pin sets the reference current required to bias the internal circuitry of the device. The overload current limit tolerance and CC currents depend upon the accuracy of this resistor, using a  $\pm 1\%$  low tempco resistor, or better, yields the best current limit accuracy and overall device performance.

## 7.3.3.5 Audio Accessory Detection

The USB Type-C spec defines an audio adapter decode state which allows implementation of an analog USB Type-C to 3.5-mm headset adapter. The TPS25810 detects an audio accessory device when both  $\underline{CC1}$  and  $\underline{CC2}$  pins sees  $V_{Ra}$  voltage (when pulled to ground by Ra resistor). The device asserts the open drain  $\overline{AUDIO}$  pin low to indicate the detection of such a device.

Product Folder Links: TPS25810

Copyright © 2015-2017, Texas Instruments Incorporated

#### Table 4. Audio Accessory Detection

| CC1 |    |                       | STATE                             |  |  |

|-----|----|-----------------------|-----------------------------------|--|--|

| Ra  | Ra | Asserted (pulled low) | Audio Adapter Accessory Connected |  |  |

Platforms supporting this extension can trigger off of the  $\overline{\text{AUDIO}}$  pin to enable accessory mode circuits to support the audio function. When the Ra pull-down is removed from the CC2 pin,  $\overline{\text{AUDIO}}$  is de-asserted or pulled high. The TPS25810 monitors the CC2 pin for audio device detach. When this function is not needed (for example in a data-less port)  $\overline{\text{AUDIO}}$  can be tied to GND or left open.

#### 7.3.3.6 Debug Accessory Detection

The Type-C spec supports an optional Debug Accessory mode used for debug only and must not be used for communicating with commercial products. When the <u>TPS25810</u> detects  $V_{Rd}$  voltage on both CC1 and CC2 pins (when pulled to ground by an Rd resistor), it asserts  $\overline{DEBUG}$  low. With  $\overline{DEBUG}$  is asserted, the system can enter debug mode for factory testing or a similar functional mode.  $\overline{DEBUG}$  de-asserts or pulls high when Rd is removed from CC1. The TPS25810 monitors the CC1 pin for Debug Accessory detach.

If Debug accessory mode is not used, tie DEBUG to GND or leave it open.

## **Table 5. Debug Accessory Detection**

| CC1 | CC2 | POL                   | STATE                          |  |  |

|-----|-----|-----------------------|--------------------------------|--|--|

| Rd  | Rd  | Asserted (pulled low) | Debug Accessory Mode connected |  |  |

# 7.3.3.7 Plug Polarity Detection

Reversible Type-C plug orientation is reported by the  $\overline{POL}$  pin when a UFP is connected. However when no UFP is attached,  $\overline{POL}$  remains de-asserted irrespective of cable plug orientation. Table 6 describes the  $\overline{POL}$  state based on which device CC pin detects  $V_{RD}$  from an attached UFP pull-down.

# **Table 6. Plug Polarity Detection**

| CC1  | CC2  | POL                   | STATE                                       |

|------|------|-----------------------|---------------------------------------------|

| Rd   | Open | Hi-z                  | UFP connected                               |

| Open | Rd   | Asserted (pulled low) | UFP connected with reverse plug orientation |

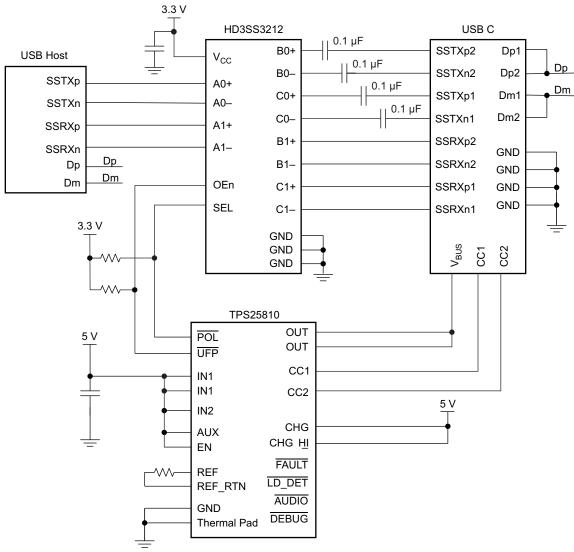

Figure 15 shows an example implementation which utilizes the POL terminal to control the SEL terminal on the HD3SS3212. The HD3SS3212 provides switching on the differential channels between Port B and Port C to Port A depending on cable orientation.

Copyright © 2016, Texas Instruments Incorporated

Figure 15. Example Implementation

#### 7.3.3.8 Device Enable Control

The logic enable pin controls the power switch and device supply current. The supply current is reduced to less than 1  $\mu$ A when a logic low is present on EN. The EN pin provides a convenient way to turn on or turn off the device while it is powered. The enable input threshold has hysteresis built-in. When this pin is pulled high, the device is turned on or enabled. When the device is disabled (EN pulled low) the internal FETs tied to IN1 and IN2 are disconnected, all open drain outputs are left open (Hi-Z), and the CC1/CC2 monitor block is turned off. The EN terminal should not be left floating.

#### 7.3.3.9 Load Detect

The load detect function in the device is enabled when it is set to broadcast high current  $V_{BUS}$  charging (CHG = CHG\_HI = High) on the CC pin. In this mode the device monitors the current to a UFP; if the current exceeds 1.95 A (TYP) the LD\_DET pin asserts. Since LD\_DET is an open drain output, pull it high with 100 k $\Omega$  to AUX when used; tie it to GND or leave open when not used.

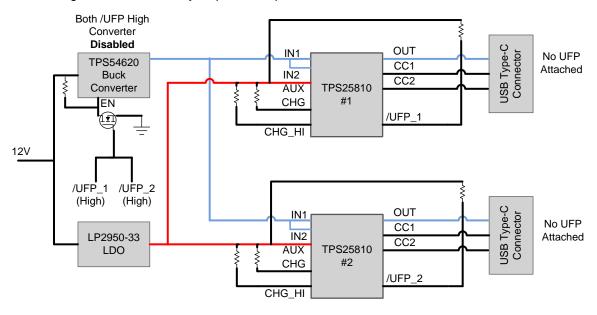

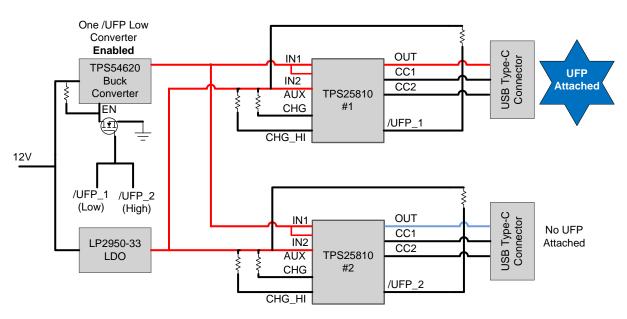

#### 7.3.3.10 Power Wake

The power wake feature supported in the TPS25810 offers the mobile systems designer a way to save on system power when no UFP is attached to the Type-C port. Refer to Figure 16. To enable power wake the UFP from device #1 and #2 are tied together (each with its own 100-k $\Omega$  pull-up) to the enable pin of a 5 V/6 A dc-dc buck converter. When no UFP is detected on both Type-C ports, the EN pin of the dc-dc is pulled high thereby disabling it. Since both TPS25810s are powered by an always-on 3.3-V LDO, turning off the IN1/IN2 supply does not affect its operation in detach state. Anytime a UFP is detected on either port, the corresponding TPS25810 UFP pin is pulled low enabling the dc-dc to provide charging current to the attached UFP. Turning off the high power dc-dc when ports are unattached saves on system power. This method can save a significant amount of power considering the TPS25810 only requires < 5  $\mu$ A when no UFP device is connected.

Copyright © 2016, Texas Instruments Incorporated

Figure 16. Power Wake Implementation

### 7.3.3.11 Port Power Management (PPM)

PPM is the intelligent and dynamic allocation of power made possible with the use of the LD\_DET pin. It is for systems that have multiple charging ports but cannot power them all at their maximum charging current simultaneously.

#### Goals of PPM are:

- 1. Enhances user experience since user does not have to search for high current charging port.

- 2. Lowered cost and size of power supply needed for implementing high current charging in a multi-port system.

#### 7.3.3.12 Implementing PPM in a System with Two Type-C Ports

Figure 17 shows PPM and power wake implemented in a system with two Type C ports both initially set to broadcast high current charging (3 A, CHG and CHG\_HI pulled high via a 100 k $\Omega$  to AUX). To enable PPM tie the LD\_DET pin from TPS25810 #1 to CHG\_HI of TPS25810 #2 and vice versa as shown in Figure 17. Each device independently monitors charging current drawn by its attached UFP.

IN1, IN2 are connected to a TPS54620; a 6-A synchronous step-down converter. AUX is powered by a LP2950-33; a low quiescent current 3.3-V LDO. With no UFP attached to either Type C port the TPS25810 is powered by the LP2950-33. This method saves a significant amount of power considering the TPS25810 requires less than 2 µA when no USB device is connected.

Copyright © 2016, Texas Instruments Incorporated

Figure 17. PPM and Power Wake Implemented

#### 7.3.3.13 PPM Operation

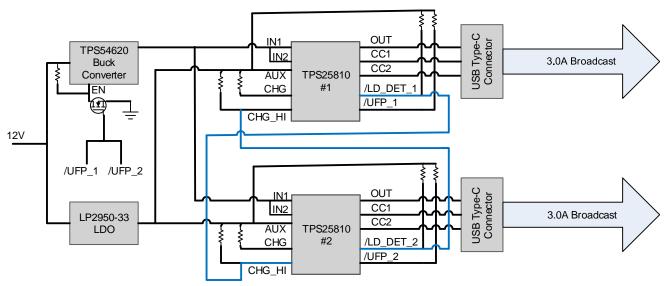

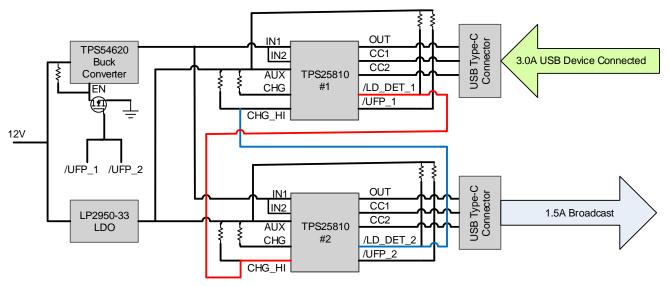

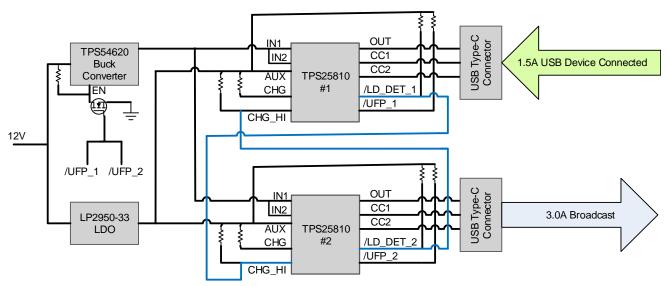

When no UFP is attached, or either of the two attached UFP is drawing current less than the \(\overline{LD\_DET}\) threshold (1.95 A typical), the \(\overline{LD\_DET}\) output for both devices is high (shown in blue in Figure 18). Now when a UFP is attached to device #1 that draws a charging current higher than the \(\overline{LD\_DET}\) threshold (1.95 A), this causes \(\overline{LD\_DET}\) to assert or pull-low (shown in red in Figure 18). Since the \(\overline{LD\_DET}\) pins of the #1 and #2 devices are connected to the other devices CHG\_HI pin, a high current detection on device #1 forces device #2 to broadcast 1.5 A or medium charging current capability on its CC pin. The Type C specification requires a UFP to monitor the CC pins continuously and adjust its current consumption (within 60 ms) to remain within the value advertised by the DFP.