Sample &

🖥 Buy

参考資料

#### bq76925

JAJSBH1D-JULY 2011-REVISED OCTOBER 2016

# bq76925 ホスト制御アナログ・フロント・エンド、3~6直列セル、Li イオン/Liポリマー・バッテリ保護および気体測定アプリケーション向け

Technical

Documents

#### 特長 1

- ホストによるセル測定用のアナログ・インター フェイス

- セル入力マルチプレクサ、レベル・シフタ、スケーラ

- 1.5/3.0Vの低ドリフト、較正済み基準電圧により、 正確なA/D変換

- ホストによる電流測定用のアナログ・インター フェイス

- 可変ゲインの電流センス・アンプで、1mΩのセンス 抵抗とともに動作可能

- ホストによる温度測定のため、サーミスタのバイ アス出力を切り替え可能

- スレッショルドを動的に変更可能な過電流コンパ レータ

- 過電流フォルトの可能性をホストに警告

- 負荷接続時にホストをウェークアップ

- セル・バランシングFETを内蔵

- 個別のホスト制御

- セルごとに50mAのバランシング電流

- セル・センスラインの断線検出をサポート

- 内蔵の3.3Vレギュレータによりマイクロコント ローラやLEDに電力を供給

- ホスト通信用のI<sup>2</sup>Cインターフェイス - (オプション) パケットCRCによる堅牢な動作

- 電源電圧範囲: 4.2~26.4V

- 低消費電力

- ノーマル・モード: 40µA (標準値)

- スリープ・モード: 1.5µA (最大値)

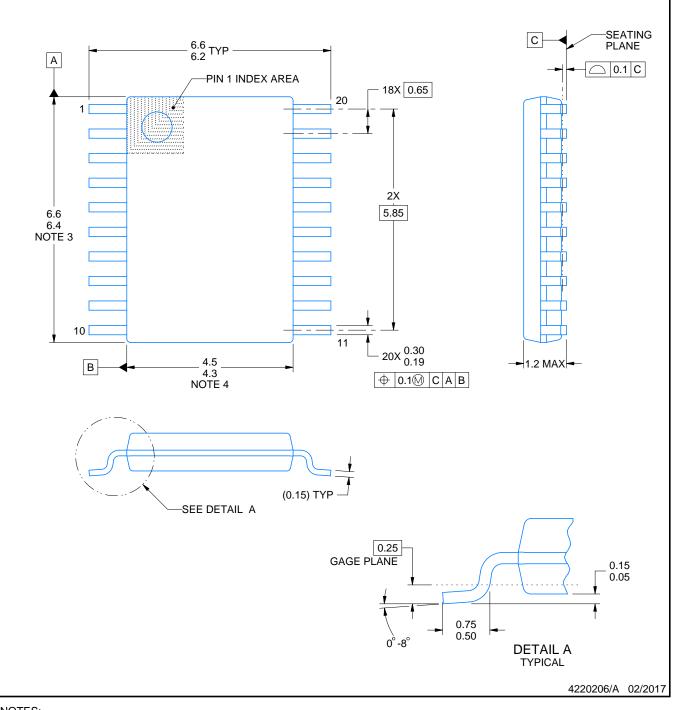

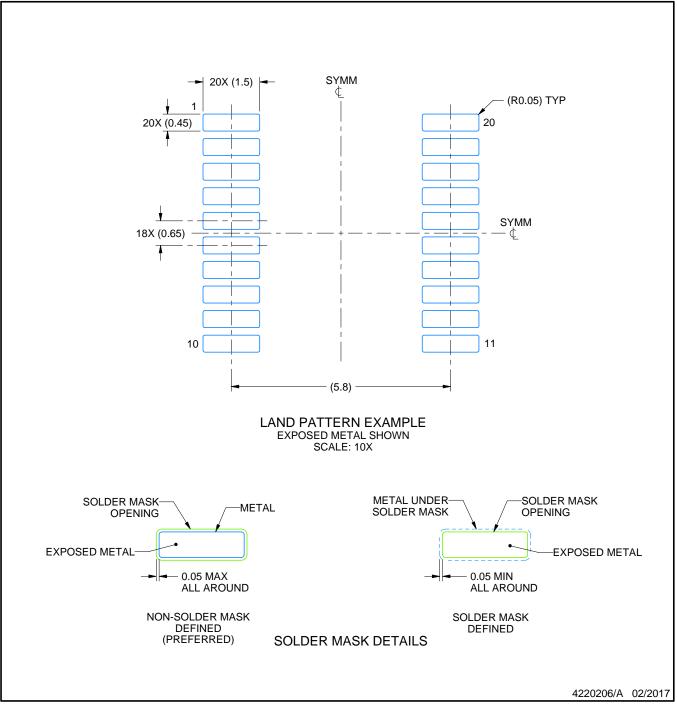

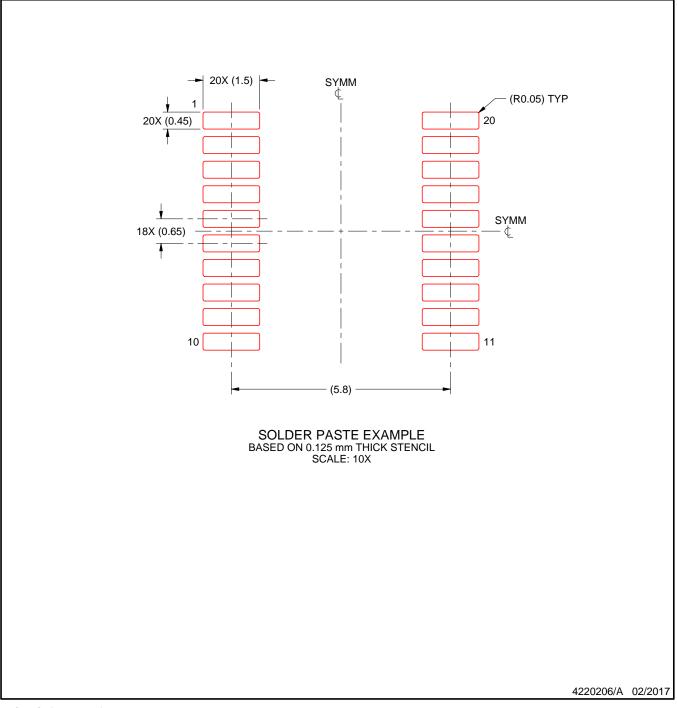

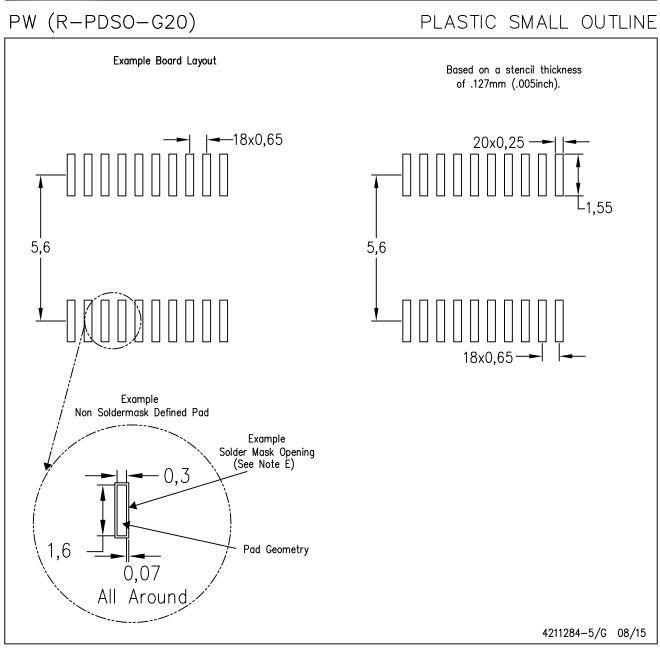

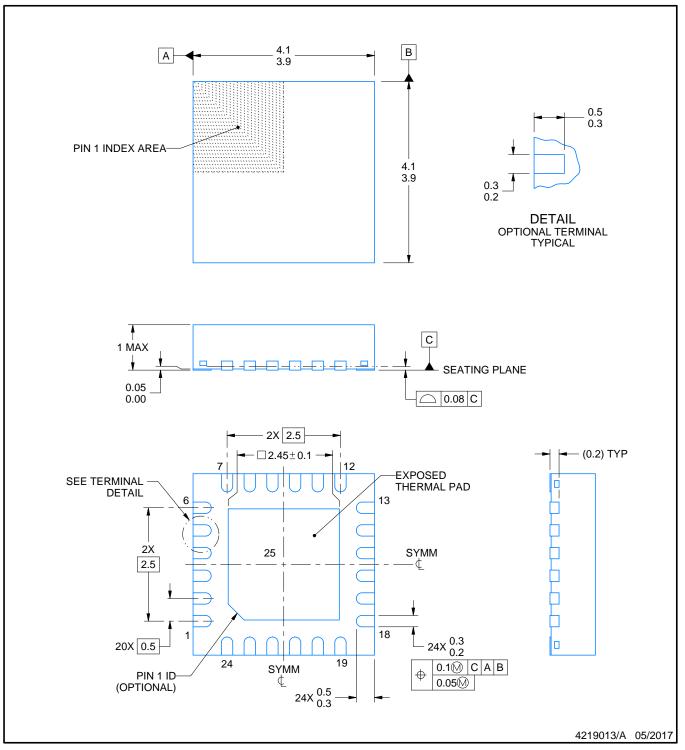

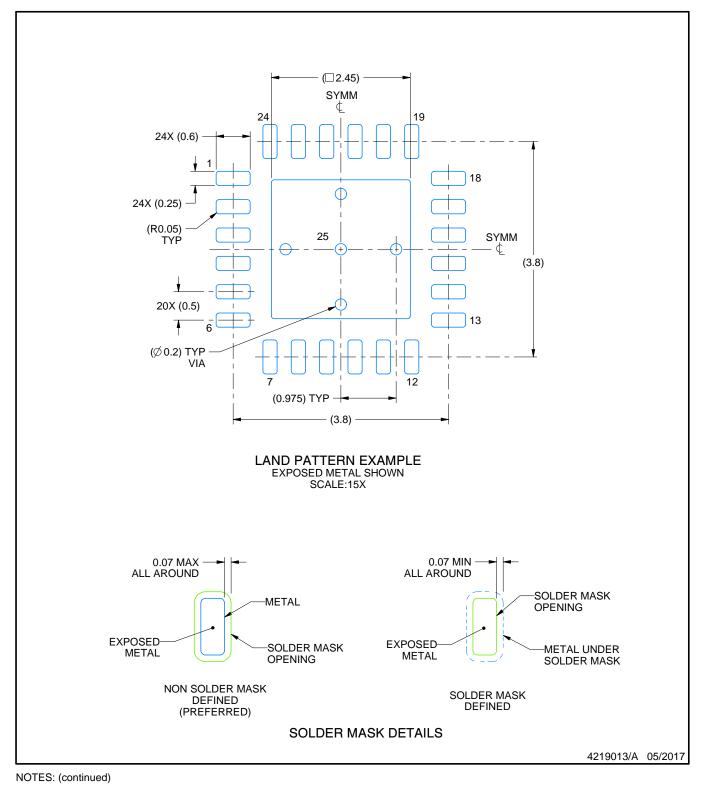

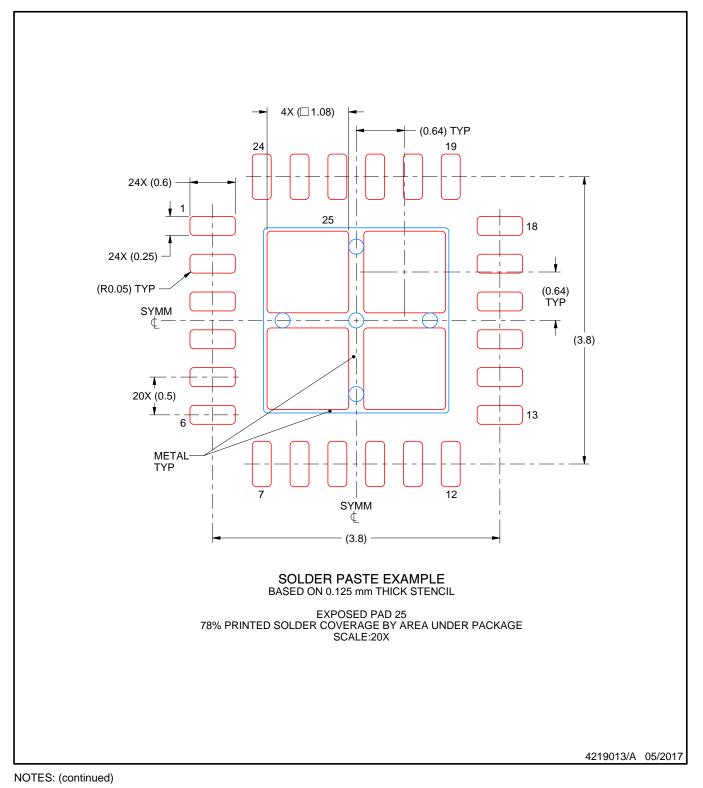

- 20ピンTSSOPまたは24ピンVQFNパッケージ

# 2 アプリケーション

- Liイオン・バッテリ・パックの主要な保護機能

- コードレス電動工具

- 小型電動車両(電動自転車、スクーターなど)

- UPSシステム

- 医療用機器

- 携帯用テスト機器

# 3 概要

Tools &

Software

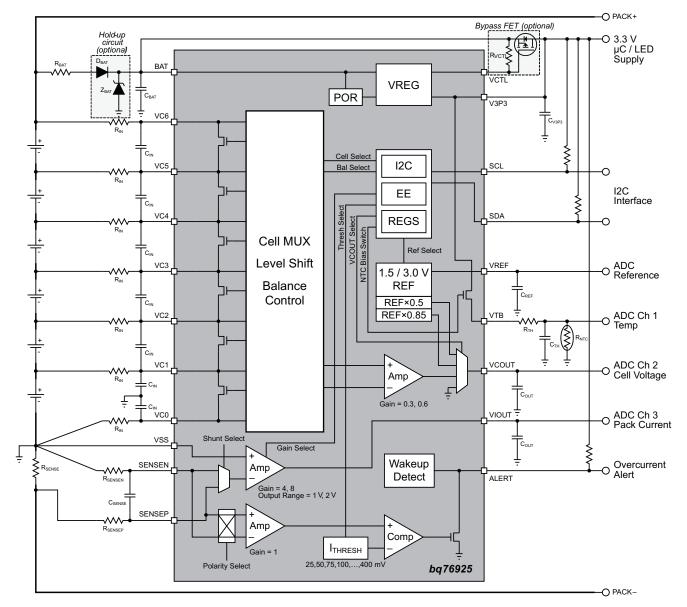

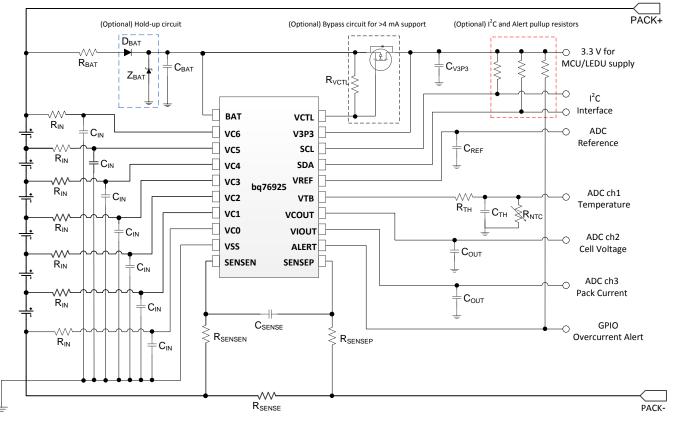

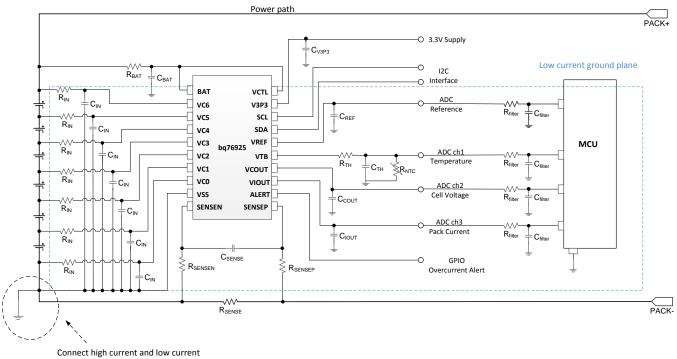

bg76925ホスト制御アナログ・フロント・エンド(AFE)は、3、 4、5、6セルを直列に接続したLiイオンおよびLiポリマー・ バッテリ向けに、パック監視、バランシング、保護の統合シ ステムを提供します。bg76925により、ホスト・コントローラ は個々のセルの電圧、パック電流、温度を簡単に監視で きます。ホストはこの情報を使用して、過電圧、低電圧、過 熱、過電流などの安全でない動作状態や障害状態、セル のアンバランス、充電状態、健全性状態などを検出できま す。

Support &

Community

20

セル入力電圧はレベル・シフト、多重化、スケーリングを経 て出力され、ホストADCで測定されます。専用ピンから低ド リフトの較正済み基準電圧が供給されるため、正確な測定 が可能です。

**製品情報**<sup>(1)</sup>

|         | 200011710  |               |

|---------|------------|---------------|

| 型番      | パッケージ      | 本体サイズ(公称)     |

| bq76925 | TSSOP (20) | 4.00mm×4.00mm |

| bq76925 | VQFN (24)  | 6.50mm×4.40mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

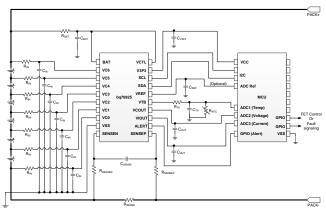

概略回路図

# 目次

| 特長                                         | 1 | 8 De  | etailed Description           | 11 |

|--------------------------------------------|---|-------|-------------------------------|----|

| アプリケーション                                   | 1 | 8.1   | 1 Overview                    | 11 |

| 概要                                         | 1 | 8.2   | 2 Functional Block Diagram    | 12 |

| 改訂履歴                                       |   | 8.3   | 3 Feature Description         | 12 |

| 概要(続き)                                     |   | 8.4   | 4 Device Functional Modes     | 18 |

| Pin Configuration and Function             |   | 8.5   |                               |    |

| Specifications                             |   | 8.6   | 6 Register Maps               | 21 |

| 7.1 Absolute Maximum Ratings               |   | 9 Ap  | oplication and Implementation | 27 |

| 7.2 ESD Ratings                            |   | 9.1   | 1 Application Information     | 27 |

| 7.3 Recommended Operating Cor              |   | 9.2   | 2 Typical Application         | 28 |

| 7.4 Thermal Information                    |   | 10 Pc | ower Supply Recommendations   | 31 |

| 7.5 Electrical Characteristics: Sup        |   | 11 La | ayout                         | 31 |

| 7.6 Internal Power Control (Startu         |   | 11    | 1.1 Layout Guidelines         | 31 |

| 7.7 3.3-V Voltage Regulator                | , | 11    | 1.2 Layout Example            | 31 |

| 7.8 Voltage Reference                      |   | 12 デ  | バイスおよびドキュメントのサポート             | 33 |

| 7.9 Cell Voltage Amplifier                 |   | 12    | 2.1 ドキュメントのサポート               | 33 |

| 7.10 Current Sense Amplifier               |   | 12    | 2.2 ドキュメントの更新通知を受け取る方法        | 33 |

| 7.11 Overcurrent Comparator                |   | 12    | 2.3 コミュニティ・リソース               | 33 |

| 7.12 Internal Temperature Measur           |   | 12    | 2.4 商標                        | 33 |

| 7.13 Cell Balancing and Open Cel           |   | 12    | 2.5 静電気放電に関する注意事項             | 33 |

| 7.14 I <sup>2</sup> C Compatible Interface |   | 12    | 2.6 Glossary                  | 33 |

| 7.15 Typical Characteristics               |   | 13 乄  | カニカル、パッケージ、および注文情報            |    |

# 4 改訂履歴

1

2

3

4

5

6

7

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Revision C (July 2015) から Revision D に変更

| • | Added test condition n = 1 – 5 at 25°C and MAX value for $I_{VCn}$ parameter |

|---|------------------------------------------------------------------------------|

| • | 追加「ドキュメントの更新通知を受け取る方法」セクション 33                                               |

#### Revision B (December 2011) から Revision C に変更

| •  | 「ESD定格」の表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に<br>関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケー<br>ジ、および注文情報」セクションを追加                                                                                                                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | コンテンツを新しいセクションに移動し、対応するセクション、図、表、ドキュメントへのハイパーリンクを追加                                                                                                                                                                                                                         |

| •  | Moved R <sub>BAT</sub> , C <sub>BAT</sub> , R <sub>IN</sub> , C <sub>IN</sub> , R <sub>SENSEN</sub> , R <sub>SENSEP</sub> , C <sub>SENSE</sub> , R <sub>VCTL</sub> , C <sub>V3P3</sub> , C <sub>REF</sub> , and C <sub>OUT</sub> table rows to <i>Design Requirements</i> 5 |

| _  |                                                                                                                                                                                                                                                                             |

| Re | vision A (July 2011) から Revision B に変更 Page Page                                                                                                                                                                                                                            |

# Revision A (July 2011) から Revision B に変更

#### 2011年7月発行のものから更新

2

# Added 24-pin QFN (RGE) Package to Production Data ...... 3

Page

#### е

# Page

XAS

# 5 概要(続き)

外部センス抵抗の両端にわたる電圧が増幅され、ホストADCへ出力されることで、充電電流と放電電流を測定できます。2 つのゲイン設定により、広範なパック電流にわたって、さまざまなセンス抵抗値による動作が可能です。

ホストによる温度測定を可能にするため、AFEには外部サーミスタ回路のバイアス用に個別の出力ピンが用意されています。この出力はホスト制御によってオン/オフを切り替え、消費電力を最小限に抑えることが可能です。

bq76925にはコンパレータが内蔵されており、電流監視用のスレッショルドを動的に選択できます。コンパレータの結果は オープン・ドレイン出力から供給され、スレッショルドを超えたときはホストに通知されます。この機能を利用して、負荷の接 続時にホストをウェークアップしたり、フォルト状況の可能性をホストに警告したりできます。

bq76925デバイスには、ホストにより完全に制御可能なセル・バランシングFETが内蔵されています。バランシング電流は外部の抵抗により設定され、最大値は50mAです。これらのFETをセルの電圧測定と組み合わせて使用し、セル・センスライン上の断線検出が可能です。

ホストはI<sup>2</sup>Cインターフェイス経由でAFEと通信します。オプションとしてパケットCRCを使用し、堅牢な動作を実現できます。このデバイスは、I<sup>2</sup>Cインターフェイスにより低電流のスリープ・モードに移行でき、ALERTピンをプルアップしてウェークアップできます。

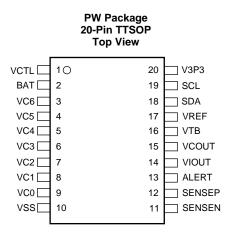

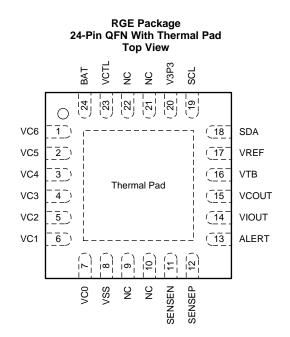

### 6 Pin Configuration and Functions

#### **Pin Functions**

| NAME   | PIN NO. |               | ТҮРЕ           | DESCRIPTION                                    |  |  |

|--------|---------|---------------|----------------|------------------------------------------------|--|--|

| NAME   | TSSOP   | VQFN          | ITE            | DESCRIPTION                                    |  |  |

| VCTL   | 1       | 23            | Output         | 3.3-V Regulator control voltage <sup>(1)</sup> |  |  |

| ALERT  | 13      | 13            | Output         | Overcurrent alert (open drain)                 |  |  |

| BAT    | 2       | 24            | Power          | Supply voltage, tied to most positive cell     |  |  |

| NC     | —       | 9, 10, 21, 22 | —              | No Connection (leave open)                     |  |  |

| SCL    | 19      | 19            | Input          | I <sup>2</sup> C Clock (open drain)            |  |  |

| SDA    | 18      | 18            | Input / Output | I <sup>2</sup> C Data (open drain)             |  |  |

| SENSEN | 11      | 11            | Input          | Negative current sense                         |  |  |

(1) When a bypass FET is used to supply the regulated 3.3-V load current, VCTL automatically adjusts to keep V3P3 = 3.3 V. If VCTL is tied to BAT, the load current is supplied through V3P3.

### **Pin Functions (continued)**

|        | PIN NO. |      | TYPE   | DECODIDION                                   |  |  |

|--------|---------|------|--------|----------------------------------------------|--|--|

| NAME   | TSSOP   | VQFN | TYPE   | DESCRIPTION                                  |  |  |

| SENSEP | 12      | 12   | Input  | Positive current sense                       |  |  |

| V3P3   | 20      | 20   | Output | 3.3-V Regulator                              |  |  |

| VC6    | 3       | 1    | Input  | Sense voltage for most positive cell         |  |  |

| VC5    | 4       | 2    | Input  | Sense voltage for second most positive cell  |  |  |

| VC4    | 5       | 3    | Input  | Sense voltage for third most positive cell   |  |  |

| VC3    | 6       | 4    | Input  | Sense voltage for fourth most positive cell  |  |  |

| VC2    | 7       | 5    | Input  | Sense voltage for fifth most positive cell   |  |  |

| VC1    | 8       | 6    | Input  | Sense voltage for least positive cell        |  |  |

| VC0    | 9       | 7    | Input  | Sense voltage for negative end of cell stack |  |  |

| VCOUT  | 15      | 15   | Output | Cell measurement voltage                     |  |  |

| VIOUT  | 14      | 14   | Output | Current measurement voltage                  |  |  |

| VREF   | 17      | 17   | Output | Reference voltage for ADC                    |  |  |

| VSS    | 10      | 8    | Power  | Ground                                       |  |  |

| VTB    | 16      | 16   | Output | Bias voltage for thermistor network          |  |  |

#### **Specifications** 7

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                  |                       |                                                   | MIN  | MAX     | UNIT |

|------------------|-----------------------|---------------------------------------------------|------|---------|------|

| V <sub>BAT</sub> | Supply voltage        | BAT                                               | -0.3 | 36      | V    |

|                  |                       | Cell input differential, VCn to VCn+1, n = 0 to 5 | -0.3 | 9       |      |

|                  |                       | Cell input, VCn, n = 1 to 6                       | -0.3 | (6 × n) |      |

| N/               | la sut us lts so      | BAT to VC6 differential                           | -10  | 10      | V    |

| VI               | Input voltage         | VC0 <sup>(2)</sup>                                | -3   | 3       | V    |

|                  |                       | SENSEP, SENSEN                                    | -3   | 3       |      |

|                  |                       | SCL, SDA                                          | -0.3 | 6       |      |

|                  |                       | VCOUT, VIOUT, VREF                                | -0.3 | 3.6     |      |

| N/               | Outrout welte as      | VTB, V3P3                                         | -0.3 | 7       | N/   |

| Vo               | Output voltage        | ALERT                                             | -0.3 | 30      | V    |

|                  |                       | VCTL                                              | -0.3 | 36      |      |

| I <sub>CB</sub>  | Cell balancing currer | ell balancing current                             |      | 70      | mA   |

| I <sub>IN</sub>  | Cell input current    |                                                   | -25  | 70      | mA   |

| T <sub>stg</sub> | Storage temperature   |                                                   | -65  | 150     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Negative voltage swings on VC0 in the absolute maximum range can cause unwanted circuit behavior and should be avoided. (2)

# 7.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

# 7.3 Recommended Operating Conditions<sup>(1)</sup>

|                   |                                 |             |                                        | MIN  | NOM | MAX           | UNIT |

|-------------------|---------------------------------|-------------|----------------------------------------|------|-----|---------------|------|

|                   | Supply voltage                  | BAT         |                                        | 4.2  |     | 26.4          | V    |

|                   |                                 | Cell input  | differential, VCn to VCn+1, n = 0 to 5 | 1.4  |     | 4.4           | V    |

|                   |                                 | Cell input, | VCn, n = 1 to 6                        |      |     | 4.4 × n       | V    |

|                   |                                 | BAT to VC   | 6 differential                         | -8   |     | 8             | V    |

|                   | land to alterna                 | VC0, SEN    | SEN                                    |      | 0   |               | V    |

| VI                | Input voltage                   | SENSEP      |                                        | -125 |     | 375           | mV   |

|                   |                                 | SCL, SDA    |                                        | 0    |     | 5.5           | V    |

|                   |                                 | V3P3        | Backfeeding <sup>(2)</sup>             |      |     | 5.5           | V    |

|                   |                                 | ALERT       | Wakeup function                        | 0    |     | 26.4          | V    |

|                   |                                 | VCOUT, V    | IOUT                                   | 0    |     | V3P3 +<br>0.2 | V    |

|                   |                                 |             | REFSEL = 0                             |      | 1.5 |               | V    |

|                   |                                 | VREF        | REFSEL = 1                             |      | 3   |               | V    |

| Vo                | Output voltage                  | VTB         |                                        |      |     | 5.5           | V    |

|                   |                                 | V3P3        | Regulating                             |      | 3.3 |               | V    |

|                   |                                 | VCTL        |                                        | 0.8  |     | 26.4          | V    |

|                   |                                 | ALERT       | Alert function                         | 0    |     | 5.5           | V    |

| I <sub>CB</sub>   | Cell balancing current          |             |                                        | 0    |     | 50            | mA   |

| T <sub>A</sub>    | Operating free-air temperature  |             |                                        | -25  |     | 85            | °C   |

| T <sub>FUNC</sub> | Functional free-air temperature |             |                                        | -40  |     | 100           | °C   |

(1) All voltages are relative to VSS, except "Cell input differential."

(2) Internal 3.3-V regulator may be overridden (that is, backfed) by applying an external voltage larger than the regulator voltage.

### 7.4 Thermal Information

|                         |                                              | bq76       |            |      |

|-------------------------|----------------------------------------------|------------|------------|------|

|                         | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | RGE (VQFN) | UNIT |

|                         |                                              | 20 PINS    | 24 PINS    |      |

| $R_{\theta JA}$         | Junction-to-ambient thermal resistance       | 97.5       | 36         | °C/W |

| R <sub>0JC (top)</sub>  | Junction-to-case (top) thermal resistance    | 31.7       | 38.6       | °C/W |

| $R_{\theta JB}$         | Junction-to-board thermal resistance         | 48.4       | 14         | °C/W |

| ΨJT                     | Junction-to-top characterization parameter   | 1.5        | 0.6        | °C/W |

| Ψјв                     | Junction-to-board characterization parameter | 47.9       | 14         | °C/W |

| $R_{\theta JC \ (bot)}$ | Junction-to-case (bottom) thermal resistance | n/a        | 4.6        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics: Supply Current

BAT = 4.2 to 26.4 V, VCn = 1.4 to 4.4,  $T_A = -25^{\circ}C$  to +85°C

Typical values stated where  $T_A = 25^{\circ}C$  and BAT= 21.6 V (unless otherwise noted)

|                  | PARAMETER                                                      | TEST CONDIT                                                                                                    | ION       | MIN | TYP   | MAX   | UNIT |

|------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------|-----|-------|-------|------|

| I <sub>DD1</sub> | Normal mode supply current                                     | All device functions enabled<br>All pins unloaded<br>SDA and SCL high                                          |           |     | 40    | 48    | μA   |

| I <sub>DD2</sub> | Standby mode 1 supply current                                  | V3P3 and overcurrent monitor er<br>All pins unloaded<br>All other device functions disable<br>SDA and SCL high |           | 14  | 17    | μA    |      |

| I <sub>DD3</sub> | Standby mode 2 supply current                                  | V3P3 enabled<br>All pins unloaded<br>All device functions disabled<br>SDA and SCL high                         |           |     | 12    | 14    | V    |

| I <sub>DD4</sub> | Sleep mode supply current                                      | V3P3 disabled<br>All pins unloaded<br>All device functions disabled<br>SDA and SCL low                         |           |     | 1     | 1.5   | μA   |

|                  |                                                                | All cell voltages equal                                                                                        | n = 6     |     | 2.4   | 2.7   |      |

| I <sub>VCn</sub> | Input current for selected cell                                | Cell balancing disabled                                                                                        | n = 1 – 5 |     |       | < 0.5 | μA   |

|                  | Open cell detection disabled<br>during cell voltage monitoring | n = 1 – 5 at 25°C                                                                                              |           |     | < 0.3 | -     |      |

| $\Delta I_{VCn}$ | Cell to cell input current difference                          | All cell voltages equal<br>Cell balancing disabled<br>Open cell detection disabled                             |           |     |       | < 0.2 | μA   |

#### 7.6 Internal Power Control (Startup and Shutdown)

|                       | PARAMETER                                           | TEST CONDITION   |                                              |     | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------------|------------------|----------------------------------------------|-----|-----|-----|------|

| V                     | Power on reset voltage                              | Measured at BAT  | Initial BAT < 1.4 VBAT rising <sup>(1)</sup> | 4.3 | 4.5 | 4.7 | V    |

| V <sub>POR</sub>      |                                                     | pin              | Initial BAT > 1.4 VBAT rising <sup>(1)</sup> | 6.5 | 7   | 7.5 | V    |

| V <sub>SHUT</sub>     | Shutdown voltage <sup>(2)</sup>                     | Measured at BAT  |                                              |     | 3.6 | V   |      |

| t <sub>POR</sub>      | Time delay after POR before<br>I2C comms allowed    | CV3P3 = 4.7 µF   |                                              |     | 1   | ms  |      |

| V <sub>WAKE</sub>     | Wakeup voltage                                      | Measured at ALER | CT pin                                       | 0.8 |     | 2   | V    |

| t <sub>WAKE_PLS</sub> | Wakeup signal pulse width                           |                  | 1                                            |     | 5   | μs  |      |

| t <sub>WAKE_DLY</sub> | Time delay after wakeup before<br>I2C comms allowed | CV3P3 = 4.7 µF   |                                              |     |     | 1   | ms   |

Initial power up will start with BAT < 1.4 V, however if BAT falls below V<sub>SHUT</sub> after rising above V<sub>POR</sub>, the power on threshold depends (1) on the minimum level reached by BAT after falling below  $V_{SHUT}$ . Following POR, the device will operate down to this voltage.

(2)

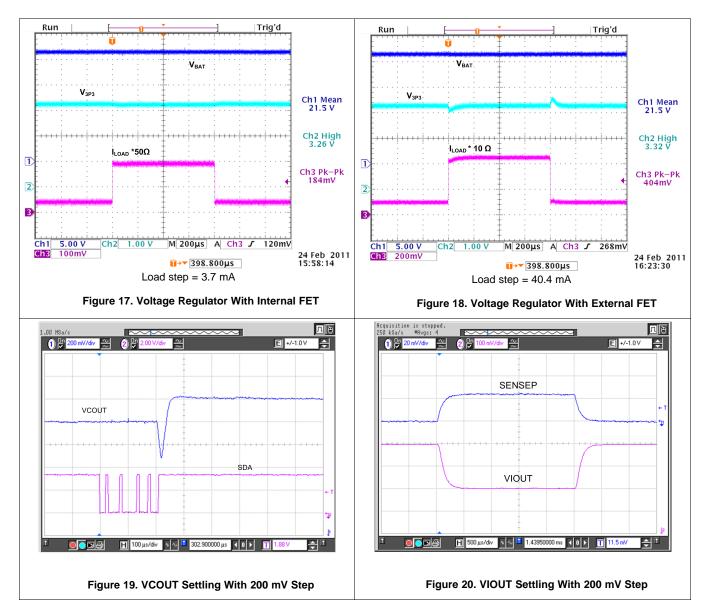

### 7.7 3.3-V Voltage Regulator

|                   | PARAMETER                           | TEST CONDITION                                                  | MIN | TYP               | MAX  | UNIT |

|-------------------|-------------------------------------|-----------------------------------------------------------------|-----|-------------------|------|------|

| V <sub>CTL</sub>  | Regulator control voltage (1)(2)    | Measured at VCTL, V3P3 regulating                               | 3.3 |                   | 26.4 | V    |

| V <sub>V3P3</sub> | Regulator output                    | Measured at V3P3, $I_{REG} = 0$ to 4 mA,<br>BAT = 4.2 to 26.4 V | 3.2 | 3.3               | 3.4  | V    |

| I <sub>REG</sub>  | V3P3 output current                 |                                                                 |     | 4                 | mA   |      |

| I <sub>SC</sub>   | V3P3 short circuit current limit    | V3P3 = 0.0 V                                                    | 10  |                   | 17   | mA   |

| V <sub>TB</sub>   | Thermistor bias voltage             | Measured at VTB, $I_{TB} = 0$                                   |     | V <sub>V3P3</sub> |      | V    |

| I <sub>TB</sub>   | Thermistor bias current             |                                                                 |     |                   | 1    | mA   |

| R <sub>TB</sub>   | Thermistor bias internal resistance | $R_{DS(ON)}$ for internal FET switch, $I_{TB} = 1 \text{ mA}$   |     | 90                | 130  | Ω    |

When a bypass FET is used to supply the regulated 3.3 V load current, VCTL automatically adjusts to keep V3P3 = 3.3 V. Note that (1)  $V_{CTL,MIN}$  and the FET V<sub>GS</sub> will determine the minimum BAT voltage at which the bypass FET will operate. If VCTL is tied to BAT, the load current is supplied through V3P3.

(2)

#### 7.8 Voltage Reference

| F                           | PARAMETER                        | TEST CONDITION                                               |                                                |       | TYP                   | MAX   | UNIT   |

|-----------------------------|----------------------------------|--------------------------------------------------------------|------------------------------------------------|-------|-----------------------|-------|--------|

|                             |                                  | Before gain correction,                                      | REF_SEL = 0                                    | 1.44  |                       | 1.56  | V      |

| Voltage reference<br>output | $T_A = 25^{\circ}C$              | REF_SEL = 1                                                  | 2.88                                           |       | 3.12                  |       |        |

|                             | output                           | After gain correction, <sup>(1)</sup><br>$T_A = 25^{\circ}C$ | REF_SEL = 0                                    | -0.1% | 1.5                   | +0.1% |        |

|                             |                                  |                                                              | REF_SEL = 1                                    | -0.1% | 3                     | +0.1% |        |

|                             |                                  | Measured at VCOUT                                            | VCOUT_SEL = 2                                  | -0.9% | $0.5 \times V_{REF}$  | +0.9% | V      |

| $V_{REF\_CAL}$              | Reference<br>calibration voltage |                                                              | VCOUT_SEL = 3                                  | -0.5% | $0.85 \times V_{REF}$ | +0.5% |        |

|                             | calibration voltage              |                                                              | $(0.85 \times V_{REF}) - (0.5 \times V_{REF})$ | -0.3% | $0.35 \times V_{REF}$ | +0.3% | V      |

| $\Delta V_{REF}$            | Voltage reference tolerance      | $T_A = 0 - 50^{\circ}C$                                      |                                                |       |                       | 40    | ppm/°C |

| I <sub>REF</sub>            | VREF output current              |                                                              |                                                |       |                       | 10    | μA     |

(1) Gain correction factor determined at final test and stored in non-volatile storage. Gain correction is applied by Host controller.

## 7.9 Cell Voltage Amplifier

|                    | PARAMETER                                    | TEST CO                                                              | NDITION                                       | MIN   | TYP | MAX  | UNIT |

|--------------------|----------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|-------|-----|------|------|

| C                  | Call voltage emplifier gain                  | Measured from VCn                                                    | REF_SEL = 0                                   | -1.6% | 0.3 | 1.5% |      |

| G <sub>VCOUT</sub> | Cell voltage amplifier gain                  | to VCOUT                                                             | REF_SEL = 1                                   | -1.6% | 0.6 | 1.5% |      |

| O <sub>VCOUT</sub> | Cell voltage amplifier offset                | Measured from VCn to VCOL                                            | -16                                           |       | 15  | mV   |      |

|                    | Cell voltage amp output range <sup>(1)</sup> | Measured at VCOUT,                                                   | REF_SEL = 0                                   | 1.47  | 1.5 | 1.53 | V    |

| V <sub>COUT</sub>  |                                              | VCn = 5 V                                                            | REF_SEL = 1                                   | 2.94  | 3   | 3.06 | V    |

| •001               |                                              | Measured at VCOUT,<br>VCn = 0 V                                      |                                               | 0     |     | V    |      |

|                    |                                              | VCn = 1.4 V to 4.4 V,                                                | $T_A = 25^{\circ}C$                           | -3    |     | 3    |      |

| $\Delta V_{COUT}$  | Cell voltage amplifier accuracy              | After correction, <sup>(2)</sup><br>Measured at VCOUT <sup>(3)</sup> | $T_A = 0^{\circ}C$ to $50^{\circ}C$           | -5    |     | 5    | mV   |

|                    |                                              | $REF_SEL = 1^{(4)}$                                                  | $T_A = -25^{\circ}C \text{ to } +85^{\circ}C$ | -8    |     | 8    |      |

| I <sub>VCOUT</sub> | VCOUT output current <sup>(5)</sup>          |                                                                      |                                               |       |     | 10   | μA   |

| t <sub>VCOUT</sub> | Delay from VCn select to VCOUT               | Output step of 200 mV, $C_{OUT}$                                     | = 0.1 µF                                      |       |     | 100  | μs   |

(1) For VCn values greater than 5 V, VCOUT clamps at approximately V3P3.

Correction factor determined at final test and stored in non-volatile storage. Correction is applied by Host controller. (2)

(3) Output referred. Input referred accuracy is calculated as ΔV<sub>COUT</sub> / G<sub>VCOUT</sub> (for example, 3 / 0.6 = 5).

(4) Correction factors are calibrated for gain of 0.6. Tolerance at gain of 0.3 is approximately doubled. Contact TI for information on devices calibrated to a gain of 0.3.

(5) Max DC load for specified accuracy.

#### 7.10 Current Sense Amplifier

|                    | PARAMETER                           | TEST CC                                | NDITION      | MIN  | TYP | MAX  | UNIT |

|--------------------|-------------------------------------|----------------------------------------|--------------|------|-----|------|------|

| <u> </u>           | Current sense amplifier gain        | Measured from SENSEN,                  | $I_GAIN = 0$ |      | 4   |      |      |

| G <sub>VIOUT</sub> |                                     | SENSEP to VIOUT                        | I_GAIN = 1   |      | 8   |      |      |

| V <sub>IIN</sub>   | Current sense amp input range       | Measured from SENSEN,<br>SENSEP to VSS | -125         |      | 375 | mV   |      |

|                    | Current sense amp output range      | Measured at VIOUT                      | REF_SEL = 0  | 0.25 |     | 1.25 | V    |

| V                  |                                     | Measured at VIOUT                      | REF_SEL = 1  | 0.5  |     | 2.5  | V    |

| V <sub>IOUT</sub>  | 7                                   | Measured at VIOUT                      | REF_SEL = 0  |      | 1   |      | V    |

|                    | Zero current output                 | SENSEP = SENSEN                        | REF_SEL = 1  |      | 2   |      | V    |

| $\Delta V_{IOUT}$  | Current amplifier accuracy          |                                        |              | -1%  |     | 1%   |      |

| IV <sub>IOUT</sub> | VIOUT output current <sup>(1)</sup> |                                        |              | 10   | μA  |      |      |

(1) Max DC load for specified accuracy

JAJSBH1D-JULY 2011-REVISED OCTOBER 2016

www.ti.com

#### 7.11 Overcurrent Comparator

|                        | PARAMETER                                            | TEST CONDITION                              | MIN  | TYP | MAX | UNIT |

|------------------------|------------------------------------------------------|---------------------------------------------|------|-----|-----|------|

| V <sub>BAT_COMP</sub>  | Minimum VBAT for comparator operation <sup>(1)</sup> |                                             |      |     | 5   | V    |

| G <sub>VCOMP</sub>     | Comparator amplifier gain                            | Measured from SENSEP to comparator<br>input |      | 1   |     |      |

| VITRIP                 | Current comparator trip threshold <sup>(2)</sup>     | 25                                          |      | 400 | mV  |      |

| 437                    | Current comparator accuracy                          | V <sub>ITRIP</sub> = 25 mV                  | -6   |     | 6   | mV   |

| $\Delta V_{ITRIP}$     | Current comparator accuracy                          | V <sub>ITRIP</sub> > 25 mV                  | -10% |     | 10% | V    |

| V <sub>OL_ALERT</sub>  | ALERT Output Low Logic                               | I <sub>ALERT</sub> = 1 mA                   |      |     | 0.4 | V    |

| V <sub>OH_ALERT</sub>  | ALERT Output High Logic <sup>(3)</sup>               |                                             | NA   | NA  | NA  |      |

| I <sub>ALERT</sub>     | ALERT Pulldown current                               | ALERT = 0.4 V, Output driving low           | 1    |     |     | mA   |

| I <sub>ALERT_LKG</sub> | ALERT Leakage current                                | ALERT = 5 V, Output Hi-Z                    |      |     | < 1 | μA   |

| t <sub>OC</sub>        | Comparator response time                             |                                             |      |     | 100 | μs   |

(1)

The Overcurrent Comparator is not guaranteed to work when VBAT is below this voltage. Trip threshold selectable from 25, 50, 75, 100, 125, 150, 175, 200, 225, 250, 275, 300, 325, 350, 375 or 400 mV. (2) (3)

This parameter NA because output is open drain.

#### 7.12 Internal Temperature Measurement

|                        | PARAMETER                                                       | TEST CONDITION                             | MIN  | TYP | MAX  | UNIT  |

|------------------------|-----------------------------------------------------------------|--------------------------------------------|------|-----|------|-------|

| V <sub>TEMP_INT</sub>  | Internal temperature voltage                                    | Measured at VCOUT, T <sub>INT</sub> = 25°C | 1.15 | 1.2 | 1.25 | V     |

| $\Delta V_{TEMP\_INT}$ | ۵۷ <sub>TEMP_INT</sub> Internal temperature voltage sensitivity |                                            |      |     |      | mV/°C |

### 7.13 Cell Balancing and Open Cell Detection

|                 | PARAMETER                   | MIN                                                                 | TYP | MAX | UNIT |    |

|-----------------|-----------------------------|---------------------------------------------------------------------|-----|-----|------|----|

| Б               | Cell balancing internal     | R <sub>DS(ON)</sub> for VC1 internal FET switch, VCn = 3.6 V        | 1   | 3   | 5    | 0  |

| R <sub>BA</sub> | L resistance <sup>(1)</sup> | R <sub>DS(ON)</sub> for internal VC2 to VC6 FET switch, VCn = 3.6 V | 3   | 5.5 | 8    | 52 |

(1) Balancing current is not internally limited. The cell balancing operation is completely controlled by the Host processor, no automatic function or time-out is included in the part. Take care to ensure that balancing current through the part is below the maximum power dissipation limit. The Host algorithm is responsible for limiting thermal dissipation to package ratings.

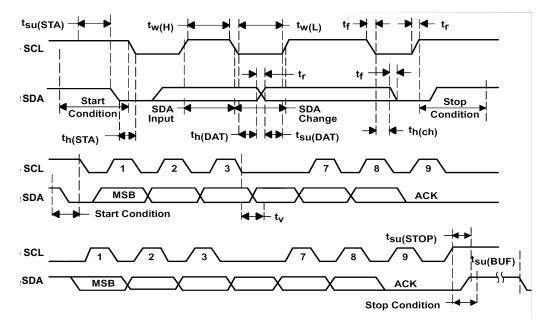

### 7.14 I<sup>2</sup>C Compatible Interface

| PARAME                | TERS                                      |                                              | MIN              | TYP | MAX  | UNIT |

|-----------------------|-------------------------------------------|----------------------------------------------|------------------|-----|------|------|

| DC PARA               | METERS                                    |                                              |                  |     |      |      |

| V <sub>IL</sub>       | Input Low Logic Threshold                 | 1                                            |                  |     | 0.6  | V    |

| V <sub>IH</sub>       | Input High Logic Threshol                 | d                                            | 2.8              |     |      | V    |

| V <sub>OL</sub>       | Output Low Logic Drive                    | I <sub>OL</sub> = 1 mA                       |                  |     | 0.20 | V    |

|                       |                                           | I <sub>OL</sub> = 2.5 mA                     |                  |     | 0.40 |      |

| V <sub>OH</sub>       | Output High Logic Drive (I                | Not applicable due to open-drain outputs)    |                  | N/A | V    |      |

| I <sub>LKG</sub>      | I <sup>2</sup> C Pin Leakage              | Pin = 5 V, Output in Hi-Z                    |                  |     | < 1  | μA   |

| AC PARA               | METERS                                    |                                              |                  |     |      |      |

| t <sub>r</sub>        | SCL, SDA Rise Time                        |                                              |                  |     | 1000 | ns   |

| t <sub>f</sub>        | SCL, SDA Fall Time                        |                                              |                  | 300 | ns   |      |

| t <sub>w(H)</sub>     | SCL Pulse Width High                      | 4                                            |                  |     | μs   |      |

| t <sub>w(L)</sub>     | SCL Pulse Width Low                       |                                              | 4.7              |     |      | μs   |

| t <sub>su(STA)</sub>  | Setup time for START cor                  | ndition                                      | 4.7              |     |      | μs   |

| t <sub>h(STA)</sub>   | START condition hold time                 | e after which first clock pulse is generated | 4                |     |      | μs   |

| t <sub>su(DAT)</sub>  | Data setup time                           |                                              | 250              |     |      | ns   |

| t <sub>h(DAT)</sub>   | Data hold time                            |                                              | 0 <sup>(1)</sup> |     |      | μs   |

| t <sub>su(STOP)</sub> | Setup time for STOP cond                  | lition                                       | 4                |     |      | μs   |

| t <sub>su(BUF)</sub>  | Time the bus must be free                 | e before new transmission can start          | 4.7              |     |      | μs   |

| t <sub>V</sub>        | Clock Low to Data Out Va                  | lid                                          |                  |     | 900  | ns   |

| t <sub>h(CH)</sub>    | Data Out Hold Time After                  | Clock Low                                    | 0                |     |      | ns   |

| f <sub>SCL</sub>      | Clock Frequency                           |                                              | 0                |     | 100  | kHz  |

| t <sub>WAKE</sub>     | I <sup>2</sup> C ready after transition t | o Wake Mode                                  |                  |     | 2.5  | ms   |

(1) Devices must provide internal hold time of at least 300 ns for the SDA signal-to-bridge of the undefined region of the falling edge of SCL.

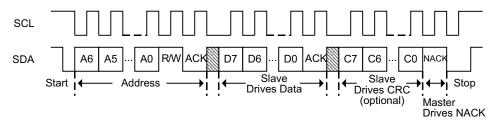

Figure 1. I<sup>2</sup>C Timing

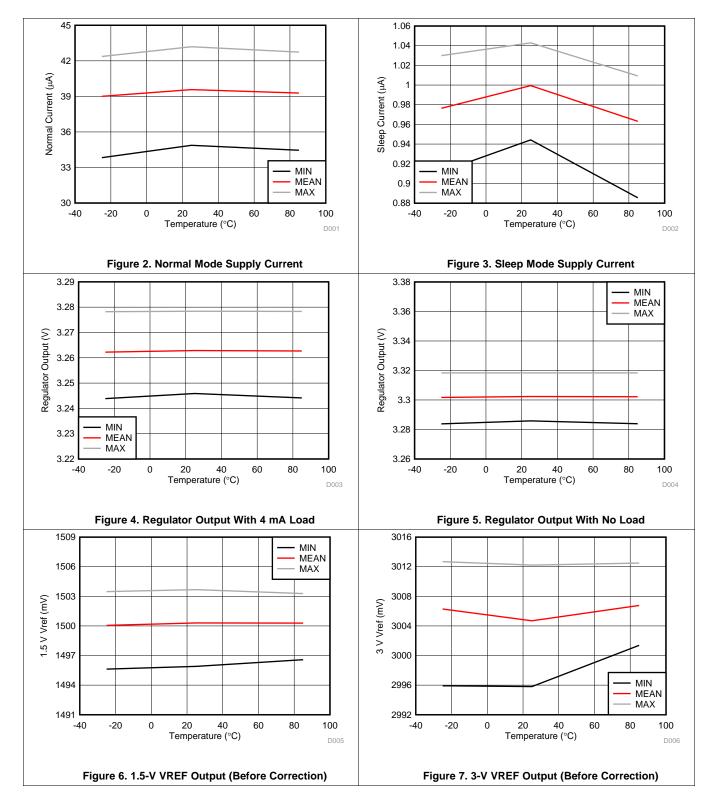

# 7.15 Typical Characteristics

### 8 Detailed Description

#### 8.1 Overview

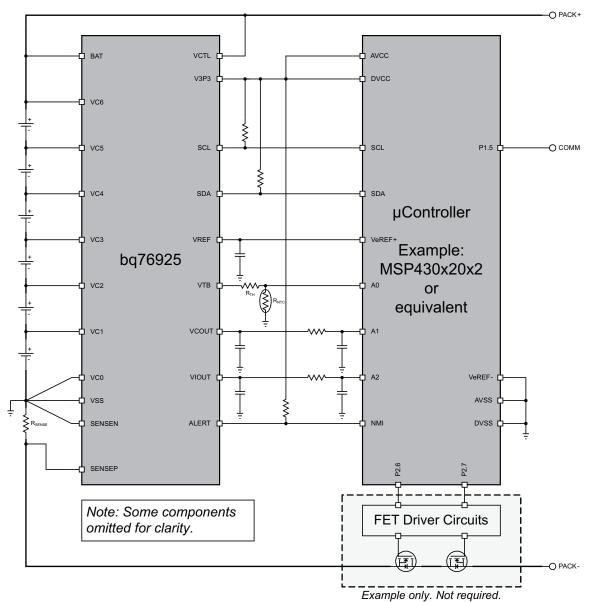

The bq76925 Host-controlled analog front end (AFE) is part of a complete pack monitoring, balancing, and protection system for 3-series to 6-series cell Lithium batteries. The bq76925 allows a Host controller to easily monitor individual cell voltages, pack current, and temperature. The Host may use this information to detect and act on a fault condition caused when one or more of these parameters exceed the limits of the application. In addition, the Host may use this information to determine end-of-charge, end-of-discharge, and other gas-gauging and state of health conditions.

Figure 8. Example of bq76925 With Host Controller

**bq76925** JAJSBH1D – JULY 2011 – REVISED OCTOBER 2016

www.ti.com

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

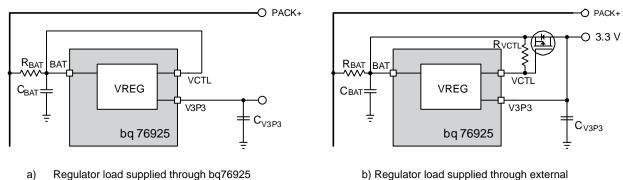

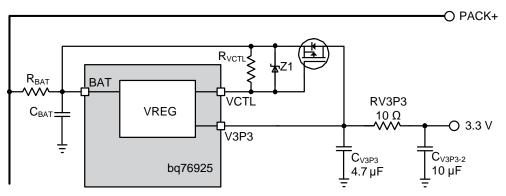

#### 8.3.1 Internal LDO Voltage Regulator

The bq76925 device provides a regulated 3.3-V supply voltage on the V3P3 pin for operating the device's internal logic and interface circuitry. This regulator may also be used to directly power an external microcontroller or other external circuitry up to a limit of 4-mA load current. In this configuration, the VCTL pin is tied directly to the BAT pin. For applications requiring more than 4 mA, an external-bypass transistor may be used to supply the load current. In this configuration, the VCTL pin is tied to supply the load current. In this configuration, the VCTL pin is tied to the gate of the bypass FET. These two configurations are show in Figure 9.

#### Feature Description (continued)

pass device

#### Figure 9. LDO Regulator Configurations

For the configuration of Figure 9b), a high-gain bypass device should be used to ensure stability. A bipolar PNP or p-channel FET bypass device may be used. Contact TI for recommendations.

The LDO regulator may be overridden (that is, back-fed) by an external-supply voltage greater than the regulated voltage on V3P3. In this configuration, the bq76925 internal logic and interface circuitry operates from the external supply and the internal 3.3-V regulator supplys no load current.

#### 8.3.2 ADC Interface

The bq76925 device is designed to interface to a multi-channel analog-to-digital converter (ADC) located in an external Host controller, such as an MSP430 Microcontroller or equivalent. Three outputs provide voltage, current, and temperature information for measurement by the Host. In addition, the bq76925 device includes a low-drift calibrated 1.5 / 3 V reference that is output on a dedicated pin for use as the reference input to the ADC.

The gain and offset characteristics of the bq76925 device are measured during factory test and stored in nonvolatile memory as correction factors. The Host reads these correction factors and applies them to the ADC conversion results in order to achieve high-measurement accuracy. In addition, the precise voltage reference of the bq76925 can be used to calibrate the gain and offset of the Host ADC.

#### 8.3.2.1 Reference Voltage

The bq76925 device outputs a stable reference voltage for use by the Host ADC. A nominal voltage of 1.5 V or 3 V is selected through the REF\_SEL bit in the CONFIG\_2 register. The reference voltage is very stable across temperature, but the initial voltage may vary by ±4%. The variation from nominal is manifested as a gain error in the ADC conversion result. To correct for this error, offset and gain correction factors are determined at final test and stored in the non-volatile registers VREF\_CAL and VREF\_CAL\_EXT. The Host reads the correction factors and applies them to the nominal reference voltage to arrive at the actual reference voltage as described under *Cell Voltage Monitoring*. After gain correction, the tolerance of the reference will be within ±0.1%.

#### 8.3.2.1.1 Host ADC Calibration

All analog-to-digital converters have inherent gain and offset errors, which adversely affect measurement accuracy. Some microcontrollers may be characterized by the manufacturer and shipped with ADC gain and offset information stored on-chip. It is also possible for such characterization to be done by the end-user on loose devices prior to PCB assembly or as a part of the assembled PCB test.

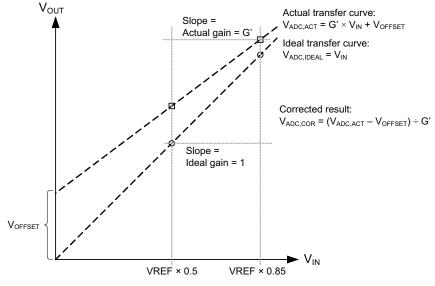

For applications where such ADC characterization is not provided or is not practical, the bq76925 device provides a means for in-situ calibration of the Host ADC through setting of the VCOUT\_SEL bits in the CELL\_CTL register two scaled versions of the reference voltage,  $0.5 \times V_{REF}$  and  $0.85 \times V_{REF}$ , can be selected for output on the VCOUT pin for measurement by the Host ADC. Measuring both scaled voltages enables the Host to do a two-point calibration of the ADC and compensate for the ADC offset and gain in all subsequent ADC measurement results as shown in Figure 10.

### Feature Description (continued)

Note that the calibration accuracy will be limited by the tolerance of the scaled reference-voltage output so that use of this method may not be effective. For these cases, TI recommends to use a higher-accuracy source for the two-point calibration shown in Figure 10.

Figure 10. Host ADC Calibration Using V<sub>REF</sub>

#### 8.3.2.2 Cell Voltage Monitoring

The cell-voltage monitoring circuits include an input level-shifter, multiplexer (MUX), and scaling amplifier. The Host selects one VCn cell input for measurement by setting the VCOUT\_SEL and CELL\_SEL bits in the CELL\_CTL register. The scaling factor is set by the REF\_SEL bit in the CONFIG\_2 register. The selected cell input is level shifted to VSS reference, scaled by a nominal gain  $G_{VCOUT} = 0.3$  (REF\_SEL = 0) or 0.6 (REF\_SEL = 1) and output on the VCOUT pin for measurement by the Host ADC.

Similar to the reference voltage, gain and offset correction factors are determined at final test for each individual cell input and stored in non-volatile registers VCn\_CAL (n = 1-6) and VC\_CAL\_EXT\_m (m = 1-2). These factors are read by the Host and applied to the ADC voltage-measurement results in order to obtain the specified accuracy.

The cell voltage offset and gain correction factors are stored as 5-bit signed integers in 2's complement format. The most significant bits (VCn\_OC\_4, VCn\_GC\_4) are stored separately and must be concatenated with the least significant bits (VCn\_OFFSET\_CORR, VCn\_GAIN\_CORR).

The reference voltage offset and gain correction factors are stored respectively as a 6-bit and 5-bit signed integer in 2's complement format. As with the cell voltage correction factors, the most significant bits (VREF\_OC\_5, VREF\_OC\_4, VREF\_GC\_4) are stored separately and must be concatenated with the least significant bits (VREF\_OFFSET\_CORR, VREF\_GAIN\_CORR).

The actual cell voltage (VCn) is calculated from the measured voltage (VCOUT) as shown in the following equations:

$$VCOUT = \frac{ADC Count}{Full Scale Count} \times VREF_{NOMINAL}$$

$$VCn = \frac{VCOUT \times GC_{VREF} + OC_{VCOUT}}{G_{VCOUT}} \times (1 + GC_{VCOUT})$$

(1)

bq76925 JAJSBH1D – JULY 2011 – REVISED OCTOBER 2016

www.ti.com

#### Feature Description (continued)

$GC_{VCOUT} = \left[ (VCn_GC_4 << 4) + VCn_GAIN_CORR \right] \times 0.001,$   $OC_{VCOUT} = \left[ (VCn_OC_4 << 4) + VCn_OFFSET_CORR \right] \times 0.001,$   $GC_{VREF} = (1 + \left[ (VREF_GC_4 << 4) + VREF_GAIN_CORR \right] \times 0.001)$   $+ \frac{\left[ (VREF_OC_5 << 5) + (VREF_OC_4 << 4) + VREF_OFFSET_CORR \right] \times 0.001}{VREF_{NOMINAL}}$

#### 8.3.2.2.1 Cell Amplifier Headroom Under Extreme Cell Imbalance

For cell voltages across (VC1 – VC0) that are less than approximately 2.64 V, extreme cell-voltage imbalances between (VC1 – VC0) and (VC2 – VC1) can lead to a loss of gain in the (VC2 – VC1) amplifier. The cell imbalance at which the loss of gain occurs is determined by Equation 3:

$$(VC2 - VC1) \times 0.6 > (VC1 - VSS)$$

Assuming VC0 = VSS, it can be seen that when (VC1 – VC0) > 2.64 volts, the voltage across (VC2 – VC1) can range up to the limit of 4.4 V without any loss of gain. At the minimum value of (VC1 – VC0) = 1.4 V, an imbalance of more than 900 mV is tolerated before any loss of gain in the (VC2 – VC1) amplifier. For higher values of (VC1 – VC0), increasingly large imbalances are tolerated. For example, when (VC1 – VC0) = 2.0 V, an imbalance up to 1.33 V (that is, (VC2 – VC1) = 3.33 V) results in no degradation of amplifier performance.

Normally, cell imbalances greater than 900 mV will signal a faulty condition of the battery pack and its use should be discontinued. The loss of gain on the second cell input does not affect the ability of the system to detect this condition. The gain fall-off is gradual so that the measured imbalance will never be less than the critical imbalance set by Equation 3.

Therefore, if the measured (VC2 – VC1) is greater than (VC1 – VSS) / 0.6, a severe imbalance is detected and the pack should enter a fault state which prevents further use. In this severe cell imbalance condition comparisons of the measured (VC2 – VC1) to any overvoltage limits will be optimistic due to the reduced gain in the amplifier, further emphasizing the need to enter a fault state.

#### 8.3.2.2.2 Cell Amplifier Headroom Under BAT Voltage Drop

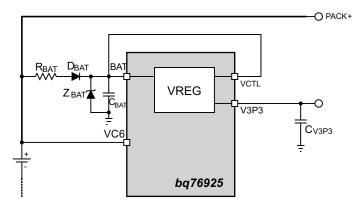

Voltage differences between BAT and the top cell potential come from two sources as shown in Figure 11: V3P3 regulator current that flows through the  $R_{BAT}$  filter resistor, and the voltage drop in the series diode  $D_{BAT}$  of the hold-up circuit. These effects cause BAT to be less than the top-cell voltage measured by the cell amplifier.

Figure 11. Sources of Voltage Drop Affecting the BAT Pin

(2)

(3)

#### Feature Description (continued)

The top-cell amplifier (VC6 – VC5) is designed to measure an input voltage down to 1.4 V with a difference between the BAT and VC6 pin up to 1.2 V (that is, BAT can be 1.2 V lower than VC6). However, in applications with fewer than 6 cells, the upper-cell inputs are typically shorted to the top-cell input. For example, in a 5-cell application VC6 and VC5 would be shorted together and the (VC5 – VC4) amplifier would measure the top-cell voltage. The case is similar for 4-cell and 3-cell applications.

For these cases when using the (VC5 – VC4), (VC4 –VC3), or (VC3 – VC2) amplifier to measure the top cell, the difference between BAT and the top-cell amplifier must be less than 240 mV in order to measure cell voltages down to 1.4 V. Note that at higher-cell input voltages the top amplifier tolerates a greater difference. For example, in a 5-cell configuration (VC6 and VC5 tied together) the (VC5 – VC4) amplifier is able to measure down to a 1.7 V input with a 600-mV difference between VC5 and BAT.

Accordingly, in systems with fewer than 6 cells, it is important in system design to minimize  $R_{BAT}$  and to use a Schottky type diode for  $D_{BAT}$  with a low forward voltage. If it is not possible to reduce the drop at BAT to an acceptable level, then for 4-cell and 5-cell configurations, the (VC6 – VC5) amplifier may be used as the top cell amplifier as shown in Table 1, which allows up to a 1.2 V difference between BAT and the top cell.

| Configuration | Cell 5    | Cell 4    | Cell 3    | Cell 2    | Cell 1    | Unused Cell Inputs      |

|---------------|-----------|-----------|-----------|-----------|-----------|-------------------------|

| 5-cell        | VC6 – VC5 | VC4 – VC3 | VC3 – VC2 | VC2 - VC1 | VC1 – VC0 | Short VC5 to VC4        |

| 4-cell        |           | VC6 - VC5 | VC3 – VC2 | VC2 – VC1 | VC1 – VC0 | Short VC5 to VC4 to VC3 |

#### Table 1. Alternate Connections for 4 and 5 Cells

#### 8.3.2.3 Current Monitoring

Current is measured by converting current to voltage through a sense resistor connected between SENSEN and SENSEP. A positive voltage at SENSEP with respect to SENSEN indicates a discharge current is flowing, and a negative voltage indicates a charge current. The small voltage developed across the sense resistor is amplified by gain  $G_{VIOUT}$  and output on the VIOUT pin for conversion by the Host ADC. The voltage on VIOUT is always positive and for zero current is set to 3/4 of the output range. The current sense amplifier is inverting; discharge current causes VIOUT to decrease and charge current causes VIOUT to increase. Therefore, the measurement range for discharge currents is 3 times the measurement range for charge currents.

The current-sense amplifier is preceded by a multiplexer that allows measurement of either the SENSEN or SENSEP input with respect to VSS. The Host selects the pin for measurement by writing the I\_AMP\_CAL bit in the CONFIG\_1 register. The Host then calculates the voltage across the sense resistor by subtracting the measured voltage at SENSEN from the measured voltage at SENSEP. If the SENSEN and VSS connections are such that charge and discharge currents do not flow through the connection between them; that is, there is no voltage drop between SENSEN and VSS due to the current being measured, then the measurement of the SENSEN voltage can be regarded as a calibration step and stored by the Host for use as a pseudo-constant in the  $V_{\text{SENSE}}$  calculation. The SENSEN voltage measurement would then only need updating when changing environmental conditions warrant.

The Host sets  $G_{VIOUT}$  by writing the I\_GAIN bit in the CONFIG\_1 register. The available gains of 4 and 8 enable operation with a variety of sense-resistor values over a broad range of pack currents. The gain may be changed at any time allowing for dynamic range and resolution adjustment. The input and output ranges of the amplifier are determined by the value of the REF\_SEL bit in the CONFIG\_2 register. These values are shown in Table 2. Because the current amplifier is inverting, the Min column under Output Range corresponds to the Max column under Input Range. Likewise, the Max column under Output Range corresponds to the Min column under Input Range.

The actual current is calculated from the measured voltage (VIOUT) as follows. Note that  $V_{\text{SENSE}}$  is positive when discharge current is flowing. In keeping with battery pack conventions, the sign of  $I_{\text{SENSE}}$  is inverted so that discharge current is negative.

$V_{SENSE} = \frac{-(VIOUT(SENSEP) - VIOUT(SENSEN))}{G_{VIOUT}}$  $I_{SENSE} = -\frac{V_{SENSE}}{R_{SENSE}}$

| REF_SEL | I_GAIN | Gain | VIOUT (V) at<br>I <sub>SENSE</sub> = 0 | Input Range <sup>(1)</sup><br>(mV) |       | Output Range <sup>(2)</sup><br>(V) |      | I <sub>SENSE</sub> Range (A) at | I <sub>SENSE</sub> Resolution<br>(mA)w/10-bit |

|---------|--------|------|----------------------------------------|------------------------------------|-------|------------------------------------|------|---------------------------------|-----------------------------------------------|

|         |        |      | (typical)                              | Min                                | Max   | Min Max                            |      | $R_{SENSE} = 1 m\Omega$         | ADC <sup>(3)</sup>                            |

| 0       | 0      | 4    | 1.0                                    | -62.5                              | 187.5 | 0.25                               | 1.25 | -62.5 - 187.5                   | 366                                           |

| 0       | 1      | 8    | 1.0                                    | -14                                | 91    | 0.27                               | 1.11 | -14 - 91                        | 183                                           |

| 1       | 0      | 4    | 2.0                                    | -125                               | 375   | 0.5                                | 2.5  | -125 - 375                      | 732                                           |

| 1       | 1      | 8    | 2.0                                    | -62.5                              | 187.5 | 0.5                                | 2.5  | -62.5 - 187.5                   | 366                                           |

#### **Table 2. Current Amplifier Configurations**

(1) SENSEN or SENSEP measured with respect to VSS.

(2) Output range assumes typical value of VIOUT at I<sub>SENSE</sub> = 0. For non-typical values, the output range will shift accordingly.

(3) Assumes 1 mΩ R<sub>SENSE</sub> and ADC reference voltage of 1.5 V and 3.0 V when REF\_SEL = 0 and 1, respectively.

#### 8.3.2.4 Overcurrent Monitoring

The bq76925 device also includes a comparator for monitoring the current-sense resistor and alerting the Host when the voltage across the sense resistor exceeds a selected threshold. The available thresholds range from 25 mV to 400 mV and are set by writing the I\_THRESH bits in the CONFIG\_1 register. Positive (discharge) or negative (charge) current may be monitored by setting the I\_COMP\_POL bit in the CONFIG\_1 register. By the choice of sense resistor and threshold, a variety of trip points are possible to support a wide range of applications.

The comparator result is driven through the open-drain ALERT output to signal the host when the threshold is exceeded. This feature can be used to wake up the Host on connection of a load or to alert the Host to a potential fault condition. The ALERT pin state is also available by reading the ALERT bit in the STATUS register.

#### 8.3.2.5 Temperature Monitoring

To enable temperature measurements by the Host, the bq76925 device provides the LDO regulator voltage on a separate output pin (VTB) for biasing an external thermistor network. In order to minimize power consumption, the Host may switch the VTB output on and off by writing to the VTB\_EN bit in the POWER\_CTL register. Note that if the LDO is back-fed by an external source, the VTB bias will be switched to the external source.

In a typical application, the thermistor network will consist of a resistor in series with an NTC thermistor, forming a resistor divider where the output is proportional to temperature. This output may be measured by the Host ADC to determine temperature.

#### 8.3.2.5.1 Internal Temperature Monitoring

The internal temperature ( $T_{INT}$ ) of the bq76925 device can be measured by setting VCOUT\_SEL = '01' and CELL\_SEL = '110' in the CELL\_CTL register. In this configuration, a voltage proportional to temperature ( $V_{TEMP \ INT}$ ) is output on the VCOUT pin. This voltage is related to the internal temperature as follows:

$V_{\text{TEMP}_{\text{INT}}}(\text{mV}) = V_{\text{TEMP}_{\text{INT}}}(T_{\text{INT}} = 25^{\circ}\text{C}) - T_{\text{INT}}(^{\circ}\text{C}) \times \Delta V_{\text{TEMP}_{\text{INT}}}$

(5)

#### 8.3.3 Cell Balancing and Open Cell Detection

The bq76925 device integrates cell-balancing FETs that are individually controlled by the Host. The balancing method is resistive bleed balancing, where the balancing current is set by the external cell input resistors. The maximum allowed balancing current is 50 mA per cell.

The Host may activate one or more cell balancing FETs by writing the BAL\_n bits in the BAL\_CTL register. To allow the greatest flexibility, the Host has complete control over the balancing FETs. However, in order to avoid exceeding the maximum cell input voltage, the bq76925 will prevent two adjacent balancing FETs from being turned on simultaneously. If two adjacent bits in the balance control register are set to 1, neither balancing transistor will be turned on. The Host based balancing algorithm must also limit the power dissipation to the maximum ratings of the device.

In a normal system, closing a cell-balancing FET will cause 2 cell voltages to appear across one cell input. This fact can be utilized to detect a cell sense-line open condition, that is, a broken wire from the cell-sense point to the bq76925 VCn input. Table 3 shows how this can be accomplished. Note that the normal cell-voltage measurements may represent a saturated or full-scale reading. However, these will normally be distinguishable from the open-cell measurement.

**ISTRUMENTS**

FXAS

| Kelvin   |         |           | Method 1            |       | Method 2 |          |                     |       |  |  |

|----------|---------|-----------|---------------------|-------|----------|----------|---------------------|-------|--|--|

| input to | Turn On | Necessary | Result              |       | Turn On  | Magazina | Result              |       |  |  |

| test     | Turn On | Measure   | Normal              | Open  | Turn On  | Measure  | Normal              | Open  |  |  |

| VC0      | BAL_1   | CELL2     | CELL2 + 0.5 × CELL1 | CELL2 |          |          |                     |       |  |  |

| VC1      | BAL_2   | CELL3     | CELL3 + 0.5 × CELL2 | CELL3 |          |          |                     |       |  |  |

| VC2      | BAL_3   | CELL4     | CELL4 + 0.5 × CELL3 | CELL4 | BAL_2    | CELL1    | CELL1 + 0.5 × CELL2 | CELL1 |  |  |

| VC3      | BAL_4   | CELL5     | CELL5 + 0.5 × CELL4 | CELL5 | BAL_3    | CELL2    | CELL2 + 0.5 × CELL3 | CELL2 |  |  |

| VC4      | BAL_5   | CELL6     | CELL6 + 0.5 × CELL5 | CELL6 | BAL_4    | CELL3    | CELL3 + 0.5 × CELL4 | CELL3 |  |  |

| VC5      |         |           |                     |       | BAL_5    | CELL4    | CELL4 + 0.5 × CELL5 | CELL4 |  |  |

| VC6      |         |           |                     |       | BAL_6    | CELL5    | CELL5 + 0.5 × CELL6 | CELL5 |  |  |

Note that the cell amplifier headroom limits discussed above apply to the open-cell detection method because by virtue of closing a switch between 2 cell inputs, internal to the device this appears as an extreme cell imbalance. Therefore, when testing for an open on CELL2 by closing the CELL1 balancing FET, the CELL2 measurement will be less than the expected normal result due to gain loss caused by the imbalance. However, the CELL2 measurement will still increase under this condition so that a difference between open (no change) and normal (measured voltage increases) can be detected.

#### 8.4 Device Functional Modes

#### 8.4.1 Power Modes

#### 8.4.1.1 POWER ON RESET (POR)

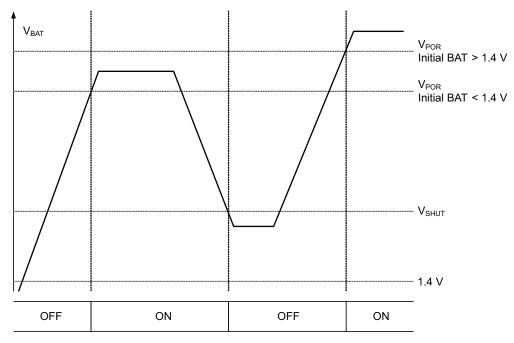

When initially powering up the bq76925 device, the voltage on the BAT pin must exceed V<sub>POR</sub> (4.7-V maximum) before the device will turn on. Following this, the device will remain operational as long as the voltage on BAT remains above V<sub>SHUT</sub> (3.6-V maximum). If the BAT voltage falls below V<sub>SHUT</sub>, the device will shut down. Recovery from shutdown occurs when BAT rises back above the V<sub>POR</sub> threshold and is equivalent to a POR. The V<sub>POR</sub> threshold following a shutdown depends on the minimum level reached by BAT after crossing below V<sub>SHUT</sub>. If BAT does not fall below approximately 1.4 V, a higher V<sub>POR</sub> (7.5-V maximum) applies. This is illustrated in Figure 12.

Figure 12. Power On State vs V<sub>BAT</sub>

#### **Device Functional Modes (continued)**

Following a power on reset, all volatile registers assume their default state. Therefore, care must be taken that transients on the BAT pin during normal operation do not fall below  $V_{SHUT}$ . To avoid this condition in systems subject to extreme transients or brown-outs, a hold-up circuit such as the one shown in the functional diagram is recommended. When using a hold-up circuit, care must be taken to observe the BAT to VC6 maximum ratings.

#### 8.4.1.2 STANDBY

Individual device functions such as cell translator, current amplifier, reference, and current comparator can be enabled and disabled under Host control by writing to the POWER\_CTL register. The STANDBY feature can be used to save power by disabling functions that are unused. In the minimum power standby mode, all device functions can be turned off leaving only the 3.3-V regulator active.

#### 8.4.1.3 SLEEP

In addition to STANDBY, there is also a SLEEP mode. In SLEEP mode the Host orders the bq76925 device to shutdown all internal circuitry and all functions including the LDO regulator. The device consumes a minimal amount of current (< 1.5  $\mu$ A) in SLEEP mode due only to leakage and powering of the wake-up detection circuitry.

SLEEP mode is entered by writing a '1' to the SLEEP bit in the POWER\_CTL register. Wake-up is achieved by pulling up the ALERT pin; however, the wake-up circuitry is not armed until the voltage at V3P3 drops to approximately 0 V. To facilitate the discharge of V3P3, an internal  $3-k\Omega$  pulldown resistor is connected from V3P3 to VSS during the time that sleep mode is active. Once V3P3 is discharged, the bq76925 may be awakened by pulling the ALERT pin above V<sub>WAKE</sub> (2-V maximum).

The SLEEP\_DIS bit in the POWER\_CTL register acts as an override to the SLEEP function. When SLEEP\_DIS is set to '1', writing the SLEEP bit has no effect (that is, SLEEP mode cannot be entered). If SLEEP\_DIS is set after SLEEP mode has been entered, the device will immediately exit SLEEP mode. This scenario can arise if SLEEP\_DIS is set after SLEEP is set, but before V3P3 has discharged below a valid operating voltage. This scenario can also occur if the V3P3 pin is held up by external circuitry and not allowed to fully discharge.

If the overcurrent alert function is not used, the ALERT pin can function as a dedicated wake-up pin. Otherwise, the ALERT pin will normally be pulled up to the LDO voltage, so care must be taken in the system design so that the wake-up signal does not interfere with proper operation of the regulator.

#### 8.5 Programming

#### 8.5.1 Host Interface

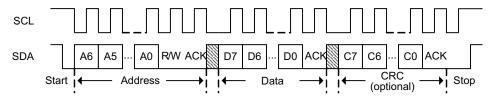

The Host communicates with the AFE through an  $I^2C$  interface. A CRC byte may optionally be used to ensure robust operation. The CRC is calculated over all bytes in the message according to the polynomial  $x^8 + x^2 + x + 1$ .

#### 8.5.1.1 $m \ell^2 C$ Addressing

In order to reduce communications overhead, the addressing scheme for the I<sup>2</sup>C interface combines the slave device address and device register addresses into a single 7-bit address as shown below.

#### ADDRESS[6:0] = (I2C\_GROUP\_ADDR[3:0] << 3) + REG\_ADDR[4:0]

The I2C\_GROUP\_ADDR is a 4-bit value stored in the EEPROM. REG\_ADDR is the 5-bit register address being accessed, and can range from 0x00 - 0x1F. The factory programmed value of the group address is '0100'. Contact TI if an alternative group address is required.

For the default I2C\_GROUP\_ADDR, the combined address can be formed as shown in Table 4.

| Table 4. Combined I <sup>2</sup> C Address for Default Group |  |

|--------------------------------------------------------------|--|

| Address                                                      |  |

| ADDRESS[6:0] |   |                  |  |  |  |  |

|--------------|---|------------------|--|--|--|--|

| 6 5 4:0      |   |                  |  |  |  |  |

| 0            | 1 | Register address |  |  |  |  |

#### 8.5.1.2 Bus Write Command to bq76925

The Host writes to the registers of the bq76925 device as shown in Figure 13. The bq76925 acknowledges each received byte by pulling the SDA line low during the acknowledge period.

The Host may optionally send a CRC after the Data byte as shown. The CRC for write commands is enabled by writing the CRC\_EN bit in the CONFIG\_2 register. If the CRC is not used, then the Host generates the Stop condition immediately after the bq76925 acknowledges receipt of the Data byte.

When the CRC is disabled, the bq76925 device will act on the command on the first rising edge of SCL following the ACK of the Data byte. This occurs as part of the normal bus setup prior to a Stop. If a CRC byte is sent while the CRC is disabled, the first rising edge of the SCL following the ACK will be the clocking of the first bit of the CRC. The bq76925 device does not distinguish these two cases. In both cases, the command will complete normally, and in the latter case the CRC will be ignored.

Figure 13. I<sup>2</sup>C Write Command

#### 8.5.1.3 Bus Read Command from bq76925 Device

The Host reads from the registers of the bq76925 device as shown in Figure 14. This protocol is similar to the write protocol, except that the slave now drives data back to the Host. The bq76925 device acknowledges each received byte by pulling the SDA line low during the acknowledge period. When the bq76925 device sends data back to the Host, the Host drives the acknowledge.

The Host may optionally request a CRC byte following the Data byte as shown. The CRC for read commands is always enabled, but not required. If the CRC is not used, then the Host simply NACK's the Data byte and then generates the Stop condition.

Figure 14. I<sup>2</sup>C Read Command

### 8.6 Register Maps

| Address     | Name         | Access | D7       | D6        | D5        | D4        | D3             | D2        | D1        | D0        |

|-------------|--------------|--------|----------|-----------|-----------|-----------|----------------|-----------|-----------|-----------|

| 0x00        | STATUS       | R/W    |          |           |           |           |                | ALERT     | CRC_ERR   | POR       |

| 0x01        | CELL_CTL     | R/W    |          |           | VCO       | UT_SEL    |                | CELL_SEL  |           |           |

| 0x02        | BAL_CTL      | R/W    |          |           | BAL_6     | BAL_5     | BAL_4          | BAL_3     | BAL_2     | BAL_1     |

| 0x03        | CONFIG_1     | R/W    |          | I_TH      | IRESH     |           | I_COMP_POL     | I_AMP_CAL |           | I_GAIN    |

| 0x04        | CONFIG_2     | R/W    | CRC_EN   |           |           |           |                |           |           | REF_SEL   |

| 0x05        | POWER_CTL    | R/W    | SLEEP    | SLEEP_DIS |           | I_COMP_EN | I_AMP_EN       | VC_AMP_EN | VTB_EN    | REF_EN    |

| 0x06        | Reserved     | R/W    |          |           |           |           |                |           |           |           |

| 0x07        | CHIP_ID      | RO     |          |           |           | CH        | IIP_ID         |           |           |           |

| 0x08 – 0x0F | Reserved     | R/W    |          |           |           |           |                |           |           |           |

| 0x10        | VREF_CAL     | EEPROM |          | VREF_OF   | FSET_CORR |           | VREF_GAIN_CORR |           |           |           |

| 0x11        | VC1_CAL      | EEPROM |          | VC1_OFF   | SET_CORR  |           | VC1_GAIN_CORR  |           |           |           |

| 0x12        | VC2_CAL      | EEPROM |          | VC2_OFF   | SET_CORR  |           | VC2_GAIN_CORR  |           |           |           |

| 0x13        | VC3_CAL      | EEPROM |          | VC3_OFF   | SET_CORR  |           | VC3_GAIN_CORR  |           |           |           |

| 0x14        | VC4_CAL      | EEPROM |          | VC4_OFF   | SET_CORR  |           |                | VC4_GA    | N_CORR    |           |

| 0x15        | VC5_CAL      | EEPROM |          | VC5_OFF   | SET_CORR  |           |                | VC5_GA    | N_CORR    |           |

| 0x16        | VC6_CAL      | EEPROM |          | VC6_OFF   | SET_CORR  |           |                | VC6_GA    | N_CORR    |           |

| 0x17        | VC_CAL_EXT_1 | EEPROM | VC1_OC_4 | VC1_GC_4  | VC2_OC_4  | VC2_GC_4  |                |           |           |           |

| 0x18        | VC_CAL_EXT_2 | EEPROM | VC3_OC_4 | VC3_GC_4  | VC4_OC_4  | VC4_GC_4  | VC5_OC_4       | VC5_GC_4  | VC6_OC_4  | VC6_GC_4  |

| 0x10 - 0x1A | Reserved     | EEPROM |          |           |           |           |                |           |           |           |

| 0x1B        | VREF_CAL_EXT | EEPROM |          |           |           |           | 1              | VREF_OC_5 | VREF_OC_4 | VREF_GC_4 |

| 0x1C - 0x1F | Reserved     | EEPROM |          |           |           |           |                |           |           |           |

#### 8.6.1 Register Descriptions

#### **Table 5. STATUS Register**

| Address | Name   | Туре      | D7 | D6 | D5 | D4 | D3 | D2    | D1      | D0  |

|---------|--------|-----------|----|----|----|----|----|-------|---------|-----|

| 0x00    | STATUS | R/W       |    |    |    |    |    | ALERT | CRC_ERR | POR |

|         |        | Defaults: | 0  | 0  | 0  | 0  | 0  | 0     | 0       | 1   |

ALERT: Over-current alert. Reflects state of the over-current comparator. '1' = over-current.

CRC\_ERR: CRC error status. Updated on every  $I^2C$  write packet when CRC\_EN = '1'. '1' = CRC error.

POR: Power on reset flag. Set on each power-up and wake-up from sleep. May be cleared by writing with '0'.

### Table 6. CELL\_CTL

| Address | Name     | Туре      | D7 <sup>(1)</sup> | D6 | D5   | D4    | D3 | D2 | D1       | D0 |

|---------|----------|-----------|-------------------|----|------|-------|----|----|----------|----|

| 0x01    | CELL_CTL | R/W       |                   |    | VCOU | T_SEL |    |    | CELL_SEL |    |

|         |          | Defaults: | 0                 | 0  |      | 0     | 0  |    | 0        |    |

(1) This bit must be kept = 0

VCOUT\_SEL: VCOUT MUX select. Selects the VCOUT pin function as follows.

| VCOUT_SEL | VCOUT                          |

|-----------|--------------------------------|

| 0 0       | VSS                            |

| 0 1       | VCn (n determined by CELL_SEL) |

| 1 0       | VREF × 0.5                     |

| 11        | VREF × 0.85                    |

#### **Table 7. VCOUT Pin Functions**

CELL\_SEL: Cell select. Selects the VCn input for output on VCOUT when VCOUT\_SEL = '01'.

VCOUT\_SEL

Copyright © 2011–2016, Texas Instruments Incorporated

#### Table 8. Cell Selection

vcout

| 0 1 | 000   | VC1                   |

|-----|-------|-----------------------|

| 0 1 | 0 0 1 | VC2                   |

| 0 1 | 010   | VC3                   |

| 0 1 | 011   | VC4                   |

| 0 1 | 100   | VC5                   |

| 0 1 | 101   | VC6                   |

| 0 1 | 110   | V <sub>TEMP,INT</sub> |

| 0 1 | 111   | Hi-Z                  |

CELL\_SEL

#### Table 9. BAL\_CTL

| Address | Name    | Туре      | D7 | D6 | D5    | D4    | D3    | D2    | D1    | D0    |

|---------|---------|-----------|----|----|-------|-------|-------|-------|-------|-------|

| 0x02    | BAL_CTL | R/W       |    |    | BAL_6 | BAL_5 | BAL_4 | BAL_3 | BAL_2 | BAL_1 |

|         |         | Defaults: | 0  | 0  | 0     | 0     | 0     | 0     | 0     | 0     |

BAL\_n: Balance control for cell n. When set, turns on balancing transistor for cell n. Setting of two adjacent balance controls is not permitted. If two adjacent balance controls are set, neither cell balancing transistor will be turned on. However, the BAL\_n bits will retain their values.

#### Table 10. CONFIG\_1

| Address | Name     | Туре      | D7 | D6   | D5    | D4 | D3         | D2        | D1 | D0     |

|---------|----------|-----------|----|------|-------|----|------------|-----------|----|--------|

| 0x03    | CONFIG_1 | R/W       |    | I_TF | IRESH |    | I_COMP_POL | I_AMP_CAL |    | I_GAIN |

|         |          | Defaults: | 0  |      |       | 0  | 0          | 0         | 0  |        |

I\_THRESH: Current comparator threshold. Sets the threshold of the current comparator as follows:

| I_THRESH | Comparator Threshold |

|----------|----------------------|

| 0x0      | 25 mV                |

| 0x1      | 50 mV                |

| 0x2      | 75 mV                |

| 0x3      | 100 mV               |

| 0x4      | 125 mV               |

| 0x5      | 150 mV               |

| 0x6      | 175 mV               |

| 0x7      | 200 mV               |

| 0x8      | 225 mV               |

| 0x9      | 250 mV               |

| 0xA      | 275 mV               |

| 0xB      | 300 mV               |

| 0xC      | 325 mV               |

| 0xD      | 350 mV               |

| 0xE      | 375 mV               |

| 0xF      | 400 mV               |

#### Table 11. Current Comparator Threshold

I\_COMP\_POL: Current comparator polarity select. When '0', trips on discharge current (SENSEP > SENSEN). When '1', trips on charge current (SENSEP < SENSEN).

I\_AMP\_CAL: Current amplifier calibration. When '0', current amplifier reports SENSEN with respect to VSS. When '1', current amplifier reports SENSEP with respect to VSS. This bit can be used for offset cancellation as described under OPERATIONAL OVERVIEW.

I\_GAIN: Current amplifier gain. Sets the nominal gain of the current amplifier as follows.

22

www.ti.com

# Table 12. Nominal Gain of the Current Amplifier

| I_GAIN | Current amp<br>gain |

|--------|---------------------|

| 0      | 4                   |

| 1      | 8                   |

#### Table 13. CONFIG\_2

| Address | Name     | Туре      | D7     | D6 | D5 | D4 | D3 | D2 | D1 | D0      |

|---------|----------|-----------|--------|----|----|----|----|----|----|---------|

| 0x04    | CONFIG_2 | R/W       | CRC_EN |    |    |    |    |    |    | REF_SEL |

|         |          | Defaults: | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0       |

CRC\_EN: CRC enable. Enables CRC comparison on write. When '1', CRC is enabled. CRC on read is always enabled but is optional for Host.

REF\_SEL: Reference voltage selection. Sets reference voltage output on VREF pin, cell-voltage amplifier gain and VIOUT output range.