**DRV8215**

JAJSU38 - APRIL 2024

# DRV8215 速度調整機能およびストール検出機能内蔵、11V、4A、ブラシ付き DC モーター ドライバ

## 1 特長

- N チャネル、H ブリッジ、ブラシ付き DC モーター ドラ イバ

- 動作電源電圧範囲:1.65V~11V

- 電圧および速度レギュレーションを内蔵

- ソフトスタートおよびストップ機能による突入電流から の保護

- 240mΩ の R<sub>DS(on)</sub> (ハイサイド+ローサイド)

- 高い出力電流能力:4A ピーク、2A RMS

- I<sup>2</sup>C 制御インターフェイス搭載 PWM

- I<sup>2</sup>C レジスタでの構成と診断

- マルチフォロア動作のサポート

- 標準およびファースト I<sup>2</sup>C モードをサポート

- 1.8V、3.3V、5V のロジック入力をサポート

- 電流センスおよび電流レギュレーション機能を内蔵

- アナログ電流センス出力 (IPROPI)

- ゲイン選択機能:

- 最小 10mA までの高精度電流センス

- R<sub>DS (ON)</sub> と過電流制限を最適化

- 100% デューティ サイクルの内部チャージ ポンプ

- 低消費電力のスリープ モードによる長いバッテリ寿命 - < 100nA の最大スリープ電流

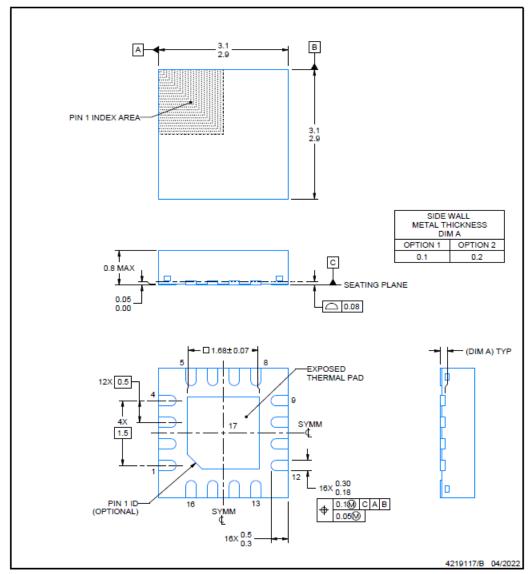

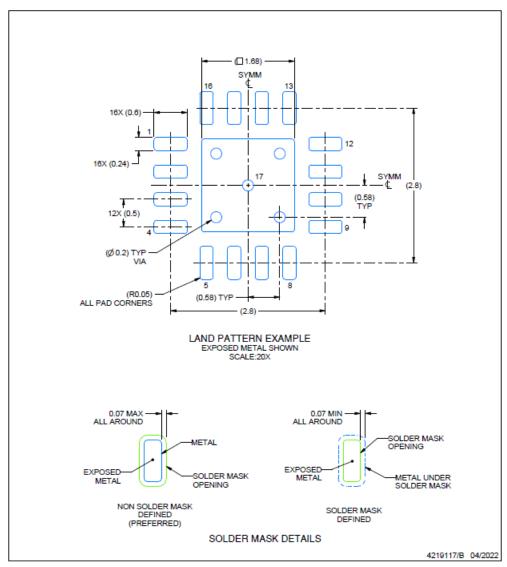

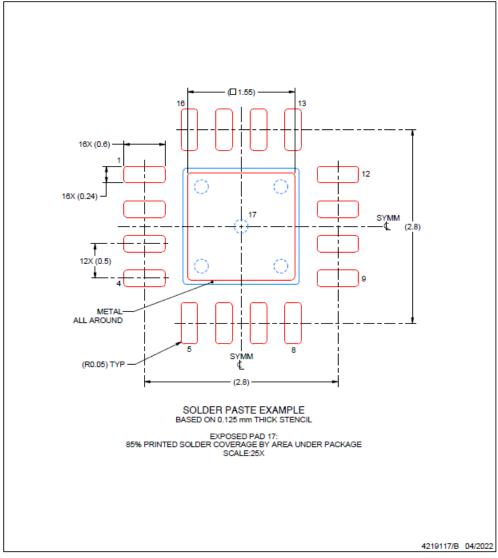

- 小さなパッケージと占有面積

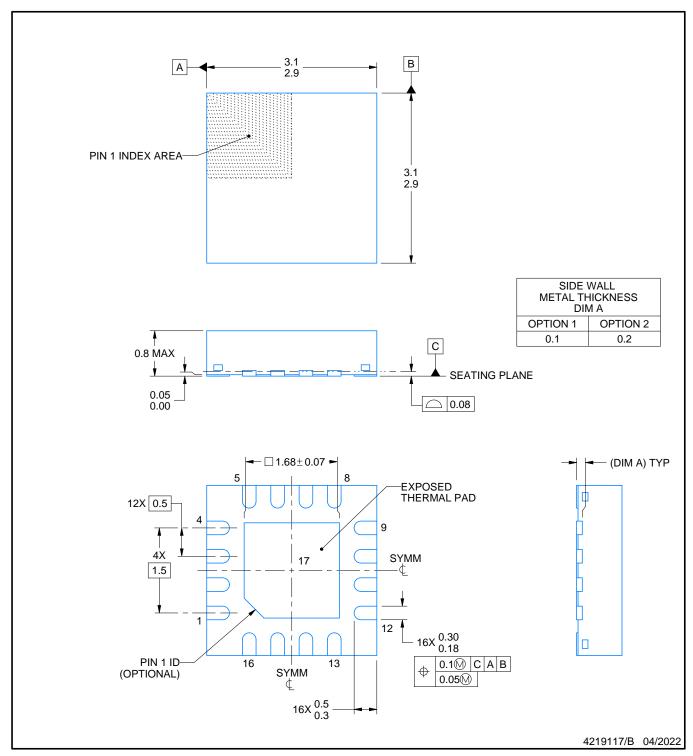

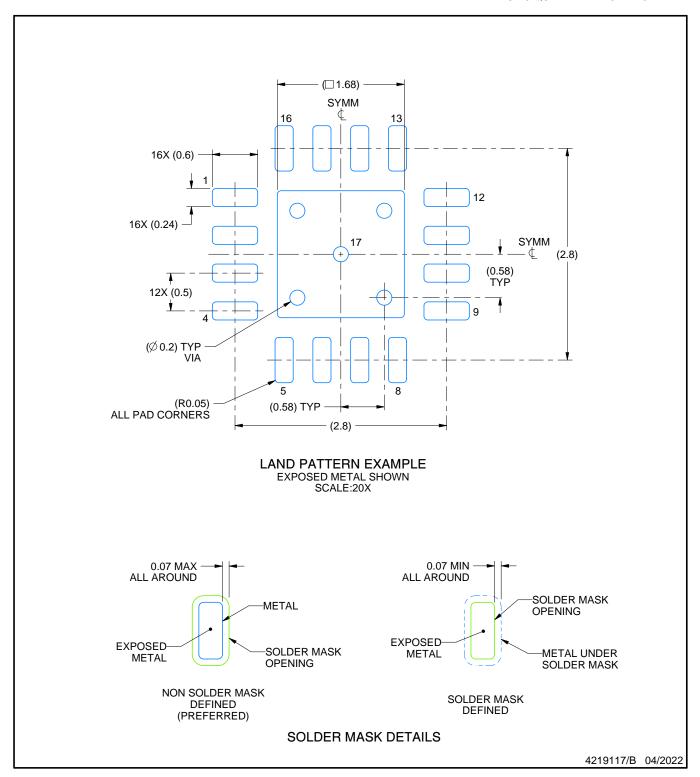

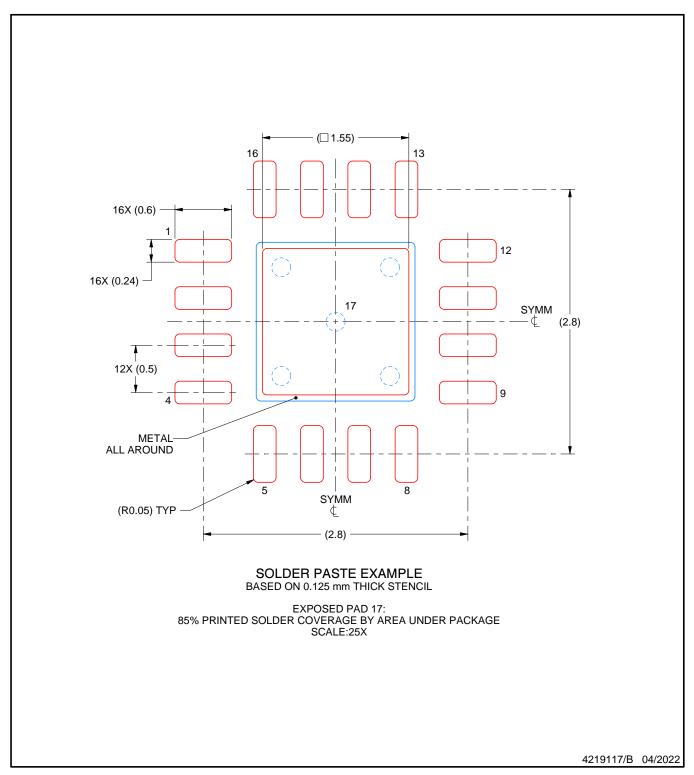

- PowerPAD™付き 16ピンWQFN、3×3mm

- 保護機能内蔵

- VCC 低電圧誤動作防止 (UVLO)

- 過電流保護 (OCP)

- サーマル シャットダウン (TSD)

- ストール検出

- 過電圧保護 (OVP)

# 2 アプリケーション

- 電子スマートロック

- 電子 / ロボット玩具

- 水道およびガスメーター

- 輸液ポンプおよびその他のポータブル医療機器

- 電動歯ブラシ、美容 & 身だしなみ

- ポータブル プリンタおよび POS (販売時点管理) デバ イス

# 3 概要

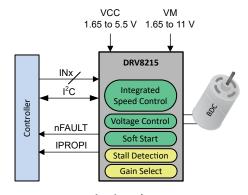

DRV8215 は、速度および電圧レギュレーション機能に加 えて、ストール検出、電流検出出力、電流レギュレーショ ン、保護回路などの追加機能を内蔵した高性能統合型 H ブリッジ モータードライバです。

この内蔵された速度および電圧レギュレーション機能は、 モーター電圧および電流情報を使用してモーターの速度 または電圧を制御するため、速度を検出するための外部 センサは不要です。これにより、基板のサイズと設計の複 雑さが低減し、システム全体のコストが削減されます。内蔵 の速度レギュレーション機能により、入力電源電圧が変化 してもモータ速度が一定に保たれるため、消費電流が最 小限に抑えられ、長期的に電力が節約されます。これは、 さまざまな負荷条件を持つアプリケーションや、入力電圧 が一定ではない操作に対してバッテリ電源に依存するア プリケーションで重要です。ソフトスタートおよびストップに より、制御されたターンオンおよびターンオフ時間が可能 になり、大きな突入電流を低減してモータ巻線を損傷から 保護することで、システムの信頼性と耐用期間が向上しま す。

内部カレントミラーは、電流センスとレギュレーションを実 装しています。そのため、大電力シャント抵抗を使う必要 がなく、基板面積を節約しシステムコストを低減できます。 IPROPI 電流センス出力を使うと、マイコンはモーターのス トールまたは負荷条件の変化を検出できます。ゲイン選択 機能により、平均モーター電流 10mA までの高精度の電 流センスが可能です。VREFピンを使うことで、起動およ び高負荷イベント中もマイコンを使わずにモーター電流を レギュレーションできます。デバイスは、センサレスモータ ストール検出とマイコンへのレポートをサポートしていま す。

#### 製品情報

|         | ACHHID TK            |                                   |

|---------|----------------------|-----------------------------------|

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ (公<br>称) <sup>(2)</sup> |

| DRV8215 | WQFN (16)            | 3.00mm × 3.00mm                   |

- 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

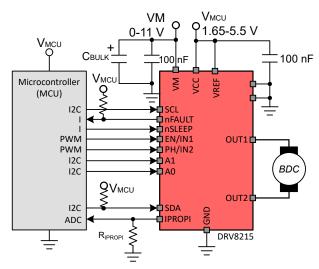

概略回路図

# **Table of Contents**

|   | 44. H                                  |   |

|---|----------------------------------------|---|

| 1 | 特長                                     | 1 |

| 2 | アプリケーション                               | 1 |

| 3 | 概要                                     | 1 |

| 4 | Device Comparison                      | 3 |

| 5 | Pin Configuration and Functions        | 2 |

| 6 | Specifications                         | Ę |

|   | 6.1 Absolute Maximum Ratings           | Ę |

|   | 6.2 ESD Ratings                        |   |

|   | 6.3 Recommended Operating Conditions   |   |

|   | 6.4 Thermal Information                | 6 |

|   | 6.5 Electrical Characteristics         | 6 |

|   | 6.6 I2C Timing Requirements            | 8 |

|   | 6.7 Timing Diagrams                    |   |

|   | 6.8 Typical Operating Characteristics1 | ( |

| 7 | Detailed Description1                  | 1 |

|   | 7.1 Overview1                          | 1 |

|   | 7.2 Functional Block Diagram1          | 2 |

|   | 7.3 Feature Description                |   |

|   | 7.4 Device Functional Modes3           | 2 |

| 7.5 Programming                           | 33              |

|-------------------------------------------|-----------------|

| 8 Register Map                            |                 |

| 8.1 DRV8215 STATUS Registers              |                 |

| 8.2 DRV8215 CONFIG Registers              |                 |

| 8.3 DRV8215_CTRL Registers                | 54              |

| 9 Application and Implementation          | <mark>67</mark> |

| 9.1 Application Information               | <mark>67</mark> |

| 9.2 Typical Application: Brushed DC Motor | <mark>67</mark> |

| 9.3 Power Supply Recommendations          | 76              |

| 9.4 Layout                                | <mark>77</mark> |

| 10 デバイスおよびドキュメントのサポート                     | 78              |

| 10.1ドキュメントの更新通知を受け取る方法                    | 78              |

| 10.2 サポート・リソース                            | 78              |

| 10.3 Trademarks                           |                 |

| 10.4 静電気放電に関する注意事項                        | 78              |

| 10.5 用語集                                  |                 |

| 11 Revision History                       |                 |

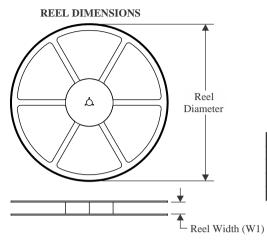

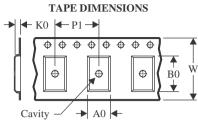

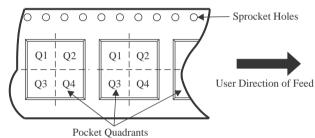

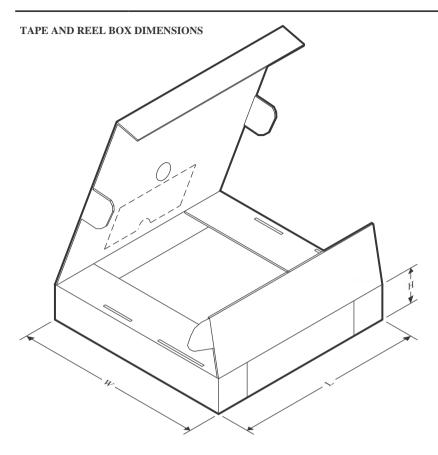

| 12 メカニカル、パッケージ、および注文情報                    | 79              |

|                                           |                 |

# **4 Device Comparison**

# 表 4-1. Device Comparison Table

| Part Number | Package | Supply VM<br>(V) | R <sub>DS(ON)</sub> (mΩ) | RMS Current<br>Capacity (A) | Sensorless<br>Position<br>Sensing | Speed<br>Regulation | Stall<br>Detection | Package Size |

|-------------|---------|------------------|--------------------------|-----------------------------|-----------------------------------|---------------------|--------------------|--------------|

| DRV8214     | RTE     | 1.65 to 11       | 240                      | 2                           | Yes                               | Yes                 | Yes                | 3 mm × 3 mm  |

| DRV8215     | RTE     | 1.65 to 11       | 240                      | 2                           | No                                | Yes                 | Yes                | 3 mm × 3 mm  |

| DRV8234     | RTE     | 4.5 to 38        | 600                      | 2                           | Yes                               | Yes                 | Yes                | 3 mm × 3 mm  |

| DRV8235     | RTE     | 4.5 to 38        | 600                      | 2                           | No                                | Yes                 | Yes                | 3 mm × 3 mm  |

| DRV8213     | RTE     | 1.65 to 11       | 240                      | 2                           | No                                | No                  | Yes                | 3 mm × 3 mm  |

| DRV8213     | DSG     | 1.65 to 11       | 240                      | 2                           | No                                | No                  | No                 | 2 mm × 2 mm  |

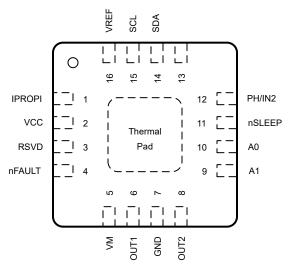

# **5 Pin Configuration and Functions**

図 5-1. RTE Package 16-Pin WQFN Top View

表 5-1. Pin Functions

|        | PIN | (4)                 |                                                                                                                                                                   |  |

|--------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | RTE | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                       |  |

| IPROPI | 1   | PWR                 | Analog current output proportional to load current. Connect a resistor from IPROPI to ground.                                                                     |  |

| vcc    | 2   | PWR                 | Logic power supply. Bypass this pin to the GND pin with a 0.1-μF ceramic capacitor rated for VCC.                                                                 |  |

| RSVD   | 3   | _                   | Reserved. Leave this pin unconnected.                                                                                                                             |  |

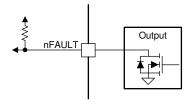

| nFAULT | 4   | OD                  | Fault indicator output. Pulled low during a fault condition. Connect an external pullup resistor for open-drain operation.                                        |  |

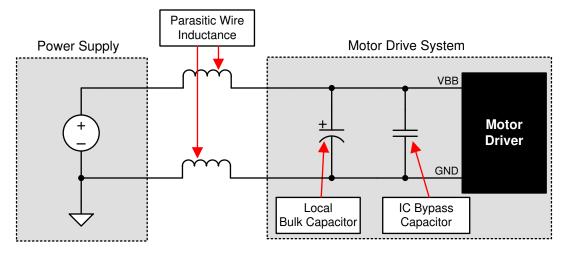

| VM     | 5   | PWR                 | Motor power supply. Bypass this pin to the GND pin with a 0.1-µF ceramic capacitor as well as sufficient bulk capacitance rated for VM.                           |  |

| OUT1   | 6   | 0                   | H-bridge output. Connect directly to the motor.                                                                                                                   |  |

| GND    | 7   | PWR                 | Device ground. Connect to system ground.                                                                                                                          |  |

| OUT2   | 8   | 0                   | H-bridge output. Connect directly to the motor.                                                                                                                   |  |

| A1     | 9   | I                   | I <sup>2</sup> C base address select pin. Tri-level input.                                                                                                        |  |

| A0     | 10  | I                   | I <sup>2</sup> C base address select pin. Tri-level input.                                                                                                        |  |

| nSLEEP | 11  | I                   | Sleep mode input. Logic high to enable device. Logic low to enter low-power sleep mode. Internal pulldown resistor.                                               |  |

| PH/IN2 | 12  | I                   | Controls the H-bridge output. Has internal pulldown.                                                                                                              |  |

| EN/IN1 | 13  | I                   | Controls the H-bridge output. Has internal pulldown.                                                                                                              |  |

| SDA    | 14  | I                   | I <sup>2</sup> C data signal. The SDA pin requires a pullup resistor.                                                                                             |  |

| SCL    | 15  | I                   | l <sup>2</sup> C clock signal.                                                                                                                                    |  |

| VREF   | 16  | I                   | Analog input to set current regulation and stall detection level.                                                                                                 |  |

| PAD    | _   | _                   | Thermal pad. Connect to board ground. For good thermal dissipation, use large ground planes on multiple layers, and multiple nearby vias connecting those planes. |  |

(1) I = Input, O = Output, PWR = Power, OD = Open-Drain Output

# **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating temperature range (unless otherwise noted)(1)

|                                                      |                                          | MIN                   | MAX                                                                                                                                                 | UNIT |

|------------------------------------------------------|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Power supply pin voltage                             | VM                                       | -0.5                  | 12                                                                                                                                                  | V    |

| Logic power supply pin voltage                       | VCC                                      | -0.5                  | 5.75                                                                                                                                                | V    |

| Power supply transient voltage ramp                  | VM, VCC                                  | 0                     | 2                                                                                                                                                   | V/µs |

| Logic pin voltage                                    | EN/IN1, PH/IN2, A1, A0, SDA, SCL, nSLEEP | -0.3                  | 5.75                                                                                                                                                | V    |

| Open-drain output pin voltage                        | nFAULT                                   | -0.3                  | 5.75                                                                                                                                                | V    |

| Proportional current output pin voltage, VM ≥ 5.45 V | IDDODI                                   | -0.3                  | 5.75                                                                                                                                                | V    |

| Proportional current output pin voltage, VM < 5.45 V | IPROPI                                   | -0.3                  | 12<br>5.75<br>2<br>5.75<br>5.75<br>5.75<br>V <sub>VM</sub> + 0.3<br>5.75<br>V <sub>VM</sub> +V <sub>SD</sub><br>Internally<br>Limited<br>125<br>150 | V    |

| Reference input pin voltage                          | VREF                                     | -0.3                  | 5.75                                                                                                                                                | V    |

| Output pin voltage                                   | OUTx                                     | -V <sub>SD</sub>      | V <sub>VM</sub> +V <sub>SD</sub>                                                                                                                    | V    |

| Output current                                       | OUTx                                     | Internally<br>Limited | , ,                                                                                                                                                 | Α    |

| Ambient temperature, T <sub>A</sub>                  | ,                                        | -40                   | 125                                                                                                                                                 | °C   |

| Junction temperature, T <sub>J</sub>                 |                                          | -40                   | 150                                                                                                                                                 | °C   |

| Storage temperature, T <sub>stg</sub>                |                                          | -65                   | 150                                                                                                                                                 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V(ESD)             | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ± 2000 V may actually have higher performance.

### **6.3 Recommended Operating Conditions**

over operating temperature range (unless otherwise noted)

|                      |                                 |                                           | MIN  | NOM MAX                                 | UNIT |

|----------------------|---------------------------------|-------------------------------------------|------|-----------------------------------------|------|

| $V_{VM}$             | Power supply voltage            | VM                                        | 0    | 11                                      | V    |

| V <sub>VCC</sub>     | Power supply voltage            | VCC                                       | 1.65 | 5.5                                     | V    |

| V <sub>IN</sub>      | Logic input voltage             | EN/IN1, PH/IN2,A1, A0, SDA,<br>SCL,nSLEEP | 0    | 5.5                                     | V    |

| f <sub>PWM</sub>     | PWM frequency                   | INx                                       | 0    | 200                                     | kHz  |

| V <sub>OD</sub>      | Open drain pullup voltage       | nFAULT                                    | 0    | 5.5                                     | V    |

| I <sub>OD</sub>      | Open drain output current       | nFAULT                                    | 0    | 5                                       | mA   |

| I <sub>OUT</sub> (1) | Peak output current             | OUTx                                      | 0    | 4                                       | Α    |

| I <sub>IPROPI</sub>  | Current sense output current    | IPROPI                                    | 0    | 1                                       | mA   |

| $V_{VREF}$           | Current limit reference voltage | VREF                                      | 0    | min (3.3,<br>V <sub>VM</sub> -<br>1.25) | V    |

| T <sub>A</sub>       | Operating ambient temperature   | •                                         | -40  | 125                                     | °C   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ± 500 V may actually have higher performance.

over operating temperature range (unless otherwise noted)

|       |                                | MIN | NOM | MAX | UNIT |

|-------|--------------------------------|-----|-----|-----|------|

| $T_J$ | Operating junction temperature | -40 |     | 150 | °C   |

(1) Power dissipation and thermal limits must be observed

#### **6.4 Thermal Information**

|                       |                                              | DEVICE     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                       |                                              | 16 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 47.8       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 48.2       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 22.4       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 22.4       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 8.6        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### **6.5 Electrical Characteristics**

0 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V and 1.65 V  $\leq$  V<sub>VCC</sub>  $\leq$  11 V,  $-40^{\circ}$ C  $\leq$  T<sub>J</sub>  $\leq$  150 $^{\circ}$ C (unless otherwise noted). Typical values are at T<sub>J</sub> = 27 $^{\circ}$ C, V<sub>VM</sub> = 5 V, V<sub>VCC</sub> = 3.3 V.

|                       | PARAMETER                           | TEST CONDITIONS                                                                                  | MIN  | TYP | MAX  | UNIT |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------------|------|-----|------|------|

| POWER SU              | JPPLIES (VM, VCC)                   |                                                                                                  |      |     |      |      |

| I <sub>VMQ</sub>      | VM sleep mode current               | nSLEEP = 0 V, $V_{VM}$ = 5 V, $V_{VCC}$ = 3.3 V, $T_J$ = 27°C, OVP disabled                      |      | 100 | 170  | nA   |

| I <sub>VMQ_OVP</sub>  | VM sleep mode current               | nSLEEP = 0 V, $V_{VM}$ = 5 V, $V_{VCC}$ = 3.3 V, $T_J$ = 27°C, OVP enabled                       |      | 0.1 | 1    | μΑ   |

| I <sub>VM</sub>       | VM active mode current              | nSLEEP = 3.3 V, EN/IN1 = 3.3 V, PH/IN2<br>= 0 V, V <sub>VM</sub> = 5 V, V <sub>VCC</sub> = 3.3 V |      | 1.3 | 1.9  | mA   |

| I <sub>VCCQ</sub>     | VCC sleep mode current              | nSLEEP = 0 V, $V_{VM}$ = 5 V, $V_{VCC}$ = 3.3 V, $T_{J}$ = 27°C                                  |      | 1   | 3.0  | nA   |

| I <sub>VCC</sub>      | VCC active mode current             | nSLEEP = 3.3 V, EN/IN1 = 3.3 V, PH/IN2<br>= 0 V, V <sub>VM</sub> = 5 V, V <sub>VCC</sub> = 3.3 V |      | 1.5 | 2    | mA   |

| t <sub>WAKE</sub>     | Turnon time                         | nSLEEP = 1 to I <sup>2</sup> C ready                                                             |      |     | 410  | μs   |

| LOGIC-LEV             | /EL INPUTS (EN/IN1, PH/IN2, SDA, SC | CL, nSLEEP)                                                                                      |      |     | •    |      |

| V <sub>IL</sub>       | Input logic low voltage             |                                                                                                  | 0    |     | 0.4  | V    |

| $V_{IH}$              | Input logic high voltage            |                                                                                                  | 1.45 |     | 5.5  | V    |

| $V_{HYS}$             | Input hysteresis                    |                                                                                                  | 49   |     |      | mV   |

| I <sub>IL</sub>       | Input logic low current             | V <sub>I</sub> = 0 V                                                                             | -1   |     | 1    | μΑ   |

| I <sub>IH</sub>       | Input logic high current            | V <sub>I</sub> = 5 V                                                                             | 15   |     | 35   | μA   |

| R <sub>PD</sub>       | Input pulldown resistance, INx      |                                                                                                  |      | 200 |      | kΩ   |

| t <sub>DEGLITCH</sub> | Input logic deglitch, INx           |                                                                                                  |      | 50  |      | ns   |

| TRI-LEVEL             | . INPUTS (A1, A0)                   |                                                                                                  |      |     |      |      |

| V <sub>THYS</sub>     | Tri-level input logic low voltage   |                                                                                                  | 0    |     | 0.4  | V    |

| I <sub>TIL</sub>      | Tri-level input Hi-Z voltage        |                                                                                                  | 0.75 |     | 1.05 | V    |

| I <sub>TIZ</sub>      | Tri-level input logic high voltage  |                                                                                                  | 1.45 |     | 5.5  | V    |

| R <sub>TPD</sub>      | Tri-level pulldown resistance       | to GND                                                                                           |      | 90  |      | kΩ   |

| I <sub>TPU</sub>      | Tri-level pullup current            | to VCC                                                                                           |      | 10  |      | μA   |

0 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V and 1.65 V  $\leq$  V<sub>VCC</sub>  $\leq$  11 V,  $-40^{\circ}$ C  $\leq$  T<sub>J</sub>  $\leq$  150 $^{\circ}$ C (unless otherwise noted). Typical values are at T<sub>J</sub> = 27 $^{\circ}$ C, V<sub>VM</sub> = 5 V, V<sub>VCC</sub> = 3.3 V.

|                        | PARAMETER                                            | TEST CONDITIONS                                                                                                             | MIN | TYP  | MAX      | UNIT |

|------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|------|----------|------|

| OPEN-DRA               | IN OUTPUTS (nFAULT, SDA)                             |                                                                                                                             |     |      |          |      |

| V <sub>OL</sub>        | Output logic low voltage                             | I <sub>OD</sub> = 5 mA                                                                                                      |     |      | 0.4      | V    |

| l <sub>oz</sub>        | Output logic high current                            | V <sub>OD</sub> = VCC                                                                                                       | -1  |      | 1        | μA   |

| t <sub>PW_nFAULT</sub> | nFAULT low pulse width                               | RC Count overflow, RC_REP = 11b                                                                                             | 30  | 50   | 70       | μs   |

| C <sub>B</sub>         | SDA capacitive load for each bus line                |                                                                                                                             |     |      | 400      | pF   |

| DRIVER OU              | TPUTS (OUTx)                                         |                                                                                                                             |     |      | <u> </u> |      |

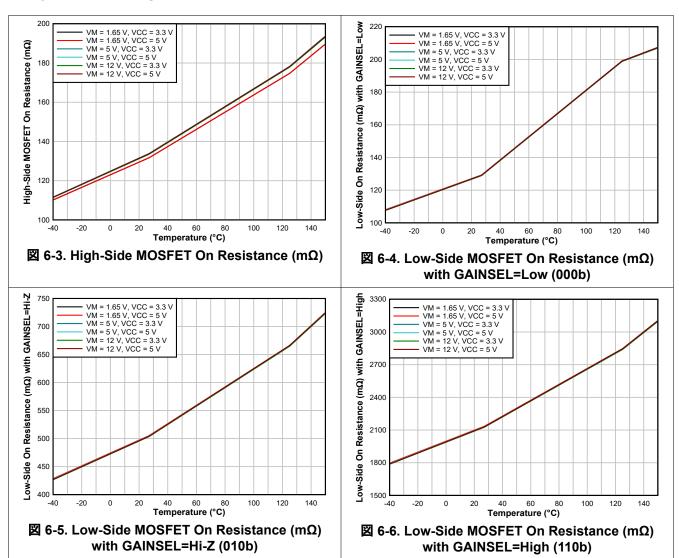

| R <sub>DS(ON)_HS</sub> | High-side MOSFET on resistance                       | I <sub>OUTx</sub> = 1 A; T <sub>J</sub> = 25 °C                                                                             |     | 120  | 155      | mΩ   |

| R <sub>DS(ON)_HS</sub> | High-side MOSFET on resistance                       | I <sub>OUTx</sub> = 1 A; T <sub>J</sub> = 125 °C                                                                            |     | 180  | 220      | mΩ   |

| R <sub>DS(ON)_HS</sub> | High-side MOSFET on resistance                       | I <sub>OUTx</sub> = 1 A; T <sub>J</sub> = 150 °C                                                                            |     | 200  | 250      | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 00Xb | I <sub>OUTx</sub> = -1 A; T <sub>J</sub> = 25 °C                                                                            |     | 120  | 145      | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 00Xb | I <sub>OUTx</sub> = -1 A; T <sub>J</sub> = 125 °C                                                                           |     | 180  | 220      | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 00Xb | I <sub>OUTx</sub> = -1 A; T <sub>J</sub> = 150 °C                                                                           |     | 200  | 250      | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 01Xb | I <sub>OUTx</sub> = -250 mA; T <sub>J</sub> = 25 °C                                                                         |     | 440  | 530      | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 01Xb | I <sub>OUTx</sub> = -250 mA; T <sub>J</sub> = 125 °C                                                                        |     | 660  | 800      | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 01Xb | I <sub>OUTx</sub> = -250 mA; T <sub>J</sub> = 150 °C                                                                        |     | 750  | 900      | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 11Xb | I <sub>OUTx</sub> = -50 mA; T <sub>J</sub> = 25 °C                                                                          |     | 2040 | 2450     | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 11Xb | I <sub>OUTx</sub> = -50 mA; T <sub>J</sub> = 125 °C                                                                         |     | 3050 | 3650     | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance,<br>CS_GAIN_SEL = 11Xb | I <sub>OUTx</sub> = -50 mA; T <sub>J</sub> = 150 °C                                                                         |     | 3450 | 4150     | mΩ   |

| $V_{SD}$               | Body diode forward voltage                           | I <sub>OUTx</sub> = -1 A                                                                                                    |     | 0.9  |          | V    |

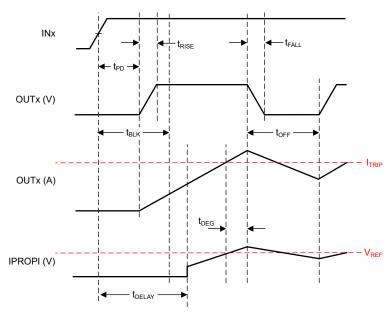

| t <sub>RISE</sub>      | Output rise time                                     | V <sub>OUTx</sub> rising from 10% to 90% of V <sub>VM</sub>                                                                 |     | 100  |          | ns   |

| t <sub>FALL</sub>      | Output fall time                                     | V <sub>OUTx</sub> falling from 90% to 10% of V <sub>VM</sub>                                                                |     | 50   |          | ns   |

| t <sub>PD</sub>        | Input to output propagation delay                    | Input to OUTx                                                                                                               |     | 650  |          | ns   |

| t <sub>DEAD</sub>      | Output dead time                                     |                                                                                                                             |     | 500  |          | ns   |

|                        | SENSE AND REGULATION (IPROPI, VRE                    | F)                                                                                                                          |     |      |          |      |

| V <sub>REF_INT</sub>   | Internal reference voltage                           | INT_VREF = 1b                                                                                                               | 480 | 500  | 520      | mV   |

| A <sub>IPROPI_H</sub>  | Current scaling factor                               | CS_GAIN_SEL = 000b, 350 mA to 2A                                                                                            |     | 244  |          | μΑ/Α |

| A <sub>IPROPI_M</sub>  | Current scaling factor                               | CS_GAIN_SEL = 010b, 60 mA to 350 mA                                                                                         |     | 1156 |          | μA/A |

| A <sub>IPROPI_L</sub>  | Current scaling factor                               | CS_GAIN_SEL = 110b, 10 mA to 60 mA                                                                                          |     | 5320 |          | μA/A |

| A <sub>ERR_H</sub>     | Current mirror total error, CS_GAIN_SEL              | $I_{OUT} = 1 \text{ A, } V_{IPROPI} \le \min(VM-1.25 \text{ V, } 3.3 \text{ V}), 3.3 \text{ V} \le V_{VM} \le 11 \text{ V}$ | -5  |      | 5        | %    |

| · EKK_H                | = 000b                                               | $I_{OUT}$ = 1 A, $V_{IPROPI} \le min(VM-1.25 \text{ V}, 3.3 \text{ V})$ , 1.65 V $\le V_{VM} \le 3.3 \text{ V}$             | -5  |      | 5        | %    |

| Δερρ                   | Current mirror total error, CS_GAIN_SEL              | $I_{OUT}$ = 250 mA, $V_{IPROPI} \le min(VM-1.25 \text{ V}, 3.3 \text{ V})$ , 3.3 V $\le V_{VM} \le 11 \text{ V}$            | -5  |      | 5        | %    |

| A <sub>ERR_M</sub>     | = 010b                                               | $I_{OUT}$ = 250 mA, $V_{IPROPI} \le min(VM-1.25 \text{ V}, 3.3 \text{ V})$ , 1.65 V $\le V_{VM} \le 3.3 \text{ V}$          | -5  |      | 5        | %    |

0 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V and 1.65 V  $\leq$  V<sub>VCC</sub>  $\leq$  11 V,  $-40^{\circ}$ C  $\leq$  T<sub>J</sub>  $\leq$  150 $^{\circ}$ C (unless otherwise noted). Typical values are at T<sub>J</sub> = 27 $^{\circ}$ C, V<sub>VM</sub> = 5 V, V<sub>VCC</sub> = 3.3 V.

| PARAMETER                                |                                                          | TEST CONDITIONS                                                                                                                                                               | MIN TYP MAX |     | MAX  | UNIT |

|------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|------|------|

| Current mirror total error CS GAIN SEL 3 |                                                          | $I_{OUT}$ = 50 mA, $V_{IPROPI} \le min(VM-1.25 V, 3.3 V), 3.3 V \le V_{VM} \le 11 V$                                                                                          | -6.5        |     | 6.5  | %    |

| A <sub>ERR_L</sub>                       | = 110b                                                   | I <sub>OUT</sub> = 50 mA, V <sub>IPROPI</sub> ≤ min(VM-1.25 V, 3.3 V), 1.65 V ≤ V <sub>VM</sub> ≤ 3.3 V                                                                       | -6.5        |     | 6.5  | %    |

| t <sub>OFF</sub>                         | Current regulation off time                              |                                                                                                                                                                               |             | 20  |      | μs   |

| t <sub>BLANK</sub>                       | Current sense blanking time                              | TBLANK = 0b                                                                                                                                                                   |             | 1.8 |      | μs   |

| t <sub>BLANK</sub>                       | Current sense blanking time                              | TBLANK = 1b                                                                                                                                                                   |             | 1   |      | μs   |

| t <sub>DEG</sub>                         | Current regulation and stall detection deglitch time     | TDEG = 0b                                                                                                                                                                     |             | 2   |      | μs   |

| t <sub>DEG</sub>                         | Current regulation and stall detection deglitch time     | TDEG = 1b                                                                                                                                                                     |             | 1   |      | μs   |

| t <sub>INRUSH</sub>                      | Inrush time blanking for stall detection                 |                                                                                                                                                                               | 5           |     | 6716 | ms   |

| Voltage reg                              | ulation                                                  |                                                                                                                                                                               |             |     |      |      |

| $\Delta V_{LINE}$                        | Line regulation                                          | $4 \text{ V} \le \text{V}_{\text{VM}} \le 11 \text{ V}, \text{ V}_{\text{VCC}} = 3.3 \text{ V}, \text{ V}_{\text{OUT}} = 3.3 \text{ V}, \text{ I}_{\text{OUT}} = 2 \text{ A}$ |             | ±1% |      |      |

| $\Delta V_{LOAD}$                        | Load regulation                                          | V <sub>VM</sub> = 5 V, V <sub>VCC</sub> = 3.3 V, V <sub>OUT</sub> = 3.3 V,<br>I <sub>OUT</sub> = 100 mA to 2 A                                                                |             | ±3% |      |      |

| PROTECTIO                                | ON CIRCUITS                                              |                                                                                                                                                                               |             |     |      |      |

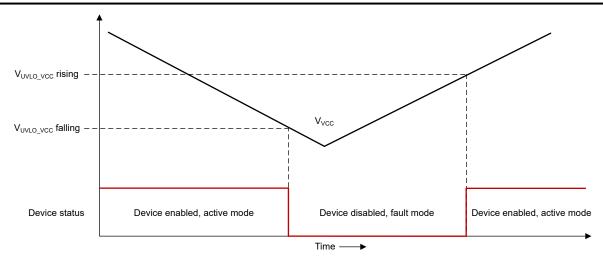

| V                                        | VCC supply undervoltage lockout                          | Supply rising                                                                                                                                                                 |             |     | 1.65 | V    |

| V <sub>UVLO_VCC</sub>                    | (UVLO)                                                   | Supply falling                                                                                                                                                                | 1.30        |     |      | V    |

| V <sub>UVLO_HYS</sub>                    | Supply UVLO hysteresis                                   | Rising to falling threshold                                                                                                                                                   |             | 120 |      | mV   |

| t <sub>UVLO</sub>                        | Supply undervoltage deglitch time                        | V <sub>VCC</sub> falling to OUTx disabled                                                                                                                                     |             | 10  |      | μs   |

| V <sub>OVP_TH</sub>                      | Overvoltage protection threshold                         | V <sub>OUT</sub> - V <sub>VM</sub>                                                                                                                                            |             | 200 |      | mV   |

| t <sub>OVP_ON</sub>                      | Overvoltage protection turn-on time                      |                                                                                                                                                                               |             | 13  |      | μs   |

| t <sub>OVP_OFF</sub>                     | Overvoltage protection turn-off time                     |                                                                                                                                                                               |             | 250 |      | μs   |

| I <sub>OCP</sub>                         | Overcurrent protection trip point,<br>CS_GAIN_SEL = 000b |                                                                                                                                                                               | 4           |     |      | Α    |

| I <sub>OCP</sub>                         | Overcurrent protection trip point,<br>CS_GAIN_SEL = 010b |                                                                                                                                                                               | 0.8         |     |      | Α    |

| I <sub>OCP</sub>                         | Overcurrent protection trip point,<br>CS_GAIN_SEL = 110b |                                                                                                                                                                               | 0.16        |     |      | Α    |

| t <sub>OCP</sub>                         | Overcurrent protection deglitch time                     |                                                                                                                                                                               |             | 2   |      | μs   |

| t <sub>RETRY</sub>                       | Retry time                                               |                                                                                                                                                                               |             | 1.7 |      | ms   |

| T <sub>TSD</sub>                         | Thermal shutdown temperature                             |                                                                                                                                                                               | 157         | 175 | 193  | °C   |

| T <sub>HYS</sub>                         | Thermal shutdown hysteresis                              |                                                                                                                                                                               |             | 18  |      | °C   |

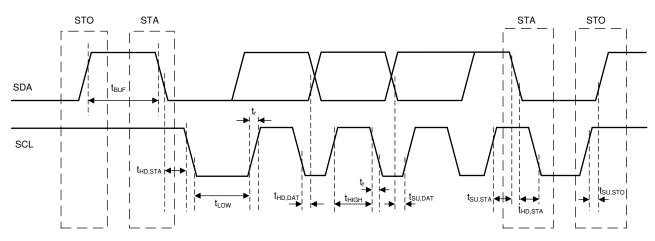

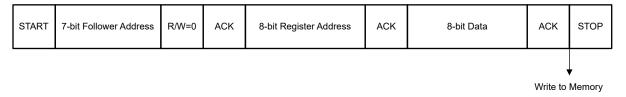

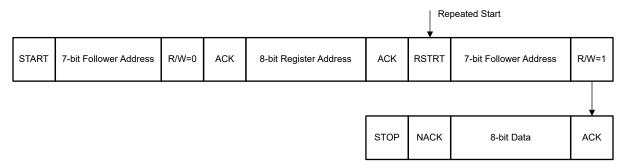

# 6.6 I2C Timing Requirements

|                     |                                                                                             | MIN   | NOM | MAX  | UNIT |

|---------------------|---------------------------------------------------------------------------------------------|-------|-----|------|------|

| STANDARD            | MODE                                                                                        |       |     |      |      |

| f <sub>SCL</sub>    | SCL Clock frequency                                                                         | 0     |     | 100  | kHz  |

| t <sub>HD,STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated | 4     |     |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                 | 4.7   |     |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                | 4     |     |      | μs   |

| t <sub>SU,STA</sub> | Setup time for a repeated START condition                                                   | 4.7   |     |      | μs   |

| t <sub>HD,DAT</sub> | Data hold time: For I2C bus devices                                                         | 0.035 |     | 3.45 | μs   |

| t <sub>SU,DAT</sub> | Data set-up time                                                                            | 250   |     |      | ns   |

Copyright © 2024 Texas Instruments Incorporated

8

Product Folder Links: DRV8215

|                     |                                                                                             | MIN   | NOM | MAX  | UNIT |

|---------------------|---------------------------------------------------------------------------------------------|-------|-----|------|------|

| t <sub>R</sub>      | SDA and SCL rise time                                                                       |       |     | 1000 | ns   |

| t <sub>F</sub>      | SDA and SCL fall time                                                                       |       |     | 300  | ns   |

| t <sub>SU,STO</sub> | Set-up time for STOP condition                                                              | 4     |     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                            | 4.7   |     |      | μs   |

| FAST MODE           |                                                                                             |       |     | 1    |      |

| f <sub>SCL</sub>    | SCL Clock frequency                                                                         | 0     |     | 400  | kHz  |

| t <sub>HD,STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated | 0.6   |     |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                 | 1.3   |     |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                | 0.6   |     |      | μs   |

| t <sub>SU,STA</sub> | Setup time for a repeated START condition                                                   | 0.6   |     |      | μs   |

| t <sub>HD,DAT</sub> | Data hold time: For I2C bus devices                                                         | 0.035 |     | 0.9  | μs   |

| t <sub>SU,DAT</sub> | Data set-up time                                                                            | 250   |     |      | ns   |

| t <sub>R</sub>      | SDA and SCL rise time                                                                       |       |     | 300  | ns   |

| t <sub>F</sub>      | SDA and SCL fall time                                                                       |       |     | 300  | ns   |

| t <sub>SU,STO</sub> | Set-up time for STOP condition                                                              | 0.6   |     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                            | 1.3   |     |      | μs   |

| t <sub>SP</sub>     | Pulse width of spikes to be supressed by input noise filter                                 |       | 50  |      | ns   |

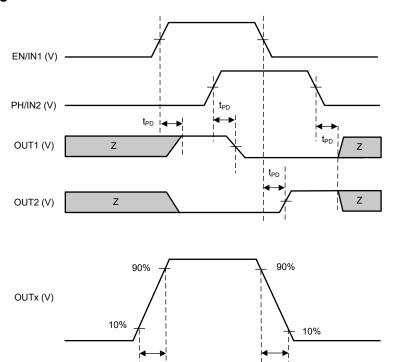

# **6.7 Timing Diagrams**

図 6-1. Input-to-Output Timing Diagram

図 6-2. I<sup>2</sup>C Timing Diagram

# 6.8 Typical Operating Characteristics

### 7 Detailed Description

#### 7.1 Overview

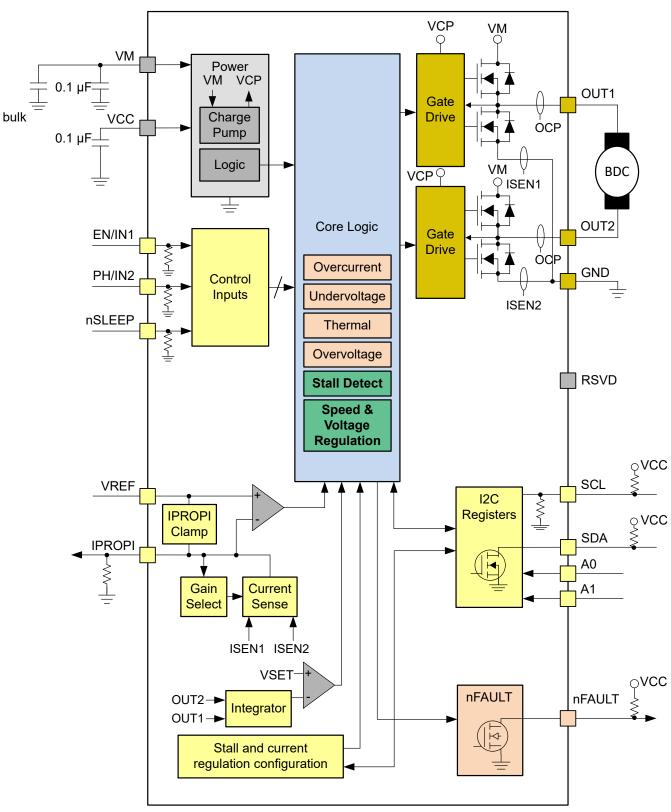

The DRV8215 is a high-performance integrated H-bridge motor driver with integrated speed and voltage regulation along with additional integrated features like stall detection, current sense output, current regulation, and protection circuitry.

The integrated speed regulation feature maintains maintains constant motor speed over varying battery voltages. The voltage regulation feature saves energy by driving the motor with a programmable lower terminal voltage. control in the device thereby reducing external components on a PCB and saving cost. The principle is based on counting the number of current ripples appearing in the motor current waveform due to commutations.

The DRV8215 contains PWM and PH/EN interfaces along with an I<sup>2</sup>C interface for configuration and detailed diagnostics. The EN/IN1 & PH/IN2 pins control the full bridge, which consists of four N-channel MOSFETs that have a typical  $R_{DS(ON)}$  of 240m $\Omega$  (including one high-side and one low-side FET). Motor speed can be controlled with pulse-width modulation (PWM), at frequencies between 0 to 200kHz. The PMODE bit in I<sup>2</sup>C registers allows to control the H-bridge solely through I<sup>2</sup>C commands, reducing the number of GPIO inputs.

The integrated current regulation feature limits motor current to a predefined maximum based on the VREF and IPROPI settings. The IPROPI signal can provide current feedback to a microcontroller during both the drive and brake/slow-decay states of the H-bridge. The gain select bits allow high accuracy current sensing down to 10 mA average motor current. The  $R_{\rm DS(ON)}$  of the low-side MOSFET and the overcurrent protection limit changes according to the gain select bits, thereby leading to optimized solutions for different values of motor current. The DRV8215 also has  $I^2$ C programmable registers to configure a hardware stall detection feature based on the IPROPI current sensing signal.

The integrated protection features protect the device in case of a system fault. These include undervoltage lockout (UVLO), overcurrent protection (OCP), and overtemperature shutdown (TSD). Fault conditions are indicated on the nFAULT pin. Additionally, the overvoltage protection (OVP) feature puts the driver into the brake state when the motor is spun manually while the device is in sleep mode or when the H-bridge is disabled. This prevents the back EMF induced high voltages on the supply rail that could potentially damage the driver and other circuits in the system.

To reduce area and external components on a printed circuit board, the device integrates a charge pump regulator and the corresponding capacitors. The separate full-bridge (VM) and logic (VCC) supplies allow the full-bridge supply voltage to drop to 0V without significant impact to  $R_{DS(ON)}$  and without triggering UVLO as long as the VCC supply is stable. The nSLEEP pin provides an ultra-low power mode to minimize current draw during system inactivity.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

#### 7.3.1 External Components

表 7-1 lists the recommended external components for the device.

表 7-1. Recommended External Components

| 3. Interest and a second compensate |                     |        |                                                                     |  |  |  |  |

|-------------------------------------|---------------------|--------|---------------------------------------------------------------------|--|--|--|--|

| COMPONENT                           | PIN 1               | PIN 2  | RECOMMENDED                                                         |  |  |  |  |

| C <sub>VM1</sub>                    | VM                  | GND    | 0.1-μF, low ESR ceramic capacitor, VM-rated.                        |  |  |  |  |

| C <sub>VM2</sub>                    | VM                  | GND    | Bulk Capacitance, VM-rated.                                         |  |  |  |  |

| C <sub>VCC</sub>                    | VCC                 | GND    | 0.1-μF, low ESR ceramic capacitor, VM-rated.                        |  |  |  |  |

| R <sub>IPROPI</sub>                 | IPROPI              | GND    | Resistor from IPROPI pin to GND, sets the current regulation level. |  |  |  |  |

| R <sub>nFAULT</sub>                 | VCC                 | nFAULT | 10 kΩ                                                               |  |  |  |  |

| R <sub>Pull-up</sub>                | SDA, SCL,<br>A0, A1 | VM     | 2.2 kΩ                                                              |  |  |  |  |

#### 7.3.2 Summary of Features

This section includes a summary of the key and advanced features of DRV8215.

- 1. DRV8215 Functional Block Diagram

- 2. Current Sense and Regulation (IPROPI)

- 3. Bridge Control

- 4. Protection

- 5. Advanced: Stall Detection

- 6. Advanced: Speed and Voltage Regulation

- 7. Advanced: Soft-Start and Soft-Stop using tinguish

# 7.3.3 Bridge Control

The DRV8215 output consists of four N-channel MOSFETs designed to drive high current. These outputs are controlled by the two inputs EN/IN1 and PH/IN2 or the I<sup>2</sup>C bits I2C\_EN\_IN1 and I2C\_PH\_IN2.

The I2C\_BC bit determines whether the bridge is controlled by the EN/IN1 and PH/IN2 pins or the I2C\_EN\_IN1 and I2C\_PH\_IN2 bits, as shown below.

表 7-2. H-Bridge Control Interface

| I2C_BC | Description                                                            |

|--------|------------------------------------------------------------------------|

| 0b     | Bridge control configured by using the EN/IN1 and PH/IN2 pins.         |

| 1b     | Bridge control configured by using the I2C_EN_IN1 and I2C_PH_IN2 bits. |

The control interface is selected by the PMODE bit. DRV8215 allows users to choose either Phase-Enable mode or PWM mode, as described below.

表 7-3. PMODE Functions

| PMODE | Control Mode |

|-------|--------------|

| 0b    | PH/EN        |

| 1b    | PWM          |

Product Folder Links: DRV8215

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

13

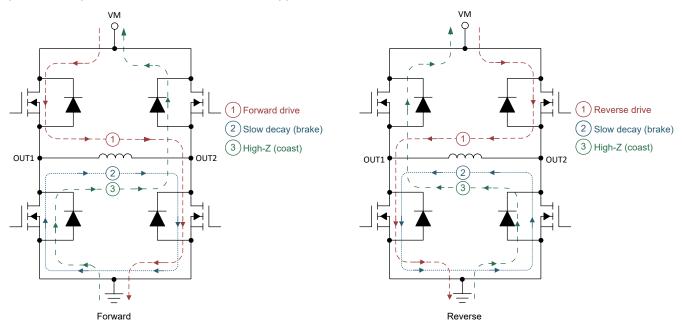

The inputs can be set to static voltages for 100% duty cycle drive, or they can be pulse-width modulated (PWM) for variable motor speed. Following diagram shows how the motor current flows through the H-bridge. The input pins can be powered before VM or VCC are applied.

図 7-1. H-Bridge Current Paths

The truth tables for each control mode are shown below. Note that these tables do not take into account the internal current regulation feature. Additionally, when an output changes from driving high to driving low (or driving low to driving high), dead time is automatically inserted to prevent shoot-through.

PH/EN mode allows for the H-bridge to be controlled with a speed and direction type of interface. The truth table for PH/EN mode is shown below.

| nSLEEP | Enable | Phase | OUT1   | OUT2   | Description                   |

|--------|--------|-------|--------|--------|-------------------------------|

| 0      | Х      | Х     | High-Z | High-Z | Sleep Mode (H-bridge High-Z)  |

| 1      | 1      | 0     | L      | Н      | Reverse (Current OUT2 → OUT1) |

| 1      | 1      | 1     | Н      | L      | Forward (Current OUT1 → OUT2) |

| 1      | 0      | Х     | L      | L      | Brake; low-side slow decay    |

表 7-4. PH/EN Control Mode (PMODE = 0b)

注

Enable refers to the EN pin when bridge control is external (I2C\_BC=0b), and the I2C\_EN\_IN1 bit when bridge control is internal (I2C\_BC=1b).

Phase refers to the PH pin when bridge control is external (I2C\_BC=0b), and the I2C\_PH\_IN2 bit when bridge control is internal (I2C\_BC=1b).

PWM mode allows for the H-bridge to enter the High-Z state while the device is awake. The truth table for PWM mode is shown below.

資料に関するフィードバック(ご意見やお問い合わせ) を送信

| 表 7-5. PW | M Control | Mode | (PMODE = | 1b) |

|-----------|-----------|------|----------|-----|

|-----------|-----------|------|----------|-----|

| nSLEEP | Input1 | Input2 | OUT1   | OUT2   | Description                   |

|--------|--------|--------|--------|--------|-------------------------------|

| 0      | Х      | Х      | High-Z | High-Z | Sleep Mode (H-bridge High-Z)  |

| 1      | 0      | 0      | High-Z | High-Z | Coast (H-bridge High-Z)       |

| 1      | 0      | 1      | L      | Н      | Reverse (Current OUT2 → OUT1) |

| 1      | 1      | 0      | Н      | L      | Forward (Current OUT1 → OUT2) |

| 1      | 1      | 1      | L      | L      | Brake; low-side slow decay    |

注

Input1 refers to the IN1 pin when bridge control is external (I2C\_BC=0b), and the I2C\_EN\_IN1 bit when bridge control is internal (I2C\_BC=1b).

Input2 refers to the IN2 pin when bridge control is external (I2C\_BC=0b), and the I2C\_PH\_IN2 bit when bridge control is internal (I2C\_BC=1b).

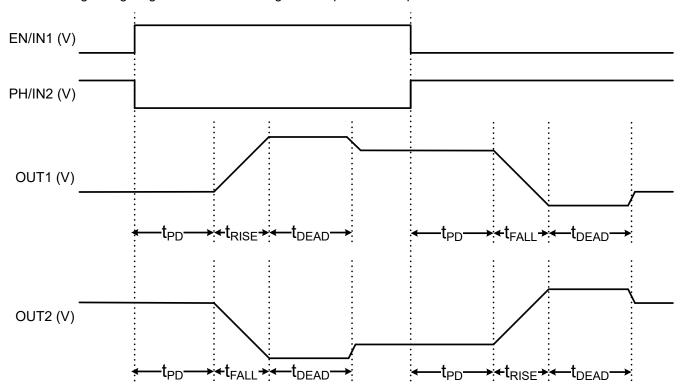

The following timing diagram shows the timing of the inputs and outputs of the motor driver.

図 7-2. H-Bridge Timing Diagram

The  $t_{DEAD}$  time is the time in the middle when the output is High-Z. The output pin voltage during  $t_{DEAD}$  depends on the direction of the output current. If the current is sourced from the pin, the voltage is a diode voltage drop below ground. If the current is sunk to pin, the voltage is a diode voltage drop above VM. This diode is the body diode of the high-side or low-side FET.

The propagation delay time  $(t_{PD})$  is measured as the time between an input edge to output change. This time accounts for input deglitch time and other internal logic propagation delays. The input deglitch time prevents noise on the input pins from affecting the output state. Additional output slew delay timing accounts for FET turn on or turn off times  $(t_{RISE})$  and  $t_{FALL}$ .

#### 7.3.4 Current Sense and Regulation (IPROPI)

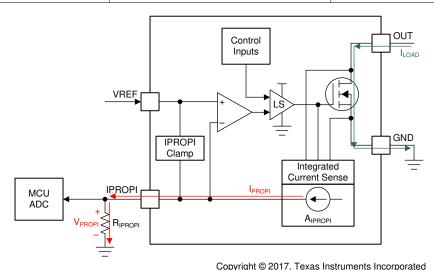

The DRV8215 integrates current sensing, regulation, and current sense feedback. The internal current mirror allows the device to sense the output current without an external sense resistor or sense circuitry, thereby reducing system size, cost, and complexity. The current regulation feature allows for the device to limit the output current in case of motor stall or high load torque events. The IPROPI output provides a current output proportional to the load current. This I<sub>IPROPI</sub> current can be converted to a V<sub>IPROPI</sub> output voltage by connecting a suitable resistor R<sub>IPROPI</sub> from this pin to the circuit ground. The following diagram shows the IPROPI timings specified in the Electrical Characteristics table.

☑ 7-3. Detailed IPROPI Timing Diagram

#### 7.3.4.1 Current Sensing and Current Mirror Gain Selection

The IPROPI pin outputs an analog current proportional to the current flowing through the low-side power MOSFETs in the H-bridge and scaled by the current mirror gain ( $A_{IPROPI}$ ). The IPROPI output current can be calculated by the following equation. The  $I_{LSx}$  in the equation is only valid when the current flows from drain to source in the low-side MOSFET. If current flows from source to drain or through the body diode, the value of  $I_{LSx}$  for that channel is zero. For instance, if the bridge is in the brake, slow-decay state, then the current out of IPROPI is only proportional to the current in one of the low-side MOSFETs.

$$I_{PROPI}(\mu A) = (I_{LS1} + I_{LS2})(A) \times A_{IPROPI}(\mu A/A)$$

(1)

The  $A_{ERR}$  parameter in the Electrical Characteristics table is the error associated with the  $A_{IPROPI}$  gain. It indicates the combined effect of offset error added to the  $I_{OUT}$  current and gain error.

The current mirror gain AIPROPI depends on the CS\_GAIN\_SEL bit setting, as shown in the table below -

表 7-6. Recommended settings for CS\_GAIN\_SEL

| CS_GAIN_SEL | A <sub>IPROPI</sub> | Recommended Current<br>Range | Low-side FET R <sub>DS(ON)</sub> | Minimum OCP Limit |

|-------------|---------------------|------------------------------|----------------------------------|-------------------|

| 000b        | 244 µA/A            | 350 mA to 2A                 | 120 mΩ                           | 4 A               |

| 010b        | 1156 μA/A           | 60 mA to 350 mA              | 440 mΩ                           | 800 mA            |

| 110b        | 5320 μA/A           | 10 mA to 60 mA               | 2040 mΩ                          | 160 mA            |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

CS\_GAIN\_SEL bits therefore allows optimizing the design for various applications by reducing OCP limit and increasing current mirror gain at lower motor currents.

The motor current is measured by an internal current mirror architecture on the low-side FETs which removes the need for an external power sense resistor as shown below. The current mirror architecture senses motor winding current in both the drive and brake low-side slow-decay periods, therefore allowing continuous current monitoring in typical bidirectional brushed DC motor applications. In coast mode, the current is freewheeling and cannot be sensed because it flows from source to drain. However, the current can be sampled by briefly reenabling the driver in either drive or slow-decay modes and measuring the current before switching back to coast mode again.

表 7-7 lists the overall CS\_GAIN\_SEL settings with the maximum current values.

| 表 1-1. CS_GAIN_SEL Settings |                       |                     |  |  |  |

|-----------------------------|-----------------------|---------------------|--|--|--|

| Bit                         | Maximum Current Value | A <sub>IPROPI</sub> |  |  |  |

| 000b                        | 4 A                   | 244 μΑ/Α            |  |  |  |

| 001b                        | 2 A                   | 244 μΑ/Α            |  |  |  |

| 010b                        | 1 A                   | 1156 μA/A           |  |  |  |

| 011b                        | 0.5 A                 | 1156 μA/A           |  |  |  |

| 1X0b                        | 0.25 A                | 5320 μA/A           |  |  |  |

| 1X1b                        | 0.125 A               | 5320 μA/A           |  |  |  |

表 7-7. CS GAIN SEL Settings

図 7-4. Integrated Current Sensing

The IPROPI pin should be connected to an external resistor ( $R_{IPROPI}$ ) to ground in order to generate a proportional voltage ( $V_{IPROPI}$ ) on the IPROPI pin with the  $I_{IPROPI}$  analog current output. This allows for the load current to be measured as the voltage drop across the  $R_{IPROPI}$  resistor with a standard analog to digital converter (ADC). The  $R_{IPROPI}$  resistor can be sized based on the expected load current in the application so that the full range of the controller ADC is utilized.

Additionally, the DRV8215 implements an internal IPROPI voltage clamp circuit to limit  $V_{IPROPI}$  with respect to  $V_{VREF}$  on the VREF pin and protect the external ADC in case of output overcurrent or unexpected high current events. TI recommends designing for at least 1.25 V of headroom between  $V_{VM}$  and the maximum  $V_{IPROPI}$  voltage to be measured by the ADC,  $V_{IPROPI\_MAX}$ . This ensures good accuracy across the range of VIPROPI voltages measured by the ADC. For instance, if  $V_{VM}$  is 4.55 V to 11 V,  $V_{IPROPI\_MAX}$  can be as high as 3.3 V. However, if  $V_{VM}$  is 3.3 V, then VIPROPI will have good accuracy up to 2.05 V.

The corresponding IPROPI voltage to the output current can be calculated as shown below -

$$V_{IPROPI}(V) = I_{PROPI}(A) \times R_{IPROPI}(\Omega)$$

(2)

The IPROPI output bandwidth is limited by the sense delay time (t<sub>DELAY</sub>) of the internal current sensing circuit. This time is the delay from the low-side MOSFET enable command (from the INx pins) to the IPROPI output being ready.

If the device is alternating between drive and slow-decay (brake) in an H-bridge PWM pattern then the low-side MOSFET sensing the current is continuously on and the sense delay time has no impact to the IPROPI output. If a command on the INx pins disables the low-side MOSFETs (according to the truth tables), the IPROPI output will disable with the input logic signal. Although the low-side MOSFETs may still conduct current as they disable according to the device slew rate (specified in the Electrical Characteristics table by t<sub>RISE</sub> time), IPROPI will not represent the current in the low-side MOSFETs during this turnoff time.

#### 7.3.4.2 Current Regulation

The DRV8215 integrates current regulation using either a fixed off-time or a cycle-by-cycle PWM current regulation scheme. This allows the device to limit the output current in case of a motor stall, high torque, or other high current load events autonomously. The current regulation scheme is selectable by the REG\_CTRL bit in  $I^2C$ .

The internal current regulation can be disabled by tying IPROPI to GND and setting the VREF pin voltage greater than GND if current feedback is not required. Additionally, current regulation can also be disabled by setting IMODE to 00b as explained below. If current feedback is required and current regulation is not required, set  $V_{VREF}$  and  $R_{IPROPI}$  such that  $V_{IPROPI}$  never reaches the  $V_{VREF}$  threshold. For proper operation of the current regulation circuit,  $V_{VREF}$  must be within the range of the VREF pin voltage specified in the Recommended Operating Conditions table.

表 7-8. REG\_CTRL Functions

| Bit* | Current Regulation Mode |

|------|-------------------------|

| 00b  | Fixed Off-Time          |

| 01b  | Cycle-By-Cycle          |

注

The current regulation threshold ( $I_{TRIP}$ ) is set through a combination of the VREF voltage ( $V_{VREF}$ ) and IPROPI output resistor ( $R_{IPROPI}$ ). This is done by comparing the voltage drop across the external  $R_{IPROPI}$  resistor to  $V_{VREF}$  with an internal comparator.

$$I_{TRIP}(A) \times A_{IPROPI}(\mu A/A) = V_{VREF}(V) / R_{IPROPI}(\Omega)$$

(3)

For example, if  $V_{VREF}$  = 3.3 V,  $R_{IPROPI}$  = 7500  $\Omega$  and  $A_{IPROPI}$  = 225  $\mu$ A/A, then  $I_{TRIP}$  will be approximately 1.96 A.

$V_{VREF}$  must be lower than  $V_{VM}$  by at least 1.25 V. The maximum recommended value of  $V_{VREF}$  is 3.3 V. If INT\_VREF bit is set to 1b,  $V_{VREF}$  is internally selected with a fixed value of 500 mV.

The  $I_{TRIP}$  comparator has both a blanking time ( $t_{BLANK}$ ) and a deglitch time ( $t_{DEG}$ ). The internal blanking time helps to prevent voltage and current transients during output switching from affecting the current regulation. These transients may be caused by a capacitor inside the motor or motor terminals. The internal deglitch time ensures that transient conditions do not prematurely trigger the current regulation. In certain cases where the transient conditions are longer than the deglitch time, placing a 10-nF capacitor on the IPROPI pin, close to the device, helps filter the transients on IPROPI output so current regulation does not prematurely trigger. The capacitor value can be modified as needed, however large capacitor values may slow down the response time of the current regulation circuit.

<sup>\*</sup>Additional REG\_CTRL options 10b and 11b allow selection between motor voltage or speed regulation described in セクション 7.3.6.2.1.

The IMODE bits determine the behavior of current regulation for the motor driver.

- When IMODE is 00b, current regulation is disabled.

- When IMODE is 01b, the device performs current regulation only during the t<sub>INRUSH</sub> time when stall detection is enabled.

- When IMODE is 10b, current regulation is enabled at all times.

The following table summarizes the IMODE bit settings.

| 表 7-9. IMODE configurati | on |

|--------------------------|----|

|--------------------------|----|

| IMODE | EN_STALL | Description                                        |

|-------|----------|----------------------------------------------------|

| 00b   | X        | No current regulation at any time                  |

| 01b   | 0b       | Current regulation at all times                    |

| Olb   | 1b       | Current regulation during t <sub>INRUSH</sub> only |

| 1Xb   | Х        | Current regulation at all times                    |

#### 7.3.4.2.1 Fixed Off-Time Current Regulation

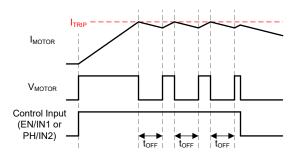

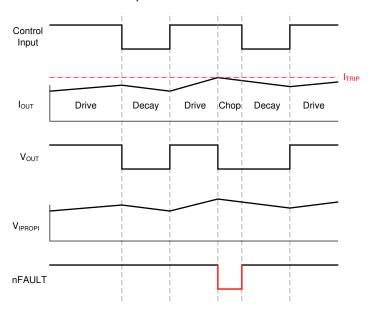

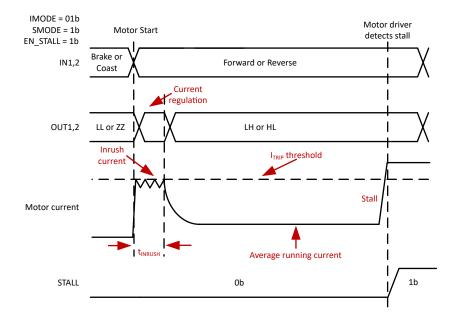

図 7-5. Fixed Off-Time Current Regulation

In the fixed off-time mode, the H-bridge enters a brake/low-side slow decay state (both low-side MOSFETs ON) for  $t_{OFF}$  duration after  $l_{OUT}$  exceeds  $l_{TRIP}$ . After  $t_{OFF}$  the outputs are re-enabled according to the control inputs unless  $l_{OUT}$  is still greater than  $l_{TRIP}$ . If  $l_{OUT}$  is still greater than  $l_{TRIP}$ , the H-bridge will enter another period of brake/low-side slow decay for  $t_{OFF}$ . If the state of the EN/IN1 or PH/IN2 control pin inputs or I2C\_EN\_IN1 or I2C\_PH\_IN2 bits changes during the  $t_{OFF}$  time, the remainder of the  $t_{OFF}$  time is ignored, and the outputs will again follow the inputs.

The fixed off-time mode allows for a simple current regulation scheme independent of the external controller. Fixed off-time mode will support 100% duty cycle current regulation since the H-bridge automatically enables after the  $t_{\text{OFF}}$  period and does not require a new control input edge on the control input pins or bits to reset the outputs.

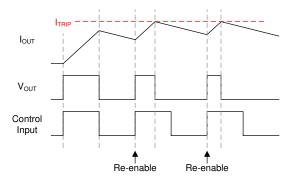

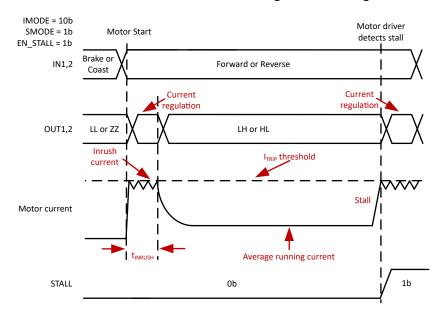

#### 7.3.4.2.2 Cycle-By-Cycle Current Regulation

In cycle-by-cycle mode, the H-bridge enters a brake, low-side slow decay state (both low-side MOSFETs ON) after  $I_{OUT}$  exceeds  $I_{TRIP}$  until the next control input edge on either the EN/IN1 or PH/IN2 pins or 0 to 1 transitions on the I2C\_EN\_IN1 or I2C\_PH\_IN2 bits. This allows for additional control of the current regulation by the external controller. This is shown in the diagram below. Cycle-by-cycle mode will not support 100% duty cycle current regulation as a new control input edge is required to reset the outputs after the brake, low-side slow decay state has been entered.

Product Folder Links: DRV8215

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

19

図 7-6. Cycle-By-Cycle Current Regulation

In cycle-by-cycle mode, the device can indicate whenever the H-bridge enters internal current regulation by pulling the nFAULT pin low. This can be used to determine when the device outputs will differ from the control inputs or the load has reached the I<sub>TRIP</sub> threshold. This behavior is controlled by the CBC\_REP bit. This is shown in the following diagram. In cycle-by-cycle mode, if the CBC\_REP bit is 1b, nFAULT will be pulled low when the H-bridge enters internal current regulation and nFAULT will be released whenever the next control input edge is received by the device and the outputs are reset.

図 7-7. Cycle-By-Cycle Current Regulation, CBC\_REP = 1b

No device functionality is affected when the nFAULT pin is pulled low for the current regulation indicator. The nFAULT pin is only used as an indicator and the device will continue normal operation. To distinguish a device fault from the current regulation indicator, the nFAULT pin can be compared with the control inputs. The current regulation indicator can only assert when the control inputs are commanding a forward or reverse drive state. If the nFAULT pin is pulled low and the control inputs are commanding the high-Z or slow-decay states, then a device fault has occurred.

#### 7.3.5 Stall Detection

The DRV8215 integrates a stall detection feature. The principle of the stall detection scheme relies on the fact that motor current increases during stall conditions. The DRV8215 compares the voltage on the IPROPI pin to the voltage on the VREF pin or 500 mV to determine whether a motor stall condition has occurred. The setting is deterimed by the INT\_VREF register.  $\gtrsim$  7-10 shows the configurable options for INT\_VREF. The following paragraphs describe how to configure the I $^2$ C registers for the desired stall detection response.

表 7-10. Settings for INT\_VREF

| Bit | Description                                  |

|-----|----------------------------------------------|

| 0b  | V <sub>VREF</sub> not fixed                  |

| 1b  | V <sub>VREF</sub> fixed internally at 500 mV |

The STALL bit in status register changes to 1b when a motor stall is detected. The EN\_STALL bit is used to enable or disable stall detection. The following table summarizes the EN\_STALL bit settings.

21

#### 表 7-11. EN STALL configuration

| EN_STALL | Description                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------|

| UD I.    | Stall detection disabled. If IMODE = 01b, current regulation occurs at all times when $V_{IPROPI} \ge V_{VREF}$ . |

| 1b       | Stall detection enabled.                                                                                          |

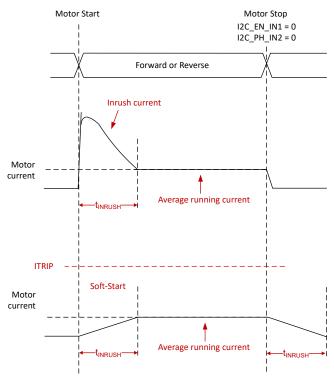

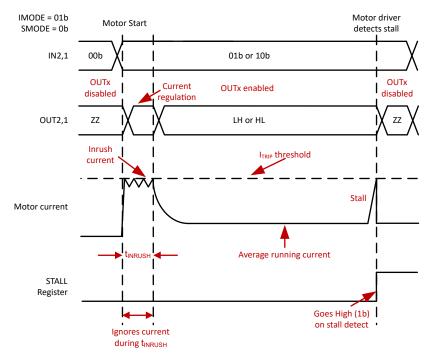

The IPROPI pin provides the current sense signal to the stall detection module. The VREF pin sets the  $I_{TRIP}$  current level at which a stall condition is detected. As shown in  $\frac{1}{8}$  7-10,  $V_{VREF}$  is internally fixed at 500mV when INT\_VREF = 1b. When  $V_{IPROPI} \ge V_{VREF}$ , it implies  $I_{OUT} \ge I_{TRIP}$ . The device detects a stall condition here. Stall detection is blanked for a period of time,  $t_{INRUSH}$ , to avoid false detection due to high inrush currents during motor startup. The IPROPI and VREF pins also support current regulation, as described earlier.

The TINRUSH[15:0] bits set the period of time the stall detection logic will ignore the inrush current during motor startup ( $t_{INRUSH}$ ). After  $t_{INRUSH}$  time expires, the DRV8215 indicates a stall condition the next instant  $V_{IPROPI}$  is greater than or equal to  $V_{VREF}$ .

When voltage or speed soft-start is disabled, the t<sub>INRUSH</sub> time directly reflects the setting of the TINRUSH bits. The t<sub>INRUSH</sub> can be set to a value between 5ms (corresponding to 0000h) and 6.7s (corresponding to FFFFh), with a default value of 1s. Each increment of LSB corresponds to 102.4µs of the inrush time.

When voltage or speed soft-start is enabled, target motor voltage or speed is soft-started and soft-stopped for the duration of  $t_{\text{INRUSH}}$  time. The TINRUSH bits should be setup such that the  $t_{\text{INRUSH}}$  = TINRUSH bit setting x WSET\_VSET. For example, if WSET\_VSET = 10 and intended inrush time is 1s, then TINRUSH bit setting should correspond to 100ms.

The following conditions cause the stall detection scheme to ignore the inrush current for  $t_{\mathsf{INRUSH}}$  time -

- Power-up of the DRV8215

- · Recovering from faults

- After device exits from sleep mode

- After recovering from stall, as explained in 表 7-12

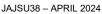

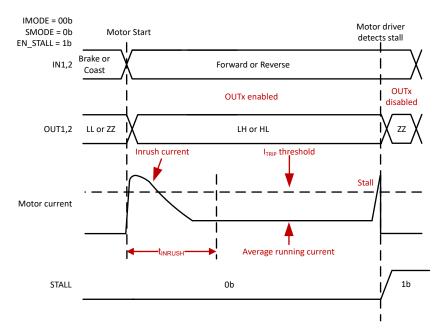

The SMODE bit programs the device's response to a stall condition. When SMODE = 0b, the outputs disable, and the STALL bit becomes 1b. When SMODE = 1b, the STALL bit becomes 1b, but the outputs continue to drive current into the motor. 表 7-12 summarizes the SMODE bit settings.

表 7-12. SMODE configuration

| SMODE | Description                                                                          | Recovery from Stall Condition                                                                                                                                                                                                                                                                                                                                                              |

|-------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0b    | Latched disable with indication: the OUTx pins disable and the STALL bit becomes 1b. | A clear fault must be issued by writing 1b to the CLR_FLT bit. STALL bit changes to 0b after a clear fault is issued. After waking up from stall, the stall detection scheme ignores the inrush current for $t_{\text{INRUSH}}$ time as described earlier. After $t_{\text{INRUSH}}$ time, if motor current is still higher than $t_{\text{ITRIP}}$ , a stall condition is detected again. |

| 1b    | Indication only: the OUTx pins remain active and the STALL bit becomes 1b.           | A clear fault must be issued by writing 1b to the CLR_FLT bit to make STALL bit 0b. After $t_{\text{INRUSH}}$ time, if motor current is still higher than $I_{\text{TRIP}}$ , a stall condition is detected again.                                                                                                                                                                         |

The **IMODE** bits determine the behavior of current regulation in the motor driver. 表 7-9 summarizes the IMODE pin settings. For more details on current regulation, see セクション 7.3.4.2.

The STALL\_REP bit determines whether stall is reported on nFAULT pin. When STALL\_REP bit is 1b, nFAULT is pulled low whenever stall is detected and STALL bit is 1b. If STALL\_REP bit is 0b, stall is not reported on nFAULT output.

The following diagrams show example timing diagrams for different configurations of the hardware stall detection feature.

図 7-8. Stall Detection with Latched Disable

図 7-9. Stall Detection with STALL indication only

23

図 7-10. Stall Detection with current regulation during inrush

図 7-11. Stall Detection with current regulation

### 7.3.6 Motor Voltage and Speed Regulation

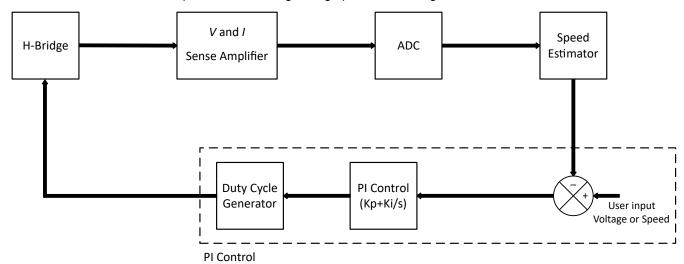

The DRV8215 provides the ability to regulate the voltage applied to the motor winding or to regulate the speed of the motor. This feature allows constant motor speed to be maintained even when operating from a varying supply voltage such as a discharging battery. The DRV8215 uses a pulse-width modulation (PWM) technique instead of a linear circuit to minimize current consumption and maximize battery life.

The intended voltage or speed can be programmed by the WSET\_VSET bits. Refer to セクション 7.3.6.2.1 for further explanation.

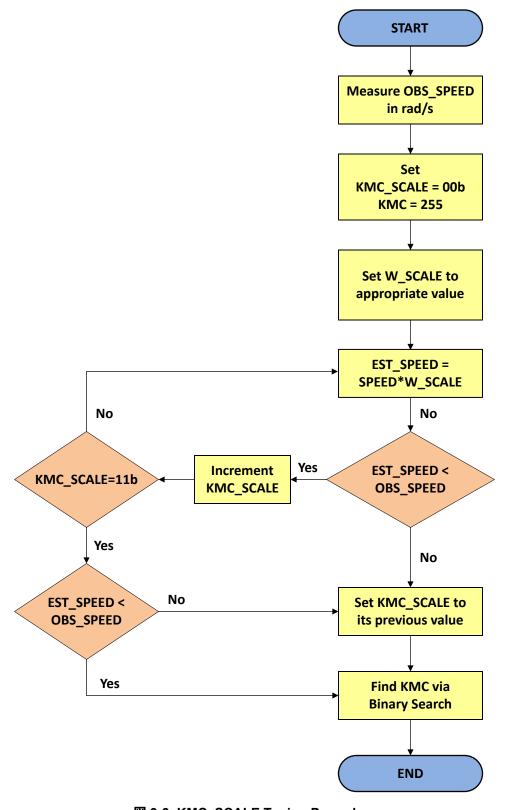

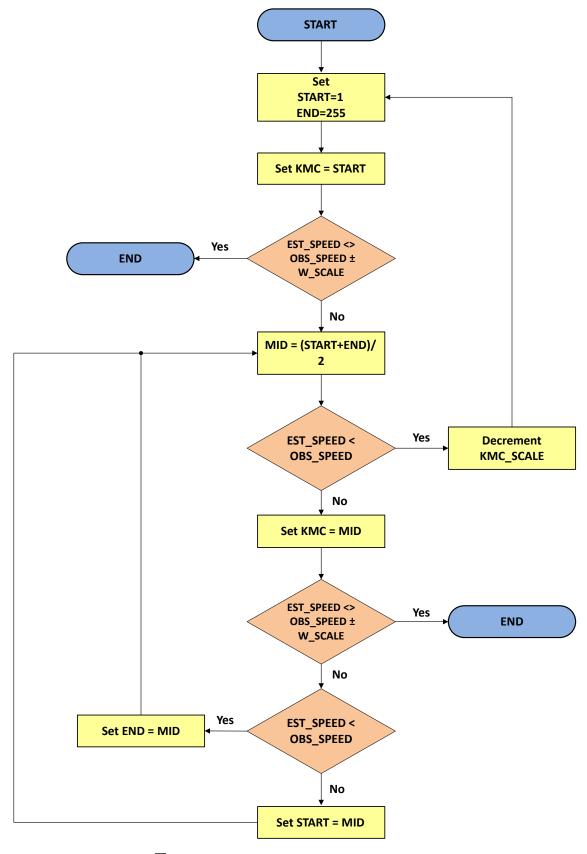

Four ranges of motor speed can be selected using the W\_SCALE bits to support low, moderate and high speed applications. The speed regulation loop compares the motor speed estimated by the speed estimator with the

Product Folder Links: DRV8215

資料に関するフィードバック(ご意見やお問い合わせ) を送信

user definded target speed. The following section describes the internal bridge control logic taking voltage regulation as an example, but is also applicable for speed regulation.

☑ 7-12 shows the closed loop PI control for regulating speed and voltage.

図 7-12. Speed and Voltage Regulation with PI Control

注