DRV8424, DRV8425 JAJSKI6C - MAY 2020 - REVISED JULY 2022

# DRV8424/25 ステッピング・ドライバ、電流センス機能内蔵、1/256 マイクロ ステッピング、STEP/DIR インターフェイス、スマート・チューン・テクノ ロジ搭載

# 1 特長

- PWM マイクロステッピングのステッパ・モータ・ドライバ

- シンプルな STEP/DIR インターフェイス

- 最高 1/256 のマイクロステッピング・インデクサ

- 電流検出機能内蔵

- 検出抵抗が不要

- ±5% のフルスケール電流精度

- スマート・チューン・ディケイ・テクノロジ、固定スロー・デ ィケイおよびミックス・ディケイ・オプション

- 4.5~33Vの動作電源電圧範囲

- 低い R<sub>DS(ON)</sub>:

- DRV8424:24V、25℃ で 330mΩ HS + LS

- DRV8425:24V、25℃ で 550mΩ HS + LS

- ブリッジごとの大電流能力

- DRV8424:4A ピーク、2.5A フルスケール、1.8A

- DRV8425:3.2A ピーク、2A フルスケール、1.4A **RMS**

- 以下とピン互換:

- DRV8426:33V, 900m $\Omega$  HS + LS

- DRV8436:48V, 900mΩ HS + LS

- DRV8434:48V $_{330}$ mΩ HS + LS

- オフ時間 PWM チョッピングを構成可能

- 7μs、16μs、24μs、32μs。

- 1.8V、3.3V、5.0V のロジック入力をサポート

- 低消費電流のスリープ・モード (2µA)

- 拡散スペクトラム・クロックによる低い電磁気妨害 (EMI)

- 小さなパッケージと占有面積

- 保護機能

- VM 低電圧誤動作防止 (UVLO)

- チャージ・ポンプ低電圧検出 (CPUV)

- 過電流保護 (OCP)

- サーマル・シャットダウン (OTSD)

- フォルト条件出力 (nFAULT)

# 2 アプリケーション

- プリンタとスキャナ

- ATM と貨幣処理機

- 工業用ミシン

- ステージ照明機器

- オフィスおよびホーム・オートメーション

- ファクトリ・オートメーションおよびロボティクス

- 医療用アプリケーション

- 3D プリンタ

# 3 概要

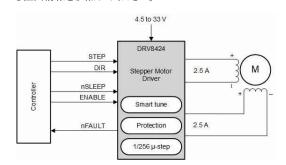

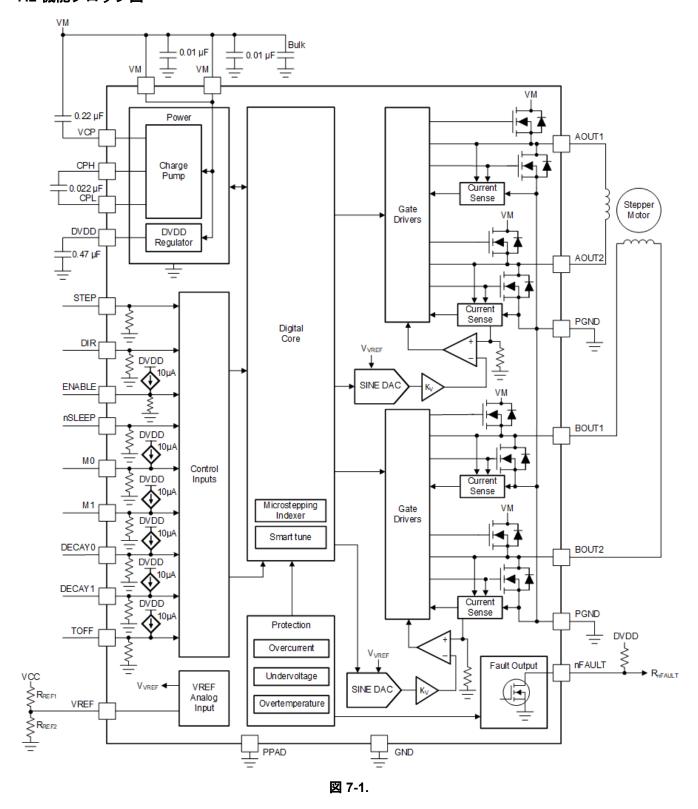

DRV8424/25 は、産業用および民生用アプリケーション 向けのステッピング・モータ・ドライバです。このデバイスに は、2 つの N チャネル・パワー MOSFET H ブリッジ・ドラ イバ、マイクロステッピング・インデクサ、および電流検出機 能が完全に統合されています。DRV8424 は最大 2.5A のフルスケール出力電流を駆動でき、DRV8425 は最大 2A のフルスケール出力電流を駆動できます (PCB 設計 に依存)。

DRV8424/25 は、2 つの外部電力検出抵抗が不要な内 部電流検出アーキテクチャを採用しているため、PCB 面 積とシステム・コストを低減できます。 本デバイスは、スマー ト・チューン、スロー、ミックスのディケイ・オプションを選択 できる内部 PWM 電流レギュレーション方式を採用してい ます。スマート・チューンは、最適な電流レギュレーション を自動的に調整し、モータの変動と経年変化を補償し、モ ータからの可聴ノイズを低減します。

シンプルな STEP/DIR インターフェイスにより、外部コント ローラからステッピング・モータの方向とステップ速度を制 御できます。 デバイスは、フルステップから 1/256 マイクロ ステッピングまでのモードに構成可能です。専用の nSLEEP ピンを使用して、低消費電力のスリープ・モード を実現します。電源の低電圧、チャージ・ポンプ障害、過 電流、短絡、過熱に対する保護機能が備わっています。フ ォルト条件は、nFAULT ピンで通知されます。

#### 製品情報(1)

| 部品番号        | パッケージ       | 本体サイズ (公称)    |

|-------------|-------------|---------------|

| DRV8424PWPR | HTSSOP (28) | 9.7mm × 4.4mm |

| DRV8424RGER | VQFN (24)   | 4.0mm × 4.0mm |

| DRV8425PWPR | HTSSOP (28) | 9.7mm × 4.4mm |

| DRV8425RGER | VQFN (24)   | 4.0mm × 4.0mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

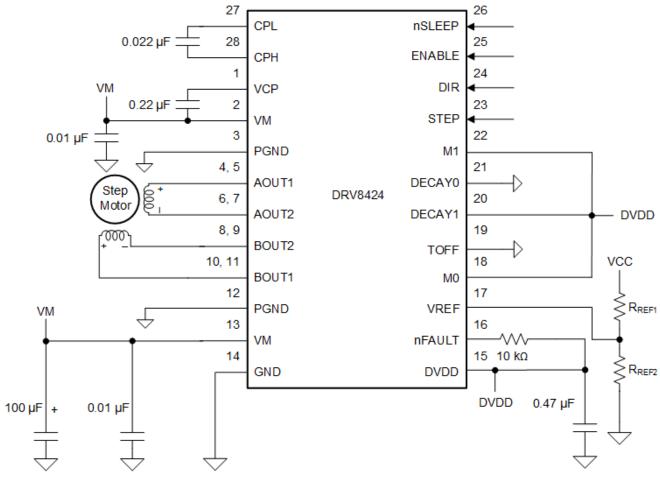

概略回路図

# 目次

| 7.4 デバイスの機能モード         |               |

|------------------------|---------------|

| 8 アプリケーションと実装          | 36            |

| 8.1 アプリケーション情報         | 36            |

| 8.2 代表的なアプリケーション       | 36            |

|                        |               |

| 9.1 バルク・コンデンサ          |               |

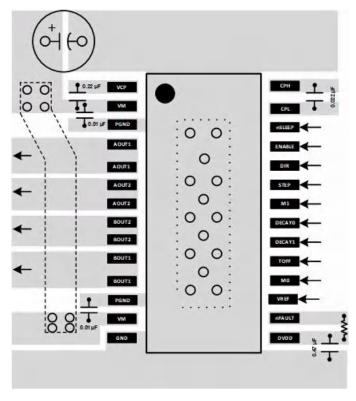

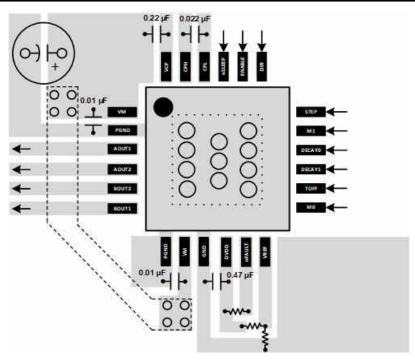

| 10 レイアウト               | 43            |

| 10.1 レイアウトのガイドライン      | 43            |

| 10.2 レイアウト例            | 43            |

| 11 デバイスおよびドキュメントのサポート  | 45            |

| 11.1 関連リンク             | 45            |

| 11.2ドキュメントの更新通知を受け取る方法 | 45            |

| 11.3 コミュニティ・リソース       | 45            |

| 11.4 商標                | 45            |

| 11.5 静電気放電に関する注意事項     | 45            |

| 12 メカニカル、パッケージ、および注文情報 | 46            |

|                        |               |

|                        | 8 アプリケーションと実装 |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# デバイス比較表

| 型番      | $R_{DS(ON)}$ (HS + LS) (m $\Omega$ ) | ブリッジあたりのフルスケール電流 (A) |

|---------|--------------------------------------|----------------------|

| DRV8424 | 330                                  | 2.5                  |

| DRV8425 | 550                                  | 2                    |

# 5 ピン構成および機能

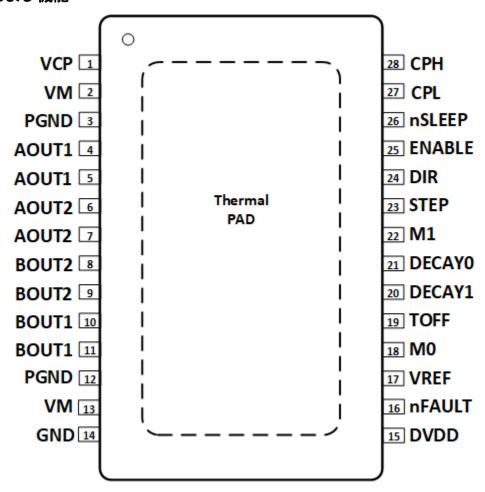

図 5-1. PWP PowerPAD™ パッケージ 28 ピン HTSSOP 上面図

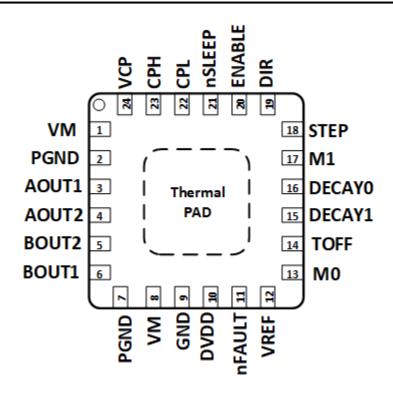

図 5-2. RGE パッケージ 24 ピン VQFN (露出サーマル・パッド付き) 上面図

表 5-1. ピン機能

|        |        |      |   | 衣 つー1.                                               | こノ懐肥                                                                                  |

|--------|--------|------|---|------------------------------------------------------|---------------------------------------------------------------------------------------|

|        | ピン     |      |   |                                                      |                                                                                       |

| かが     | 番号     | 番号   |   | 種類                                                   | 説明                                                                                    |

| 名称     | HTSSOP | VQFN |   |                                                      |                                                                                       |

| AOUT1  | 4、5    | 3    | 0 | 出力                                                   | 巻線 A 出力。ステッピング・モータの巻線に接続します。                                                          |

| AOUT2  | 6、7    | 4    | 0 | 出力                                                   | 巻線 A 出力。ステッピング・モータの巻線に接続します。                                                          |

| PGND   | 3、12   | 2、7  | _ | 電源                                                   | 電源グランド。システム・グランドに接続します。                                                               |

| BOUT2  | 8,9    | 5    | 0 | 出力                                                   | 巻線 B 出力。ステッピング・モータの巻線に接続します。                                                          |

| BOUT1  | 10、11  | 6    | 0 | 出力                                                   | 巻線 B 出力。ステッピング・モータの巻線に接続します。                                                          |

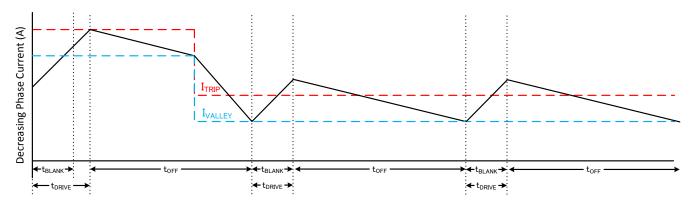

| СРН    | 28     | 23   |   | 電源                                                   | チャージ・ポンプのスイッチング・ノード。 X7R、0.022μF、VM 定格セラミッ                                            |

| CPL    | 27     | 22   |   | 电你                                                   | ク・コンデンサを CPH と CPL の間に接続します。                                                          |

| DIR    | 24     | 19   | ı | 入力                                                   | 方向入力。ロジック・レベルによりステッピング方向を設定します。内部プルダウン抵抗。                                             |

| ENABLE | 25     | 20   | I | 入力                                                   | 論理 Low でデバイスの出力をディセーブル。 論理 High でイネーブル。<br>DVDD への内部プルアップ。 OCP および OTSD 応答のタイプも決定します。 |

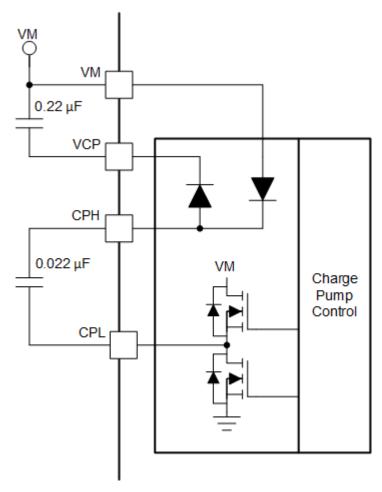

| DVDD   | 15     | 10   | 0 | 電源                                                   | ロジック電源電圧。X7R、0.47μF~1μF、6.3V または 10V 定格セラミック・コンデンサを GND との間に接続します。                    |

| GND    | 14     | 9    | _ | 電源                                                   | デバイスのグランド。システム・グランドに接続します。                                                            |

| VREF   | 17     | 12   | I | 入力                                                   | 電流設定リファレンス入力。DRV8424 の場合は最大値 3.3V、DRV8425 の場合は 2.64V。DVDD と抵抗分割器を使用して VREF を供給できます。   |

| M0     | 18     | 13   |   | 7 +                                                  | マイクロステッピング・モード設定ピン。ステップ・モードを設定します。内                                                   |

| M1     | 22     | 17   |   | 入力                                                   | 部プルダウン抵抗。                                                                             |

| DECAY0 | 21     | 16   |   | 入力 ディケイ・モード設定ピン。ディケイ・モードを設定します (セクション 7.3 セクションを参照)。 |                                                                                       |

| DECAY1 | 20     | 15   | ' |                                                      |                                                                                       |

# 表 5-1. ピン機能 (continued)

|        | SCOTT CONTINUOU) |      |     |              |                                                                                                       |  |  |

|--------|------------------|------|-----|--------------|-------------------------------------------------------------------------------------------------------|--|--|

|        | ピン               |      |     |              |                                                                                                       |  |  |

| to the | 番号               |      | I/O | 種類           | 説明                                                                                                    |  |  |

| 名称     | HTSSOP           | VQFN |     |              |                                                                                                       |  |  |

| STEP   | 23               | 18   | I   | 入力           | ステップ入力。立ち上がりエッジでインデクサが 1 ステップ進みます。内部プルダウン抵抗。                                                          |  |  |

| VCP    | 1                | 24   | _   | 電源           | チャージ・ポンプの出力。X7R、0.22μF、16V セラミック・コンデンサを<br>VM との間に接続します。                                              |  |  |

| VM     | 2、13             | 1,8  | _   | 電源           | 電源。モータ電源電圧に接続し、VM 定格の 2 つの 0.01µF セラミック・コンデンサ (各ピンに 1 つずつ) と 1 つのバルク・コンデンサを使用して PGND にバイパスします。        |  |  |

| TOFF   | 19               | 14   | I   | 入力           | 電流チョッピング中のディケイ・モードのオフ時間を設定します。4 レベル・ピン。また、スマート・チューン・リップル・コントロール・モードでリップル電流を設定します。                     |  |  |

| nFAULT | 16               | 11   | 0   | オープンドレ<br>イン | フォルト通知。フォルト条件により論理 Low に駆動されます。オープンドレイン出力には外部プルアップ抵抗が必要です。                                            |  |  |

| nSLEEP | 26               | 21   | I   | 入力           | スリープ・モード入力。ロジック High でデバイスをイネーブル。ロジック Low で低消費電力スリープ・モードに移行。内部プルダウン抵抗。nSLEEP Low パルスにより、フォルトがクリアされます。 |  |  |

| PAD    | -                | -    | -   | -            | サーマル・パッド。システム・グランドに接続します。                                                                             |  |  |

# 6 仕様

# 6.1 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

|                                                          | 最小   | 最大                  | 単位 |

|----------------------------------------------------------|------|---------------------|----|

| 電源電圧 (VM)                                                | -0.3 | 35                  | V  |

| チャージ・ポンプ電圧 (VCP、CPH)                                     | -0.3 | V <sub>VM</sub> + 7 | V  |

| チャージ・ポンプ負スイッチング・ピン (CPL)                                 | -0.3 | $V_{VM}$            | V  |

| nSLEEP ピン電圧 (nSLEEP)                                     | -0.3 | $V_{VM}$            | V  |

| 内部レギュレータ電圧 (DVDD)                                        | -0.3 | 5.75                | V  |

| 制御ピン電圧 (STEP、DIR、ENABLE、nFAULT、DECAYO、DECAY1、TOFF、MO、M1) | -0.3 | 5.75                | V  |

| オープンドレイン出力電流 (nFAULT)                                    | 0    | 10                  | mA |

| Reference input pin voltage (VREF)                       | -0.3 | 5.75                | V  |

| 巻線出力ピン電圧 (連続) (AOUT1、AOUT2、BOUT1、BOUT2)                  | -1   | V <sub>VM</sub> + 1 | V  |

| 巻線出力ピン電圧 (過渡 100ns) (AOUT1、AOUT2、BOUT1、BOUT2)            | -3   | V <sub>VM</sub> + 3 | V  |

| ピーク駆動電流 (AOUT1、AOUT2、BOUT1、BOUT2)                        | 内部的  | に制限                 | Α  |

| 動作時周囲温度、TA                                               | -40  | 125                 | °C |

| 動作時の接合部温度、TJ                                             | -40  | 150                 | °C |

| 保管温度、T <sub>stg</sub>                                    | -65  | 150                 | °C |

<sup>(1)</sup> 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

# 6.2 ESD 定格

|                         |                                          |                                       |        | 値     | 単位 |

|-------------------------|------------------------------------------|---------------------------------------|--------|-------|----|

|                         |                                          | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 |        | ±2000 |    |

| V <sub>(ESD)</sub> 静電放電 | デバイス帯電モデル (CDM)、JEDEC 規格 JESD22- C101 準拠 | PWP のコーナー・ピン (1、14、15、28)             | ±750   | V     |    |

|                         |                                          |                                       | その他のピン | ±500  |    |

# 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                                | 最小   | 最大                 | 単位  |

|-------------------|--------------------------------|------|--------------------|-----|

| $V_{VM}$          | 通常 (DC) 動作の電源電圧範囲              | 4.5  | 33                 | V   |

| VI                | 論理レベル入力電圧                      | 0    | 5.5                | V   |

| $V_{VREF}$        | VREF 電圧(DRV8424)               | 0.05 | 3.3                | V   |

| V <sub>VREF</sub> | VREF 電圧 (DRV8425)              | 0.05 | 2.64               | V   |

| $f_{STEP}$        | 印加 STEP 信号 (STEP)              | 0    | 500 <sup>(1)</sup> | kHz |

| I <sub>FS</sub>   | モータ・フルスケール電流 (xOUTx) (DRV8424) | 0    | 2.5 <sup>(2)</sup> | Α   |

| I <sub>FS</sub>   | モータ・フルスケール電流 (xOUTx) (DRV8425) | 0    | 2 (2)              | Α   |

| I <sub>rms</sub>  | モータ RMS 電流 (xOUTx) (DRV8424)   | 0    | 1.8 <sup>(2)</sup> | Α   |

| I <sub>rms</sub>  | モータ RMS 電流 (xOUTx) (DRV8425)   | 0    | 1.4 <sup>(2)</sup> | Α   |

| T <sub>A</sub>    | 動作時の周囲温度                       | -40  | 125                | °C  |

| TJ                | 動作時のジャンクション温度                  | -40  | 150                | °C  |

- (1) STEP 入力は最高 500kHz で動作しますが、システムの帯域幅はモータの負荷により制限されます。

- (2) 消費電力および温度の制限に従う必要があります。

# 6.4 熱に関する情報

|                       |                             | DRV8424/25   |            |      |  |

|-----------------------|-----------------------------|--------------|------------|------|--|

|                       | <b>熱評価基準</b> <sup>(1)</sup> | PWP (HTSSOP) | RGE (VQFN) | 単位   |  |

|                       |                             | 28 ピン        | 24 ピン      |      |  |

| $R_{\theta JA}$       | 接合部から周囲への熱抵抗                | 31.0         | 40.7       | °C/W |  |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗         | 25.2         | 31.8       | °C/W |  |

| $R_{\theta JB}$       | 接合部から基板への熱抵抗                | 10.8         | 17.7       | °C/W |  |

| ΨЈТ                   | 接合部から上面への熱特性                | 0.4          | 0.6        | °C/W |  |

| $\Psi_{JB}$           | 接合部から基板への評価パラメータ            | 10.7         | 17.7       | °C/W |  |

| $R_{\theta JC(bot)}$  | 接合部からケース (底面) への熱抵抗         | 3.3          | 4.7        | °C/W |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

Submit Document Feedback

# 6.5 電気的特性

標準値は  $T_A = 25^{\circ}C$ 、 $V_{VM} = 24V$  での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| す。                   | パラメータ                       | テスト条件                                        | 最小        | 標準                  | 最大   | 単位  |

|----------------------|-----------------------------|----------------------------------------------|-----------|---------------------|------|-----|

| 電源 (VM、              | DVDD)                       |                                              |           |                     |      |     |

| I <sub>VM</sub>      | VM 動作電源電流                   | ENABLE = 1、nSLEEP = 1、モータ負荷なし                |           | 5                   | 6.5  | mA  |

| I <sub>VMQ</sub>     | VM スリープ・モード電源電流             | nSLEEP = 0                                   |           | 2                   | 4    | μA  |

| t <sub>SLEEP</sub>   | スリープ時間                      | nSLEEP = 0 でスリープモード                          | 120       |                     |      | μs  |

| t <sub>RESET</sub>   | nSLEEP リセット・パルス             | nSLEEP = Low でフォルトをクリア                       | 20        |                     | 40   | μs  |

| t <sub>WAKE</sub>    | ウェークアップ時間                   | nSLEEP = 1 で出力遷移                             |           | 0.8                 | 1.2  | ms  |

| t <sub>ON</sub>      | ターンオン時間                     | VM > UVLO で出力遷移                              |           | 0.8                 | 1.2  | ms  |

| t <sub>EN</sub>      | イネーブル時間                     | ENABLE =0/1 で出力遷移                            |           |                     | 5    | μs  |

|                      |                             | 外部負荷なし、6V < V <sub>VM</sub> < 33 V           | 4.75      | 5                   | 5.25 | V   |

| $V_{DVDD}$           | 内部レギュレータ電圧                  | 外部負荷なし、V <sub>VM</sub> = 4.5 V               | 4.2       | 4.35                |      | V   |

| チャージ・ホ               | <br>『ンプ (VCP、CPH、CPL)       | VIVI                                         |           |                     |      |     |

| V <sub>CP</sub>      | VCP 動作電圧                    | 6 V < V <sub>VM</sub> < 33 V                 |           | V <sub>VM</sub> + 5 |      | V   |

| f <sub>(CP)</sub>    | チャージ・ポンプ・スイッチング周波数          | V <sub>VM</sub> > UVLO, nSLEEP = 1           |           | 360                 |      | kHz |

| 論理レベル                | <br>入力 (STEP、DIR、nSLEEP)    |                                              |           |                     |      |     |

| V <sub>IL</sub>      | 入力論理 <b>Low</b> 電圧          |                                              | 0         |                     | 0.6  | V   |

| V <sub>IH</sub>      | 入力論理 High 電圧                |                                              | 1.5       |                     | 5.5  | V   |

| V <sub>HYS</sub>     | 入力論理ヒステリシス                  |                                              |           | 150                 |      | mV  |

| I <sub>IL</sub>      | 入力論理 Low 電流                 | V <sub>IN</sub> = 0V                         | <b>–1</b> |                     | 1    | μA  |

| I <sub>IH</sub>      | 入力論理 High 電流                | V <sub>IN</sub> = 5V                         |           |                     | 100  | μA  |

| トライレベル               | ·入力 (M0、DECAY0、DECAY1、E     |                                              |           |                     |      |     |

| V <sub>I1</sub>      | 入力論理 Low 電圧                 | GND に接続                                      | 0         |                     | 0.6  | V   |

| V <sub>I2</sub>      | 入力 <b>Hi-Z</b> 電圧           | ハイ・インピーダンス                                   | 1.8       | 2                   | 2.2  | V   |

| V <sub>I3</sub>      | 入力論理 High 電圧                | DVDD に接続                                     | 2.7       |                     | 5.5  | V   |

| I <sub>O</sub>       | 出力プルアップ電流                   |                                              |           | 10                  |      | μA  |

| クワッドレベ               | ル入力 (M1、TOFF)               |                                              |           |                     | '    |     |

| V <sub>I1</sub>      | 入力論理 Low 電圧                 | GND に接続                                      | 0         |                     | 0.6  | V   |

| V <sub>I2</sub>      |                             | 330kΩ ± 5% を GND との間に接続                      | 1         | 1.25                | 1.4  | V   |

| V <sub>I3</sub>      | 入力 Hi-Z 電圧                  | ハイ・インピーダンス                                   | 1.8       | 2                   | 2.2  | V   |

| V <sub>I4</sub>      | 入力論理 High 電圧                | DVDD に接続                                     | 2.7       |                     | 5.5  | V   |

| I <sub>IL</sub>      | 出力プルアップ電流                   |                                              |           | 10                  |      | μA  |

| 制御出力 (1              | nFAULT)                     |                                              |           |                     |      |     |

| V <sub>OL</sub>      | 出力論理 Low 電圧                 | I <sub>O</sub> = 5mA                         |           |                     | 0.5  | V   |

| I <sub>OH</sub>      | 出力論理 High リーク電流             |                                              | -1        |                     | 1    | μΑ  |

| モータ・ドラ               | イバ出力 (AOUT1、AOUT2、BOUT      | Г1、BOUT2)                                    |           |                     |      |     |

|                      | 13 No. 5 1                  | $T_J = 25$ °C, $I_O = -1A$                   |           | 165                 | 200  | mΩ  |

| R <sub>DS(ONH)</sub> | ハイサイド FET オン抵抗<br>(DRV8424) | T <sub>J</sub> = 125°C, I <sub>O</sub> = -1A |           | 250                 | 300  | mΩ  |

|                      | , , ,                       | T <sub>J</sub> = 150°C, I <sub>O</sub> = -1A |           | 280                 | 350  | mΩ  |

|                      | 3 85 5 1211                 | $T_J = 25^{\circ}C, I_O = 1 A$               |           | 165                 | 200  | mΩ  |

| R <sub>DS(ONL)</sub> | ローサイド FET オン抵抗<br>(DRV8424) | T <sub>J</sub> = 125°C, I <sub>O</sub> = 1 A |           | 250                 | 300  | mΩ  |

|                      | (DRV8424)                   | T <sub>J</sub> = 150°C, I <sub>O</sub> = 1 A |           | 280                 | 350  | mΩ  |

標準値は  $T_A = 25$ °C、 $V_{VM} = 24$ V での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| 7 0                   | パラメータ                        | テスト条件                                                  | 最小    | 標準                  | 最大    | 単位   |

|-----------------------|------------------------------|--------------------------------------------------------|-------|---------------------|-------|------|

|                       |                              | T <sub>J</sub> = 25°C, I <sub>O</sub> = -1A            |       | 275                 | 330   | mΩ   |

| R <sub>DS(ONH)</sub>  | ハイサイド FET オン抵抗<br>(DRV8425)  | $T_J = 125^{\circ}C, I_O = -1A$                        |       | 410                 | 500   | mΩ   |

|                       | (                            | T <sub>J</sub> = 150°C, I <sub>O</sub> = -1A           |       | 460                 | 580   | mΩ   |

|                       |                              | T <sub>J</sub> = 25°C, I <sub>O</sub> = 1 A            |       | 275                 | 330   | mΩ   |

| R <sub>DS(ONL)</sub>  | ローサイド FET オン抵抗<br>(DRV8425)  | T <sub>J</sub> = 125°C, I <sub>O</sub> = 1 A           |       | 410                 | 500   | mΩ   |

|                       | (51(40420)                   | T <sub>J</sub> = 150°C, I <sub>O</sub> = 1 A           |       | 460                 | 580   | mΩ   |

| t <sub>SR</sub>       | 出力スルーレート                     | V <sub>VM</sub> = 24V、I <sub>O</sub> = 1A、10% と 90% の間 |       | 240                 |       | V/µs |

| PWM 電流                | li御 (VREF)                   |                                                        |       |                     |       |      |

| K <sub>V</sub>        | トランスインピーダンス・ゲイン              | VREF = 3.3 V                                           | 1.254 | 1.32                | 1.386 | V/A  |

| I <sub>VREF</sub>     | VREF リーク電流                   | VREF = 3.3 V                                           |       |                     | 8.25  | μA   |

|                       |                              | TOFF = 0                                               |       | 7                   |       |      |

| t <sub>OFF</sub>      | PWM オフ時間                     | TOFF = 1                                               |       | 16                  |       | - µs |

|                       |                              | TOFF = ハイ・インピーダンス                                      |       | 24                  |       |      |

|                       |                              | TOFF = 330kΩ を GND との間に接続                              |       | 32                  |       |      |

|                       | 電流トリップ精度                     | I <sub>O</sub> = 2.5A、10%~20% 電流設定                     | -8    |                     | 12    |      |

| $\Delta I_{TRIP}$     |                              | I <sub>O</sub> = 2.5A、20%~40% 電流設定                     | -7    |                     | 7     | %    |

|                       |                              | I <sub>O</sub> = 2.5A、40%~100% 電流設定                    | -5    |                     | 5     |      |

| I <sub>O,CH</sub>     | AOUT とBOUT の電流マッチング          | I <sub>O</sub> = 2.5 A                                 | -2.5  |                     | 2.5   | %    |

| 保護回路                  |                              |                                                        |       |                     |       |      |

| V                     | <b>VM</b> 広季工部新作件 (11/11/01) | VM 立ち下がり、UVLO 立ち下がり                                    | 4.1   | 4.25                | 4.35  | V    |

| $V_{UVLO}$            | VM 低電圧誤動作防止 (UVLO)           | VM 立ち上がり、UVLO 立ち上がり                                    | 4.2   | 4.35                | 4.45  | V    |

| V <sub>UVLO,HYS</sub> | 低電圧ヒステリシス                    | 立ち上がりから立ち下がりへのスレッショルド                                  |       | 100                 |       | mV   |

| $V_{CPUV}$            | チャージ・ポンプ低電圧                  | VCP 立ち下がり、CPUV 通知                                      |       | V <sub>VM</sub> + 2 |       | V    |

| $I_{OCP}$             | 過電流保護                        | FET を流れる電流、DRV8424                                     | 4     |                     |       | Α    |

| I <sub>OCP</sub>      | 過電流保護                        | FET を流れる電流、DRV8425                                     | 3.2   |                     |       | Α    |

| t <sub>OCP</sub>      | 過電流グリッチ除去時間                  |                                                        |       | 1.8                 |       | μs   |

| t <sub>RETRY</sub>    | 過電流リトライ時間                    |                                                        |       | 4                   |       | ms   |

| T <sub>OTSD</sub>     | サーマル・シャットダウン                 | ダイ温度 T <sub>J</sub>                                    | 150   | 165                 | 180   | °C   |

| $T_{HYS\_OTSD}$       | 過熱保護閾値ヒステリシス                 | ダイ温度 T <sub>J</sub>                                    |       | 20                  |       | °C   |

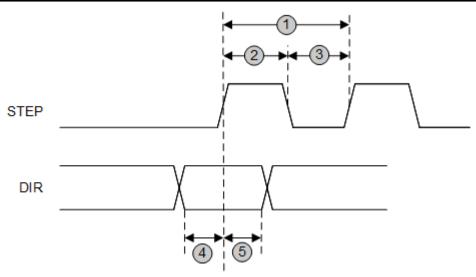

# 6.6 インデクサ・タイミング要件

特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| 番号 |                          |                                        | 最小  | 最大                 | 単位  |

|----|--------------------------|----------------------------------------|-----|--------------------|-----|

| 1  | $f_{STEP}$               | ステップ周波数                                |     | 500 <sup>(1)</sup> | kHz |

| 2  | t <sub>WH(STEP)</sub>    | パルス幅、STEP High                         | 970 |                    | ns  |

| 3  | t <sub>WL(STEP)</sub>    | パルス幅、STEP Low                          | 970 |                    | ns  |

| 4  | t <sub>SU(DIR, Mx)</sub> | セットアップ時間、DIR または MODEx から STEP 立ち上がりまで | 200 |                    | ns  |

| 5  | t <sub>H(DIR, Mx)</sub>  | ホールド時間、ステップ立ち上がりから DIR または MODEx 変更まで  | 200 |                    | ns  |

(1) STEP 入力は最高 500kHz で動作しますが、システムの帯域幅はモータの負荷により制限されます。

図 6-1. ステップおよび方向のタイミング図

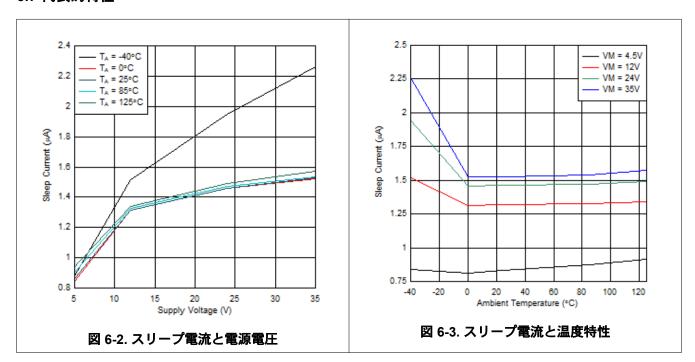

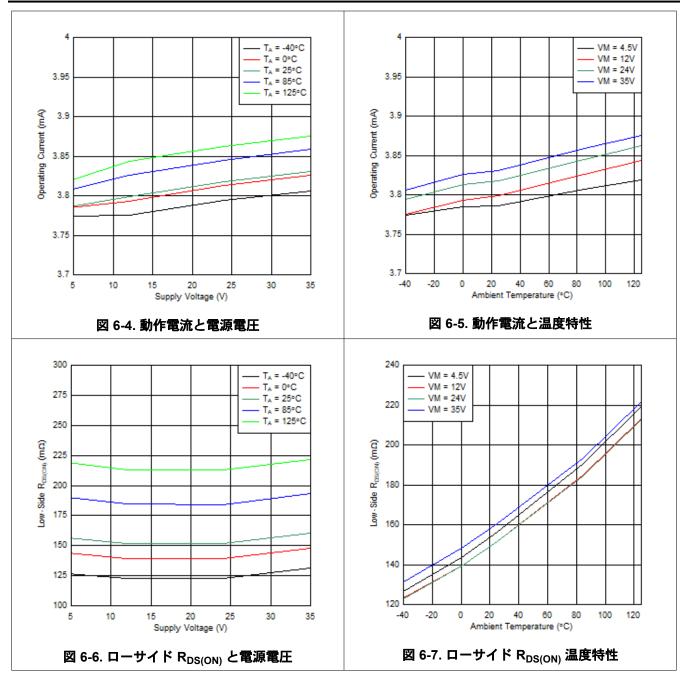

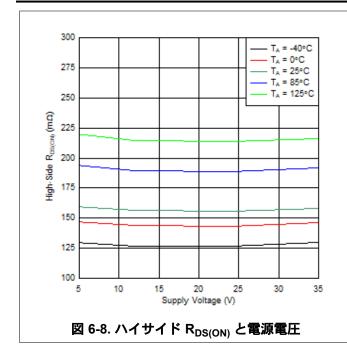

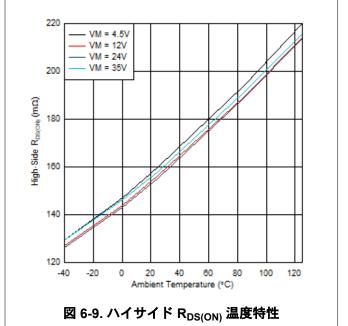

# 6.7 代表的特性

## 7 詳細説明

#### 7.1 概要

DDRV8424/25 デバイスは、バイポーラ・ステッピング・モータ向けの統合型モータ・ドライバ・ソリューションです。これらの デバイスは、2 つの N チャネルパワー MOSFET H ブリッジ、電流検出抵抗とレギュレーション回路、およびマイクロステッピング・インデクサを統合することで、最大の統合を実現します。DRV8424 および DRV8425 は、DRV8426、DRV8436、DRV8434 とピン互換です。DRV8424 および DRV8425 は、4.5~33V の広い電源電圧をサポートできます。DRV8424 は最大 4A ピーク、2.5A フルスケール、または 1.8A の 2 乗平均平方根(RMS)の出力電流を供給し、DRV8425 は最大 3.2A ピーク、2A フルスケール、または 1.4A の 2 乗平均平方根(RMS)の出力電流を供給します。実際のフルスケールおよび RMS 電流は、周囲温度、電源電圧、PCB の熱性能に依存します。

DRV8424/25 デバイスは電流センス・アーキテクチャを内蔵しているため、2 つの外部電力センス抵抗が不要になり、基板面積、BOM コスト、設計作業が大幅に削減され、消費電力が大幅に低減されます。このアーキテクチャでは、電流センシングに電流ミラー手法と内部パワー MOSFET を使うことで、センス抵抗での電力消費をなくしています。電流レギュレーションの設定点は VREF ピンの電圧で調整できます。

シンプルな STEP/DIR インターフェイスにより、外部コントローラからステッピング・モータの方向とステップ速度を制御できます。内部マイクロステッピング・インデクサを使うと、巻線電流レベルを制御する外部コントローラを使わなくても高精度のマイクロステッピングを実行できます。このインデクサはフルステップ、ハーフステップ、1/4、1/8、1/16、1/32、1/64、1/128、1/256 マイクロステッピングを実行できます。高いマイクロステップにより、大きな可聴ノイズの低減とスムーズな動作が可能になります。標準のハーフステップ・モードに加えて、非真円ハーフステップ・モードを利用して、モータの RPMが高いときにトルク出力を増大させることもできます。

ステッピング・モータ・ドライバは、スロー・ディケイ、ミックス・ディケイ、ファースト・ディケイなど、いくつかの種類のディケイ・モードを実装することにより、巻線電流を再循環する必要があります。DRV8424/25 には、スマート・チューン・ディケイ・モードが搭載されています。スマート・チューンは革新的なディケイ・メカニズムで、電圧、モータ速度、ばらつき、経年変化の影響に関係なく、最適な電流レギュレーション性能を自動的に調整します。スマート・チューン・リップル・コントロールでは、オフ時間可変型のリップル電流制御方式により、モータ巻線電流の歪みを最小限に抑えることができます。スマート・チューン・ダイナミック・ディケイでは、オフ時間固定のダイナミック・ファースト・ディケイ率方式により、モータ巻線電流の歪みを最小限に抑え、周波数成分が最小化でき、設計作業も低減できます。このシームレスで簡単な自動スマート・チューンに加えて、DRV8424/25 はスロー・ミックスやミックス・ディケイなどの従来のディケイ・モードも備えています。

また、低消費電力スリープ・モードを内蔵しているため、モータをアクティブ駆動していないときにシステムの電力を節約できます。

# 7.2 機能ブロック図

# 7.3 機能説明

表 7-1 に、DRV8424/25 の推奨外付け部品を示します。

#### 表 7-1. DRV8424/25 外付け部品

| 部品                        | ピン1     | ピン2    | 推奨する事項                                                             |

|---------------------------|---------|--------|--------------------------------------------------------------------|

| C <sub>VM1</sub>          | VM      | PGND   | 2 つの X7R、0.01μF、VM 定格セラミック・コンデンサ                                   |

| C <sub>VM2</sub>          | VM      | PGND   | バルク、VM 定格コンデンサ                                                     |

| C <sub>CP</sub>           | VCP     | VM     | X7R、0.22μF、16V セラミック・コンデンサ                                         |

| C <sub>SW</sub>           | СРН     | CPL    | X7R、0.022μF、VM 定格セラミック・コンデンサ                                       |

| C <sub>DVDD</sub>         | DVDD    | GND    | X7R、0.47μF~1μF、6.3V セラミック・コンデンサ                                    |

| R <sub>nFAULT</sub>       | VCC (1) | nFAULT | 4.7kΩ 以上の抵抗                                                        |

| R <sub>REF1</sub>         | VREF    | VCC    | チョッピング電流を制限するための抵抗。 $R_{REF1}$ と $R_{REF2}$ の並列抵抗値を $50k\Omega$ より |

| R <sub>REF2</sub> (オプション) | VREF    | GND    | <b>るいさくすることを推奨します。</b>                                             |

(1) VCC は DRV8424/25 のピンではありませんが、オープンドレイン出力の nFAULT は VCC 電源電圧にプルアップする必要があります。nFAULT は DVDD にプルアップすることもできます。

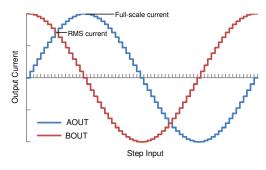

#### 7.3.1 ステッピング・モータ・ドライバの電流定格

ステッピング・モータ・ドライバは、出力電流を表す 3 種類の数値 (ピーク、RMS、フルスケール) を使用して分類できます。

#### 7.3.1.1 ピーク電流定格

ステッピング・ドライバのピーク電流は、過電流保護閾値 I<sub>OCP</sub> で制限されます。ピーク電流は、すべての過渡電流パルスを指します (例:静電容量の充電時、デューティ・サイクルが極めて小さい場合)。一般に、I<sub>OCP</sub> の最小値は、ステッピング・モータ・ドライバのピーク電流定格を規定します。 DRV8424 の場合、ピーク電流定格はブリッジごとに 4A、 DRV8425 の場合、ピーク電流定格はブリッジごとに 3.2A です。

#### 7.3.1.2 RMS 電流定格

RMS (平均) 電流は、IC の熱性能を考慮して求めます。RMS 電流は、25℃の代表的なシステムでの R<sub>DS(ON)</sub>、立ち上がりおよび立ち下がり時間、PWM 周波数、デバイスの静止電流、パッケージの熱的性能に基づいて計算されます。実動作時の RMS 電流は放熱と周囲温度に応じて上下する場合があります。DRV8424 の場合、RMS 電流定格はブリッジごとに 1.75A、DRV8425 の場合、RMS 電流定格はブリッジごとに 1.4A です。

#### 7.3.1.3 フルスケール電流定格

フルスケール電流とは、マイクロステッピング時の正弦電流波形の最大値を指します。この正弦波振幅は RMS 電流に関係しているため、フルスケール電流もデバイスの熱性能を考慮して求めます。フルスケール電流定格は、正弦波電流波形の場合は約√2 × I<sub>RMS</sub>、方形波電流波形の場合は I<sub>RMS</sub> (フルステップ)です。

表 7-2. 電流定格

|            | DRV8424 | DRV8425 |

|------------|---------|---------|

| ピーク電流定格    | 4A      | 3.2 A   |

| RMS 電流定格   | 1.8 A   | 1.4 A   |

| フルスケール電流定格 | 2.5A    | 2A      |

図 7-2. フルスケール電流と RMS 電流

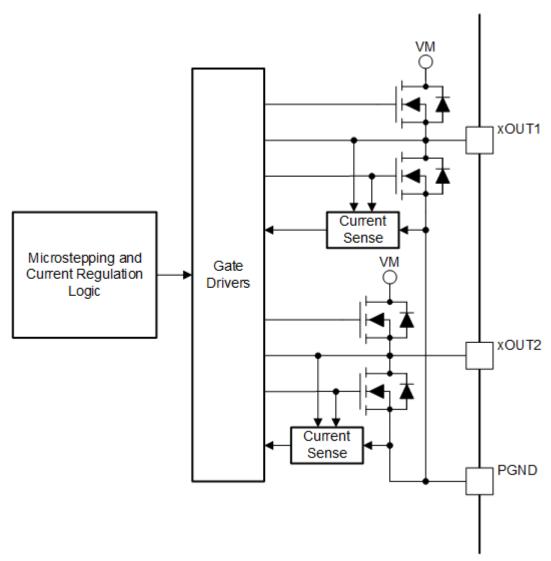

#### 7.3.2 PWM モータ・ドライバ

図 7-3. PWM モータ・ドライバのブロック図

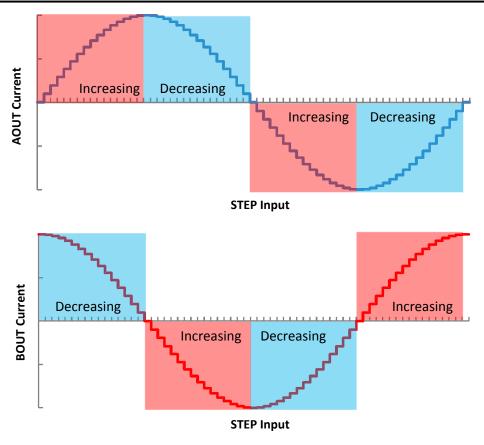

## 7.3.3 マイクロステッピング・インデクサ

DRV8424/25 の内蔵インデックス状態制御 (インデクサ) ロジックを使用すると、各種ステップ・モードに対応できます。表7-3 に示すとおり、M0 ピンと M1 ピンを使用してステップ・モードを設定します。この設定は、実行中に変更できます。

表 7-3. マイクロステッピング・インデクサの設定

| MODE0          | MODE1                     | ステップ・モード                 |

|----------------|---------------------------|--------------------------|

| 0              | 0                         | 100% 電流によるフルステップ (2 相励起) |

| 0              | 330kΩ を<br>GND との<br>間に接続 | 71% 電流によるフルステップ (2 相励起)  |

| 1              | 0                         | 非真円 1/2 ステップ             |

| ハイ・イン<br>ピーダンス | 0                         | 1/2 ステップ                 |

# 表 7-3. マイクロステッピング・インデクサの設定 (continued)

|                |                           | (          |

|----------------|---------------------------|------------|

| MODE0          | MODE1                     | ステップ・モード   |

| 0              | 1                         | 1/4 ステップ   |

| 1              | 1                         | 1/8 ステップ   |

| ハイ・イン<br>ピーダンス | 1                         | 1/16 ステップ  |

| 0              | ハイ・イン<br>ピーダンス            | 1/32 ステップ  |

| ハイ・イン<br>ピーダンス | 330kΩ を<br>GND との<br>間に接続 | 1/64 ステップ  |

| Hi-Z           | Hi-Z                      | 1/128 ステップ |

| 1              | ハイ・イン<br>ピーダンス            | 1/256 ステップ |

表 7-4 に、フルステップ (71% 電流)、1/2 ステップ、1/4 ステップ、1/8 ステップ動作の電流の相対値とステップ方向を示します。マイクロステッピングの分解能がより高い場合も同じパターンに従います。AOUT 電流は電気角の正弦、BOUT 電流は電気角の余弦です。正電流は、駆動時に xOUT1 ピンから xOUT2 ピンに流れる電流と定義します。

STEP 入力の各立ち上がりエッジで、インデクサは表内の次の状態に移行します。この方向は、DIR ピンが論理 High の場合です。 DIR ピンが論理 Low の場合、シーケンスは反転します。

#### 注

ステップの実行中にステップ・モードが変更された場合、STEP の立ち上がりエッジで、インデクサは次の有効な状態に進み、新しいステップ・モード設定になります。

初期励起状態は 45°の電気角で、両方のコイルのフルスケール電流の 71% に対応します。この状態には、デバイス起動後、ロジック・リセット解除後、スリープ・モードを解除後のいずれかで移行します。

表 7-4. 電流の相対値とステップ方向

| 1/8 ステップ | 1/4 ステップ | 1/2 ステップ | フルステップ 71% | AOUT 電流<br>(フルスケールに対する %) | BOUT 電流<br>(フルスケールに対す<br>る%) | 電気角 (度) |

|----------|----------|----------|------------|---------------------------|------------------------------|---------|

| 1        | 1        | 1        |            | 0%                        | 100%                         | 0.00    |

| 2        |          |          |            | 20%                       | 98%                          | 11.25   |

| 3        | 2        |          |            | 38%                       | 92%                          | 22.50   |

| 4        |          |          |            | 56%                       | 83%                          | 33.75   |

| 5        | 3        | 2        | 1          | 71%                       | 71%                          | 45.00   |

| 6        |          |          |            | 83%                       | 56%                          | 56.25   |

| 7        | 4        |          |            | 92%                       | 38%                          | 67.50   |

| 8        |          |          |            | 98%                       | 20%                          | 78.75   |

| 9        | 5        | 3        |            | 100%                      | 0%                           | 90.00   |

| 10       |          |          |            | 98%                       | -20%                         | 101.25  |

| 11       | 6        |          |            | 92%                       | -38%                         | 112.50  |

| 12       |          |          |            | 83%                       | -56%                         | 123.75  |

| 13       | 7        | 4        | 2          | 71%                       | -71%                         | 135.00  |

| 14       |          |          |            | 56%                       | -83%                         | 146.25  |

| 15       | 8        |          |            | 38%                       | -92%                         | 157.50  |

| 16       |          |          |            | 20%                       | -98%                         | 168.75  |

| 17       | 9        | 5        |            | 0%                        | -100%                        | 180.00  |

# 表 7-4. 電流の相対値とステップ方向 (continued)

| 式 1-7. 电加砂油 MECパノ ノノカド (Continuca) |          |          |            |                           |                              |         |

|------------------------------------|----------|----------|------------|---------------------------|------------------------------|---------|

| 1/8 ステップ                           | 1/4 ステップ | 1/2 ステップ | フルステップ 71% | AOUT 電流<br>(フルスケールに対する %) | BOUT 電流<br>(フルスケールに対す<br>る%) | 電気角 (度) |

| 18                                 |          |          |            | -20%                      | -98%                         | 191.25  |

| 19                                 | 10       |          |            | -38%                      | -92%                         | 202.50  |

| 20                                 |          |          |            | -56%                      | -83%                         | 213.75  |

| 21                                 | 11       | 6        | 3          | -71%                      | -71%                         | 225.00  |

| 22                                 |          |          |            | -83%                      | -56%                         | 236.25  |

| 23                                 | 12       |          |            | -92%                      | -38%                         | 247.50  |

| 24                                 |          |          |            | -98%                      | -20%                         | 258.75  |

| 25                                 | 13       | 7        |            | -100%                     | 0%                           | 270.00  |

| 26                                 |          |          |            | -98%                      | 20%                          | 281.25  |

| 27                                 | 14       |          |            | -92%                      | 38%                          | 292.50  |

| 28                                 |          |          |            | -83%                      | 56%                          | 303.75  |

| 29                                 | 15       | 8        | 4          | -71%                      | 71%                          | 315.00  |

| 30                                 |          |          |            | -56%                      | 83%                          | 326.25  |

| 31                                 | 16       |          |            | -38%                      | 92%                          | 337.50  |

| 32                                 |          |          |            | -20%                      | 98%                          | 348.75  |

|                                    |          |          |            |                           |                              |         |

表 7-5 に、100% のフルスケール電流によるフルステップ動作を示します。このステッピング・モードは、71% の電流によるフルステップ・モードよりも多くの電力を消費しますが、高いモータ RPM で高トルクを実現できます。

表 7-5. 100% 電流によるフルステップ

| フルステップ 100% |      | BOUT 電流<br>(フルスケールに対する %) | 電気角 (度) |

|-------------|------|---------------------------|---------|

| 1           | 100  | 100                       | 45      |

| 2           | 100  | -100                      | 135     |

| 3           | -100 | -100                      | 225     |

| 4           | -100 | 100                       | 315     |

表 7-6 に、非真円 1/2 ステップ動作を示します。このステッピング・モードは真円 1/2 ステップ動作よりも多くの電力を消費しますが、高いモータ RPM で高トルクを実現できます。

表 7-6. 非真円 1/2 ステッピング電流

| 非真円 1/2 ステップ | AOUT 電流<br>(フルスケールに対する %) | BOUT 電流<br>(フルスケールに対する %) | 電気角 (度) |

|--------------|---------------------------|---------------------------|---------|

| 1            | 0                         | 100                       | 0       |

| 2            | 100                       | 100                       | 45      |

| 3            | 100                       | 0                         | 90      |

| 4            | 100                       | -100                      | 135     |

| 5            | 0                         | -100                      | 180     |

| 6            | -100                      | -100                      | 225     |

| 7            | -100                      | 0                         | 270     |

| 8            | -100                      | 100                       | 315     |

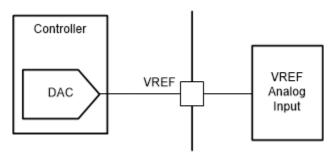

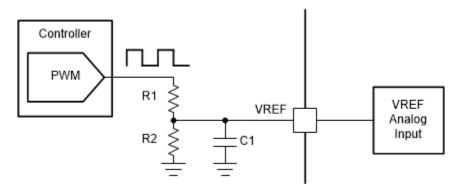

#### 7.3.4 MCU DAC による VREF の制御

場合によっては、フルスケール出力電流を、モータの速度と負荷に応じて各種の値に変更する必要があります。VREF ピンの電圧をシステムで調整する事でフルスケール電流を変更できます。

この動作モードでは、DAC 電圧が増加するにつれて、フルスケール・レギュレーション電流も減少します。正常に動作させるには、DRV8424 の場合は DAC の出力が 3.3V を超えないように、DRV8425 の場合は 2.64V を超えないようにする必要があります。

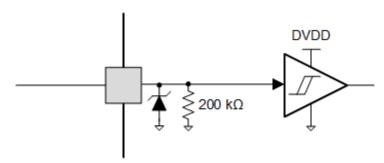

図 7-4. DAC 出力による VREF の制御

また、PWM 信号とローパス・フィルタを使用して VREF ピンを調整することもできます。

図 7-5. PWM 出力による VREF の制御

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

#### 7.3.5 電流レギュレーション

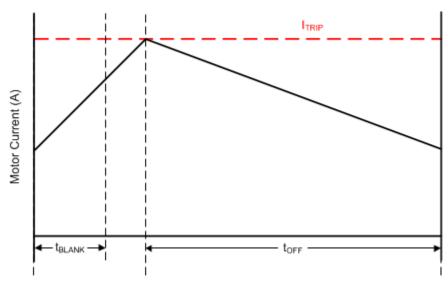

モータ巻線に流れる電流は、調整可能なオフ時間 PWM 電流レギュレーション回路によって制御されます。H ブリッジをイネーブルすると、現在の DC 電圧、巻線のインダクタンス、逆起電力の大きさに応じた速度で、巻線を流れる電流が増加します。電流が電流レギュレーション・スレッショルドに達すると、ブリッジは TOFF ピンの設定で決まる時間の間ディケイ・モードに移行して電流を低減します。オフ時間が経過すると、ブリッジは再イネーブルされ、次の PWM サイクルを開始します。

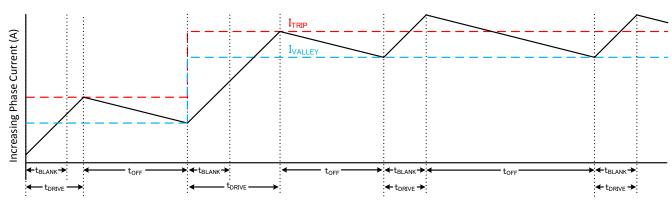

図 7-6. 電流チョッピング波形

PWM レギュレーション電流は、ローサイド・パワー MOSFET と並列に接続した電流センス MOSFET の両端の電圧を監視するコンパレータによって設定されます。電流センス MOSFET は、正弦波で重み付けした電流モード DAC の出力であるリファレンス電流でバイアスされます。この DAC のフルスケール・リファレンス電流は VREF ピンの電圧で設定します。

このフルスケール・レギュレーション電流 ( $I_{FS}$ ) は次の式で計算できます。 $I_{FS}$  (A) =  $V_{REF}$  (V) /  $K_V$  (V/A) =  $V_{REF}$  (V) / 1.32 (V/A)

#### 7.3.6 減衰モード

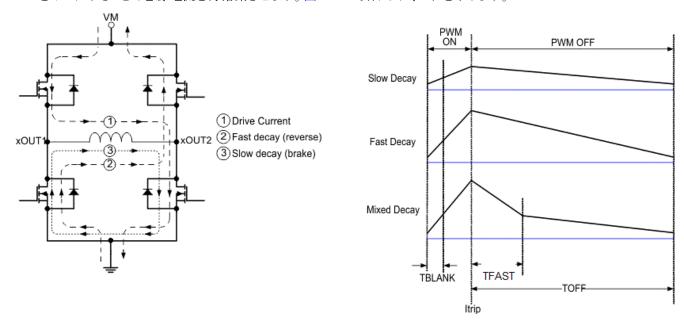

PWM 電流チョッピング中、PWM 電流チョッピング・スレッショルドに達するまで H ブリッジはモータ巻線を駆動します。 図 7-7 の項目 1 に、これを示します。

チョッピング電流スレッショルドに達した後、H ブリッジは 2 種類の状態 (高速減衰または低速減衰) で動作できます。高速減衰モードでは、PWM チョッピング電流スレッショルドに達すると、巻線電流が逆方向に流れるように H ブリッジは状態を反転させます。図 7-7 の項目 2 に、高速減衰モードを示します。低速減衰モードでは、ブリッジの両方のローサイド FET をオンにすることで巻線電流を再循環させます。図 7-7 の項目 3 に、これを示します。

図 7-7. 減衰モード

DRV8424/25 のディケイ・モードは DECAY0 ピンと DECAY1 ピンで選択されます (表 7-7 を参照)。 DECAY1 ピンが ハイ・インピーダンスの場合、 DECAY0 ピンの電圧に関係なく、 ディケイ・モードはスマート・チューン・ダイナミック・ディケイ になります。 このディケイ・モードは、 実行中に変更できます。 ディケイ・モードの変更後、10μs のデグリッチ時間後に新しいディケイ・モードが適用されます。

| DECAY0         | DECAY1 | 増加ステップ                | 減少ステップ                |

|----------------|--------|-----------------------|-----------------------|

| 0              | 0      | スマート・チューン・ダイナミック・ディケ  | スマート・チューン・ダイナミック・ディケイ |

| 0              | 1      | スマート・チューン・リップル・コントロール | スマート・チューン・リップル・コントロール |

| 1              | 0      | 混合減衰:30% 高速           | 混合減衰:30% 高速           |

| 1              | 1      | 低速減衰                  | 混合減衰:30% 高速           |

| ハイ・インピ<br>ーダンス | 0      | 混合減衰:60% 高速           | 混合減衰:60% 高速           |

| ハイ・インピ<br>ーダンス | 1      | 低速減衰                  | 低速減衰                  |

表 7-7. 減衰モードの設定

図 7-8 に、電流の増減を定義します。低速混合減衰モードの場合、電流増加ステップ中は低速減衰モードに設定され、電流減少ステップ中は混合減衰モードに設定されます。フルステップ動作および非真円 1/2 ステップ動作では、減少ステップに対応する減衰モードが常に使用されます。

図 7-8. 増加および減少ステップの定義

t<sub>DRIVE</sub>

←t<sub>DRIVE</sub> →

## 7.3.6.1 電流増加および減少でスロー・ディケイ

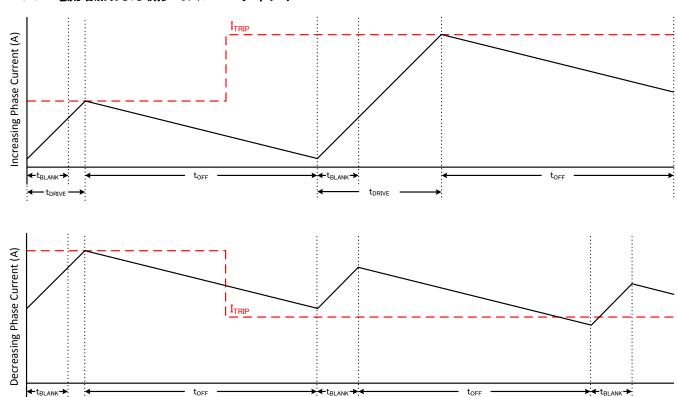

図 7-9. スロー/スロー・ディケイ・モード

←t<sub>DRIVE</sub> →

スロー・ディケイ中、Hブリッジのローサイド FET はどちらもオンになり、電流を再循環させます。

スロー・ディケイ・モードは、与えられた toff に対して、ディケイ・モードの中で最も小さい電流リップルを示します。しかし電流減少ステップでは、スロー・ディケイでは電流が非常にゆっくり減少するため、新しい ITRIP レベルに落ち着くのに長い時間がかかります。

電流が長時間保持されている (STEP ピンの入力がない) 場合、またはステップ速度が非常に小さい場合、モータ巻線に 逆起電力が生じないため、スロー・ディケイでは適切に電流を制御できない場合があります。この状態では、モータ電流が 急速に増加する可能性があり、長いオフ時間を必要とする場合があります。場合によっては、このために電流レギュレーションが失われる可能性があるため、より積極的なディケイ・モードが推奨されます。

# 7.3.6.2 電流増加ではスロー・ディケイ、電流減少ではミックス・ディケイ

Under the transmitter of the tr

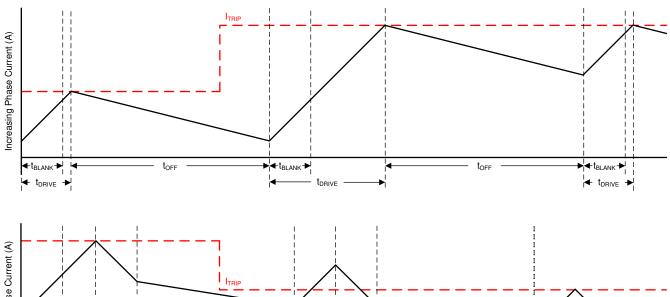

図 7-10. スロー・ミックス・ディケイ・モード

ミックス・ディケイでは、toff 時間の初めの一定期間はファースト・ディケイを行い、その後スロー・ディケイに切り替わります。このモードでは、ミックス・ディケイは電流減少時にのみアクティブになります。電流増加時にはスロー・ディケイが使用されます。

このモードでは、電流増加時にスロー・ディケイと同じ電流リップルが生じていますが、これは、電流増加時にはスロー・ディケイのみを使用するためです。電流減少時のリップルは、スロー・ディケイ時より大きくなりますが、ファースト・ディケイ時よりは小さくなります。電流減少ステップでは、ミックス・ディケイはスロー・ディケイよりも高速に新しい ITRIP レベルに落ち着きます。

## 7.3.6.3 電流増加および減少でミックス・ディケイ

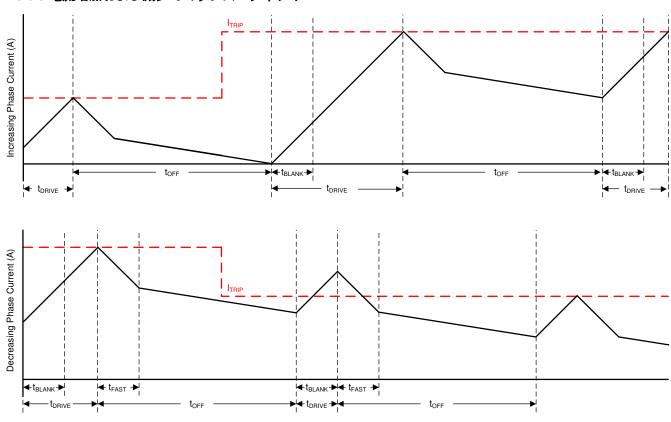

図 7-11. ミックス・ミックス・ディケイ・モード

ミックス・ディケイでは、toff 時間の初めの一定期間はファースト・ディケイを行い、その後スロー・ディケイに切り替わります。このモードでは、電流増加ステップと電流減少ステップの両方ともミックス・ディケイになります。

このモードでのリップルは、スロー・ディケイ時より大きくなりますが、ファースト・ディケイ時よりは小さくなります。電流減少ステップでは、ミックス・ディケイはスロー・ディケイよりも高速に新しい ITRIP レベルに落ち着きます。

電流が長時間保持されている (STEP ピンの入力がない)場合、またはステップ速度が非常に小さい場合、モータ巻線に 逆起電力が生じないため、スロー・ディケイでは適切に電流を制御できない場合があります。この状態では、モータ電流が 急速に増加する可能性があり、非常に長いオフ時間が必要です。増加または減少のミックス・ディケイ・モードを使用する と、モータ巻線に逆起電力が生じない場合、電流レベルは制御状態を維持できます。

# 7.3.6.4 スマート・チューン・ダイナミック・ディケイ

スマート・チューン電流レギュレーション方式は、従来の固定オフ時間電流レギュレーション方式に比べて高度な電流レギュレーション制御手法です。スマート・チューン電流レギュレーション方式を使うと、ステッピング・モータ・ドライバは以下のような動作要因に基づいてディケイ方式を調整できます。

- モータの巻線抵抗およびインダクタンス

- モータの経年変化

- モータの動的速度および負荷

- モータの電源電圧変動

- 立ち上がりおよび立ち下がりステップでのモータの逆起電力の差

- ステップ遷移

- 小電流と大電流の dl/dt

本デバイスは2つのスマート・チューン電流レギュレーション・モード (スマート・チューン・ダイナミック・ディケイとスマート・チューン・リップル・コントロール)を備えています。

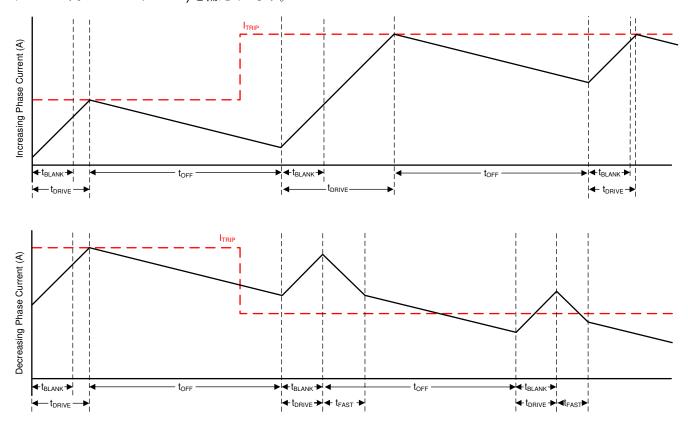

図 7-12. スマート・チューン・ダイナミック・ディケイ・モード

スマート・チューン・ダイナミック・ディケイでは、スロー、ミックス、ファースト・ディケイといったディケイ・モードが自動的に構成されるため、ディケイ・モードの選択が大幅に簡略化されます。ミックス・ディケイでは、スマート・チューンにより、ミックス・ディケイの総時間に対するファースト・ディケイの割合が動的に調整されます。この機能により、モータのリップルを最小限に抑える最良のディケイ設定が自動的に決定されるため、モータのチューニングが不要になります。

ディケイ・モード設定は、各 PWM サイクルで繰り返し最適化されます。モータ電流が目標トリップ・レベルを超えると、レギュレーション損失を防ぐため、次のサイクルでディケイ・モードはより積極的になります (ファースト・ディケイの割合を増やします)。目標トリップ・レベルに達するまでに長い駆動時間を必要とする場合は、リップルを抑え、効率を上げるために、次のサイクルでディケイ・モードはより消極的になります (ファースト・ディケイの割合を減らします)。立ち下がりステップでは、次のステップに素早く達するために、スマート・チューン・ダイナミック・ディケイは自動的にファースト・ディケイに切り替わります。

スマート・チューン・ダイナミック・ディケイは、電流レギュレーション方式で電流リップルを最小限に抑える必要がありながら、固定周波数を維持する必要があるアプリケーションに最適です。

# 7.3.6.5 スマート・チューン・リップル・コントロール

図 7-13. スマート・チューン・リップル・コントロール・ディケイ・モード

スマート・チューン・リップル・コントロールは、 $I_{TRIP}$  レベルと  $I_{VALLEY}$  レベルを設定することで動作します。電流レベルが  $I_{TRIP}$  に達すると、ドライバは  $t_{OFF}$  時間が経過するまでスロー・ディケイに移行する代わりに、 $I_{VALLEY}$  に達するまでスロー・ディケイに移行します。スロー・ディケイは、両方のローサイド MOSFET がオンになって電流が再循環できるモード 1 と同様に動作します。このモードでは、電流レベルと動作条件に応じて  $t_{OFF}$  が変化します。

このディケイ・モードのリップル電流は、TOFF ピンによってプログラミングされます。リップル電流は、特定のマイクロステップ・レベルの ITRIP に依存します。

| TOFF                       | 特定のマイクロステップ・レベルでの電流リップル |

|----------------------------|-------------------------|

| 0                          | 19mA + ITRIP ∅ 1%       |

| 1                          | 19mA + ITRIP Ø 2%       |

| ハイ・インピーダンス                 | 19mA + ITRIP ∅ 4%       |

| <b>330k</b> Ω を GND との間に接続 | 19mA + ITRIP Ø 6%       |

表 7-8. 電流リップル設定

このリップル制御方法によって、はるかに厳密な電流レベルのレギュレーションが可能になり、モータの効率とシステムの性能が向上します。スマート・チューン・リップル制御は、可変オフ時間レギュレーション方式に対応するシステムで電流レギュレーションの電流リップルを小さくするために使用できます。PWM 周波数が可聴範囲外であることを確認するには、低リップル電流設定を選択します。ただし、リップル電流の値が大きいほど、PWM 周波数が低下し、スイッチング損失が減少します。

#### 7.3.6.6 PWM オフ時間

TOFF ピンは、表 7-7 に示すように、スマート・チューン・リップル・コントロールを除くすべてのディケイ・モードの PWM オフ時間を設定します。このオフ時間設定は、実行中に変更できます。オフ時間設定を変更した後、10µs のデグリッチ時間後に新しいオフ時間が適用されます。

| 表 7-9. オフド | 間の設定 |

|------------|------|

|------------|------|

| TOFF               | オフ時間 |

|--------------------|------|

| 0                  | 7μs  |

| 1                  | 16µs |

| ハイ・インピーダンス         | 24µs |

| 330kΩ を GND との間に接続 | 32µs |

#### 7.3.6.7 ブランキング時間

H ブリッジで電流が出力されると (駆動相の開始)、電流センス・コンパレータ出力を一定時間 ( $t_{BLANK}$ ) 無視した後、電流センス回路を有効にします。ブランキング時間は、PWM の最小駆動時間も設定します。ブランキング時間は約  $1 \mu s$ です。

## 7.3.7 チャージ・ポンプ

ハイサイド N チャネル MOSFET のゲート駆動電圧を供給するため、チャージ・ポンプが内蔵されています。このチャージ・ポンプには、VM ピンと VCP ピンの間に電荷保持のためのコンデンサを接続する必要があります。また、フライング・コンデンサの役割として、CPH ピンと CPL ピンの間にもセラミック・コンデンサを接続する必要があります。

図 7-14. チャージ・ポンプのブロック図

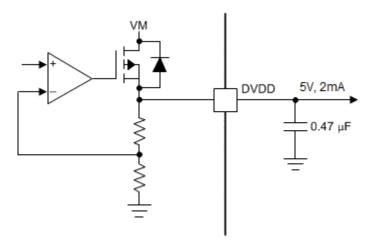

## 7.3.8 リニア電圧レギュレータ

DRV8424/25 には、リニア電圧レギュレータが内蔵されています。 DVDD レギュレータの出力は、リファレンス電圧に使用することができます。 DVDD は、最大 2mA の負荷電流を供給できます。 正常に動作させるため、 セラミック・コンデンサを使用して DVDD ピンを GND にバイパスします。

DVDD の出力は通常 5V です。 DVDD LDO の電流負荷が 2mA を超えると、出力電圧は大きく低下します。

図 7-15. リニア電圧レギュレータのブロック図

#### 図 7-16. リニア電圧レギュレータのブロック図

デジタル入力 (すなわち Mx、DECAYx、TOFF) を永続的に High に固定する場合、入力を外部レギュレータではなく DVDD ピンに接続することを推奨します。これにより、VM ピンに電圧が印加されないときやスリープ・モード時に電力を節約できます。 DVDD のレギュレータがディセーブルされている間、電流が入力プルダウン抵抗に流れないためです。参考までに、論理レベル入力は 200kΩ (標準値) のプルダウンを備えています。

nSLEEP ピンを DVDD に接続しないでください。さもないと本デバイスはスリープ・モードから出ることができません。

#### 7.3.9 論理レベル、トライレベル、クワッドレベルのピン構造図

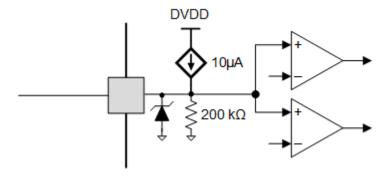

図 7-17 に、MO、DECAYO、DECAY1、ENABLE ピンの入力構造を示します。

図 7-17. トライレベル入力ピン構造図

図 7-17 に、M1、TOFF ピンの入力構造を示します。

図 7-18. クワッドレベル入力ピン構造図

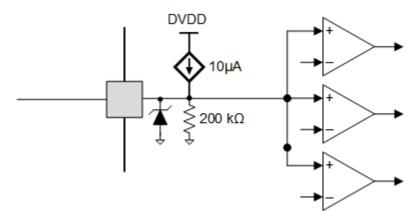

図 7-19 に、STEP、DIR、nSLEEP ピンの入力構造を示します。

図 7-19. 論理レベル入力ピン構造図

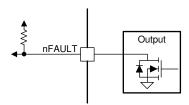

#### 7.3.10 nFAULT ピン

nFAULT ピンはオープンドレインの出力を持っているため、5V、3.3V または 1.8V 電源にプルアップする必要があります。フォルトが検出された場合、nFAULT ピンは論理 Low になります。起動後、nFAULT ピンは High になります。5V にプルアップする場合、nFAULT ピンを DVDD ピンに抵抗で接続できます。3.3V または 1.8V にプルアップする場合、外部電源を使う必要があります。

図 7-20. nFAULT ピン

#### 7.3.11 保護回路

DRV8424/25 は、電源低電圧、チャージ・ポンプ低電圧、出力過電流、デバイス過熱イベントからデバイスを保護します。

# 7.3.11.1 VM 低電圧誤動作防止 (UVLO)

VM ピンの電圧が電圧源の UVLO スレッショルド電圧を下回ると常に、すべての出力がディセーブルされ、nFAULT ピンが Low に駆動されます。この条件では、チャージ・ポンプはディセーブルされます。 VM 低電圧条件が解消すると、通常動作に復帰します (モータ・ドライバの動作と nFAULT の解放)。

## 7.3.11.2 VCP 低電圧誤動作防止 (CPUV)

VCP ピンの電圧が CPUV 電圧を下回ると常に、すべての出力がディセーブルされ、nFAULT ピンが Low に駆動されます。この条件の間、チャージ・ポンプはアクティブのまま維持されます。 VCP 低電圧条件が解消すると、通常動作に復帰します (モータ・ドライバの動作と nFAULT の解放)。

#### 7.3.11.3 過電流保護 (OCP)

各 FET のアナログ電流制限回路は、ゲート駆動を止めることで、FET に流れる電流を制限します。この電流制限が toce時間よりも長く続いた場合、両方の H ブリッジの FET がディセーブルされ、nFAULT ピンは Low に駆動されます。この条件の間、チャージ・ポンプはアクティブのまま維持されます。過電流保護は 2 つのモード (ラッチド・シャットダウンと自動リトライ) で動作できます。この動作モードは、実行中に変更できます。

#### 7.3.11.3.1 ラッチド・シャットダウン

ラッチド・シャットダウン・モードを選択するには、DRV8424/25 の ENABLE ピンをハイ・インピーダンスにする必要があります。このモードでは、OCP イベントの後、出力がディセーブルされ、nFAULT ピンが Low に駆動されます。OCP 条件が解消すると、nSLEEP リセット・パルスが印加された後、または電源を切って再投入した後、通常動作に復帰します。

#### 7.3.11.3.2 自動リトライ

自動リトライ・モードを選択するには、DRV8424/25 の ENABLE ピンを HIGH (>2.7V) にする必要があります。このモードでは、OCP イベントの後、出力がディセーブルされ、nFAULT ピンが Low に駆動されます。t<sub>RETRY</sub> 時間が経過し、フォルト条件が解消した後、自動的に通常動作に復帰します (モータ・ドライバの動作と nFAULT の解放)。

## 7.3.11.4 サーマル・シャットダウン (OTSD)

デバイス温度がサーマル・シャットダウン限界値 (Totso) を超えると、H ブリッジのすべての MOSFET がディセーブルされ、nFAULT ピンが Low に駆動されます。この条件の間、チャージ・ポンプはディセーブルされます。サーマル・シャットダウン保護は 2 つのモード (ラッチド・シャットダウンと自動リトライ) で動作できます。この動作モードは、実行中に変更できます。

# 7.3.11.4.1 ラッチド・シャットダウン

ラッチド・シャットダウン・モードを選択するには、DRV8424/25 の ENABLE ピンをハイ・インピーダンスにする必要があります。このモードでは、OTSD イベントの後、関連する出力がディセーブルされ、nFAULT ピンが Low に駆動されます。接合部温度が、過熱スレッショルド限界値からヒステリシスを引いた値 (Totsp - Thys\_otsp) を下回った後に、nSLEEP リセット・パルスが印加された後、または電源を切って再投入した後、通常動作に復帰します。

#### 7.3.11.4.2 自動リトライ

自動リトライ・モードを選択するには、DRV8424/25 の ENABLE ピンを HIGH (>2.7V) にする必要があります。このモードでは、OTSD イベントの後、すべての出力がディセーブルされ、nFAULT ピンが Low に駆動されます。接合部温度が、過熱スレッショルド限界値からヒステリシスを引いた値 ( $T_{OTSD} - T_{HYS\_OTSD}$ ) を下回ると、通常動作に復帰します (モータ・ドライバの動作と nFAULT ラインの解放)。

#### 7.3.11.5 フォルト条件のまとめ

#### 表 7-10. フォルト条件のまとめ

| フォルト                | 条件                      | 構成 | 異常通知   | H ブリッジ     | チャージ・<br>ポンプ | インデクサ  | ロジック                                  | 復帰                         |

|---------------------|-------------------------|----|--------|------------|--------------|--------|---------------------------------------|----------------------------|

| VM 低電圧 (UVLO)       | VM < V <sub>UVLO</sub>  | _  | nFAULT | ディセーブル     | ディセーブル       | ディセーブル | リセット<br>(V <sub>DVDD</sub> <<br>3.9V) | 自動:VM > V <sub>UVLO</sub>  |

| VCP 低電圧検出<br>(CPUV) | VCP < V <sub>CPUV</sub> | _  | nFAULT | ディセーブ<br>ル | 動作           | 動作     | 動作                                    | 自動:VCP > V <sub>CPUV</sub> |

#### 表 7-10. フォルト条件のまとめ (continued)

| フォルト                                          | 条件                                  | 構成                                | 異常通知   | H ブリッジ     | チャージ・<br>ポンプ | インデクサ | ロジック | 復帰                                                               |

|-----------------------------------------------|-------------------------------------|-----------------------------------|--------|------------|--------------|-------|------|------------------------------------------------------------------|

| 過電流 (OCP) I <sub>OUT</sub> > I <sub>OCP</sub> | I <sub>OUT</sub> > I <sub>OCP</sub> | <b>ENABLE =</b><br>ハイ・インピ<br>ーダンス | nFAULT | ディセーブル     | 動作           | 動作    | 動作   | ラッチ                                                              |

|                                               |                                     | ENABLE =                          | nFAULT | ディセーブ<br>ル | 動作           | 動作    | 動作   | 自動リトライ:t <sub>RETRY</sub>                                        |

| サーマル・シャットダウン (OTSD)                           | T <sub>J</sub> > T <sub>TSD</sub>   | ENABLE =<br>ハイ・インピ<br>ーダンス        | nFAULT | ディセーブル     | ディセーブル       | 動作    | 動作   | ラッチ                                                              |

|                                               |                                     | ENABLE =                          | nFAULT | ディセーブ<br>ル | ディセーブ<br>ル   | 動作    | 動作   | 自動:T <sub>J</sub> < T <sub>OTSD</sub> -<br>T <sub>HYS_OTSD</sub> |

# 7.4 デバイスの機能モード

# 7.4.1 スリープ・モード (nSLEEP = 0)

DRV8424/25 の状態は nSLEEP ピンで制御されます。nSLEEP ピンが Low になると、DRV8424/25 は低消費電力の スリープ・モードに移行します。スリープ・モードでは、すべての内蔵 MOSFET がディセーブルされ、チャージ・ポンプが ディセーブルされます。nSLEEP ピンでの立ち下がりエッジの後、t<sub>SLEEP</sub> 時間が経過すると、デバイスはスリープ・モード に移行します。nSLEEP ピンが High になると、DRV8424/25 は自動的にスリープから復帰します。t<sub>WAKE</sub> 時間が経過すると、デバイスは入力可能な状態になります。

## 7.4.2 ディセーブル・モード (nSLEEP = 1、ENABLE = 0)

ENABLE ピンは、DRV8424/25 をイネーブルまたはディセーブルにするために使用されます。ENABLE ピンが Low になると、出力ドライバは無効化され、ハイ・インピーダンス状態になります。

# 7.4.3 動作モード (nSLEEP = 1、ENABLE = ハイ・インピーダンス / 1)

nSLEEP ピンが High、ENABLE ピンがハイ・インピーダンスまたは High、VM > UVLO のすべてに該当する場合、本デバイスはアクティブ・モードに入ります。 t<sub>WAKE</sub> 時間が経過すると、デバイスは入力可能な状態になります。

#### 7.4.4 nSLEEP リセット・パルス

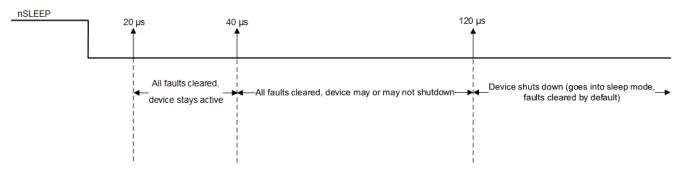

ラッチされたフォルトは短い nSLEEP パルスでクリアできます。このパルス幅は 20μs より長く 40μs より短い必要があります。 nSLEEP が 40μs より長く 120μs より短い間 Low である場合、フォルトはクリアされますが、本デバイスはタイミング図で示すように、シャットダウンする場合としない場合があります (図 7-21 を参照)。このリセット・パルスはチャージ・ポンプの状態にもその他の機能ブロックの状態にも影響を与えません。

図 7-21. nSLEEP リセット・パルス

#### 7.4.5 機能モードのまとめ

表 7-11 に、機能モードのまとめを示します。

# 表 7-11. 機能モードのまとめ

| 条件       |                 | 構成                                                         | H ブリッジ | DVDD レギュレ<br>ータ | チャージ・ポンプ | インデクサ  | ロジック   |

|----------|-----------------|------------------------------------------------------------|--------|-----------------|----------|--------|--------|

| スリープ・モード | 4.5V < VM < 33V | nSLEEPピン<br>= 0                                            | ディセーブル | ディセーブル          | ディセーブル   | ディセーブル | ディセーブル |

| 動作       | 4.5V < VM < 33V | nSLEEP ピン<br>= 1<br>ENABLE ピン<br>= 1 またはハ<br>イ・インピーダン<br>ス | 動作     | 動作              | 動作       | 動作     | 動作     |

| ディセーブル   | 4.5V < VM < 33V | nSLEEP ピン<br>= 1<br>ENABLE ピン<br>= 0                       | ディセーブル | 動作              | 動作       | 動作     | 動作     |

# 8 アプリケーションと実装

#### 注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

# 8.1 アプリケーション情報

DRV8424 はバイポーラ・ステッピング制御で使用されます。

# 8.2 代表的なアプリケーション

次の設計手順で DRV8428 を構成できます。

図 8-1. 代表的なアプリケーション回路図

# 8.2.1 設計要件

表 8-1 に、代表的なアプリケーションの設計入力パラメータを示します。

表 8-1. 設計パラメータ

| 設計パラメータ | 略号             | 値の例    |

|---------|----------------|--------|

| 電源電圧    | VM             | 24V    |

| モータ巻線抵抗 | R <sub>L</sub> | 1.5Ω/相 |

| 表              | 8-1. 設計パラメータ (continued) |   |

|----------------|--------------------------|---|

| <b>設計パラメータ</b> | 略号                       | 1 |

| - カ光炉 ひょげりかいつ  | 1.                       | Τ |

|                  | • (             |           |

|------------------|-----------------|-----------|

| 設計パラメータ          | 略号              | 値の例       |

| モータ巻線インダクタンス     | LL              | 2mH/相     |

| モータ・フルステップ角      | $\theta_{step}$ | 1.8°/ステップ |

| 目標マイクロステッピング・レベル | n <sub>m</sub>  | 1/8 ステップ  |

| 目標モータ速度          | V               | 18.75rpm  |

| 目標フルスケール電流       | I <sub>ES</sub> | 2A        |

## 8.2.2 詳細な設計手順

## 8.2.2.1 ステッピング・モータの速度

DRV8424/25 を構成するには、まず、モータ速度とマイクロステッピング・レベルの目標値が必要です。対象とするアプリ ケーションで一定速度が必要な場合、周波数  $f_{\text{step}}$  の矩形波を STEP ピンに印加する必要があります。目標モータ速度 が高すぎる場合、モータは回転しません。モータが目標速度に対応できることを確認してください。モータ速度 (v)、マイク ロステッピング・レベル  $(n_m)$ 、モータのフルステップ角  $(\theta_{sten})$  の目標値に対応する  $f_{sten}$  を計算するには 式 1 を使用しま す。

$$f_{\text{step}} \text{ (steps / s)} = \frac{\text{v (rpm)} \times 360 (^{\circ} / \text{rot})}{\theta_{\text{step}} (^{\circ} / \text{step}) \times n_{\text{m}} \text{ (steps / microstep)} \times 60 \text{ (s / min)}}$$

(1)

$\theta_{step}$  値は、ステッピング・モータのデータシートまたはモータそのものに記載されています。 たとえば、1/8 マイクロステッ プ・モードで 18.75rpm という目標に対して、本アプリケーションのモータは 1.8°/step で回転する必要があります。式 1 を使用すると、 $f_{step}$  は 500Hz として計算できます。

マイクロステッピング・レベルは MO および M1 ピンで設定され、表 8-2 に示す設定のいずれかにできます。 マイクロステ ッピング・レベルが高いほどモータの動きは円滑になり、可聴ノイズは小さくなりますが、同じモータ速度を実現するのによ り高い  $f_{\text{step}}$  を必要とします。

表 8-2. マイクロステッピング・インデクサの設定

| 我 0-2. マイプロスノブピング インブブラの政化 |                           |                          |  |  |  |  |  |  |  |

|----------------------------|---------------------------|--------------------------|--|--|--|--|--|--|--|

| MODE0                      | MODE1                     | ステップ・モード                 |  |  |  |  |  |  |  |

| 0                          | 0                         | 100% 電流によるフルステップ (2 相励起) |  |  |  |  |  |  |  |

| 0                          | 330kΩ を<br>GND との<br>間に接続 | 71% 電流によるフルステップ (2 相励起)  |  |  |  |  |  |  |  |

| 1                          | 0                         | 非真円 <b>1/2</b> ステップ      |  |  |  |  |  |  |  |

| ハイ・イン<br>ピーダンス             | 0                         | 1/2 ステップ                 |  |  |  |  |  |  |  |

| 0                          | 1                         | 1/4 ステップ                 |  |  |  |  |  |  |  |

| 1                          | 1                         | 1/8 ステップ                 |  |  |  |  |  |  |  |

| ハイ・イン<br>ピーダンス             | 1                         | 1/16 ステップ                |  |  |  |  |  |  |  |

| 0                          | ハイ・イン<br>ピーダンス            | 1/32 ステップ                |  |  |  |  |  |  |  |

| ハイ・イン<br>ピーダンス             |                           | 1/64 ステップ                |  |  |  |  |  |  |  |

|                            | ハイ・イン<br>ピーダンス            | 1/128 ステップ               |  |  |  |  |  |  |  |

| 1                          | ハイ・イン<br>ピーダンス            | 1/256 ステップ               |  |  |  |  |  |  |  |

## 8.2.2.2 電流レギュレーション

出力負荷が VM 電源に接続されている場合、負荷電流を  $I_{TRIP}$  レベルに調整できます。 OUT1 および OUT2 出力の  $I_{TRIP}$  電流レベルは VREF ピンによって制御され、 OUT3 および OUT4 出力の  $I_{TRIP}$  レベルは VREF ピンによって制御されます。  $I_{TRIP}$  電流は、  $I_{TRIP}$  (A) = VREF (V) / 1.32 (V/A) として計算できます。 VREF 電圧は、 DVDD ピンからグランド に分圧抵抗を接続することでプログラミングできます。 両方の VREF ピンを接続して、 4 つの出力チャネルすべてに対して同じ ITRIP 電流をプログラムできます。

## 8.2.2.3 ディケイ・モード

表 7-7 に示すように、本デバイスは 6 種類のディケイ・モードをサポートしています。モータ巻線電流が電流チョッピング・スレッショルド ( $I_{TRIP}$ ) に達すると、DRV8424/25 は  $t_{OFF}$  の 6 つのディケイ・モードのいずれかに巻線を配置します。  $t_{OFF}$  が経過すると、新たなドライブフェーズが開始します。

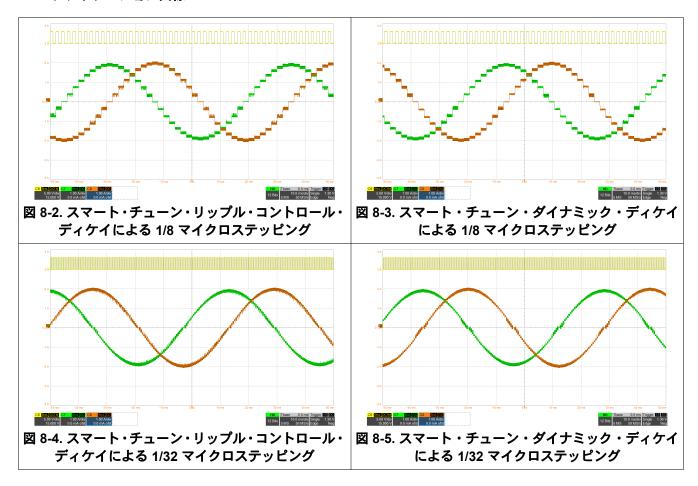

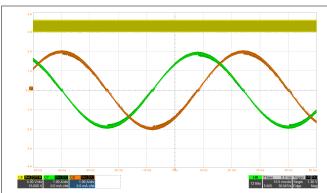

## 8.2.3 アプリケーション曲線

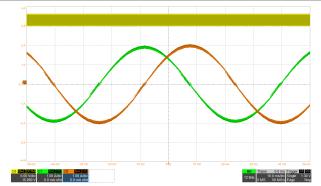

ディケイによる 1/256 マイクロステッピング

図 8-6. スマート・チューン・リップル・コントロール・ 図 8-7. スマート・チューン・ダイナミック・ディケイ による 1/256 マイクロステッピング

## 8.2.4 熱に関連するアプリケーション

このセクションでは、デバイスの消費電力の計算と接合部温度の概算について説明します。

## 8.2.4.1 消費電力との関係

全消費電力は主な 3 つの要素 (導通損失 ( $P_{COND}$ )、スイッチング損失 ( $P_{SW}$ )、静止消費電流による電力損失 ( $P_{Q}$ )) で構成されます。

#### 8.2.4.1.1 導通損失

フル・ブリッジに接続されたモータの電流経路は一方のハーフ・ブリッジのハイサイド FET と他方のハーフ・ブリッジのローサイド FET を通ります。導通損失 ( $P_{COND}$ ) は、式 2 のように、モータの RMS 電流 ( $I_{RMS}$ )、ハイサイド・オン抵抗 ( $R_{DS(ONH)}$ )、ローサイド・オン抵抗 ( $R_{DS(ONH)}$ ) で決まります。

$$P_{COND} = 2x (I_{RMS})^2 x (R_{DS(ONH)} + R_{DS(ONL)})$$

(2)

表 8-2 で説明する代表的なアプリケーションの導通損失は式 3 のように計算されます。

$$P_{COND} = 2x (I_{RMS})^2 x (R_{DS(ONH)} + R_{DS(ONL)}) = 2x (2A / \sqrt{2})^2 x (0.165\Omega + 0.165\Omega) = 1.32$$

(3)

注

この電力の計算値は、ハイサイド FET とローサイド FET のオン抵抗に大きな影響を与えるデバイス温度に大きく影響されます。より精密に計算するには、FET のオン抵抗の温度依存性を考慮します。

## 8.2.4.1.2 スイッチング損失

PWM スイッチング周波数に起因する電力損失はスルーレート ( $t_{SR}$ )、電源電圧、モータの RMS 電流、PWM スイッチング周波数で決まります。各 H ブリッジの立ち上がり時間のスイッチング損失と立ち下がり時間のスイッチング損失は式 4 および式 5 のように計算されます。

$$P_{SW RISE} = 0.5x V_{VM} \times I_{RMS} \times t_{RISE PWM} \times f_{PWM}$$

(4)

$$P_{SW FALL} = 0.5x V_{VM} \times I_{RMS} \times t_{FALL PWM} \times f_{PWM}$$

(5)

$t_{RISE\_PWM}$  と  $t_{FALL\_PWM}$  はどちらも  $V_{VM}/t_{SR}$ .として近似されます。各種パラメータの値を代入した後、30kHz PWM 周波数を仮定すると、各 H ブリッジのスイッチング損失は以下のように計算されます。

$$P_{SW RISE} = 0.5x 24V \times (2A / \sqrt{2}) \times (24V / 240V/\mu s) \times 30kHz = 0.051W$$

(6)

$$P_{SW\_FALL} = 0.5x \ 24V \ x \ (2A \ / \ \sqrt{2}) \ x \ (24V \ / \ 240V \ / \mu s) \ x \ 30kHz = 0.051W$$

(7)

ステッピング・モータ・ドライバの全スイッチング損失 ( $P_{SW}$ ) は立ち上がり時間のスイッチング損失 ( $P_{SW\_RISE}$ ) と立ち下がり時間のスイッチング損失 ( $P_{SW\_FALL}$ ) の合計の 2 倍として以下のように計算されます。

$$P_{SW} = 2x (P_{SW RISE} + P_{SW FALL}) = 2x (0.051W + 0.051W) = 0.204W$$

(8)

注

立ち上がり時間 (t<sub>RISE</sub>) と立ち下がり時間 (t<sub>FALL</sub>) はスルーレート (t<sub>SR</sub>) の標準値に基づいて計算されます。このパラメータは、電源電圧、温度、デバイス間のばらつきに基づいて変化することが予想されます。

スイッチング損失は PWM スイッチング周波数に正比例します。アプリケーションでの PWM 周波数は電源電圧、モータ・コイルのインダクタンス、逆起電圧、オフ時間 (スマート・チューン・リップル・コントロール・ディケイ・モードの場合はリップル電流) で決まります。

## 8.2.4.1.3 静止電流による消費電力

電源によって消費される静止電流による消費電力は以下のように計算されます。

$$P_{Q} = V_{VM} \times I_{VM}$$

(9)

値を代入すると、静止電力損失は以下のように計算されます。

$$P_Q = 24V \times 5mA = 0.12W$$

(10)

注

静止電力損失は、動作電源電流 (I<sub>VM</sub>、標準値) を使用して計算されます。この動作電源電流は電源電圧、温度、デバイス間のばらつきによって決まります。

#### 8.2.4.1.4 全消費電力

全消費電力 (P<sub>TOT</sub>) は導通損失、スイッチング損失、静止電力損失の合計として式 11 に示すのように計算されます。

$$P_{TOT} = P_{COND} + P_{SW} + P_{Q} = 1.32W + 0.204W + 0.12W = 1.644W$$

(11)

## 8.2.4.2 デバイスの接合部温度の概算

周囲温度  $T_A$ 、全消費電力  $(P_{TOT})$  の場合、接合部温度  $(T_J)$  は  $T_J = T_A + (P_{TOT} \times R_{\theta,IA})$  で計算されます。

JEDEC 規格の 4 層 PCB を考慮すれば、接合部から周囲への熱抵抗 (R<sub>θJA</sub>) は、HTSSOP パッケージの場合 31℃/W、VQFN パッケージの場合 40.7℃/W です。

25°C の周囲温度を仮定すると、HTSSOP パッケージの接合部温度は以下のように計算されます。

$$T_{LI} = 25^{\circ}\text{C} + (1.644\text{W} \times 31^{\circ}\text{C/W}) = 75.96^{\circ}\text{C}$$

(12)

VQFN パッケージの接合部温度は以下のように計算されます。

$$T_{IJ} = 25^{\circ}\text{C} + (1.644\text{W} \times 40.7^{\circ}\text{C/W}) = 91.91^{\circ}\text{C}$$

(13)

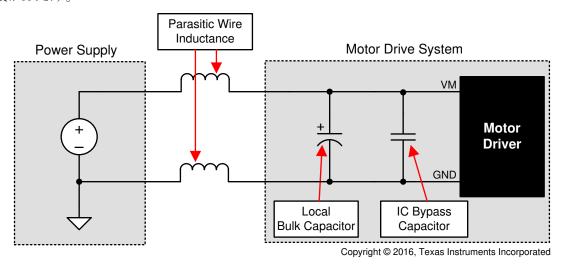

# 9 電源に関する推奨事項

DRV8424/25 は、4.5V~33V の入力電圧源 (VM) 範囲で動作するように設計されています。 VM 定格の  $0.01\mu F$  セラミック・コンデンサを、DRV8424/25 にできるだけ近付けて各 VM ピンに配置する必要があります。 また、バルク・コンデンサを VM に接続する必要があります。

# 9.1 バルク・コンデンサ

適切なローカル・バルク・コンデンサを使用することは、モータ駆動システムの設計で重要な要素の 1 つです。一般に、バルク容量が大きいほど利点がありますが、コストと物理的なサイズが増加します。

必要なローカル容量値は、次のようなさまざまな要因で決まります。

- モータ・システムが必要とする最大電流

- 電源容量(電流供給能力)

- 電源とモータ・システムの間の寄生インダクタンスの大きさ

- 許容される電圧リップル

- 使用するモータの種類 (ブラシ付き DC、ブラシレス DC、ステッピング)

- モータのブレーキ方式。

電源とモータ駆動システムの間のインダクタンスにより、電源からの電流が変化できる割合が制限されます。ローカル・バルク容量が小さすぎる場合、システムはモータからの過剰な電流要求やダンプによる電圧変動の影響を受けます。十分なバルク容量を使うことで、モータの電圧は安定し、大電流を素早く供給できます。

データシートには一般に、推奨値が記載されていますが、バルク・コンデンサの容量が適切かどうかを判断するには、システム・レベルのテストが必要です。

モータが電源にエネルギーを伝達する場合のマージンを確保するため、バルク・コンデンサの定格電圧は動作電圧より高くする必要があります。

図 9-1. 外部電源を使用したモータ駆動システムの構成例

# 10 レイアウト

# 10.1 レイアウトのガイドライン

推奨する VM 定格で 0.01μF の低 ESR セラミック・バイパス・コンデンサを使用して、VM ピンを PGND にバイパスする 必要があります。このコンデンサは VM ピンのできるだけ近くに配置し、太いトレースまたはグランド・プレーンでデバイス の PGND ピンに接続する必要があります。

VM 定格のバルク・コンデンサを使用して、VM ピンを PGND にバイパスする必要があります。この部品には電解コンデンサが使用できます。

低 ESR セラミック・コンデンサを CPL ピンと CPH ピンの間に配置する必要があります。 VM 電圧定格の 0.022μF を推奨します。 この部品はピンにできるだけ近付けて配置します。

低 ESR セラミック・コンデンサを VM ピンと VCP ピンの間に配置する必要があります。16V 定格の 0.22µF を推奨します。この部品はピンにできるだけ近付けて配置します。

低 ESR セラミック・コンデンサを使用して DVDD ピンをグランドにバイパスします。 6.3V 定格の 0.47μF を推奨します。 このバイパス・コンデンサはピンにできるだけ近付けて配置します。

サーマル・パッドはシステム・グランドに接続する必要があります。

## 10.2 レイアウト例

図 10-1. HTSSOP のレイアウト例

図 10-2. QFN のレイアウト例

# 11 デバイスおよびドキュメントのサポート

## 11.1 関連リンク

次の表に、クイック・アクセス・リンクを示します。カテゴリには、技術資料、サポートとコミュニティ・リソース、ツールとソフトウェア、およびご注文へのクイック・アクセスが含まれます。

- テキサス・インスツルメンツ、『ステッパ・モーターの可聴ノイズを低減する方法』アプリケーション・レポート

- テキサス・インスツルメンツ、『動作の滑らかさと精度を向上させる方法』アプリケーション・レポート

- テキサス・インスツルメンツ、『DRV8xxx によるユニポーラ・ステッパ・モーターの駆動方法』アプリケーション・レポート

- テキサス・インスツルメンツ、『モータ・ドライバ消費電力の計算』アプリケーション・レポート (英語)

- テキサス・インスツルメンツ、『電流再循環および減衰モード』アプリケーション・レポート(英語)

- テキサス・インスツルメンツ、『モータ・ドライバの電流定格の理解』アプリケーション・レポート (英語)

- テキサス・インスツルメンツ、『モータ・ドライブのレイアウト・ガイド』アプリケーション・レポート

## 表 11-1. 関連リンク

| 製品      | プロダクト・フォルダ | ご注文はこちら  | 技術資料     | ツールとソフトウェア | サポートとコミュニティ |

|---------|------------|----------|----------|------------|-------------|

| DRV8424 | こちらをクリック   | こちらをクリック | こちらをクリック | こちらをクリック   | こちらをクリック    |

| DRV8425 | こちらをクリック   | こちらをクリック | こちらをクリック | こちらをクリック   | こちらをクリック    |

# 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

# 11.3 コミュニティ・リソース

## 11.4 商標

すべての商標は、それぞれの所有者に帰属します。

## 11.5 静電気放電に関する注意事項

# 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

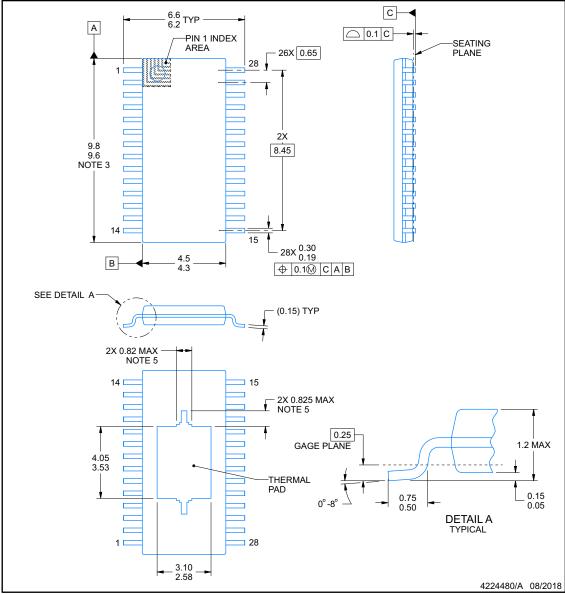

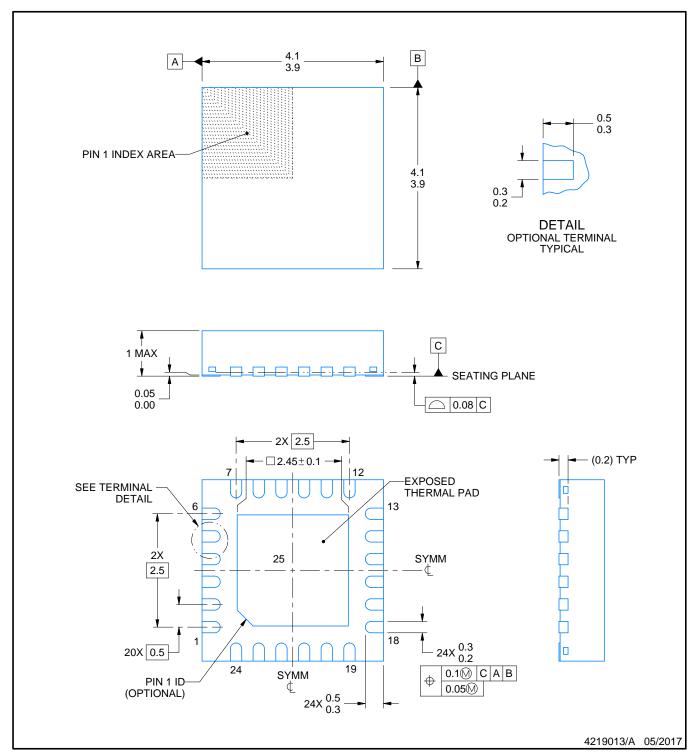

**PWP0028M**

## PACKAGE OUTLINE

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

## NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing

- per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

- 5. Features may differ or may not be present.

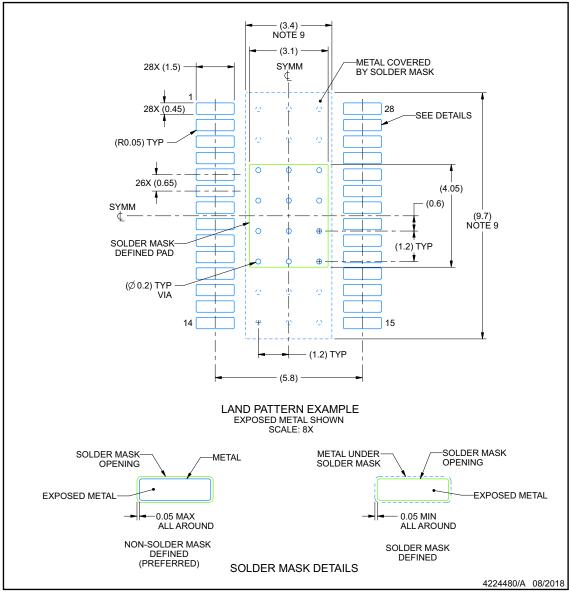

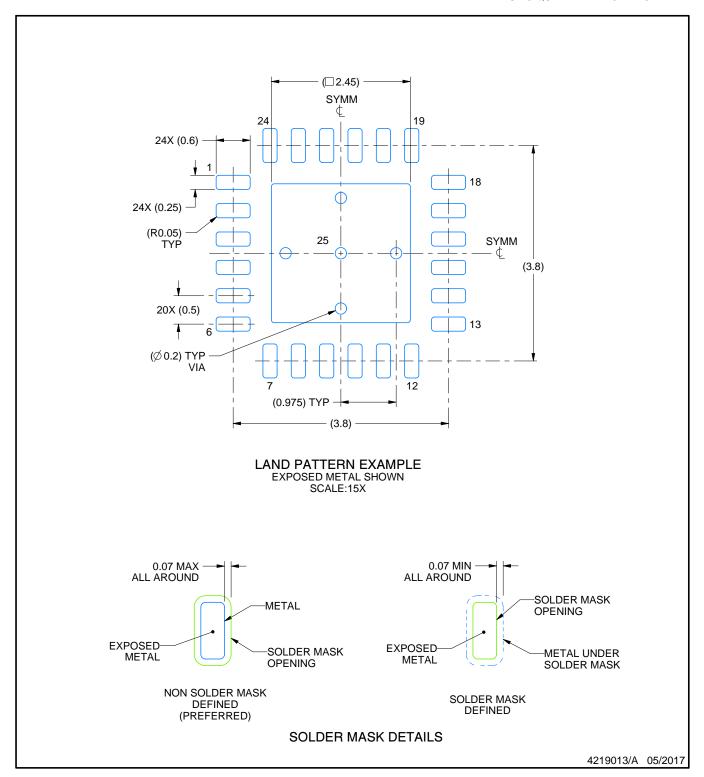

## **EXAMPLE BOARD LAYOUT**

# **PWP0028M**

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged

- or tented.

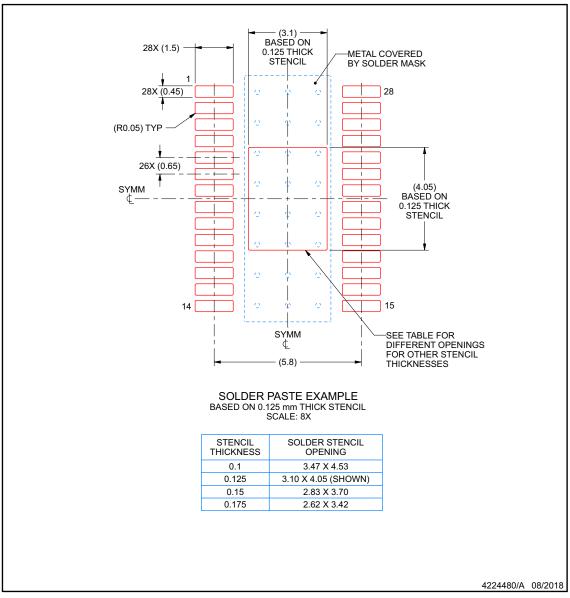

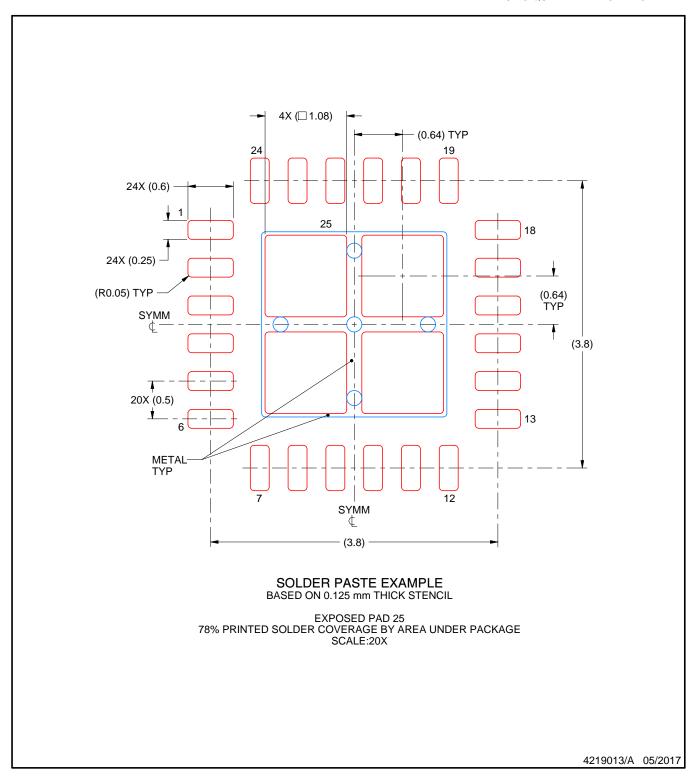

## **EXAMPLE STENCIL DESIGN**

# **PWP0028M**

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- design recommendations.

12. Board assembly site may have different recommendations for stencil design.

www.ti.com 12-Apr-2023

### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| DRV8424PWPR      | ACTIVE     | HTSSOP       | PWP                | 28   | 2500           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | DRV8424                 | Samples |

| DRV8424RGER      | ACTIVE     | VQFN         | RGE                | 24   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | DRV<br>8424             | Samples |

| DRV8425PWPR      | ACTIVE     | HTSSOP       | PWP                | 28   | 2500           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | DRV8425                 | Samples |

| DRV8425RGER      | ACTIVE     | VQFN         | RGE                | 24   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | DRV<br>8425             | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

# PACKAGE OPTION ADDENDUM

www.ti.com 12-Apr-2023

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

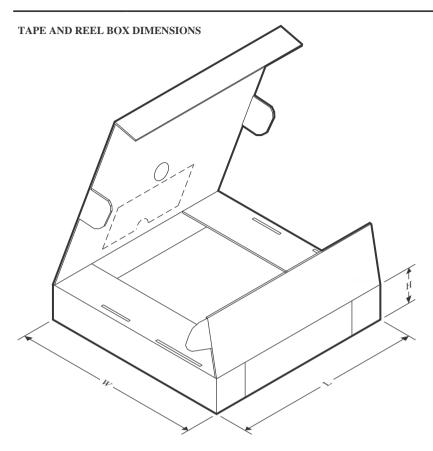

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

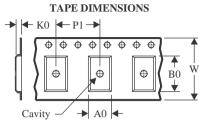

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

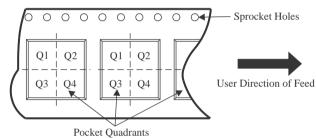

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV8424PWPR | HTSSOP          | PWP                | 28 | 2500 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

| DRV8424RGER | VQFN            | RGE                | 24 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| DRV8425PWPR | HTSSOP          | PWP                | 28 | 2500 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

| DRV8425RGER | VQFN            | RGE                | 24 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

www.ti.com 3-Jun-2022

## \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV8424PWPR | HTSSOP       | PWP             | 28   | 2500 | 356.0       | 356.0      | 35.0        |

| DRV8424RGER | VQFN         | RGE             | 24   | 3000 | 367.0       | 367.0      | 35.0        |

| DRV8425PWPR | HTSSOP       | PWP             | 28   | 2500 | 356.0       | 356.0      | 35.0        |

| DRV8425RGER | VQFN         | RGE             | 24   | 3000 | 367.0       | 367.0      | 35.0        |

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4204104/H

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

4.4 x 9.7, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated