**DRV8952** JAJSL44 - MARCH 2023

# DRV8952 電流検出出力を持つ 4 チャネル・ハーフブリッジ・ドライバ

### 1 特長

- 4 チャネルのハーフブリッジ・ドライバ

- 各ハーフブリッジの独立制御

- 4.5V~55V の動作電源電圧範囲

- 低い R<sub>DS(ON)</sub>:FET ごとに **50mΩ** (24V、25℃)

- 大電流能力:

- DDW パッケージ:出力ごとに最大 5A

- PWP パッケージ: 出力ごとに最大 4A

- さまざまな種類の負荷を駆動可能

- 最大4つのソレノイドまたはバルブ

- 1つのステッパ・モーター

- 2 つのブラシ付き DC モーター

- 1 つまたは 2 つの熱電冷却器 (TEC)

- 1 つの 3 相ブラシレス DC モーター

- 1 つの 3 相永久磁石同期モーター (PMSM)

- 電流検出およびレギュレーション機能を内蔵

- 複数のハイサイド MOSFET 間にまたがる電流検

- 各ハーフブリッジ (DDW) の IPROPI 出力

- 最大電流時に 5% の検出精度

- オプションの外部検出抵抗

- 次のデバイスとピン互換

- DRV8955PWP:48V、4 チャネル・ハーフブリッジ・ ドライバ

- DRV8962DDW:65V、4 チャネル・ハーフブリッジ・ ドライバ

- 独立したロジック電源電圧 (VCC) (DDW)

- 出力立ち上がり/立ち下がり時間をプログラム可能 (DDW)

- フォルトからの回復方法をプログラム可能 (DDW)

- 1.8V、3.3V、5.0Vのロジック入力をサポート

- 低消費電流のスリープ・モード (3µA)

- 保護機能

- VM 低電圧誤動作防止 (UVLO)

- チャージ・ポンプ低電圧検出 (CPUV)

- 過電流保護 (OCP)

- サーマル・シャットダウン (OTSD)

- フォルト条件出力 (nFAULT)

## 2 アプリケーション

- ファクトリ・オートメーション、ステッパ・ドライブ、ロボット

- 医療用画像処理、診断、および機器

- 舞台照明

- PLC

- TECドライバ

- BLDC モーター・モジュール

- ブラシ付き DC およびステッパ・モーター・ドライバ

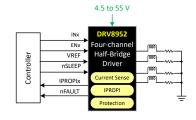

### 3 概要

DRV8952 は広い電圧範囲に対応した大電力、4 チャネ ル、ハーフブリッジ・ドライバで、さまざまな産業用アプリケ ーションに適しています。このデバイスは最大 **55V** の電源 電圧をサポートし、オン抵抗が  $50m\Omega$  の MOSFET を内 蔵しているため、DDW パッケージでは最大 5A、PWP パ ッケージでは最大 4A の電流を出力ごとに供給できます。

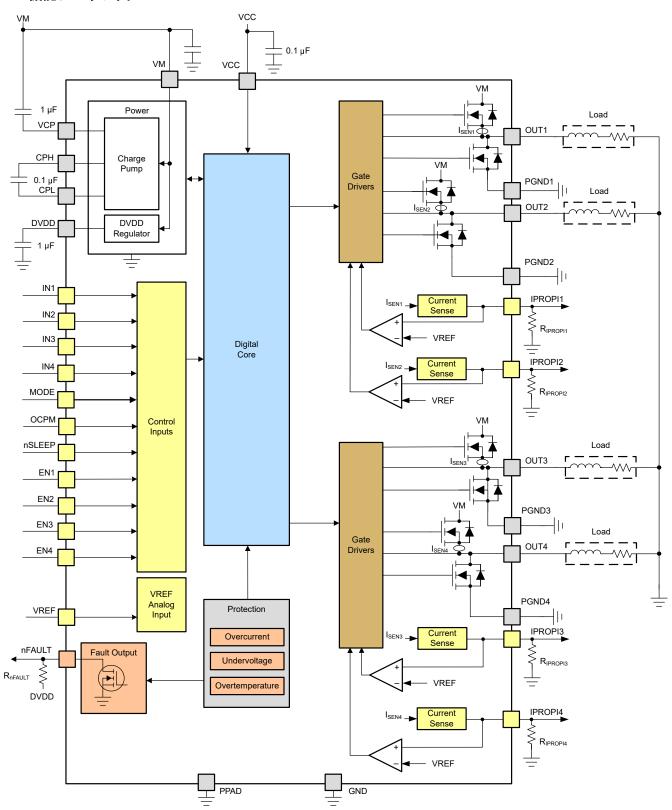

このデバイスは、最大4つのソレノイドまたはバルブ、1つ のステッパ・モーター、2 つのブラシ付き DC モーター、1 つの BLDC または PMSM モーター、および最大 2 つの 熱電冷却器 (ペルチェ素子) の駆動に使用できます。この デバイスの出力段は、4 つの独立したハーフブリッジとして 構成された N チャネル・パワー MOSFET、チャージ・ポン プ・レギュレータ、電流検出およびレギュレーション回路、 電流検出出力、保護回路で構成されます。

ハイサイド MOSFET の両端に電流検出機能が統合され ているため、負荷を出力からグランドに接続したときに電 流をレギュレートできます。可変の外部電圧リファレンス (VREF) により、電流レギュレーションの制限を設定できま す。DDW パッケージにおいて、このデバイスには **4** つの 比例電流出力ピンがあり、各ハーフブリッジ・ハイサイド FET に 1 つずつ接続されています。 オプションの外部検 出抵抗を、PGND ピンからシステム・グランドに接続するこ とができます。

低消費電力のスリープ・モードにより、非常に低い静止電 流を実現できます。保護機能として、電源低電圧誤動作 防止 (UVLO)、チャージ・ポンプ低電圧検出 (CPUV)、出 力過電流検出 (OCP)、デバイス過熱検出 (OTSD) が内 蔵されています。

### デバイス情報 <sup>(1)</sup>

| 部品番号        | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |

|-------------|----------------------|---------------|

| DRV8952DDWR | HTSSOP (44)          | 14mm x 6.1mm  |

| DRV8952PWPR | HTSSOP (28)          | 9.7mm × 4.4mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

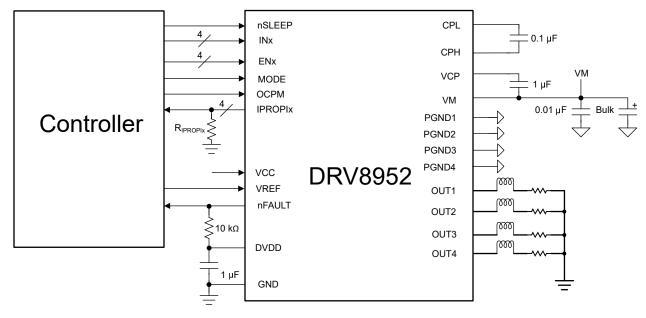

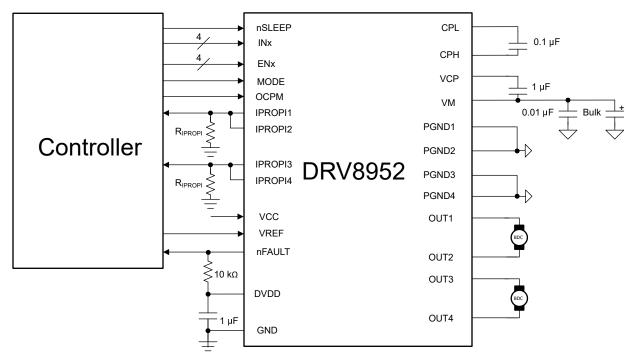

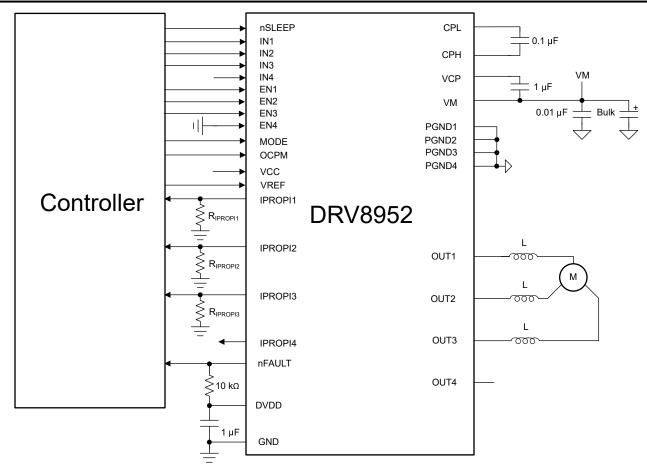

DRV8952 の概略回路図

## 目次

| 1 特長1               | 7.10 保護回路              | 20               |

|---------------------|------------------------|------------------|

| 2 アプリケーション1         | 7.11 デバイスの機能モード        | 22               |

| 3 概要1               | 8 アプリケーションと実装          | <mark>2</mark> 4 |

| 4 改訂履歴2             | 8.1 アプリケーション情報         |                  |

| 5 ピン構成および機能3        | 9 パッケージの熱に関する考慮事項      | 37               |

| 6 仕様6               | 9.1 DDW パッケージ          |                  |

| 6.1 絶対最大定格6         | 10 電源に関する推奨事項          | 40               |

| 6.2 ESD 定格6         | 10.1 バルク容量             | 40               |

| 6.3 推奨動作条件6         | 10.2 電源                | 40               |

| 6.4 熱に関する情報7        | 11 レイアウト               | 41               |

| 6.5 電気的特性7          | 11.1 レイアウトのガイドライン      | 41               |

| 6.6 代表的な特性10        | 11.2 PCB 材料に関する推奨事項    | 41               |

| 7 詳細説明12            | 11.3 熱に関する注意事項         | 41               |

| 7.1 概要12            | 12 デバイスおよびドキュメントのサポート  | 42               |

| 7.2 機能ブロック図13       | 12.1 関連資料              | 42               |

| 7.3 機能説明13          | 12.2ドキュメントの更新通知を受け取る方法 | 42               |

| 7.4 独立のハーフブリッジ動作14  | 12.3 サポート・リソース         | 42               |

| 7.5 電流検出とレギュレーション15 | 12.4 商標                | 42               |

| 7.6 チャージ・ポンプ19      | 12.5 静電気放電に関する注意事項     | 42               |

| 7.7 リニア電圧レギュレータ19   | 12.6 用語集               | 42               |

| 7.8 VCC 電圧電源20      | 13 メカニカル、パッケージ、および注文情報 | 43               |

| 7.9 ロジック・レベル・ピンの図20 | 13.1 テープおよびリール情報       | 50               |

|                     |                        |                  |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付         | リビジョン | 注  |

|------------|-------|----|

| 2023 年 3 月 | *     | 初版 |

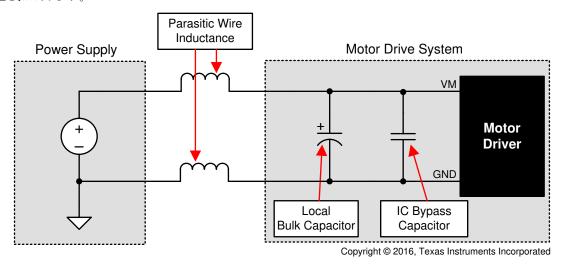

### 5 ピン構成および機能

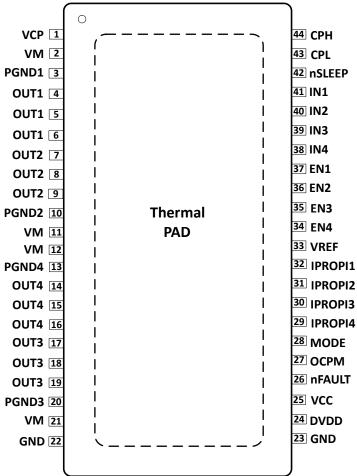

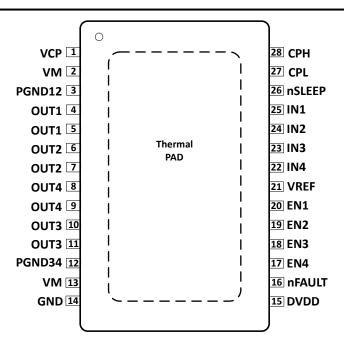

DRV8952 は、熱的に強化された 44 ピン HTSSOP (DDW) および 28 ピン HTSSOP (PWP) パッケージで供給されます。

図 5-1. DDW パッケージ、上面図

図 5-2. PWP パッケージ (28 ピン HTSSOP)、上面図

|         | ピン            |      | AC. W. | av pr                                                                                |

|---------|---------------|------|--------|--------------------------------------------------------------------------------------|

| 名称      | DDW           | PWP  | 種類     | 説明                                                                                   |

| VCP     | 1             | 1    | 電力     | チャージ・ポンプの出力。X7R、1μF、16V セラミック・コンデンサを VCP と VM との間に接続します。                             |

| VM      | 2, 11, 12, 21 | 2、13 | 電力     | 電源。モーターの電源電圧に接続し、VM 定格の 2 つの 0.01µF セラミック・コンデンサと 1 つのバルク・コンデンサを使用して、PGND ピンにバイパスします。 |

| IPROPI1 | 32            | -    | 出力     | ハーフブリッジ 1 の電流検出出力。                                                                   |

| IPROPI2 | 31            | -    | 出力     | ハーフブリッジ 2 の電流検出出力。                                                                   |

| IPROPI3 | 30            | -    | 出力     | ハーフブリッジ3の電流検出出力。                                                                     |

| IPROPI4 | 29            | -    | 出力     | ハーフブリッジ 4 の電流検出出力。                                                                   |

| EN1     | 37            | 20   | 入力     | ハーフブリッジ 1 のイネーブル入力。                                                                  |

| EN2     | 36            | 19   | 入力     | ハーフブリッジ 2 のイネーブル入力。                                                                  |

| EN3     | 35            | 18   | 入力     | ハーフブリッジ3のイネーブル入力。                                                                    |

| EN4     | 34            | 17   | 入力     | ハーフブリッジ 4 のイネーブル入力。                                                                  |

| IN1     | 41            | 25   | 入力     | ハーフブリッジ 1 の PWM 入力。                                                                  |

| IN2     | 40            | 24   | 入力     | ハーフブリッジ 2 の PWM 入力。                                                                  |

| IN3     | 39            | 23   | 入力     | ハーフブリッジ 3 の PWM 入力。                                                                  |

| IN4     | 38            | 22   | 入力     | ハーフブリッジ 4 の PWM 入力。                                                                  |

| СРН     | 44            | 28   | 毒士     | チャージ・ポンプのスイッチング・ノード。X7R、0.022μF、VM 定格のセラミッ                                           |

| CPL     | 43            | 27   | 電力     | ク・コンデンサを CPH と CPL の間に接続します。                                                         |

| PGND12  | -             | 3    | 電力     | ハーフブリッジ 1 および 2 の共通電源グランド。システム・グランドに接続します。                                           |

| PGND34  | -             | 12   | 電力     | ハーフブリッジ 3 および 4 の共通電源グランド。システム・グランドに接続します。                                           |

| PGND1   | 3             | -    | 電力     | ハーフ・ブリッジ1の電源グランド。システム・グランドに接続します。                                                    |

English Data Sheet: SLOSE83

|        | ピン       |       | arc.wr        | av ne                                                                                                          |  |

|--------|----------|-------|---------------|----------------------------------------------------------------------------------------------------------------|--|

| 名称     | DDW      | PWP   | 種類            | 説明                                                                                                             |  |

| PGND2  | 10       | -     | 電力            | ハーフ・ブリッジ2の電源グランド。システム・グランドに接続します。                                                                              |  |

| PGND3  | 20       | -     | 電力            | ハーフ・ブリッジ3の電源グランド。システム・グランドに接続します。                                                                              |  |

| PGND4  | 13       | -     | 電力            | ハーフ・ブリッジ 4 の電源グランド。システム・グランドに接続します。                                                                            |  |

| OUT1   | 4、5、6    | 4、5   | 出力            | 負荷ピンに接続します。                                                                                                    |  |

| OUT2   | 7, 8, 9  | 6、7   | 出力            | 負荷ピンに接続します。                                                                                                    |  |

| OUT3   | 17、18、19 | 10、11 | 出力            | 負荷ピンに接続します。                                                                                                    |  |

| OUT4   | 14、15、16 | 8,9   | 出力            | 負荷ピンに接続します。                                                                                                    |  |

| GND    | 22、23    | 14    | 電力            | デバイスのグランド。システム・グランドに接続します。                                                                                     |  |

| DVDD   | 24       | 15    | 電力            | 内部 LDO 出力。X7R、0.47μF~1μF、6.3V または 10V 定格のセラミック・<br>ンデンサを GND との間に接続します。                                        |  |

| VREF   | 33       | 21    | 入力            | 電流レギュレーションのスレッショルドを設定するための電圧リファレンス入力。<br>DVDD と分割抵抗を使用して VREF を供給できます。                                         |  |

| VCC    | 25       | -     | 電力            | 内部ロジック・ブロックの電源電圧。個別のロジック電源電圧が利用できない場合は、VCC ピンを DVDD ピンに接続します。                                                  |  |

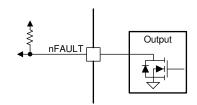

| nFAULT | 26       | 16    | オープン・ド<br>レイン | フォルト通知出力。フォルト条件のときにロジック Low にプルされます。オープン・ドレイン出力には、外付けのプルアップ抵抗が必要です。                                            |  |

| MODE   | 28       | -     | 入力            | このピンは、出力の立ち上がり/立ち下がり時間をプログラムします。                                                                               |  |

| ОСРМ   | 27       | -     | 入力            | フォルトからの回復の方法を決定します。OCPM 電圧に応じて、フォルトからの回復はラッチオフまたは自動再試行タイプになります。                                                |  |

| nSLEEP | 42       | 26    | 入力            | スリープ・モード入力。デバイスは、ロジック High でイネーブルになり、ロジック Low で低消費電力スリープ・モードに移行します。狭い nSLEEP リセット・パルスにより、ラッチされているフォルトがクリアされます。 |  |

| PAD    | -        | -     | -             | サーマル・パッド。システム・グランドに接続します。                                                                                      |  |

### 6 仕様

自由気流での動作温度範囲内 (特に記述のない限り)。(11)(2)

#### 6.1 絶対最大定格

|                          | 最小値  | 最大値                    | 単位 |

|--------------------------|------|------------------------|----|

| 電源電圧 (VM)                | -0.3 | 60                     | V  |

| チャージ・ポンプ電圧 (VCP、CPH)     | -0.3 | V <sub>VM</sub> + 5.75 | V  |

| チャージ・ポンプ負スイッチング・ピン (CPL) | -0.3 | V <sub>VM</sub>        | V  |

| nSLEEP ピン電圧 (nSLEEP)     | -0.3 | V <sub>VM</sub>        | V  |

| 内部レギュレータ電圧 (DVDD)        | -0.3 | 5.75                   | V  |

| 外部ロジック電源 (VCC)           | -0.3 | 5.75                   | V  |

| リファレンス入力ピン電圧 (VREF)      | -0.3 | 5.75                   | V  |

| IPROPI ピン電圧 (IPROPI)     | -0.3 | DVDD + 0.3             | V  |

| 制御ピン電圧                   | -0.3 | 5.75                   | V  |

| PGNDx から GND への電圧        | -0.5 | 0.5                    | V  |

| PGNDx から GND への電圧、1µs 未満 | -2.5 | 2.5                    | V  |

| オープン・ドレイン出力電流 (nFAULT)   | 0    | 10                     | mA |

| OUTx ピンの連続電圧             | -1   | V <sub>VM</sub> + 1    | V  |

| 過渡 100ns の OUTx ピン電圧     | -3   | V <sub>VM</sub> + 3    | V  |

| ピーク駆動電流                  | 内部自  | りに制限                   | Α  |

| 動作時の周囲温度、TA              | -40  | 125                    | °C |

| 動作時の接合部温度、T」             | -40  | 150                    | °C |

| 保存温度、T <sub>stg</sub>    | -65  | 150                    | °C |

<sup>(1)</sup> 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレス定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

#### 6.2 ESD 定格

|                    | <b>-</b> |                                                          |        |       |    |

|--------------------|----------|----------------------------------------------------------|--------|-------|----|

|                    |          |                                                          |        | 値     | 単位 |

|                    |          | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     |        | ±2000 |    |

| V <sub>(ESD)</sub> | 静電気放電    | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | 角のピン   | ±750  | V  |

|                    |          | ファイス帝电モアル (CDM)、ANSI/ESDA/JEDEC JS-002 卓拠                | その他のピン | ±500  |    |

- 1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                  |                    | 最小値  | 最大値 | 単位  |

|------------------|--------------------|------|-----|-----|

| $V_{VM}$         | 通常 (DC) 動作の電源電圧範囲  | 4.5  | 55  | V   |

| VI               | ロジック・レベル入力電圧       | 0    | 5.5 | V   |

| V <sub>VCC</sub> | VCCピン電圧            | 3.05 | 5.5 | V   |

| V <sub>REF</sub> | リファレンス電圧 (VREF)    | 0.05 | 3.3 | V   |

| $f_{PWM}$        | 印加される PWM 信号       | 0    | 200 | kHz |

| I <sub>DDW</sub> | 出力あたりの電流、DDW パッケージ | 0    | 5   | А   |

Submit Document Feedback

<sup>(2)</sup> すべての電圧値は、回路のグランド端子 GND を基準としたものです。

6.3 推奨動作条件 (continued)

自由気流での動作温度範囲内 (特に記述のない限り)

|                  |                    | 最小値 | 最大値 | 単位 |

|------------------|--------------------|-----|-----|----|

| I <sub>PWP</sub> | 出力あたりの電流、PWP パッケージ | 0   | 4   | A  |

| T <sub>A</sub>   | 動作時周囲温度            | -40 | 125 | °C |

| T <sub>J</sub>   | 動作時接合部温度           | -40 | 150 | °C |

## 6.4 熱に関する情報

|                        | 熱評価基準               | DDW  | PWP  | 単位   |

|------------------------|---------------------|------|------|------|

| R <sub>0JA</sub>       | 接合部から周囲への熱抵抗        | 22.5 | 24.5 | °C/W |

| R <sub>0</sub> JC(top) | 接合部からケース (上面) への熱抵抗 | 9.8  | 13.5 | °C/W |

| $R_{\theta JB}$        | 接合部から基板への熱抵抗        | 5.9  | 5.2  | °C/W |

| ΨЈТ                    | 接合部から上面への熱特性パラメータ   | 0.2  | 0.2  | °C/W |

| ΨЈВ                    | 接合部から基板への特性パラメータ    | 5.8  | 5.1  | °C/W |

| $R_{\theta JC(bot)}$   | 接合部からケース (底面) への熱抵抗 | 0.9  | 0.9  | °C/W |

### 6.5 電気的特性

標準値は  $T_A = 25$ °C、 $V_{VM} = 24$ V での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

|                        | パラメータ                            | テスト条件                             | 最小値  | 標準値                 | 最大値  | 単位  |

|------------------------|----------------------------------|-----------------------------------|------|---------------------|------|-----|

| 電源 (VM、C               | (VDD)                            |                                   |      |                     |      |     |

|                        | \/\\                             | nSLEEP = 1、無負荷、VCC=外部 5V          |      | 4                   | 7    | mA  |

| I <sub>VM</sub>        | VM 動作電源電流                        | nSLEEP = 1、無負荷、VCC = DVDD         |      | 6                   | 9    | mA  |

| $I_{VMQ}$              | VM スリープ・モード電源電流                  | nSLEEP = 0                        |      | 3                   | 8    | μΑ  |

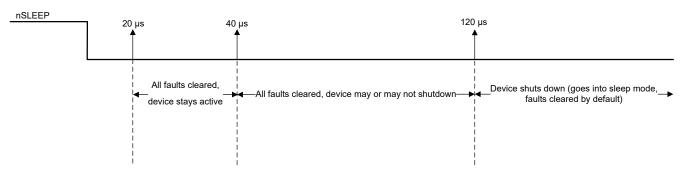

| t <sub>SLEEP</sub>     | スリープ時間                           | nSLEEP = 0 からスリープ・モードまで           | 120  |                     |      | μs  |

| t <sub>RESET</sub>     | nSLEEP リセット・パルス                  | nSLEEP = Low でフォルトをクリア            | 20   |                     | 40   | μs  |

| t <sub>WAKE</sub>      | ウェークアップ時間                        | nSLEEP = 1 で出力遷移                  |      | 0.85                | 1.2  | ms  |

| t <sub>ON</sub>        | ターンオン時間                          | VM > UVLO で出力遷移                   |      | 0.85                | 1.3  | ms  |

| \/                     | 上地, 18 、 5年17                    | 外部負荷なし、6V < V <sub>VM</sub> < 55V | 4.75 | 5                   | 5.25 | V   |

| $V_{DVDD}$             | 内部レギュレータ電圧                       | 外部負荷なし、V <sub>VM</sub> = 4.5V     | 4.2  | 4.35                |      | V   |

| チャージ・ポ                 | ンプ (VCP、CPH、CPL)                 |                                   |      | -                   |      |     |

| V <sub>VCP</sub>       | VCP 動作電圧                         | 6V < V <sub>VM</sub> < 55V        |      | V <sub>VM</sub> + 5 |      | V   |

| f <sub>(VCP)</sub>     | チャージ・ポンプのスイッチング周<br>波数           | V <sub>VM</sub> > UVLO、nSLEEP = 1 |      | 360                 |      | kHz |

| ロジック・レベ                | ドル入力 (IN1、IN2、IN3、IN4、EN1、E      | EN2、EN3、EN4、MODE、OCPM、nSLEE       | P)   |                     |      |     |

| V <sub>IL</sub>        | 入力ロジック Low 電圧                    |                                   | 0    |                     | 0.6  | V   |

| V <sub>IH</sub>        | 入力ロジック High 電圧                   |                                   | 1.5  |                     | 5.5  | V   |

| $V_{HYS}$              | 入力ロジック・ヒステリシス (nSLEEP を除くすべてのピン) |                                   |      | 100                 |      | mV  |

| V <sub>HYS_nSLEE</sub> | nSLEEP ロジック・ヒステリシス               |                                   |      | 300                 |      | mV  |

| I <sub>IL</sub>        | 入力ロジック Low 電流                    | V <sub>IN</sub> = 0V              | -1   |                     | 1    | μΑ  |

| I <sub>IH</sub>        | 入力ロジック High 電流                   | V <sub>IN</sub> = DVDD            |      |                     | 50   | μΑ  |

| t <sub>1</sub>         | ENx High から OUTx High の遅延        | INx = 1                           |      |                     | 2    | μs  |

標準値は  $T_A = 25^{\circ}C$ 、 $V_{VM} = 24V$  での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

|                       | パラメータ                     | テスト条件                                                                      | 最小値   | 標準値  | 最大値   | 単位                                  |

|-----------------------|---------------------------|----------------------------------------------------------------------------|-------|------|-------|-------------------------------------|

| t <sub>2</sub>        | ENx Low から OUTx Low の遅延   | INx = 1                                                                    |       |      | 2     | μs                                  |

| t <sub>3</sub>        | ENx High から OUTx Low の遅延  | INx = 0                                                                    |       |      | 2     | μs                                  |

| t <sub>4</sub>        | ENx Low から OUTx High の遅延  | INx = 0                                                                    |       |      | 2     | μs                                  |

| t <sub>5</sub>        | INx High から OUTx High の遅延 |                                                                            |       | 600  |       | ns                                  |

| t <sub>6</sub>        | INx Low から OUTx Low の遅延   |                                                                            |       | 600  |       | ns                                  |

| 制御出力 (r               | FAULT)                    |                                                                            | •     | '    |       |                                     |

| V <sub>OL</sub>       | 出力ロジック Low 電圧             | I <sub>O</sub> = 5mA                                                       |       |      | 0.35  | V                                   |

| I <sub>OH</sub>       | 出力ロジック High リーク電流         |                                                                            | -1    |      | 1     | μΑ                                  |

| モーター・ド                | ライバ出力 (OUT1、OUT2、OUT3、O   | UT4)                                                                       |       |      |       |                                     |

|                       |                           | T <sub>J</sub> = 25°C、I <sub>O</sub> = -5A、DDW パッケージ                       |       | 54   | 63    | $\boldsymbol{m}\boldsymbol{\Omega}$ |

| R <sub>DS(ONH</sub> , | ハイサイド FET オン抵抗、DDW パッケージ  | T <sub>J</sub> = 125℃、I <sub>O</sub> = -5A、DDW パッケージ                       |       | 80   | 94    | mΩ                                  |

| DDW)                  |                           | T <sub>J</sub> = 150°C、I <sub>O</sub> = -5A、DDW パッケージ                      |       | 90   | 105   | mΩ                                  |

|                       |                           | T <sub>J</sub> = 25℃、I <sub>O</sub> = 5A、DDW パッケージ                         |       | 58   | 66    | mΩ                                  |

| R <sub>DS(ONL</sub>   | ローサイド FET オン抵抗、DDW パッケージ  | T <sub>J</sub> = 125℃、I <sub>O</sub> = 5A、DDW パッケージ                        |       | 85   | 98    | mΩ                                  |

| DDW) ッケージ             |                           | T <sub>J</sub> = 150℃、I <sub>O</sub> = 5A、DDW パッケージ                        |       | 94   | 107   | mΩ                                  |

|                       |                           | T <sub>J</sub> = 25℃、I <sub>O</sub> = -5A、PWP パッケージ                        |       | 58   | 65    | mΩ                                  |

| R <sub>DS(ONH</sub> , | ハイサイド FET オン抵抗、PWP パッケージ  | T <sub>J</sub> = 125°C、I <sub>O</sub> = -5A、PWP パッケージ                      |       | 85   | 98    | mΩ                                  |

| PWP)                  |                           | T <sub>J</sub> = 150°C、I <sub>O</sub> = -5A、PWP パッケージ                      |       | 94   | 107   | mΩ                                  |

|                       |                           | T <sub>J</sub> = 25℃、I <sub>O</sub> = 5A、PWP パッケージ                         |       | 55   | 66    | mΩ                                  |

| R <sub>DS(ONL</sub>   |                           | T <sub>J</sub> = 125°C、I <sub>O</sub> = 5A、PWP パッケージ                       |       | 83   | 100   | mΩ                                  |

| PWP)                  |                           | T <sub>J</sub> = 150℃、I <sub>O</sub> = 5A、PWP パッケージ                        |       | 94   | 116   | mΩ                                  |

| t <sub>RF</sub>       | 出力立ち上がり/立ち下がり時間           | DDW パッケージまたは PWP パッケージ<br>の場合、I <sub>O</sub> = 5A、MODE = 0、10%~<br>90% の範囲 |       | 140  |       | ns                                  |

|                       |                           | DDW パッケージの場合、I <sub>O</sub> = 5A、<br>MODE = 1、10%~90% の範囲                  |       | 70   |       | ns                                  |

| t <sub>D</sub>        | 出力デッドタイム                  | VM = 24V, I <sub>O</sub> = 5A                                              |       | 300  |       | ns                                  |

| 電流検出お                 | よびレギュレーション (IPROPI、VREF   | )                                                                          | •     |      |       |                                     |

| A <sub>IPROPI</sub>   | 電流ミラー・ゲイン                 |                                                                            |       | 212  |       | μA/A                                |

| K <sub>V</sub>        | トランスインピーダンス・ゲイン           | VREF = 3.3V、PWP パッケージ                                                      | 0.625 | 0.66 | 0.695 | V/A                                 |

|                       |                           | 定格電流の 10%~20%                                                              | -7    |      | 9     |                                     |

| A <sub>ERR</sub>      | 電流ミラー・スケーリング誤差            | 定格電流の 20%~40%                                                              | -4    |      | 6     | %                                   |

|                       |                           | 40%~100% 定格電流                                                              | -3.5  |      | 5     |                                     |

| I <sub>VREF</sub>     | VREF リーク電流                | VREF = 3.3V                                                                |       |      | 20    | nA                                  |

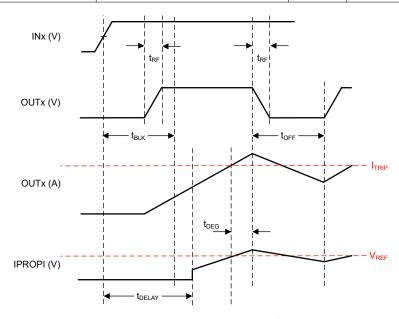

| toff                  | PWM オフ時間                  |                                                                            |       | 16   |       | μs                                  |

| *UFF                  | 電流レギュレーション・グリッチ除去         |                                                                            |       | -    |       | μ3                                  |

| t <sub>DEG</sub>      | 時間                        |                                                                            |       | 0.5  |       | μs                                  |

| t <sub>BLK</sub>      | 電流レギュレーション・ブランキング 時間      |                                                                            |       | 1.5  |       | μs                                  |

| t <sub>DELAY</sub>    | 電流検出遅延時間                  |                                                                            |       | 2    |       | μs                                  |

標準値は  $T_A = 25$ °C、 $V_{VM} = 24$ V での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

|                       | パラメータ                  | テスト条件                     | 最小値      | 標準値                 | 最大値  | 単位 |

|-----------------------|------------------------|---------------------------|----------|---------------------|------|----|

| 保護回路                  |                        |                           |          |                     |      |    |

|                       |                        | VM 立ち下がり                  | 4.1      | 4.23                | 4.35 | V  |

| $V_{UVLO}$            | VM 低電圧誤動作防止 (UVLO)     | VM 立ち上がり                  | 4.2 4.35 |                     | 4.47 | v  |

| VCC                   | VOO 低景区部新作叶山 (11)(1 O) | VCC 立ち下がり                 | 2.7      | 2.8                 | 2.9  | V  |

| VCC <sub>UVLO</sub>   | VCC 低電圧誤動作防止 (UVLO)    | VCC 立ち上がり                 | 2.75     | 2.92                | 3.05 |    |

| V <sub>UVLO,HYS</sub> | 低電圧ヒステリシス              | 立ち上がりから立ち下がりへのスレッショ<br>ルド |          | 110                 |      | mV |

| V <sub>CPUV</sub>     | チャージ・ポンプ低電圧            | VCP 立ち下がり                 |          | V <sub>VM</sub> + 2 |      | V  |

| I <sub>OCP</sub>      | 過電流保護                  | いずれかの FET を流れる電流          | 7.6      |                     |      | Α  |

| t <sub>OCP</sub>      | 過電流検出遅延                |                           |          | 2.2                 |      | μs |

| t <sub>RETRY</sub>    | 過電流リトライ時間              |                           |          | 4.1                 |      | ms |

| T <sub>OTSD</sub>     | サーマル・シャットダウン           | ダイ温度 T <sub>J</sub>       | 150      | 165                 | 180  | °C |

| T <sub>HYS_OTSD</sub> | サーマル・シャットダウン・ヒステリシス    | ダイ温度 T <sub>J</sub>       |          | 20                  |      | °C |

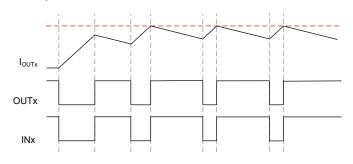

図 6-1. IPROPI のタイミング図

### 6.6 代表的な特性

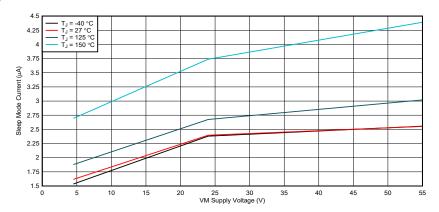

図 6-2. スリープ・モード電源電流

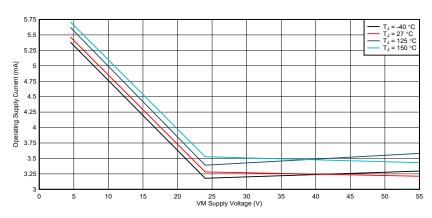

図 6-3. 動作電源電流、VCC=外部 5V

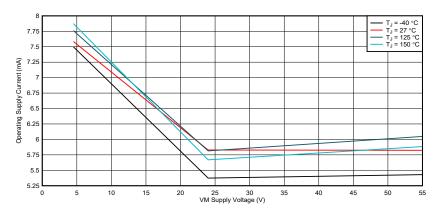

図 6-4. 動作電源電流、VCC = DVDD

English Data Sheet: SLOSE83

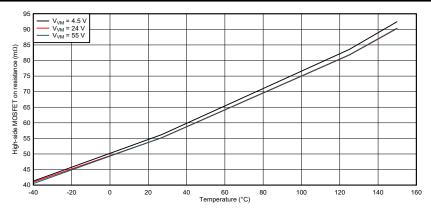

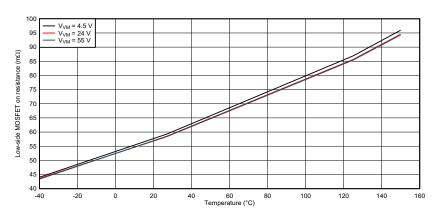

図 6-5. ハイサイド FET オン抵抗

図 6-6. ローサイド FET オン抵抗

### 7 詳細説明

#### 7.1 概要

DRV8952 は 4 チャネルのハーフブリッジ・ドライバで、4.5V~55V で動作し、各種の負荷について広い範囲の負荷電流に対応しています。このデバイスは、4 つのハーフブリッジ出力電力段を内蔵しています。また、このデバイスはチャージ・ポンプ・レギュレータを内蔵しており、効率的なハイサイド N チャネル MOSFET と 100% デューティ・サイクル動作に対応しています。DRV8952 は、単一の電源入力 (VM) で動作できます。DDW パッケージを使用する場合、代わりに VCC ピンを 2 番目の電源に接続し、内部ロジック・ブロックに電力を供給することもできます。nSLEEP ピンにより、超低消費電力モードに移行して、スリープ時の消費電流を最小限に抑えることができます。

このデバイスは、44 ピン HTSSOP (DDW) パッケージと、別の 28 ピン HTSSOP (PWP) パッケージの 2 つのパッケージで供給されます。DDW パッケージは出力ごとに最大 5A の電流を供給し、PWP パッケージは出力ごとに最大 4A の電流を供給できます。DRV8952 DDW パッケージは DRV8962 とピン互換で、DRV8952 PWP パッケージは DRV8955 とピン互換です。実際に供給可能な電流は、周囲温度、電源電圧、PCB の熱設計に依存します。

DRV8952 DDW パッケージは電流センス出力を提供します。IPROPI ピンは、ハイサイド MOSFET の電流に比例した 小さな電流を出力します。IPROPI ピンからの電流は、外付け抵抗 (R<sub>IPROPI</sub>) を使用して、比例電圧に変換できます。電流検出回路を内蔵することで、DRV8952 は固定オフ時間 PWM チョッピング方式で出力電流を制限できます。また、負荷情報を外部コントローラに提供して、負荷の変化を検出できます。IPROPI 出力の検出精度は、定格電流の 40%~100% について -3.5%/+5% です。より高精度の検出が必要な場合は、外付けの電力検出抵抗も接続できます。システムの要求に応じて負荷電流を制限するために、電流レギュレーションのレベルは、動作中に VREF ピンで設定できます。

システムに異常状態が発生した場合、内蔵する各種保護機能がデバイスを保護します。保護機能には、低電圧誤動作防止 (UVLO)、チャージ・ポンプ低電圧 (CPUV)、過電流保護 (OCP)、過熱シャットダウン (OTSD) があります。フォルト状態は、nFAULT ピンにより通知されます。

## 7.2 機能ブロック図

### 7.3 機能説明

次の表に、DRV8952 の外付け部品の推奨値を示します。

### 表 7-1. 外付け部品

| 品略                   | ピン1          | ピン 2   | 推奨事項                                 |

|----------------------|--------------|--------|--------------------------------------|

| C <sub>VM1</sub>     | VM           | PGND1  | X7R、0.01μF、VM 定格セラミック・コンデンサ          |

| C <sub>VM2</sub>     | VM           | PGND3  | X7R、0.01μF、VM 定格セラミック・コンデンサ          |

| C <sub>VM3</sub>     | VM           | PGND1  | バルク、VM 定格コンデンサ                       |

| C <sub>VCP</sub>     | VCP          | VM     | X7R、1μF、16V セラミック・コンデンサ              |

| C <sub>SW</sub>      | СРН          | CPL    | X7R、0.1μF、VM 定格セラミック・コンデンサ           |

| C <sub>DVDD</sub>    | DVDD         | GND    | X7R、1μF、6.3V または 10V 定格セラミック・コンデンサ   |

| C <sub>VCC</sub>     | VCC          | GND    | X7R、0.1μF、6.3V または 10V 定格セラミック・コンデンサ |

| R <sub>nFAULT</sub>  | DVDD または VCC | nFAULT | 10kΩ の抵抗                             |

| R <sub>REF1</sub>    | VREF         | DVDD   | 電流レギュレーション・スレッショルドを設定するための抵抗。        |

| R <sub>REF2</sub>    | VREF         | GND    | 电机レイユレーション・ヘレツショルトを放足りるにめり抵仇。<br>    |

| R <sub>IPROPIx</sub> | IPROPIx      | GND    | 詳細については、セクション 7.5.1 を参照してください。       |

### 7.4 独立のハーフブリッジ動作

- DRV8952 は、4 つのハーフブリッジ負荷を同時に駆動できます。

- DDW パッケージの場合、MODE ピンは、標準的な出力の立ち上がりおよび立ち下がり時間を 70ns または 140ns に設定します。

- PWP パッケージの立ち上がりおよび立ち下がり時間は 140ns です。

- ENx ピンは、出力をイネーブルまたはディセーブル (ハイ・インピーダンス) します。

- INx ピンは、出力の状態 (ハイまたはロー) を制御します

- INx ピンは、静的またはパルス幅変調 (PWM) 信号を受け付けます。

- INx および ENx 入力には、VM を印加する前に電力を供給できます。

- 真理値表では、内部電流レギュレーション機能を考慮していません。

- デバイスは、ハーフブリッジのハイサイド MOSFET とローサイド MOSFET の切り替え時に、自動的にデッドタイムを 生成します。

表 7-2. 独立ハーフブリッジ動作の真理値表

| nSLEEP | INx | ENx | OUTx       | 説明                                           |

|--------|-----|-----|------------|----------------------------------------------|

| 0      | Х   | х   | ハイ・インピーダンス | スリープ・モード、すべてのハーフブリッジはディセ<br>ーブル (ハイ・インピーダンス) |

| 1      | X   | 0   | ハイ・インピーダンス | 個々の出力はディセーブル (ハイ・インピーダンス)                    |

| 1      | 0   | 1   | L          | OUTx ローサイド・オン                                |

| 1      | 1   | 1   | Н          | OUTx ハイサイド・オン                                |

入力は、DC モーターの速度などの PWM 制御にも使用できます。PWM による巻線制御では、駆動電流が中断されたとき、モーターの誘導性の性質から、電流を継続して流す必要があります。これを「再循環電流」といいます。再循環電流を扱うため、H ブリッジは 2 つの異なる状態 (高速減衰または低速減衰) で動作できます。高速減衰モードでは、H ブリッジがディセーブルされ、再循環電流がボディ・ダイオードに流れます。低速減衰では、モーターの巻線が短絡します。

PWM で高速減衰を使用するときは、ENx ピンに PWM 信号が印加されます。低速減衰を使用するときは、INx ピンに PWM 信号が印加されます。次の表に、OUT1 と OUT2 を H ブリッジとして使用し、DC モーターを駆動する例を示します。

表 7-3. PWM 機能

| IN1 | EN1 | IN2 | EN2 | 機能           |

|-----|-----|-----|-----|--------------|

| 1   | 1   | PWM | 1   | 順方向 PWM、低速減衰 |

| PWM | 1   | 1   | 1   | 逆方向 PWM、低速減衰 |

Submit Document Feedback

| 表 7-3. PWM 榜 | 鮠 (continued) |

|--------------|---------------|

|--------------|---------------|

| IN1 | EN1 | IN2 | EN2 | 機能           |

|-----|-----|-----|-----|--------------|

| 1   | PWM | 0   | PWM | 順方向 PWM、高速減衰 |

| 0   | PWM | 1   | PWM | 逆方向 PWM、高速減衰 |

#### 7.5 電流検出とレギュレーション

DRV8952 には、ハイサイド MOSFET の両端での電流検出、電流レギュレーション、電流検出フィードバックが内蔵されています。これらの機能により、負荷が出力ノードとグランドとの間に接続されているとき、外部検出抵抗や検出回路を接続せずに負荷電流を検出できるため、システムのサイズ、コスト、複雑性を低減できます。デバイスは、DDW パッケージの電流検出比例出力 (IPROPI) を使用して、負荷電流に関する詳細なフィードバックをコントローラに提供できます。

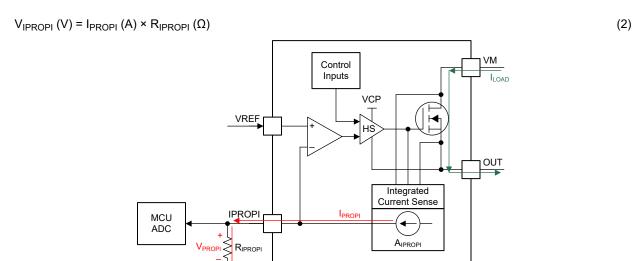

#### 7.5.1 電流検出とフィードバック

DDW パッケージの DRV8952 は、ハーフブリッジごとに 1 つ、合計 4 つの IPROPI 出力をサポートしています。IPROPI 出力は、次に示すように、各ハイサイド MOSFET の電流を表します。

$$I_{PROPI} = I_{HS} \times A_{IPROPI}$$

(1)

ここで、I<sub>HS</sub> はハイサイド MOSFET を流れる電流、A<sub>IPROPI</sub> は電流ミラーのゲインです。

比例電圧 ( $V_{IPROPI}$ ) を IPROPI ピンで生成するには、外付け抵抗 ( $R_{IPROPI}$ ) を介して、各 IPROPI ピンをグランドに接続する必要があります。これにより、標準のアナログ / デジタル・コンバータ (ADC) を使用して、 $R_{IPROPI}$  抵抗の両端の電圧降下として電流を測定できます。 $R_{IPROPI}$  抵抗は、すべてのコントローラ ADC を利用できるように、そのアプリケーションの負荷電流の期待値に基づいて値を調整できます。デバイスの内部にはクランプ回路が実装されており、VREF ピンの $V_{VREF}$  を基準として  $V_{IPROPI}$  を制限し、出力過電流または想定外の大電流イベント時に外部 ADC を保護できます。IPROPI の電圧は、VREF の最大推奨値である 3.3V よりも低くします。

出力電流に対応する IPROPI 電圧は、次の式で計算できます。

図 7-1. 内蔵電流検出回路

「電気的特性」表の A<sub>ERR</sub> パラメータは、A<sub>IPROPI</sub> ゲインに関連する誤差です。この誤差は、I<sub>OUT</sub> 電流に加算されたオフセット誤差とゲイン誤差の複合的な影響を示しています。

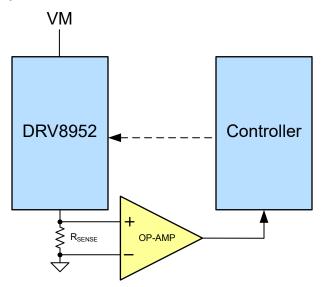

### 7.5.2 外付け抵抗による電流検出

IPROPI 出力の精度は、定格電流の 40%~100% について -3.5%~+5% です。より正確な電流検出が必要な場合、または PWP パッケージの場合は、以下に示すように、PGND ピンとシステム・グランドとの間に外部検出抵抗を使用して負荷電流を検出することもできます。

図 7-2. 外付け抵抗による電流検出

外付け検出抵抗の両端での電圧降下は、300mV を超えないようにします。

検出抵抗は、対応する IC のピンのできるだけ近くに配置します。センス抵抗を左右対称に配置することで、マッチングが適切になります。電圧スパイクとリンギングを防止するため、低インダクタンスのセンス抵抗を使用してください。最適な性能を確保するため、センス抵抗には十分大きな電力を定格とする表面接地型の抵抗を使用してください。

#### 7.5.3 電流レギュレーション

DDW パッケージの DRV8952 の場合、電流チョッピング・スレッショルド ( $I_{TRIP}$ ) は、VREF 電圧 ( $V_{VREF}$ ) と IPROPI 出力抵抗 ( $R_{IPROPI}$ ) の組み合わせにより設定されます。具体的には、内部コンパレータを使用して、外付け  $R_{IPROPI}$  抵抗両端の電圧降下を  $V_{VREF}$  と比較します。

$$I_{TRIP}(A) \times A_{IPROPI}(\mu A/A) = V_{VREF}(V) / R_{IPROPI}(\Omega)$$

(3)

たとえば、V<sub>VREF</sub> が 3.3V のときに I<sub>TRIP</sub> を 5A に設定するには、R<sub>IPROPI</sub> に次の値が必要です。

$R_{IPROPI} = V_{VREF} / (I_{TRIP} \times A_{IPROPI}) = 3.3 / (5 \times 212 \times 10^{-6}) = 3.09 k\Omega$

IPROPI を GND に接続し、VREF ピンの電圧を GND より高く設定することで、内部電流レギュレーション機能をディセーブルできます (電流帰還が不要の場合)。電流帰還が必要でありかつ電流レギュレーションが不要である場合、 $V_{IPROPI}$ が  $V_{VREF}$  スレッショルドに到達することがないように  $V_{VREF}$  と  $R_{IPROPI}$  を設定します。

PWP パッケージの DRV8952 の場合、電流チョッピング・スレッショルド ( $I_{TRIP}$ ) は、以下のように VREF 電圧 ( $V_{VREF}$ ) によって設定されます。

$$I_{TRIP}(A) = V_{VREF}(V) / K_V(V/A)$$

(4)

DRV8952 は、最大 4 つの抵抗性負荷または誘導性負荷を同時に駆動できます。出力負荷がグランドに接続されているときは、負荷電流を I<sub>TRIP</sub> レベルにレギュレートできます。PWM オフ時間 (t<sub>OFF</sub>) は 16μs に固定されています。固定オフ時間モードにより、外部コントローラを使用せずに、シンプルな電流チョッピング方式を実現できます。固定オフ時間モードは 100% デューティ・サイクル電流レギュレーションをサポートします。

負荷電流を制御するもう 1 つの方法は、サイクル単位の制御モードです。このモードでは、INx 入力ピンの PWM パルス幅を制御する必要があります。このため、外部コントローラによる電流チョッピング方式の追加制御が可能です。

ハイサイドとローサイドの負荷を駆動する、いくつかのシナリオを以下に示します。

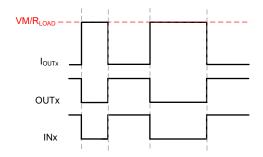

#### • グランドに接続された抵抗性負荷:

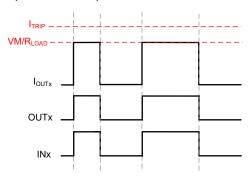

レギュレートされた電流は  $I_{TRIP}$  を超えません。 $I_{TRIP}$  が (VM /  $R_{LOAD}$ ) より高いなら、INx = 1 の間、負荷電流は VM /  $R_{LOAD}$  のレベルにレギュレートされます ( $\boxtimes$  7-3 を参照)。

図 7-3. グランドに接続された抵抗性負荷、サイクル単位の制御

#### • グランドに接続された誘導性負荷:

暴走や過電流保護のトリガを防止するため、電流がサイクルごとに十分減衰することを保証する必要があります。

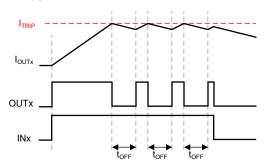

• 図 7-4 に示すシナリオでは、INx = 1 のとき、 $I_{OUT}$  が  $I_{TRIP}$  を超えた後で、ローサイド MOSFET が期間  $t_{OFF}$  だけオンになります。 $t_{OFF}$  が経過すると、再度  $I_{OUT}$  が  $I_{TRIP}$  を超えるまで、ハイサイド MOSFET が再度オンになります。

図 7-4. グランドに接続された誘導性負荷、固定オフ時間電流のチョッピング

$t_{OFF}$  時間の経過後も電流が  $I_{TRIP}$  レベルより高いままなら、デバイスは強制的に同じ時間の  $t_{OFF}$  を繰り返します。オフ時間の延長は、 $t_{OFF}$  時間の終了時に検出される電流が  $I_{TRIP}$  より低くなるまで続きます。

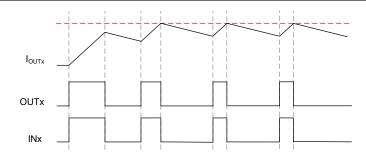

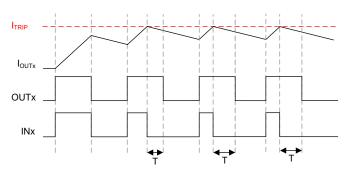

• サイクル単位の方式を使用して負荷を制御することもできます。INx = 1 のとき、負荷を流れる電流は増大し、INx = 0 のとき、負荷を流れる電流は減衰します。INx パルスのデューティ・サイクルを適切に選択することで、電流を目標値にレギュレートできます。このような各種のシナリオを、図 7-5 と図 7-6 に示します。

English Data Sheet: SLOSE83

図 7-5. グランドに接続された誘導性負荷、サイクル単位の制御

次のシナリオでは、電流が暴走しないように INx ピンのデューティ・サイクルを調整する必要があります (T は Toff より小さい必要があります)。

図 7-6. グランドに接続された誘導性負荷、サイクル単位の制御

#### VM に接続された負荷:

このような負荷は、INx ピンのパルス幅によって制御できます。図 7-7 と ② 7-8 に示すように、INx = 0 のとき電流が増大し、INx = 1 のとき電流が減衰します。

図 7-7. VM に接続された誘導性負荷、サイクル単位の制御

このシナリオでは、電流が暴走しないように、INxピンのデューティ・サイクルを調整する必要があります。

図 7-8. グランドに接続された抵抗性負荷、サイクル単位の制御

Submit Document Feedback

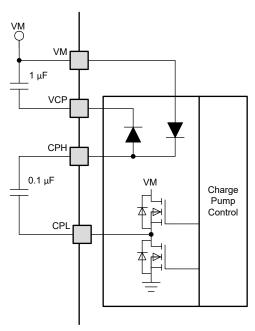

### 7.6 チャージ・ポンプ

ハイサイド N チャネル MOSFET のゲート駆動電圧を供給するため、チャージ・ポンプが内蔵されています。このチャージ・ポンプには、VM ピンと VCP ピンの間に電荷を蓄積するためのコンデンサを接続する必要があります。また、CPH ピンと CPL ピンの間にもフライング・コンデンサとして働くセラミック・コンデンサを接続する必要があります。

図 7-9. チャージ・ポンプのブロック図

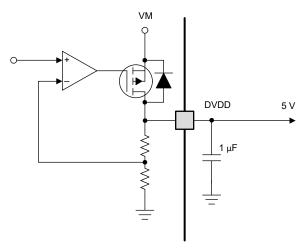

### 7.7 リニア電圧レギュレータ

本デバイスには、リニア電圧レギュレータが内蔵されています。 VCC ピンを DVDD に接続すると、DVDD レギュレータはローサイド・ゲート・ドライバとすべての内部回路に電力を供給します。 正常に動作させるため、1μF のセラミック・コンデンサを使用して DVDD ピンを GND にバイパスします。 DVDD 出力は通常 5V です。

図 7-10. リニア電圧レギュレータのブロック図

デジタル入力を永続的に High に固定する必要がある場合は、入力を外部レギュレータではなく DVDD ピンに接続することを推奨します。この方法により、VM ピンに電圧が印加されないときやスリープ・モード時に電力を節約します。 DVDD のレギュレータがディセーブルされ、電流が入力プルダウン抵抗に流れないためです。 参考までに、ロジック・レベル入力は 200kΩ (標準値) のプルダウンを備えています。

JAJSL44 – MARCH 2023

nSLEEP ピンを DVDD に接続することはできません。これを接続すると、本デバイスはスリープ・モードから復帰できなくなります。

#### 7.8 VCC 電圧電源

DDW パッケージの DRV8952 の場合、外部電圧を VCC ピンに印加することで、内部ロジック回路に電力を供給することができます。 VCC ピンの電圧は 3.05V~5.5V の範囲内で、適切にレギュレートする必要があります。 外部電源が利用できない場合、 VCC をデバイスの DVDD ピンに接続する必要があります。

VCC から電力を供給するとき、内部ロジック・ブロックは VM 電源レールから電力を消費しないため、DRV8952 の電力 損失を低減できます。これは、高電圧アプリケーションや、周囲の温度が高いとき非常に有益です。0.1µF のセラミック・コ ンデンサを使用して、VCC ピンをグランドにバイパスします。

#### 7.9 ロジック・レベル・ピンの図

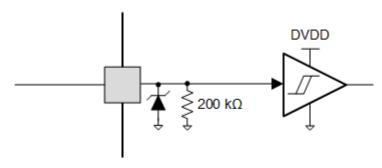

下のピンの図は、INx、ENx、MODE、OCPM、nSLEEP の各ピンの入力構造を示しています。

図 7-11. ロジック・レベル入力ピンの図

### 7.10 保護回路

本デバイスは、電源低電圧、チャージ・ポンプ低電圧、出力過電流、デバイス過熱イベントからデバイスを保護します。

#### 7.10.1 VM 低電圧誤動作防止 (UVLO)

VM ピンの電圧が UVLO スレッショルド電圧を下回ると、次の動作が行われます。

- すべての出力がディセーブル (ハイ・インピーダンス) になる

- nFAULT ピンは Low に駆動される

- チャージ・ポンプがディセーブルになる

VM 電圧が UVLO 立ち上がりスレッショルド電圧を上回ると、通常動作が再開されます (ドライバが動作し、nFAULT が解放されます)。

VM 電圧が内部デジタル・リセット電圧 (最大 3.9V) を下回ると、内部ロジック回路がディセーブルされ、nFAULT のプルダウンもディセーブルされます。したがって、VM が約 3.9V を下回ると、nFAULT は再び High になります。

#### 7.10.2 VCP 低電圧誤動作防止 (CPUV)

VCP ピンの電圧が CPUV 電圧を下回ると、次の動作が行われます。

- すべての出力がディセーブル (ハイ・インピーダンス) になる

- nFAULT ピンは Low に駆動される

- チャージ・ポンプはアクティブのまま

VCP 低電圧条件が解消すると、通常動作に復帰します (ドライバが動作し、nFAULT が解放されます)。

#### 7.10.3 ロジック電源パワーオン・リセット (POR)

VCC ピンの電圧が VCC<sub>UVLO</sub> スレッショルドを下回ると、次のようになります。

20 Submit Document Feedback

www.ti.com/ja-jp JAJSL44 - MARCH 2023

- すべての出力がディセーブル (ハイ・インピーダンス) になる

- チャージ・ポンプがディセーブルになる

VCC UVLO は nFAULT ピンで通知されません。 VCC 低電圧状態が解消されると、通常のモーター・ドライバの動作が 再開されます。

#### 7.10.4 過電流保護 (OCP)

各 MOSFET のアナログ電流制限回路は、ゲート駆動を止めることで、MOSFET に流れる電流を制限します。この電流 制限が toce 時間よりも長く続くと、過電流フォルトが検出されます。

- 過電流が発生しているハーフブリッジのみがディセーブルされます

- nFAULT が Low に駆動されます

- チャージ・ポンプはアクティブのままです

ハイサイドとローサイドの両方の MOSFET が過電流状態の場合、グランドまたは電源への短絡が起きていることを意味 し、これによって過電流フォルトが検出されます。

DDW パッケージの場合、過電流状態が解消されたときの回復の機構は、OCPM ピンの設定によって決まります。OCPM ピンは、ラッチオフまたは自動再試行タイプのいずれかの回復をプログラムします。

- OCPM ピンがロジック Low のとき、デバイスはラッチオフ・タイプの回復を行います。 すなわち、OCP 状態が解消され ると、nSLEEP リセット・パルスが印加された後、または電源を切って再投入した後で、通常動作に復帰します。

- OCPM ピンがロジック High のとき、t<sub>RFTRY</sub> 時間が経過し、フォルト状態が解消した後で、自動的に通常動作に復帰し ます (ドライバが動作し、nFAULT が解放されます)。

PWP パッケージはラッチオフ・タイプの回復のみをサポートします。 nSLEEP リセット・パルスの印加または電源の再投入 後、通常動作が再開されます。

### 7.10.5 サーマル・シャットダウン (OTSD)

ダイ温度がサーマル・シャットダウン制限 (Totso) を超えると、サーマル・シャットダウンが検出されます。サーマル・シャッ トダウンが検出されると、次の動作が行われます。

- ハーフブリッジのすべての MOSFET がディセーブルされます

- nFAULT が Low に駆動されます

- チャージ・ポンプがディセーブルされます

DDW パッケージの場合、サーマル・シャットダウン状態が解消されたときの回復の機構は、OCPM ピンの設定によって決 まります。OCPM ピンは、ラッチオフまたは自動再試行タイプのいずれかの回復をプログラムします。

- OCPM ピンがロジック Low のとき、デバイスにはラッチオフ・タイプの回復機能があります。 つまり、接合部温度が過熱 スレッショルド制限値からヒステリシスを引いた値 (Totsp - Thysotsp)を下回った後、nSLEEP リセット・パルスが印 加されるか、電源を切って再投入すると、通常動作が再開されます。

- OCPM ピンが論理 High のとき、接合部温度が過熱スレッショルド制限値からヒステリシスを引いた値 (Totsp -T<sub>HYS OTSD</sub>)を下回ると、通常動作が自動的に再開されます。

PWP パッケージの場合、サーマル・シャットダウン・フォルトの後、接合部温度が過熱スレッショルド制限値からヒステリシ スを引いた値 (Totsd - Thys\_otsd) を下回ると、通常動作が自動的に再開されます。

#### 7.10.6 nFAULT 出力

nFAULT ピンはオープンドレインの出力を持っているため、5V、3.3V または 1.8V 電源にプルアップする必要がありま す。フォルトが検出された場合、nFAULT ピンはロジック Low になります。電源投入後に、nFAULT ピンは High になりま す。 5V にプルアップする場合、nFAULT ピンから抵抗を介して DVDD ピンに接続できます。 3.3V または 1.8V にプルア ップする場合は、外部電源を使う必要があります。

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

21

図 7-12. nFAULT ピン

#### 7.10.7 フォルト条件のまとめ

表 7-4. フォルト条件のまとめ

| FAULT                  | 条件                                                               | 異常通知   | H ブリッジ | チャージ・ポン<br>プ | ロジック | 復帰                                                              |

|------------------------|------------------------------------------------------------------|--------|--------|--------------|------|-----------------------------------------------------------------|

| VM 低電圧 (UVLO)          | VM 低電圧 (UVLO) VM < V <sub>UVLO</sub>                             |        | ディセーブル | ディセーブル       | リセット | VM > V <sub>UVLO</sub>                                          |

| VCP 低電圧 (CPUV)         | VCP < V <sub>CPUV</sub>                                          | nFAULT | ディセーブル | 動作           | 動作   | VCP > V <sub>CPUV</sub>                                         |

| ロジック電源 POR             | VCC < VCC <sub>UVLO</sub>                                        | -      | ディセーブル | ディセーブル       | リセット | VCC > VCC <sub>UVLO</sub>                                       |

|                        | l <sub>OUT</sub> > l <sub>OCP</sub><br>、OCPM = 0 (DDW パッ<br>ケージ) | nFAULT | ディセーブル | 動作           | 動作   | ラッチ:<br>nSLEEP リセット・パルス                                         |

| 過電流 (OCP)              | l <sub>OUT</sub> > l <sub>OCP</sub><br>、OCPM = 1 (DDW パッ<br>ケージ) | nFAULT | ディセーブル | 動作           | 動作   | 自動リトライ:t <sub>RETRY</sub>                                       |

|                        | l <sub>OUT</sub> > l <sub>OCP</sub><br>、PWP パッケージ                | nFAULT | ディセーブル | 動作           | 動作   | ラッチ:<br>nSLEEP リセット・パルス                                         |

|                        | T <sub>J</sub> > T <sub>TSD</sub> 、OCPM = 0<br>(DDW パッケージ)       | nFAULT | ディセーブル | ディセーブル       | 動作   | ラッチ:<br>nSLEEP リセット・パルス                                         |

| サーマル・シャットダウン<br>(OTSD) | T <sub>J</sub> > T <sub>TSD</sub> 、OCPM = 1<br>(DDW パッケージ)       | nFAULT | ディセーブル | ディセーブル       | 動作   | 自動:T」 <t<sub>OTSD -<br/>T<sub>HYS_OTSD</sub></t<sub>            |

|                        | T <sub>J</sub> > T <sub>TSD</sub> 、<br>PWP パッケージ                 | nFAULT | ディセーブル | ディセーブル       | 動作   | 自動:T <sub>J</sub> <t<sub>OTSD-<br/>T<sub>HYS_OTSD</sub></t<sub> |

### 7.11 デバイスの機能モード

### 7.11.1 スリープ・モード (nSLEEP = 0)

nSLEEP ピンが Low になると、本デバイスは低消費電力のスリープ・モードに移行します。スリープ・モードでは、すべて の内部 MOSFET、DVDD レギュレータ、SPI、チャージ・ポンプがディセーブルになります。 nSLEEP ピンでの立ち下がり エッジの後、t<sub>SLEEP</sub> 時間が経過すると、デバイスはスリープ・モードに移行します。 nSLEEP ピンが High になると、本デ バイスは自動的にスリープから復帰します。twake 時間が経過すると、デバイスは入力可能な状態になります。

#### 7.11.2 動作モード

このモードは、次の場合にイネーブルになります。

- nSLEEP が High

- VM > UVLO

twake時間が経過すると、デバイスは入力可能な状態になります。

### 7.11.3 nSLEEP リセット・パルス

ラッチされたフォルトは nSLEEP リセット・パルスでクリアできます。このパルス幅は 20μs より長く 40μs より短い必要があ ります。 nSLEEP が 40µs より長く 120µs より短い間 Low である場合、フォルトはクリアされますが、本デバイスはシャット

Product Folder Links: DRV8952

Submit Document Feedback

ダウンする場合としない場合があります (タイミング図を参照)。このリセット・パルスは、チャージ・ポンプの状態にも、その他の機能ブロックの状態にも影響を与えません。

図 7-13. nSLEEP リセット・パルス

### 7.11.4 機能モードのまとめ

機能モードのまとめを示します。

表 7-5. 機能モードのまとめ

| 条件       |                 | 構成          | H ブリッジ | DVDD レギュレー<br>タ | チャージ・ポンプ | ロジック   |

|----------|-----------------|-------------|--------|-----------------|----------|--------|

| スリープ・モード | 4.5V < VM < 55V | nSLEEPピン=0  | ディセーブル | ディセーブル          | ディセーブル   | ディセーブル |

| 動作       | 4.5V < VM < 55V | nSLEEP ピン=1 | 動作     | 動作              | 動作       | 動作     |

### 8 アプリケーションと実装

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

#### 8.1 アプリケーション情報

DRV8952 は、次のタイプの負荷を駆動するために使用できます。

- 最大4つのソレノイド負荷

- 1 つのステッパ・モーター

- 2 つのブラシ付き DC モーター

- 1 つの 3 相正弦波ブラシレス DC モーター

- 1 つの 3 相永久磁石同期モーター (PMSM)

- 1 つまたは 2 つの熱電冷却器 (TEC)

#### 8.1.1 ソレノイド負荷の駆動

DRV8952 は、同時に 4 つのソレノイド負荷を駆動できます。グランドに接続された負荷の場合、IPROPI ピンは負荷電流情報を出力し (DDW パッケージの場合)、負荷電流は VREF ピンの電圧によって決定される I<sub>TRIP</sub> レベルにレギュレートできます。

DRV8952 は、4 つのハーフブリッジそれぞれについて、独立の IN および EN ピンをサポートしています。また、4 つのハーフブリッジにはすべて、別の PGND ピンがあります。

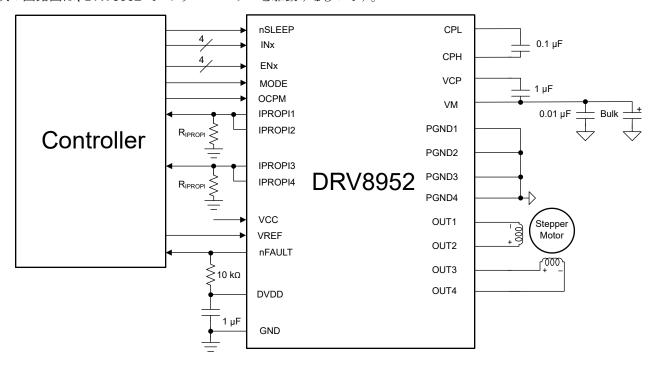

#### 8.1.1.1 ソレノイド・ドライバの代表的なアプリケーション

グランドに接続された 4 つの負荷を駆動する DRV8952 の回路図を、図 8-1 に示します。

図 8-1. DRV8952 によるソレノイドの駆動

#### 8.1.1.2 熱に関する計算

本デバイスの出力電流および消費電力特性は、PCB 設計と外部条件に大きく依存します。ここでは、これらの値を計算するための指針を提示します。

本デバイスの総消費電力は、おもに3つの要素から成ります。それらは、パワー MOSFET R<sub>DS(ON)</sub> (導通) 損失、パワー MOSFET スイッチング損失、および電源静止電流損失です。それ以外の要素が電力損失の増加に影響することもありますが、この3つの主要な要素に比べると通常わずかです。

#### 8.1.1.2.1 電力損失の計算

各ハーフブリッジの合計消費電力は、次のように計算できます。

$P_{HB} = P_{HS} + P_{LS} = [R_{DS(ON)} \times I_L^2] + [((2 \times V_D \times t_D) + (VM \times t_{RF})) \times I_L \times f_{PWM}]$

- R<sub>DS(ON)</sub>=各 FET のオン抵抗

- DRV8952 の場合、通常 25℃で平均 56mΩ です

- f<sub>PWM</sub>=PWM スイッチング周波数

- VM =ドライバへの電源電圧

- I<sub>I</sub>=負荷電流

- D=PWM のデューティ・サイクル (0~1)

- t<sub>RF</sub>=出力電圧の立ち上がり/立ち下がり時間

- DRV8952 の場合、立ち上がり / 立ち下がり時間は DDW パッケージで 70ns または 140ns、PWP パッケージで 140ns です。

- $V_D$ =FET ボディ・ダイオードの順方向バイアス電圧

- DRV8952 では 1V です

- tn=デッドタイム

- DRV8952 では 300ns です

したがって、DRV8952 の合計消費電力は次の式で与えられます。

$P_{TOT} = n \times P_{HB} + P_{O}$

ここで、n は同時にスイッチングされるハーフブリッジの数、Po は静止電力損失です。

この例では、次のことを想定します。

- 4 つのハーフブリッジはすべてスイッチングを行います

- VM = 24V

- I<sub>1</sub> = 3A

- 周囲温度 (T<sub>A</sub>) = 25℃

- t<sub>RF</sub> = 140ns

- 入力 PWM 周波数=20kHz

VCC ピンが外部電源に接続されているとき、静止電流は 4mA なので、 $P_Q$  は  $(24V \times 4mA) = 96mW$  になります。

$P_{HB} = [56m\Omega \times 3^2] + [((2 \times 1V \times 300ns) + (24V \times 140ns)) \times 3A \times 20KHz] = 0.742W$

$P_{TOT} = (4 \times 0.742) + 0.096 = 3.062W$

#### 8.1.1.2.2 接合部温度の推定

接合部温度の推定値は次のとおりです。 $T_J = T_A + (P_{TOT} \times \theta_{JA})$

接合部から周囲への熱抵抗  $\theta_{JA}$  は、DDW パッケージでは 22.5°C/W、JEDEC 標準 PCB における PWP パッケージでは 24.5°C/W です。

Product Folder Links: DRV8952

したがって、DDW パッケージの場合、接合部温度の最初の推定値は次のようになります。

$T_J = T_A + (P_{TOT} \times \theta_{JA}) = 25 + (3.062 \times 22.5) = 93.9^{\circ}C$

PWP パッケージの場合、接合部温度の最初の推定値は次のようになります。

$T_J = T_A + (P_{TOT} \times \theta_{JA}) = 25 + (3.062 \times 24.5) = 100^{\circ}C$

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

25

### **DRV8952**

JAJSL44 – MARCH 2023

より正確な計算を行うには、「代表的な動作特性」セクションに示されている、デバイス接合部温度に対する FET のオン抵抗の依存性を考慮してください。

English Data Sheet: SLOSE83

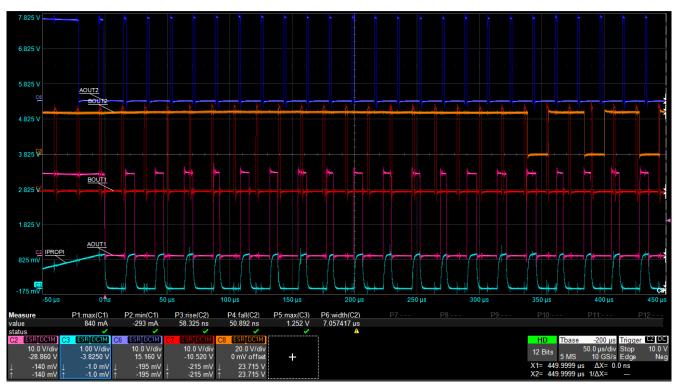

### 8.1.1.3 アプリケーション特性の波形

パターンは上から下へ順に:OUT1、OUT2、OUT3、OUT4、IPROPI1

図 8-2.4 つの負荷を同時に駆動します

パターンは上から下へ順に:OUT1、IOUT1、IN1、IPROPI1

図 8-3. IPROPI 出力による電流レギュレーション

#### 8.1.2 ステッパ・モーターの駆動

DRV8952 は、PWM 入力インターフェイスを使用して 1 つのステッパ・モーターを駆動できます。

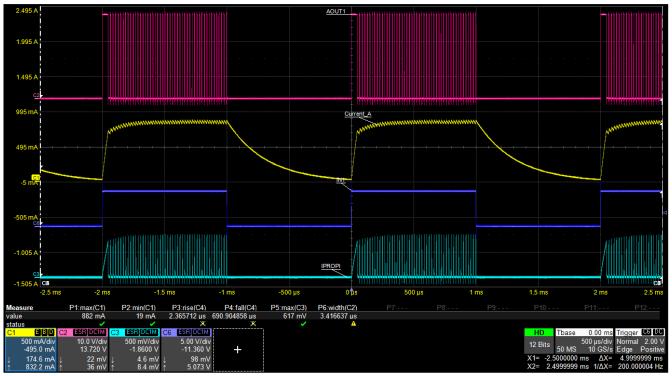

#### 8.1.2.1 ステッパ・ドライバの代表的なアプリケーション

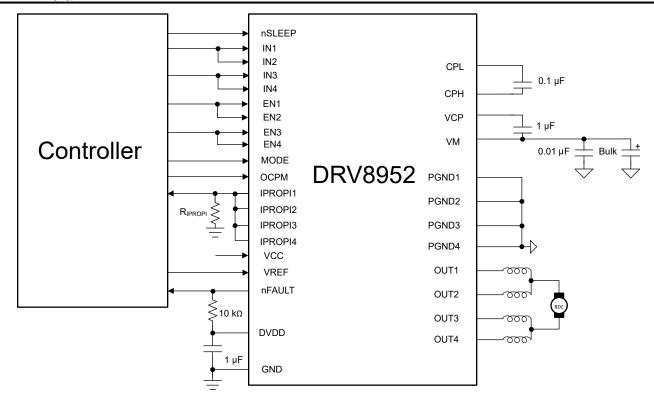

次の回路図は、DRV8952 でステッパ・モーターを駆動するものです。

図 8-4. DRV8952 によるステッパ・モーターの駆動

フルスケール電流 ( $I_{FS}$ ) は、どちらかの巻線によって駆動される最大電流です。この数量は、VREF 電圧と IPROPI ピンからグランドに接続された抵抗 (IPS) は、IPS (IPS) に依存します。 IPS (IPS) ないの最大許容電圧は IPS (IPS) に依存します。 IPS (IPS) ないの最大許容電圧は IPS (IPS) に依存します。 IPS (IPS) は、IPS (

注

モーターを飽和させないように、 $I_{FS}$  電流は 式 5 にも従う必要があります。VM はモーターの電源電圧、 $R_L$  はモーターの巻線の抵抗です。

$$I_{FS}\left(A\right) < \frac{VM\left(V\right)}{R_{L}\left(\Omega\right) + 2 \times R_{DS\left(ON\right)}\left(\Omega\right)}$$

(5)

モーターの目標の速度が高すぎると、モーターは回転しません。モーターが目標の速度に対応できることを確認してください。

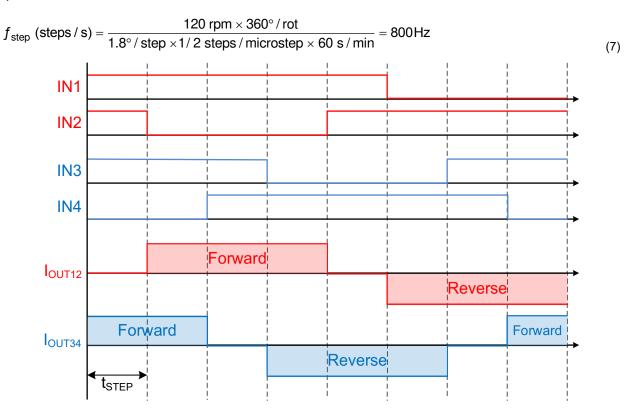

モーターの目標の速度 (V)、マイクロステッピング・レベル ( $n_m$ )、モーターのフルステップ角度 ( $\theta_{step}$ ) を求めるには、入力波形の周波数を次のように決定します。

$$f_{\text{step}} \text{ (steps / s)} = \frac{\text{v (rpm)} \times 360 (^{\circ} / \text{rot})}{\theta_{\text{step}} (^{\circ} / \text{step}) \times n_{\text{m}} \text{ (steps / microstep)} \times 60 \text{ (s / min)}}$$

(6)

$\theta_{\text{step}}$  は、ステッパ・モーターのデータシート、またはモーター自体に記載されています。

周波数  $f_{\text{step}}$  は、DRV8952 の入力の変化の周波数を示します。次の図では、1/  $f_{\text{step}}$  =  $t_{\text{STEP}}$  となります。目標の速度が **120rpm、1/2** ステップでの計算例を、式 7 に示します。

図 8-5. 1/2 ステッピング動作の例

DDW パッケージの場合、同じ H ブリッジに対応する IPROPI 出力を、互いに接続します。 IPROPI1 と IPROPI2 を互い に接続すると、ドライブ・モードと低速減衰 (ハイサイド再循環) モードの間に、ステッパのコイル A の電流 (OUT1 と OUT2 の間に接続)を表します。 同様に、IPROPI3 と IPROPI4 を互いに接続すると、コイル B の電流を表します。 2 つ の IPROPI ピンを互いに接続すると、実効電流ミラー・ゲインは標準値 424µA/A になります。 結合した IPROPI ピンとグ ランドとの間の抵抗は、それに応じて選択します。

#### 8.1.2.2 電力損失の計算

以下の計算では、電源電圧が 24V、フルスケール電流が 5A、立ち上がり / 立ち下がり時間が 140ns、入力 PWM 周波 数が 30kHz の使用事例を想定しています。

全消費電力は主な 3 つの要素 (導通損失 ( $P_{COND}$ )、スイッチング損失 ( $P_{SW}$ )、静止電流による電力損失 ( $P_{O}$ ))で構成さ れます。

導通損失 (P<sub>COND</sub>) は、式8に示すように、モーターの RMS 電流 (I<sub>RMS</sub>)、ハイサイド・オン抵抗 (R<sub>DS(ONH)</sub>)、ローサイド・ オン抵抗 (R<sub>DS(ONL)</sub>) で決まります。

$$P_{COND} = 2 \times (I_{RMS})^2 \times (R_{DS(ONH)} + R_{DS(ONL)})$$

(8)

セクション 8.1.2.1 に示されている代表的なアプリケーションの導通損失は、式9のように計算されます。

$$P_{COND} = 2 \times (I_{RMS})^2 \times (R_{DS(ONH)} + R_{DS(ONL)}) = 2 \times (5A / \sqrt{2})^2 \times (0.112\Omega) = 2.8W$$

(9)

PWM スイッチング周波数に起因する電力損失は、出力電圧の立ち上がり時間 / 立ち下がり時間 (tpr)、電源電圧、モー ターの RMS 電流、PWM スイッチング周波数で決まります。各 H ブリッジの立ち上がり時間と立ち下がり時間のスイッチ ング損失は、式 10 と式 11 のように計算されます。

$$P_{SW\_RISE} = 0.5 \times V_{VM} \times I_{RMS} \times t_{RF} \times f_{PWM}$$

(10)

$$P_{SW FALL} = 0.5 \times V_{VM} \times I_{RMS} \times t_{RF} \times f_{PWM}$$

(11)

各種パラメータの値を代入した後、各 H ブリッジのスイッチング損失は次のように計算されます。

$$P_{SW RISE} = 0.5 \times 24V \times (5A / \sqrt{2}) \times (140ns) \times 30kHz = 0.178W$$

(12)

$$P_{SW FALL} = 0.5 \times 24V \times (5A / \sqrt{2}) \times (100ns) \times 30kHz = 0.178W$$

(13)

ステッパ・モーター・ドライバの合計スイッチング損失 (P<sub>SW</sub>) は立ち上がり時間のスイッチング損失 (P<sub>SW\_RISE</sub>) と立ち下がり時間のスイッチング損失 (P<sub>SW\_FALL</sub>) の和の 2 倍として以下のように計算されます。

$$P_{SW} = 2 \times (P_{SW RISE} + P_{SW FALL}) = 2 \times (0.178W + 0.178W) = 0.712W$$

(14)

注

出力の立ち上がりと立ち下がりの時間  $(t_{RF})$  は、電源電圧、温度、デバイス間のばらつきに基づいて変化すると予想されます。

VCC ピンが外部電圧に接続されているとき、静止電流は標準値で 4mA です。電源電圧によって消費される静止時電流による消費電力は、以下のように計算されます。

$$P_{O} = V_{VM} \times I_{VM} \tag{15}$$

値を代入すると、静止時の電力損失は以下のように計算されます。

$$P_{O} = 24V \times 4mA = 0.096W$$

(16)

注

静止電力損失は、動作電源電流 (I<sub>VM</sub>) の標準値を使用して計算されます。この値は電源電圧、温度、デバイス間のばらつきによって変化します。

全消費電力 (P<sub>TOT</sub>) は導通損失、スイッチング損失、静止電力損失の合計として 式 17 のように計算されます。

$$P_{TOT} = P_{COND} + P_{SW} + P_{Q} = 2.8W + 0.712W + 0.096W = 3.608W$$

(17)

#### 8.1.2.3 接合部温度の推定

周囲温度が T<sub>A</sub>、総消費電力 (P<sub>TOT</sub>) の場合、接合部温度 (T<sub>J</sub>) は次のように計算されます。

$T_J = T_A + (P_{TOT} \times R_{\theta, JA})$

JEDEC 規格の 4 層 PCB の場合を考えると、接合部から周囲への熱抵抗 (R<sub>θJA</sub>) は、DDW パッケージで 22.5℃/W、PWP パッケージで 24.5℃/W です。

周囲温度が 25℃と仮定すると、DDW パッケージの接合部温度は次のように計算されます。

$$T_J = 25^{\circ}C + (3.608W \times 22.5^{\circ}C/W) = 106.2^{\circ}C$$

(18)

PWP パッケージの接合部温度は次のように計算されます。

$$T_J = 25^{\circ}C + (3.608W \times 24.5^{\circ}C/W) = 113.4^{\circ}C$$

(19)

より正確な計算を行うには、「代表的な動作特性」セクションに示されている、デバイス接合部温度に対する FET のオン抵抗の依存性を考慮してください。

### 8.1.3 ブラシ付き DC モーターの駆動

DRV8952 は、1 つまたは 2 つのブラシ付き DC モーターの駆動に使用できます。

#### 8.1.3.1 ブラシ付き DC ドライバの代表的なアプリケーション

次の回路図は、2 つのブラシ付き DC モーターを駆動する DRV8952 を示したものです。

図 8-6. DRV8952 による 2 つのブラシ付き DC モーターの駆動

ブラシ付き DC モーターを制御する方法を、次の真理値表に示します。

表 8-1. ブラシ付き DC モーターの真理値表

| 機能    | EN1 | EN2 | IN1 | IN2 | OUT1 | OUT2 |

|-------|-----|-----|-----|-----|------|------|

| フォワード | 1   | 1   | 1   | PWM | Н    | H/L  |

| リバース  | 1   | 1   | PWM | 1   | H/L  | Н    |

| ブレーキ  | 1   | 1   | 1   | 1   | Н    | Н    |

| ブレーキ* | 1   | 1   | 0   | 0   | L    | L    |

| コースト* | 0   | Х   | X   | X   | Z    | Х    |

| コースト* | ×   | 0   | ×   | ×   | ×    | Z    |

#### 8.1.3.2 電力損失の計算

ハイサイド再循環を使用する H ブリッジの場合、各 FET の消費電力は次のように概算できます。

- $P_{HS1} = R_{DS(ON)} \times I_L^2$   $P_{LS1} = 0$

- $\begin{aligned} &P_{HS2} = [R_{DS(ON)} \times I_L^2 \times (1\text{-}D)] + [2 \times V_D \times I_L \times t_D \times f_{PWM}] \\ &P_{LS2} = [R_{DS(ON)} \times I_L^2 \times D] + [VM \times I_L \times t_{RF} \times f_{PWM}] \end{aligned}$

<sup>\*</sup> DDW パッケージの IPROPI ピンは、これらの条件では比例電流を出力できません。

逆方向の負荷電流フローの消費電力を推定するためにも同じ式が適用されますが、HS1 を HS2 に、LS1 を LS2 に交換します。

上記の式に次の値を代入します。

- VM = 24V

- $I_1 = 4A$

- $R_{DS(ON)} = 56m\Omega$

- D = 0.5

- V<sub>D</sub> = 1V

- $T_D = 300 ns$

- t<sub>RF</sub> = 140ns

- f<sub>PWM</sub> = 20kHz

各 FET での損失は次のように計算できます。

$$P_{HS1} = 56m\Omega \times 4^2 = 0.896W$$

$P_{1,S1} = 0$

$P_{HS2} = [56m\Omega \times 4^2 \times (1-0.5)] + [2 \times 1V \times 4A \times 300ns \times 20kHz] = 0.496W$

$$P_{LS2} = [56m\Omega \times 4^2 \times 0.5] + [24 \times 4A \times 140ns \times 20kHz] = 0.717W$$

静止電流損失 Po = 24V × 4mA = 0.096W

$$P_{TOT} = 2 \times (P_{HS1} + P_{LS1} + P_{HS2} + P_{LS2}) + P_{Q} = 2 \times (0.896 + 0 + 0.496 + 0.717) + 0.096 = 4.314W$$

#### 8.1.3.3 接合部温度の推定

周囲温度が TA、総消費電力 (PTOT) の場合、接合部温度 (T」) は次のように計算されます。

$$T_J = T_A + (P_{TOT} \times R_{\theta JA})$$

JEDEC 規格の 4 層 PCB の場合を考えると、接合部から周囲への熱抵抗 (R<sub>θJA</sub>) は、DDW パッケージで 22.5℃/W、PWP パッケージで 24.5℃/W です。

周囲温度が 25℃と仮定すると、DDW パッケージの接合部温度は次のように計算されます。

$$T_J = 25^{\circ}C + (4.314W \times 22.5^{\circ}C/W) = 122.1^{\circ}C$$

(20)

より精密に計算するには、FET のオン抵抗のデバイス接合部温度に対する依存性を考慮します。

### 8.1.3.4 単一のブラシ付き DC モーターの駆動

DRV8952 の出力を並列に接続して、駆動電流を増やすことができます。 単一のブラシ付き DC モーターを駆動する DRV8952 の回路図を、図 8-7 に示します。

図 8-7. DRV8952 による単一のブラシ付き DC モーターの駆動

このモードでは、出力ピンの後、2 つのチャネルを互いに接続する前に、最小 30nH~100nH のインダクタンス、またはフェライト・ビーズが必要です。これにより、並列チャネルの不整合 (非対称の PCB レイアウトなど) によるスイッチング過渡時に、2 つの並列チャネル間でのシュートスルーを防止できます。

#### 8.1.4 熱電冷却器 (TEC) の駆動

熱電冷却器 (TEC) はペルチェ効果に基いて動作します。TEC の両端に電圧が印加されると、DC 電流が半導体の接合部を流れ、温度差が生じます。熱は、TEC の片側から反対側に伝達されます。これにより、TEC 素子の「高温」側と「低温」側が形成されます。DC 電流が逆になると、高温側と低温側も逆になります。

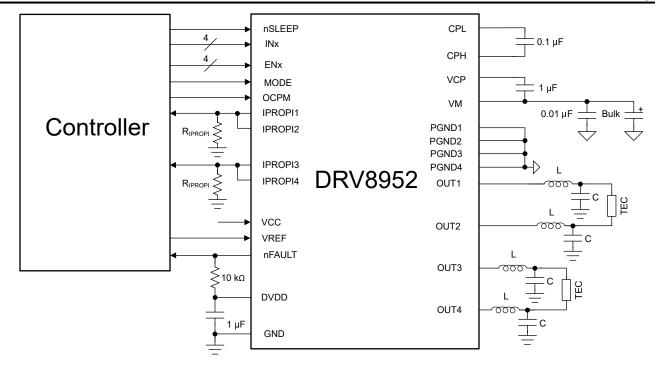

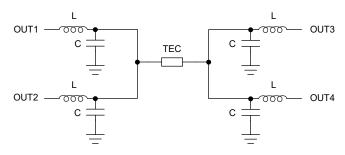

TEC を流れる電流を変調する一般的な方法は、PWM 駆動を使用し、オンとオフのデューティ・サイクルを変えて、平均電流を変化させることです。単一電源で加熱と冷却の両方を可能にするには、H ブリッジ・トポロジが必要です。 DRV8952 は 2 つの H ブリッジを駆動し、最大 5A の電流で 2 つの TEC を双方向駆動できます。 ハーフブリッジのペアを並列接続して、最大 10A の電流で 1 つの TEC を駆動することもできます。

また、DDW パッケージの DRV8952 には 5% の精度を達成する電流検出出力 (IPROPI) も備えているため、閉ループ 制御トポロジで 2 つの外部シャント抵抗が不要になり、部品表のコストとスペースを削減できます。 DRV8952 ドライバに接続された 2 つの TEC の回路図を、図 8-8 に示します。

図 8-8.2 つの TEC の駆動

より大きな電流で 1 つの TEC を駆動する回路図を、図 8-9 に示します。

図 8-9.1 つの TEC を大電流で駆動

出力ノードに接続された LC フィルタは、DRV8952 からの PWM 出力を、TEC 両端の低リップル DC 電圧に変換します。高速過渡 (方形波電力など) により TEC の寿命が短くなる可能性があるため、リップル電流を最小化するにはフィルタが必要です。最大リップル電流は、最大電流の 10% 未満にすることを推奨します。 TEC の最大温度差は、リップル電流が増加すると減少し、次の式で計算されます。

$$\Delta T = \Delta T_{\text{MAX}} / (1 + N^2) \tag{21}$$

ここで、 $\Delta T$  は実際の温度差、 $\Delta T_{MAX}$  は TEC データシートに記載されている可能な最大の温度差、N はリップルと最大電流の比です。n は 0.1 より大きくはしません。

入力 PWM 周波数の選択は、スイッチング損失と、より小型のインダクタおよびコンデンサの使用との間のトレードオフです。また、PWM 周波数が高いと、TEC の両端の電圧を厳密に制御でき、LC コンポーネントのコストを削減できる可能性もあります。

2次ローパス・フィルタの伝達関数を、式21に示します。

$$H(j\omega) = 1 / (1 - (\omega / \omega_0)^2 + j\omega / Q\omega_n)$$

(22)

ここで、

$\omega_0 = 1/\sqrt{(LC)}$ 、フィルタの共振周波数

Q=品質係数

ω=DRV8952 の入力 PWM 周波数

フィルタの共振周波数は通常、PWM 周波数よりも 1 桁以上低い値を選択します。この想定から、式 21 は次のように簡素化できます。

dB 単位の H = -40 log (f<sub>S</sub>/f<sub>0</sub>)

ここで、 $f_0 = 1/2\pi\sqrt{(LC)}$ 、 $f_S$  は入力 PWM スイッチング周波数です。

- L = 10μH、C = 22μF の場合、共振周波数は 10.7kHz です。

- この共振周波数は、100kHz のスイッチング周波数で 39dB の減衰に相当します。

- VM = 24V の場合、39dB の減衰は、TEC 素子の両端におけるリップル電圧の大きさが約 270mV であることを意味します。

- したがって、抵抗が 1.5Ω の TEC 素子の場合、TEC を流れるリップル電流は 180mA になります。

- DRV8952 の最大出力電流 5A では、180mA は 3.6% のリップル電流に相当します。

- これにより、式 21 から TEC 素子の最大温度差が約 0.13% 低減されます。

TEC 素子を通過する電源電圧と DC 電流に応じて LC の値を調整します。 DRV8952 は、最高 200kHz の入力 PWM 周波数をサポートしています。 入力 PWM 周波数を選択する前に、 与えられた周囲温度におけるデバイスの電力損失を慎重に考慮する必要があります。

一部の TEC ベースの冷暖房システムでは、電流ループを閉じることが重要です。DDW パッケージの DRV8952 は、外付けの電流シャント抵抗を使用せずに、この機能を実現できます。内部電流ミラーは各ハーフブリッジの電流を監視するために使用され、この情報は IPROPI ピンで利用できます。マイクロコントローラは、IPROPI ピンの電圧に基づいて PWM デューティを監視および調整できます。2 つの TEC を駆動するときは、対応するハーフブリッジの IPROPI ピンを互いに接続して、H ブリッジ電流を測定します。たとえば、図 8-8 に示す回路図では、IPROPI1 と IPROPI2 が互いに接続され、IPROPI3 と IPROPI4 もまた互いに接続されています。図 8-9 に示すように 1 つの TEC のみを駆動する場合は、すべての IPROPI ピンを互いに接続します。

さらに、DRV8952 は、外部電圧リファレンス (VREF) をデバイスに供給して電流レギュレーションのトリップ・ポイントを調整することにより、内部で電流をレギュレートできます。電流ループはその後、H ブリッジ自体の中で閉じます。

#### 8.1.5 ブラシレス DC モーターの駆動

DRV8952 は、3 相ブラシレス DC (BLDC) モーターの駆動にも使用できます。 DRV8952 では、BLDC モーターの駆動に必要な 3 相を独立に制御できます。 対応する EN ピンをグランドに接続することで、 BLDC モーターの駆動中に DRV8952 の 4 つのハーフブリッジのいずれかをディセーブルできます。 BLDC モーターを駆動する DRV8952 の回路図を、図 8-10 に示します。

図 8-10. DRV8952 による BLDC モーターの駆動

BLDC モーターの駆動に必要な 3 つのハーフブリッジは、EN1、EN2、EN3、IN1、IN2、IN3 の 6 つの入力で制御できます。

- EN1 が Low のとき、OUT1 はハイ・インピーダンスになり、ハイサイドおよびローサイド FET の内部ボディ・ダイオード を電流が流れるようになります。

- EN1 が High で IN1 が Low のとき、OUT1 は Low に駆動され、ローサイド FET がイネーブルになります。

- EN1 が High で IN1 が High のとき、OUT1 は High に駆動され、ハイサイド FET がイネーブルになります。

- OUT2 と OUT3 についても同様です。

- EN4 をグランドに接続すると、OUT4 を永続的にディセーブルできます。

出力ピンの後には、最小 30nH~100nH のインダクタンスまたはフェライト・ビーズを接続する必要があります。これにより、チャネル間の不整合 (プロセスのばらつき、非対称の PCB レイアウトなど) によるシュートスルーを防止できます。

DDW パッケージの IPROPI ピンは、各ハーフブリッジのハイサイド FET を流れる電流に比例した電流を出力します。 最大定格電流での IPROPI 出力の精度は 5% です。

### $I_{PROPI} = I_{HS} \times A_{IPROPI}$

比例電圧 ( $V_{IPROPI}$ ) を IPROPI ピンで生成するには、外付け抵抗 ( $R_{IPROPI}$ ) を介して、各 IPROPI ピンをグランドに接続する必要があります。これにより、標準のアナログ / デジタル・コンバータ (ADC) を使用して、 $R_{IPROPI}$  抵抗両端の電圧降下として負荷電流を測定できます。

### $V_{IPROPI} = IPROPI \times R_{IPROPI}$

電流検出の精度を高める必要がある場合、または PWP パッケージの場合は、PGND ピンとシステム・グランドとの間に外付け検出抵抗を配置できます。外付け検出抵抗の両端での電圧降下は、300mV を超えないようにします。

#### 9 パッケージの熱に関する考慮事項

#### 9.1 DDW パッケージ

データシートに規定されている電力を供給するには、パッケージのサーマル・パッドが PCB の大部分を覆うようにはんだ付けする必要があります。詳細については、セクション 11.1 を参照してください。

#### 9.1.1 熱性能

データシートに規定する接合部から周囲への熱抵抗 R<sub>θJA</sub> は、おもに各種ドライバの比較または熱性能の概算に役立ちます。しかし、実際のシステム性能は、PCB 層構成 (スタックアップ)、配線、ビア数、サーマル・パッド周りの銅面積に応じて、この値よりも良くなったり、悪くなったりします。ドライバが特定の電流を駆動する時間の長さもまた、消費電力や熱性能に影響を与えます。ここでは、定常状態および過渡熱条件での設計方法について考察します。

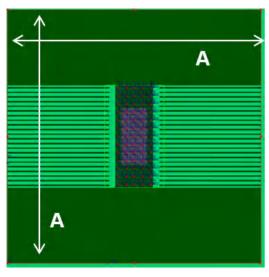

このセクションのデータは、次の基準を使用してシミュレーションしたものです。

#### HTSSOP (DDW パッケージ)

- 2 層 PCB (サイズ 114.3 x 76.2 x 1.6mm)、標準 FR4、1oz (35μm 銅箔厚) または 2oz 銅箔厚。 サーマル・ビアはサーマル・パッドの下にのみ配置 (13 x 5 個のサーマル・ビア・アレイ、1.1mm 間隔、0.2mm 直径、0.025mm 銅メッキ)。

- 上層:HTSSOP パッケージ・フットプリントと銅プレーン・ヒートシンク。シミュレーションでは、上層の銅箔面積を変化させています。

- 下層:ドライバのサーマル・パッド下のビアで熱的に接続されたグランド・プレーン。下層の銅箔面積は上層の銅箔面積によって変化します。

- 4層 PCB (サイズ 114.3 x 76.2 x 1.6mm)、標準 FR4。外側のプレーンは 1oz (35 $\mu$ m 銅箔厚) または 2oz 銅箔厚。 内側のプレーンは 1oz で一定。サーマル・ビアはサーマル・パッドの下にのみ配置 (13 x 5 個のサーマル・ビア・アレイ、1.1mm 間隔、0.2mm 直径、0.025mm 銅メッキ)。

- 上層:HTSSOP パッケージ・フットプリントと銅プレーン・ヒートシンク。シミュレーションでは、上層の銅箔面積を変化させています。

- 中間層 1:サーマル・パッドとビアで熱的に接続された GND プレーン。グランド・プレーンの面積は、上層の銅箔面積によって異なります。

- 中間層 2:電源プレーン、熱的接続なし。電源プレーンの面積は、上層の銅箔面積によって異なります。

- 下層: TOP および内部 GND プレーンからビア・スティッチで熱的に接続された信号層。下層のサーマル・パッドは上層の銅箔面積と同じサイズ。

DDW パッケージについてシミュレーションした基板の例を 図 9-1 に示します。表 9-1 に、各シミュレーションで変化させた基板の寸法を示します。

図 9-1. DDW の PCB モデルの上層

Product Folder Links: DRV8952

表 9-1. DDW パッケージの寸法 A

| 銅 (Cu) 面積 (cm²) | 寸法 A (mm) |  |  |  |  |

|-----------------|-----------|--|--|--|--|

| 2               | 19.79     |  |  |  |  |

| 4               | 26.07     |  |  |  |  |

| 8               | 34.63     |  |  |  |  |

| 16              | 46.54     |  |  |  |  |

| 32              | 63.25     |  |  |  |  |

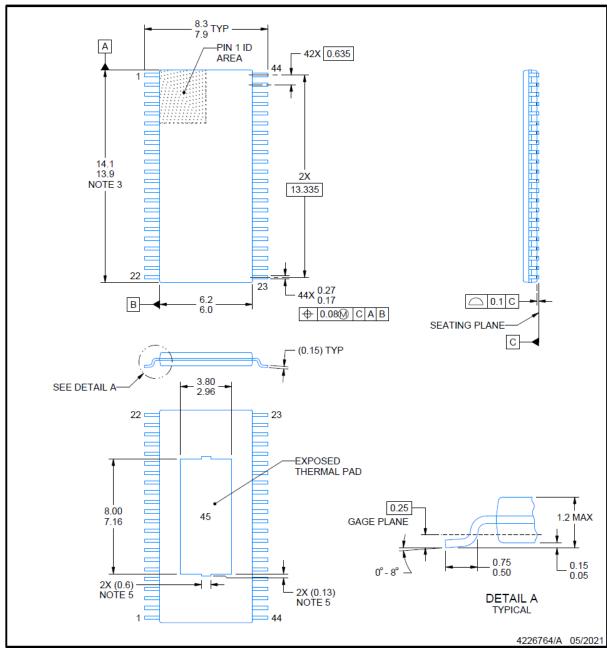

#### 9.1.1.1 定常状態熱性能

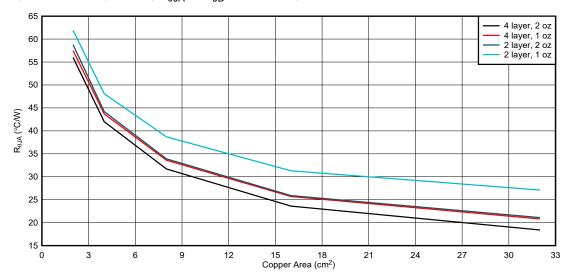

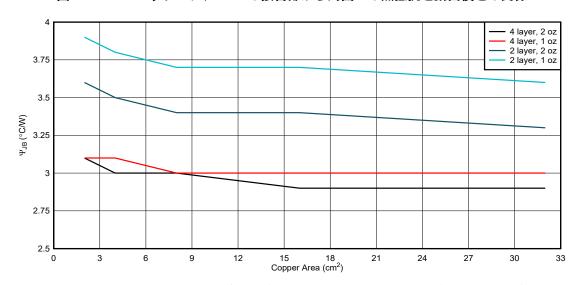

「定常状態条件」とは、ドライバが長時間にわたって一定の RMS 電流で動作することを指します。このセクションの図は、 銅面積、銅厚、PCB 層数に応じた  $R_{\theta JA}$  と  $\Psi_{JB}$  (接合部から基板への熱特性) の変化を示しています。 銅面積が大きく、 層数が多く、 銅プレーンが厚いほど、  $R_{\theta JA}$  と  $\Psi_{JB}$  は小さくなり、 PCB レイアウトの熱性能が高くなることを示しています。

図 9-2. DDW パッケージ、PCB の接合部から周囲への熱抵抗と銅面積との関係

図 9-3. DDW パッケージ、接合部から基板への特性パラメータと銅面積との関係

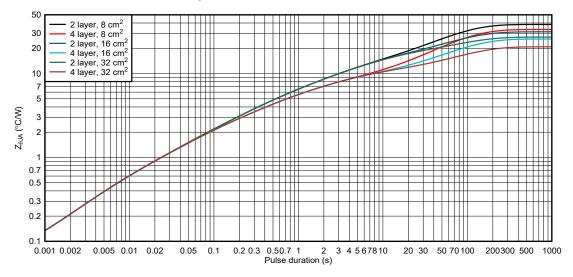

9.1.1.2 過渡熱性能

ドライバは、短時間に大きな電流が流れるさまざまな過渡駆動条件になる可能性があります。たとえば、次のような条件があります。

- ローターが最初に静止しているときのモータ起動。

- 電源またはグランドがモータの出力のいずれかに短絡し、過電流保護がトリガされるフォルト条件。

- モータまたはソレノイドが短時間駆動された後、解放される。

このような過渡条件では、銅の面積や厚さに加えて、駆動時間も熱性能に影響を与えます。過渡条件の場合、熱インピーダンス (Z<sub>6JA</sub>) パラメータは、接合部から周囲への熱性能を示します。このセクションの図は、DDW パッケージの 1oz および 2oz の銅レイアウトの熱インピーダンスをシミュレートしたものです。これらのグラフは、短い電流パルスで熱性能が高くなることを示しています。駆動時間が短い場合、本デバイスのダイ・サイズとパッケージが熱性能を支配します。より長いドライブ・パルスの場合、基板レイアウトが熱性能により大きな影響を与えます。どちらのグラフの熱インピーダンス曲線も、ドライブ・パルス期間が長くなるに従って層数と銅面積に応じた差が観測されることを示しています。長いパルスの場合、定常状態の性能になるとみなすことができます。

図 9-4. DDW パッケージと 1oz 銅レイアウトでの、接合部から周囲への熱インピーダンス

図 9-5. DDW パッケージと 2oz 銅レイアウトでの、接合部から周囲への熱インピーダンス

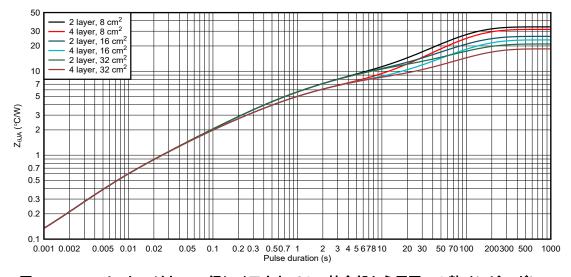

#### 10 電源に関する推奨事項

DRV8952 は、4.5V~55V の入力電源電圧 (VM) 範囲で動作するように設計されています。 VM 定格の 0.01µF セラミッ ク・コンデンサを、DRV8952 の VM ピンの近くに配置する必要があります。 また、バルク・コンデンサを VM に接続する必 要があります。

#### 10.1 バルク容量

システムの設計では、適切なローカル・バルク容量が重要な要素です。一般に、バルク容量が大きいほど利点があります が、コストと物理的なサイズが増加します。

必要なローカル容量は、次のようなさまざまな要因で決まります。

- システムで必要な最大電流

- 電源容量 (電流供給能力)

- 電源とシステムとの間にある寄生インダクタンスの大きさ

- 許容される電圧リップル

電源とモーター駆動システムの間のインダクタンスにより、電源からの電流が変化する速度が制限されます。ローカル・バ ルク容量が小さすぎると、大電流を供給しようとする場合、またはダンプが発生した場合、システムの電圧が変動します。 十分なバルク容量を備えることで、電圧は安定し、大電流を素早く供給できます。

データシートには一般に、推奨値が記載されていますが、バルク・コンデンサの容量が適切かどうかを判断するには、シス テム・レベルのテストが必要です。

モーターが電源にエネルギーを伝達する場合のマージンを確保するため、バルク・コンデンサの定格電圧は動作電圧より 高くする必要があります。

図 10-1. 外部電源を持つシステムの構成例

#### 10.2 電源

40

DRV8952 は、VM ピンに接続された単一の電源電圧のみで動作します。

- VM ピンは、ハーフブリッジに電源を供給します。

- 内部電圧レギュレータは、デジタルおよび低電圧アナログ回路に 5V 電源 (DVDD) を供給します。 DVDD ピンを外部 回路の電圧源として使用することは推奨しません。

- DDW パッケージの場合、外部低電圧電源を VCC ピンに接続することで、内部回路に電力を供給することができま す。過渡時に一定の電圧を供給するため、0.1μF のデカップリング・コンデンサを VCC ピンの近くに配置する必要が あります。

- さらに、ハイサイド・ゲート・ドライブには、より高い電圧の電源が必要です。この電源は内蔵のチャージ・ポンプによっ て生成され、外付けのコンデンサが必要です。

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

#### 11 レイアウト

#### 11.1 レイアウトのガイドライン

- VM 定格の低 ESR セラミック・バイパス・コンデンサを推奨値 0.01µF で使用して、VM ピンを PGND にバイパスする 必要があります。このコンデンサは VM ピンのできるだけ近くに配置し、太いパターンまたはグランド・プレーンでデバイスの PGND ピンに接続する必要があります。

- VM 定格のバルク・コンデンサを使用して、VM ピンを PGND にバイパスする必要があります。この部品には電解コンデンサが使用できます。

- 低 ESR セラミック・コンデンサを CPL ピンと CPH ピンの間に配置する必要があります。 VM 定格の 0.1µF を推奨します。 この部品はピンにできるだけ近付けて配置します。

- 低 ESR セラミック・コンデンサを VM ピンと VCP ピンの間に配置する必要があります。16V 定格の 1µF を推奨します。この部品はピンにできるだけ近付けて配置します。

- 低 ESR セラミック・コンデンサを使用して、DVDD ピンをグランドにバイパスします。 6.3V 定格の 1μF を推奨します。 このバイパス・コンデンサはピンにできるだけ近付けて配置します。

- DDW パッケージの場合、低 ESR セラミック・コンデンサを使用して、VCC ピンをグランドにバイパスします。 6.3V 定格の 0.1µF を推奨します。 このバイパス・コンデンサはピンにできるだけ近付けて配置します。

- 一般に、電源ピンとデカップリング・コンデンサの間のインダクタンスを防ぐ必要があります。

- サーマル・パッドはシステム・グランドに接続する必要があります。

- システムや基板全体には、大きく、切れ目のない単一のグランド・プレーンを使用することを推奨します。グランド・プレーンは PCB の下層に作成できます。

- インピーダンスとインダクタンスを最小化するため、グランド・ピンからビアを経由して下層のグランド・プレーンに接続する配線は、できる限り短く、幅広くする必要があります。

- インピーダンスを低減するために、複数のビアを推奨します。

- 熱の拡散を改善するために、デバイスの周囲のスペースをできるだけ大きく、特に PCB の下層に確保してください。

- サーマル・パッドを単一または複数の内部グランド・プレーンに接続することでも、熱の拡散と熱抵抗の低減に役立ちます。

#### 11.2 PCB 材料に関する推奨事項

放熱性能を向上させ、EMI マージンを改善するために、上層と下層の両方に FR-4 ガラス・エポキシ材料、2 オンス (70μm) の銅を用いることを推奨します (PCB パターンのインダクタンスが低いため)。

#### 11.3 熱に関する注意事項

パッケージのサーマル・パッドは、熱能力を向上させるため、デバイスの底面に取り付けられています。データシートに規定されている電力を供給するには、サーマル・パッドが PCB の大部分を覆うようにはんだ付けする必要があります。詳細については、セクション 11.1 を参照してください。

Product Folder Links: DRV8952

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

4

#### 12 デバイスおよびドキュメントのサポート

テキサス・インスツルメンツでは、幅広い開発ツールを提供しています。デバイスの性能の評価、コードの生成、ソリューションの開発を行うためのツールとソフトウェアを、以下で紹介します。

#### 12.1 関連資料

- テキサス・インスツルメンツ、『DRV8xxx によるユニポーラ・ステッパ・モーターの駆動方法』アプリケーション・レポート

- テキサス・インスツルメンツ、『モーター・ドライバの消費電力の計算』アプリケーション・レポート

- テキサス・インスツルメンツ、『電流再循環および減衰モード』アプリケーション・レポート

- テキサス・インスツルメンツ、『モーター・ドライバの電流定格の理解』アプリケーション・レポート

- テキサス・インスツルメンツ、『モーター・ドライブのレイアウト・ガイド』アプリケーション・レポート

- テキサス・インスツルメンツ、『半導体および IC パッケージの熱評価基準』アプリケーション・レポート

- テキサス・インスツルメンツ、『TEC の駆動で検討すべきモーター・ドライバ』

#### 12.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 12.3 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 12.4 商標

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 12.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 12.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLOSE83

#### 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスについて利用可能な最新のデータです。このデータは、予告なしに、また、ドキュメントの改訂なしに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

Product Folder Links: DRV8952

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

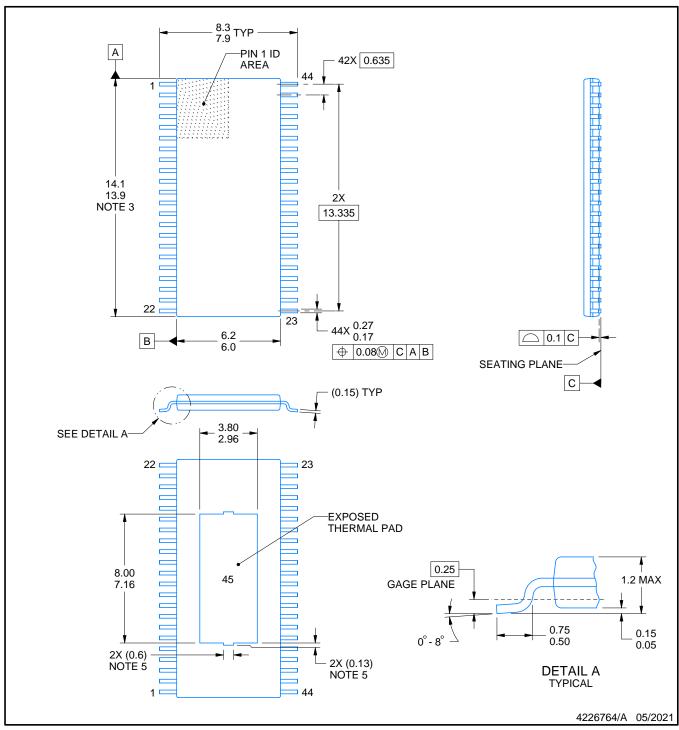

**DDW0044E**

#### PACKAGE OUTLINE

#### PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolera per ASME Y14.5M.

This drawing is subject to change without notice.

This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

Reference JEDEC registration MO-153.

Features may differ or may not be present.

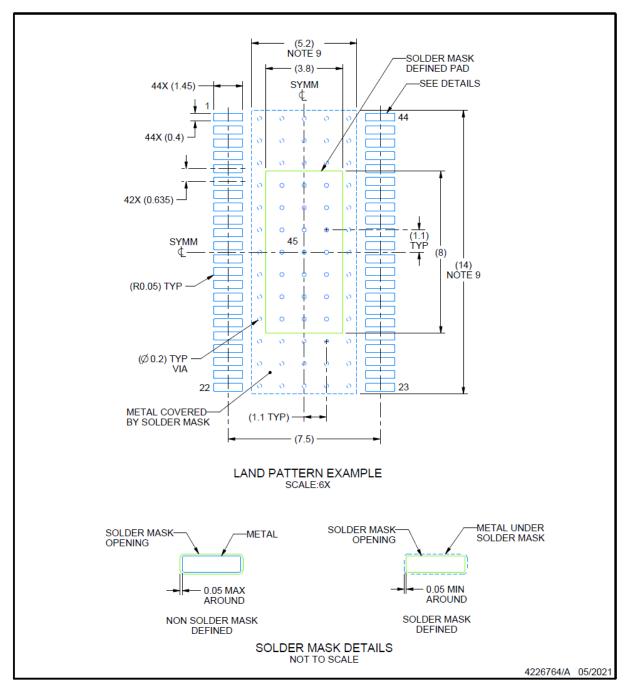

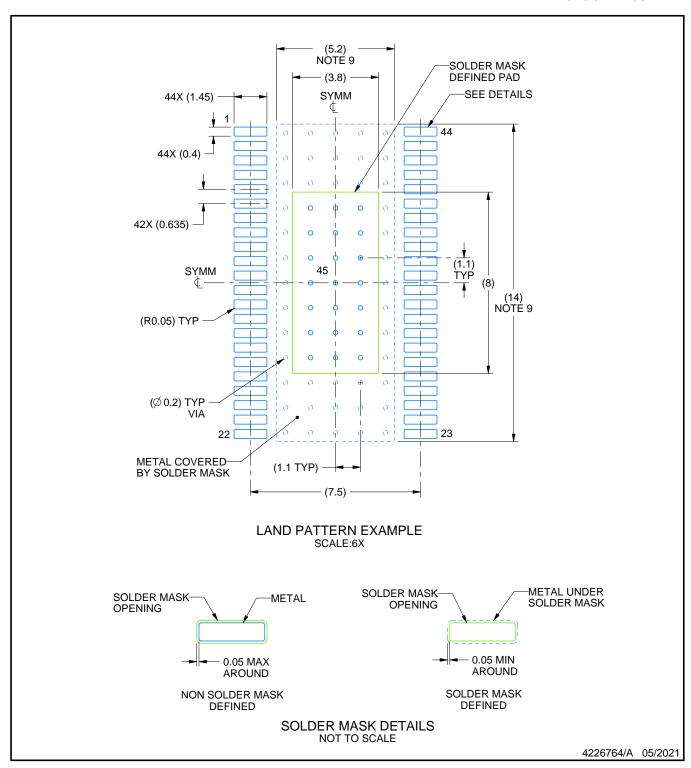

#### **EXAMPLE BOARD LAYOUT**

#### **DDW0044E**

#### PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

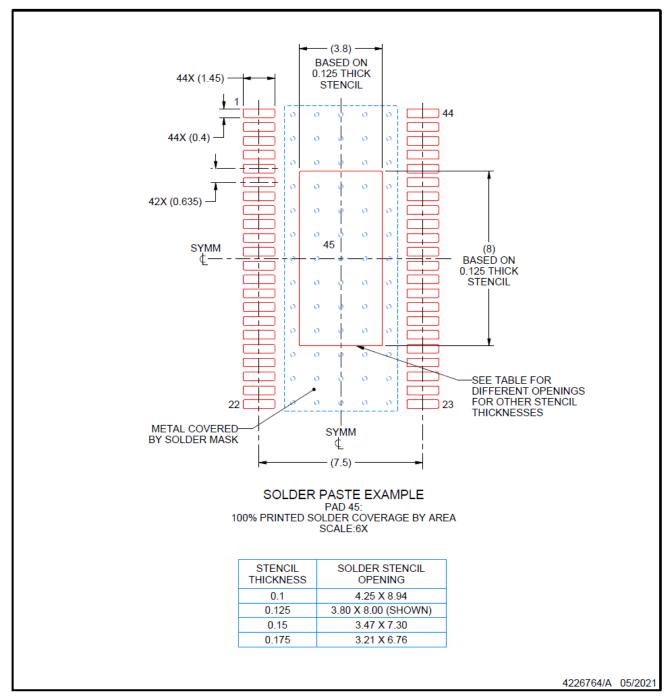

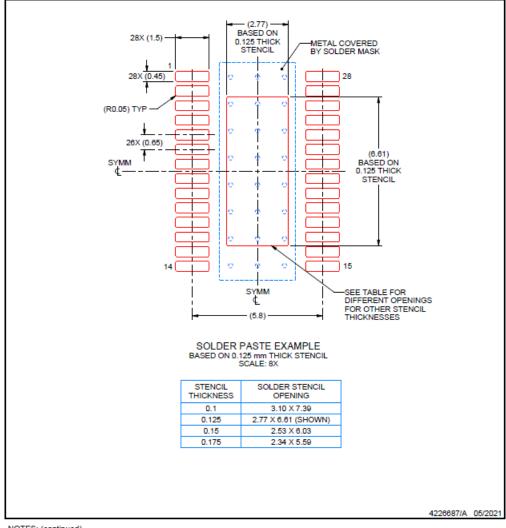

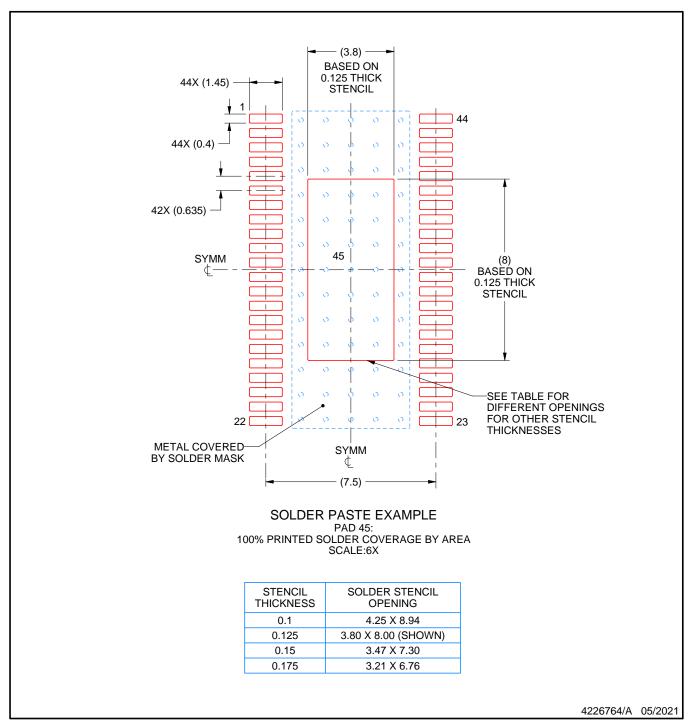

#### **EXAMPLE STENCIL DESIGN**

### **DDW0044E**

#### PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

<sup>11.</sup> Board assembly site may have different recommendations for stencil design.

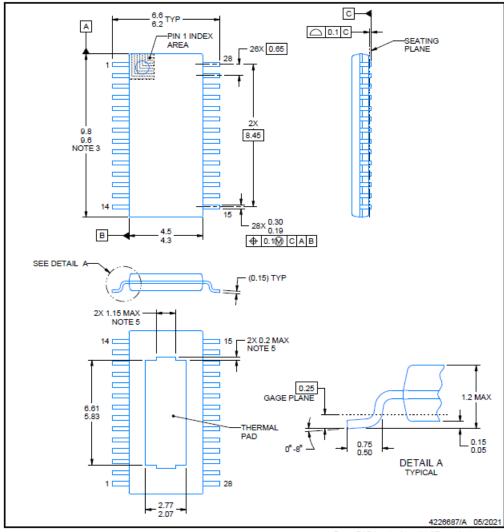

## **PWP0028T**

#### PACKAGE OUTLINE

#### PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

This drawing is subject to change without notice.

This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

Reference JEDEC registration MO-153.

- 5. Features may differ or may not be present.

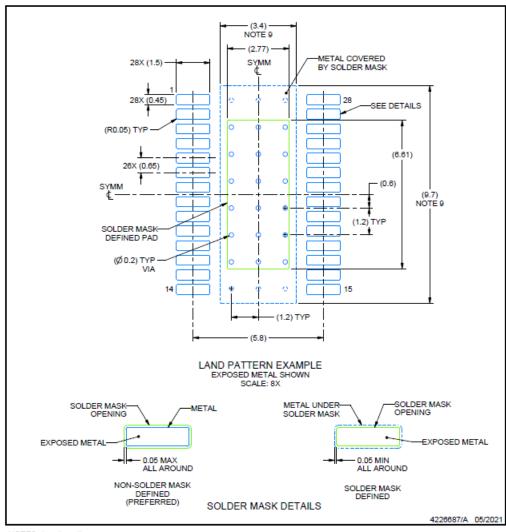

#### EXAMPLE BOARD LAYOUT

#### **PWP0028T**

#### PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- Notification to Order may have attended easigns.

Solder mask tolerances between and around signal pads can vary based on board fabrication site.

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- Size of metal pad may vary due to creepage requirement.

Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged. or tented.

Product Folder Links: DRV8952

#### **EXAMPLE STENCIL DESIGN**

#### **PWP0028T**

#### PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate

design recommendations.

Board assembly site may have different recommendations for stencil design.

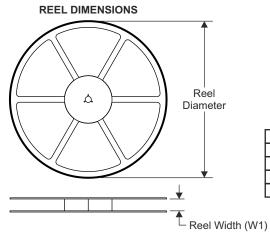

#### 13.1 テープおよびリール情報

# TAPE DIMENSIONS KO P1 BO W Cavity A0

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | ·                                                         |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    |                                                           |

#### **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

パッケージ ・タイプ パッケージ 図 リール 直径 (mm) リール 幅 W1 (mm) A0 B0 K0 P1 w Pin1の デバイス ピン数 SPQ (mm) (mm) (mm) (mm) (mm) 象限 DRV8952PWPR HTSSOP 28 2500 330.0 16.4 6.75 10.1 1.8 12 16 Q1 DRV8952DDWR HTSSOP DDW 2500 330.0 24.4 8.9 1.4 12 24 Q1

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLOSE83

| デバイス        | パッケージ・タイプ | パッケージ図 | ピン<br>数 | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |  |

|-------------|-----------|--------|---------|------|---------|--------|---------|--|

| DRV8952PWPR | HTSSOP    | PWP    | 28      | 2500 | 356.0   | 356.0  | 35.0    |  |

| DRV8952DDWR | HTSSOP    | DDW    | 44      | 2500 | 367.0   | 367.0  | 45.0    |  |

English Data Sheet: SLOSE83

www.ti.com 1-Apr-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| DRV8952DDWR      | ACTIVE | HTSSOP       | DDW                | 44   | 2500           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | DRV8952              | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

6.1 x 14, 0.635 mm pitch

PLASTIC SMALL OUTLINE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

www.ti.com

PLASTIC SMALL OUTLINE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- 4. Reference JEDEC registration MO-153.

- 5. Features may differ or may not be present.

PLASTIC SMALL OUTLINE

- 6. Publication IPC-7351 may have alternate designs.

- Solder mask tolerances between and around signal pads can vary based on board fabrication site.

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

PLASTIC SMALL OUTLINE

- 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 11. Board assembly site may have different recommendations for stencil design.

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated