🕳 Order

Now

#### DS90LV049H

参考資料

JAJSGU8B-SEPTEMBER 2005-REVISED JANUARY 2019

Support &

Community

22

# DS90LV049H 高温対応 3V LVDS デュアル・ライン・ドライバおよびレ シーバ・ペア

Technical

Documents

- 1 特長

- 高温 (+125°C) 動作に対応

- 最高 400Mbps のスイッチング速度

- フロースルーのピン配置によりPCBレイアウトを 簡素化

- ドライバのチャネル間スキュー:50ps (標準値)

- レシーバのチャネル間スキュー:50ps (標準値)

- 3.3V 単一電源設計

- TRI-STATE 出力制御

- レシーバ入力に内部でフェイルセーフ・バイアス を印加

- 低消費電力:70mW (3.3V 固定)

- 電源オフ時に LVDS 出力が高インピーダンス

- TIA/EIA-644-A LVDS 規格に準拠

- 低背型の 16 ピン TSSOP パッケージで供給

- 2 アプリケーション

- 基板間通信

- 試験/測定機器

- モータ駆動

- LED ビデオ・ウォール

- ワイヤレス・インフラ

- 通信インフラ

- 多機能プリンタ

- NIC カード

- ラック・サーバー

- 超音波スキャナ

#### 3 概要

🥭 Tools &

Software

DS90LV049Hは、超低消費電力、非常に優れたノイズ耐性、高いデータ・スループットを必要とするアプリケーション用に設計された、デュアル CMOS 差動ライン・ドライバ /レシーバ・ペアです。このデバイスは、低電圧差動信号 (LVDS) テクノロジを活用し、400Mbps を超えるデータ速度をサポートするよう設計されています。DS90LV049Hは TSSOP パッケージを採用しているため、PCB レイアウト が簡単なフロー・スルー配線が可能です。

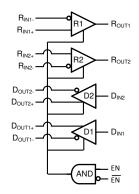

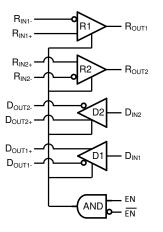

DS90LV049H のドライバは LVTTL/LVCMOS 信号を受け取り、LVDS 信号に変換します。レシーバは LVDS 信号を受け取り、3V CMOS 信号に変換します。LVDS 入力バッファはフェイルセーフ・バイアスを内蔵しており、レシーバ入力がフローティングの場合、出力を既知の H (HIGH) 状態にします。さらに、DS90LV049H は TRI-STATE 機能をサポートしており、デバイスが使用されていないときは低消費電力のアイドル状態に移行します。

EN および EN 入力は互いに AND 接続され、TRI-STATE 出力を制御します。イネーブルは 4 つのゲートす べてに共通です。

#### 製品情報<sup>(1)</sup>

| 型番         | パッケージ      | 本体サイズ(公称)     |

|------------|------------|---------------|

| DS90LV049H | TSSOP (16) | 5.00mm×4.40mm |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にある注文情報を参照してください。

#### 機能図

# 目次

9

9.1

12.4

| 1 | 特長   |                                    |

|---|------|------------------------------------|

| 2 | アプ   | リケーション1                            |

| 3 | 概要   | <sup>[</sup> 1                     |

| 4 | 改訂   | 7履歴2                               |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 4                      |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 4              |

|   | 6.5  | Electrical Characteristics 5       |

|   | 6.6  | Switching Characteristics 6        |

|   | 6.7  | Typical Characteristics 7          |

| 7 | Para | ameter Measurement Information7    |

| 8 | Deta | ailed Description 11               |

|   | 8.1  | Overview 11                        |

|   | 8.2  | Functional Block Diagram 11        |

|   | 7427 | ल्ल क |

|---|------|-------|

| 4 | 改訂   | 腹歴    |

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Revision A (April 2013) から Revision B に変更

| • | 「製品情報」表、「製品比較」表、「ESD定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーショ<br>ンと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セ |     |

|---|------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | クション、「メカニカル、パッケージ、および注文情報」セクションを追加                                                                                                 | . 1 |

| • | データシートのページの上端にナビゲーション・リンクを追加し、NRND バナーを削除                                                                                          | . 1 |

| • | Moved the thermal resistance ( $\theta_{JA}$ ) parameter in the Absolute Maximum Ratings table to the Thermal Information          |     |

| 2013年4月発行のものから更新 | Page |

|------------------|------|

8.3 Feature Description..... 11 8.4 Device Functional Modes...... 13 Application and Implementation ...... 14

Application Information..... 14 9.2 Typical Application ...... 14 10 Power Supply Recommendations ...... 17 11.1 Layout Guidelines ..... 17 11.2 Layout Example ..... 21 12 デバイスおよびドキュメントのサポート ...... 22 12.1 関連資料 ...... 22 12.2 ドキュメントの更新通知を受け取る方法...... 22 12.3 コミュニティ・リソース...... 22

商標......22 12.5 静電気放電に関する注意事項 ...... 22 12.6 Glossary ...... 22 13 メカニカル、パッケージ、および注文情報 ...... 22

Page

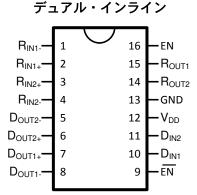

# 5 Pin Configuration and Functions

| PW Package<br>16-Pin TSSOP<br>Top View |   |                    |                    |  |

|----------------------------------------|---|--------------------|--------------------|--|

| R <sub>IN1-</sub>                      | 1 | $\mathcal{I}_{16}$ | FN                 |  |

| R <sub>IN1+</sub>                      | 2 | 15                 | -R <sub>OUT1</sub> |  |

| R <sub>IN2+</sub>                      | 3 | 14                 | -R <sub>OUT2</sub> |  |

| R <sub>IN2</sub> -                     | 4 | 13                 | -GND               |  |

| D <sub>OUT2</sub> .                    | 5 | 12                 | -V <sub>DD</sub>   |  |

| D <sub>OUT2+</sub>                     | 6 | 11                 | -D <sub>IN2</sub>  |  |

| D <sub>OUT1+</sub>                     | 7 | 10                 | -D <sub>IN1</sub>  |  |

| D <sub>OUT1</sub> .                    | 8 | 9                  | - EN               |  |

|                                        |   |                    |                    |  |

#### **Pin Functions**

|                   | PIN I/O |     | DESCRIPTION                                                                              |  |  |

|-------------------|---------|-----|------------------------------------------------------------------------------------------|--|--|

| NAME NO.          |         | 1/0 | DESCRIPTION                                                                              |  |  |

| D <sub>IN</sub>   | 10, 11  | I   | Driver input pins, LVCMOS levels. There is a pulldown current source present.            |  |  |

| D <sub>OUT+</sub> | 6, 7    | 0   | Noninverting driver output pins, LVDS levels.                                            |  |  |

| D <sub>OUT-</sub> | 5, 8    | 0   | Inverting driver output pins, LVDS levels.                                               |  |  |

| R <sub>IN+</sub>  | 2, 3    | I   | Noninverting receiver input pins, LVDS levels. There is a pullup current source present. |  |  |

| R <sub>IN-</sub>  | 1, 4    | I   | Inverting receiver input pins, LVDS levels. There is a pulldown current source present.  |  |  |

| R <sub>OUT</sub>  | 14, 15  | 0   | Receiver output pins, LVCMOS levels.                                                     |  |  |

| EN, EN            | 9, 16   | I   | Enable and Disable pins. There are pulldown current sources present at both pins.        |  |  |

| V <sub>DD</sub>   | 12      | I   | Power supply pin.                                                                        |  |  |

| GND               | 13      | I   | Ground pin.                                                                              |  |  |

STRUMENTS

XAS

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                                                                     |                                       | MIN  | MAX                     | UNIT  |

|-------------------------------------------------------------------------------------|---------------------------------------|------|-------------------------|-------|

| Supply Voltage (V <sub>DD</sub> )                                                   |                                       | -0.3 | 4                       | V     |

| LVCMOS Input Voltage (DIN)                                                          |                                       | -0.3 | (V <sub>DD</sub> + 0.3) | V     |

| LVDS Input Voltage (R <sub>IN+</sub> , R <sub>IN-</sub> )                           |                                       | -0.3 |                         | V     |

| Enable Input Voltage (EN, EN)                                                       |                                       | -0.3 | (V <sub>DD</sub> + 0.3) | V     |

| LVCMOS Output Voltage (R <sub>OUT</sub> )                                           |                                       | -0.3 | (V <sub>DD</sub> + 0.3) | V     |

| LVDS Output Voltage (D <sub>OUT+</sub> , D <sub>OUT-</sub> )                        |                                       | -0.3 | 3.9                     | V     |

| LVCMOS Output Short Circuit Current (R <sub>OUT</sub> )                             |                                       |      | 100                     | mA    |

| LVDS Output Short Circuit Current (D <sub>OUT+</sub> , D <sub>OUT-</sub> )          |                                       |      | 24                      | mA    |

| LVDS Output Short Circuit Current Duration (D <sub>OUT+</sub> , D <sub>OUT-</sub> ) |                                       | Cont | Continuous              |       |

| Lead Temperature Range                                                              | Soldering (4 sec.)                    |      | 260                     | °C    |

| Maximum Junction Temperature                                                        |                                       |      | 150                     | °C    |

| Maximum Package Power                                                               | PW0016A Package                       |      | 866                     | mW    |

| Dissipation at +25°C                                                                | Derate PW0016A Package ( above +25°C) |      | 6.9                     | mW/°C |

| Storage Temperature, T <sub>stg</sub>                                               |                                       | -65  | 150                     | °C    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

## 6.2 ESD Ratings

|                    |                         |                                                                                      | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 $^{(1)}$ (1.5 k $\Omega,$ 100 pF) | 7000  | V    |

| (_32)              | -                       | (MM, 0 Ω, 200 pF)                                                                    | 250   |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±7000 V may actually have higher performance.

### 6.3 Recommended Operating Conditions

|                                        | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------|------|------|------|------|

| Supply Voltage (V <sub>DD</sub> )      | +3.0 | +3.3 | +3.6 | V    |

| Ambient Temperature (T <sub>A</sub> )  | -40  | 25   | +125 | °C   |

| Junction Temperature (T <sub>J</sub> ) |      |      | +130 | °C   |

### 6.4 Thermal Information

|                      |                                              | DS90LV049H |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                      |                                              | 16 PINS    | -    |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 109.9      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 40.8       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 57         | °C/W |

| ΨJT                  | Junction-to-top characterization parameter   | 4.4        | °C/W |

| ΨJB                  | Junction-to-board characterization parameter | 56.3       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.5 Electrical Characteristics

Over supply voltage and operating temperature ranges, unless otherwise specified. (1)(2)(3)

|                  | PARAMETER                                                                 | TEST CONDITIONS                                                     | PIN                                    | MIN   | TYP  | MAX             | UNIT |

|------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------|-------|------|-----------------|------|

| LVCMOS           | Input DC Specifications (Driver Inpu                                      | ts, ENABLE Pins)                                                    |                                        |       |      | I               |      |

| VIH              | Input High Voltage                                                        |                                                                     |                                        | 2     |      | V <sub>DD</sub> | V    |

| V <sub>IL</sub>  | Input Low Voltage                                                         |                                                                     | D <sub>IN</sub>                        | GND   |      | 0.8             | V    |

| IIH              | Input High Current                                                        | $V_{IN} = V_{DD}$                                                   | EN                                     | -10   | 1    | +10             | μA   |

| IIL              | Input Low Current                                                         | V <sub>IN</sub> = GND                                               | EN                                     | -10   | -0.1 | +10             | μA   |

| V <sub>CL</sub>  | Input Clamp Voltage                                                       | I <sub>CL</sub> = −18 mA                                            |                                        | -1.5  | -0.6 |                 | V    |

| LVDS Ou          | Itput DC Specifications (Driver Output                                    | ts)                                                                 |                                        |       |      |                 |      |

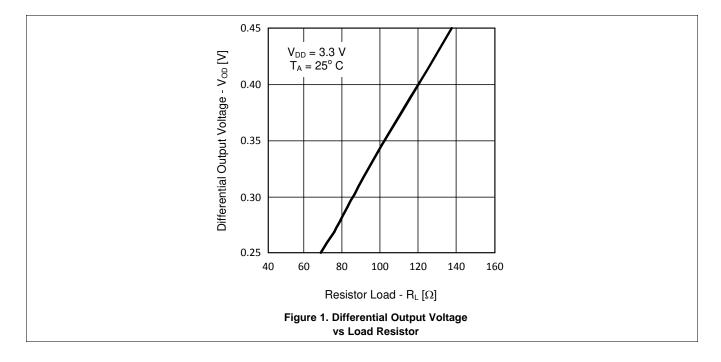

| V <sub>OD</sub>  | Differential Output Voltage                                               |                                                                     |                                        | 250   | 350  | 450             | mV   |

| ΔV <sub>OD</sub> | Change in Magnitude of V <sub>OD</sub> for<br>Complementary Output States | R <sub>L</sub> = 100 Ω                                              |                                        |       | 1    | 35              | mV   |

| V <sub>OS</sub>  | Offset Voltage                                                            | (Figure 2)                                                          |                                        | 1.125 | 1.23 | 1.375           | V    |

| ΔV <sub>OS</sub> | Change in Magnitude of V <sub>OS</sub> for<br>Complementary Output States |                                                                     |                                        |       | 1    | 25              | mV   |

| I <sub>OS</sub>  | Output Short-Circuit Current <sup>(4)</sup>                               |                                                                     | D <sub>OUT-</sub><br>D <sub>OUT+</sub> |       | -5.8 | -9              | mA   |

| I <sub>OSD</sub> | Differential Output Short-Circuit Current <sup>(4)</sup>                  | ENABLED, V <sub>OD</sub> = 0 V                                      |                                        |       | -5.8 | -9              | mA   |

| I <sub>OFF</sub> | Power-off Leakage                                                         | $V_{OUT} = 0 V \text{ or } 3.6 V$<br>$V_{DD} = 0 V \text{ or Open}$ |                                        | -20   | ±1   | +20             | μA   |

| I <sub>OZ</sub>  | Output TRI-STATE Current                                                  | $EN = 0 V and \overline{EN} = V_{DD}$<br>$V_{OUT} = 0 V or V_{DD}$  |                                        | -10   | ±1   | +10             | μA   |

| LVDS Inp         | out DC Specifications (Receiver Input                                     | s)                                                                  |                                        |       |      |                 |      |

| V <sub>TH</sub>  | Differential Input High Threshold                                         |                                                                     |                                        |       | -15  | 35              | mV   |

| V <sub>TL</sub>  | Differential Input Low Threshold                                          | V <sub>CM</sub> = 1.2 V, 0.05 V, 2.35 V                             |                                        | -100  | -15  |                 | mV   |

| V <sub>CMR</sub> | Common-Mode Voltage Range                                                 | V <sub>ID</sub> = 100 mV, V <sub>DD</sub> =3.3 V                    | R <sub>IN+</sub>                       | 0.05  |      | 3               | V    |

|                  | Input Current                                                             | V <sub>DD</sub> =3.6 V<br>V <sub>IN</sub> =0 V or 2.8 V             | R <sub>IN-</sub>                       | -12   | ±4   | +12             | μA   |

| I <sub>IN</sub>  | Input Current                                                             | V <sub>DD</sub> =0 V<br>V <sub>IN</sub> =0 V or 2.8 V or 3.6 V      |                                        | -10   | ±1   | +10             | μA   |

| LVCMOS           | Output DC Specifications (Receiver                                        | Outputs)                                                            |                                        |       |      |                 |      |

| V <sub>он</sub>  | Output High Voltage                                                       | I <sub>OH</sub> = -0.4 mA, V <sub>ID</sub> = 200 mV                 |                                        | 2.7   | 3.3  |                 | V    |

| V <sub>OL</sub>  | Output Low Voltage                                                        | I <sub>OL</sub> = 2 mA, V <sub>ID</sub> = 200 mV                    | R <sub>OUT</sub>                       |       | 0.05 | 0.25            | V    |

| I <sub>OZ</sub>  | Output TRI-STATE Current                                                  | Disabled, V <sub>OUT</sub> =0 V or V <sub>DD</sub>                  |                                        | -10   | ±1   | +10             | μA   |

| General I        | DC Specifications                                                         |                                                                     |                                        |       |      |                 |      |

| I <sub>DD</sub>  | Power Supply Current <sup>(5)</sup>                                       | EN = 3.3 V                                                          | N/                                     |       | 21   | 35              | mA   |

| I <sub>DDZ</sub> | TRI-State Supply Current                                                  | EN = 0 V                                                            | V <sub>DD</sub>                        |       | 15   | 25              | mA   |

(1) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except:  $V_{TH}$ ,  $V_{TL}$ ,  $V_{OD}$  and  $\Delta V_{OD}$ . All typical values are given for:  $V_{DD}$  = +3.3 V,  $T_A$  = +25°C.

(2)

The DS90LV049H's drivers are current mode devices and only function within datasheet specifications when a resistive load is applied (3) to their outputs. The typical range of the resistor values is 90  $\Omega$  to 110  $\Omega.$

(4) Output short circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only.

Both driver and receiver inputs are static. All LVDS outputs have 100 Ω load. All LVCMOS outputs are floating. None of the outputs (5) have any lumped capacitive load.

JAJSGU8B-SEPTEMBER 2005-REVISED JANUARY 2019

www.ti.com

#### 6.6 Switching Characteristics

$V_{DD}$  = +3.3V ± 10%,  $T_A$  = -40°C to +125°C<sup>(1)(2)</sup>

|                   | PARAMETER                                                                          | TEST CONDITIONS                               | MIN | TYP  | MAX | UNIT |

|-------------------|------------------------------------------------------------------------------------|-----------------------------------------------|-----|------|-----|------|

| LVDS O            | utputs (Driver Outputs)                                                            |                                               |     |      |     |      |

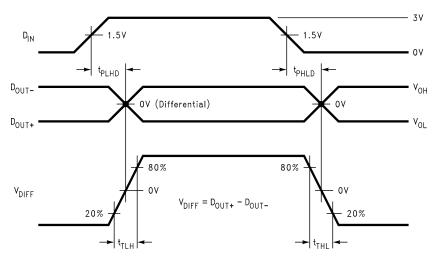

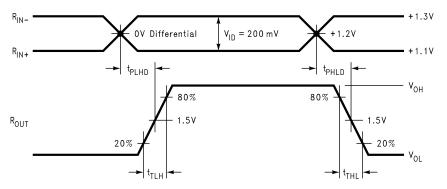

| t <sub>PHLD</sub> | Differential Propagation Delay High to Low                                         |                                               |     | 0.7  | 2   | ns   |

| t <sub>PLHD</sub> | Differential Propagation Delay Low to High                                         |                                               |     | 0.7  | 2   | ns   |

| t <sub>SKD1</sub> | Differential Pulse Skew  t <sub>PHLD</sub> - t <sub>PLHD</sub>   <sup>(3)(4)</sup> |                                               | 0   | 0.05 | 0.4 | ns   |

| t <sub>SKD2</sub> | Differential Channel-to-Channel Skew <sup>(3)(5)</sup>                             | $R_L = 100 \Omega$<br>(Figure 3 and Figure 4) | 0   | 0.05 | 0.5 | ns   |

| t <sub>SKD3</sub> | Differential Part-to-Part Skew <sup>(3)(6)</sup>                                   |                                               | 0   |      | 1   | ns   |

| t <sub>TLH</sub>  | Rise Time <sup>(3)</sup>                                                           |                                               | 0.2 | 0.4  | 1   | ns   |

| t <sub>THL</sub>  | Fall Time <sup>(3)</sup>                                                           |                                               | 0.2 | 0.4  | 1   | ns   |

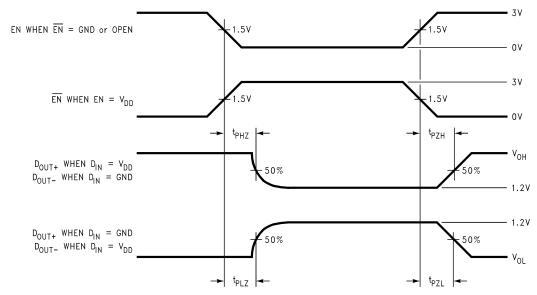

| t <sub>PHZ</sub>  | Disable Time High to Z                                                             |                                               |     | 1.5  | 3   | ns   |

| t <sub>PLZ</sub>  | Disable Time Low to Z                                                              | R <sub>L</sub> = 100 Ω                        |     | 1.5  | 3   | ns   |

| t <sub>PZH</sub>  | Enable Time Z to High                                                              | (Figure 5 and Figure 6)                       | 1   | 3    | 6   | ns   |

| t <sub>PZL</sub>  | Enable Time Z to Low                                                               |                                               | 1   | 3    | 6   | ns   |

| f <sub>MAX</sub>  | Maximum Operating Frequency <sup>(7)</sup>                                         |                                               | 200 | 250  |     | MHz  |

| LVCMO             | S Outputs (Receiver Outputs)                                                       |                                               | 1   |      |     |      |

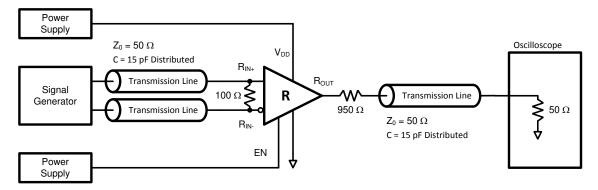

| t <sub>PHL</sub>  | Propagation Delay High to Low                                                      |                                               | 0.5 | 2    | 3.5 | ns   |

| t <sub>PLH</sub>  | Propagation Delay Low to High                                                      |                                               | 0.5 | 2    | 3.5 | ns   |

| t <sub>SK1</sub>  | Pulse Skew  t <sub>PHL</sub> - t <sub>PLH</sub>   <sup>(8)</sup>                   |                                               | 0   | 0.05 | 0.4 | ns   |

| t <sub>SK2</sub>  | Channel-to-Channel Skew <sup>(9)</sup>                                             | (Figure 7 and Figure 8)                       | 0   | 0.05 | 0.5 | ns   |

| t <sub>SK3</sub>  | Part-to-Part Skew <sup>(10)</sup>                                                  |                                               | 0   |      | 1   | ns   |

| t <sub>TLH</sub>  | Rise Time <sup>(3)</sup>                                                           |                                               | 0.3 | 0.9  | 1.4 | ns   |

| t <sub>THL</sub>  | Fall Time <sup>(3)</sup>                                                           |                                               | 0.3 | 0.75 | 1.4 | ns   |

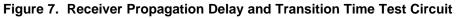

| t <sub>PHZ</sub>  | Disable Time High to Z                                                             |                                               | 3   | 5.6  | 8   | ns   |

| t <sub>PLZ</sub>  | Disable Time Low to Z                                                              | (Figure 0 and Figure 40)                      | 3   | 5.4  | 8   | ns   |

| t <sub>PZH</sub>  | Enable Time Z to High                                                              | (Figure 9 and Figure 10)                      | 2.5 | 4.6  | 7   | ns   |

| t <sub>PZL</sub>  | Enable Time Z to Low                                                               |                                               | 2.5 | 4.6  | 7   | ns   |

| f <sub>MAX</sub>  | Maximum Operating Frequency <sup>(11)</sup>                                        |                                               | 200 | 250  |     | MHz  |

(1) All typical values are given for:  $V_{DD}$  = +3.3 V,  $T_A$  = +25°C.

(2) Generator waveform for all tests unless otherwise specified: f = 1 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \le 1 \text{ ns}$ , and  $t_f \le 1 \text{ ns}$ .

(3) These parameters are specified by design. The limits are based on statistical analysis of the device performance over PVT (process, voltage, temperature) ranges.

(4) t<sub>SKD1</sub> or differential pulse skew is defined as |t<sub>PHLD</sub> - t<sub>PLHD</sub>]. It is the magnitude difference in the differential propagation delays between the positive going edge and the negative going edge of the same driver channel.

(5) t<sub>SKD2</sub> or differential channel-to-channel skew is defined as the magnitude difference in the differential propagation delays between two driver channels on the same device.

- (6) t<sub>SKD3</sub> or differential part-to-part skew is defined as |t<sub>PLHD Max</sub> t<sub>PLHD Min</sub>| or |t<sub>PHLD Max</sub> t<sub>PHLD Min</sub>|. It is the difference between the minimum and maximum specified differential propagation delays. This specification applies to devices at the same V<sub>DD</sub> and within 5°C of each other within the operating temperature range.

- (7)  $f_{MAX}$  generator input conditions:  $t_r = t_f < 1$  ns (0% to 100%), 50% duty cycle, 0 V to 3 V. Output Criteria: duty cycle = 45%/55%,  $V_{OD} > 250$  mV, all channels switching.

- (8) t<sub>SK1</sub> or pulse skew is defined as |t<sub>PHL</sub> t<sub>PLH</sub>|. It is the magnitude difference in the propagation delays between the positive going edge and the negative going edge of the same receiver channel.

(9) t<sub>SK2</sub> or channel-to-channel skew is defined as the magnitude difference in the propagation delays between two receiver channels on the same device.

- (10) t<sub>SK3</sub> or part-to-part skew is defined as |t<sub>PLH Max</sub> t<sub>PLH Min</sub>| or |t<sub>PHL Max</sub> t<sub>PHL Min</sub>|. It is the difference between the minimum and maximum specified propagation delays. This specification applies to devices at the same V<sub>DD</sub> and within 5°C of each other within the operating temperature range.

- (11)  $f_{MAX}$  generator input conditions:  $t_r = t_f < 1$  ns (0% to 100%), 50% duty cycle,  $V_{ID} = 200$  mV,  $V_{CM} = 1.2$  V. Output Criteria: duty cycle = 45%/55%,  $V_{OH} > 2.7$  V,  $V_{OL} < 0.25$  V, all channels switching.

# 6.7 Typical Characteristics

### 7 Parameter Measurement Information

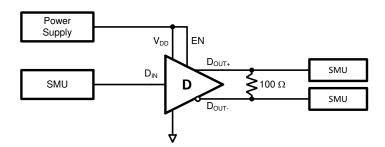

Figure 2. Driver  $V_{\text{OD}}$  and  $V_{\text{OS}}$  Test Circuit

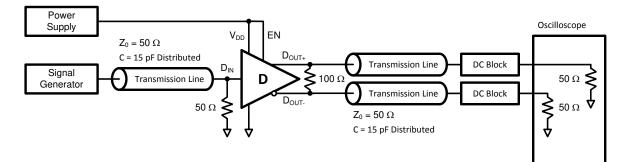

Figure 3. Driver Propagation Delay and Transition Time Test Circuit

# NSTRUMENTS

Texas

www.ti.com

#### **Parameter Measurement Information (continued)**

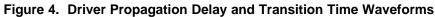

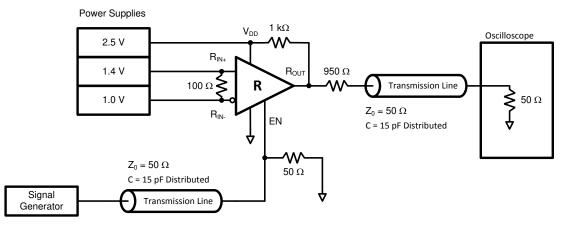

#### Figure 5. Driver TRI-STATE Delay Test Circuit

Figure 8. Receiver Propagation Delay and Transition Time Waveforms

Figure 9. Receiver TRI-STATE Delay Test Circuit

# Parameter Measurement Information (continued)

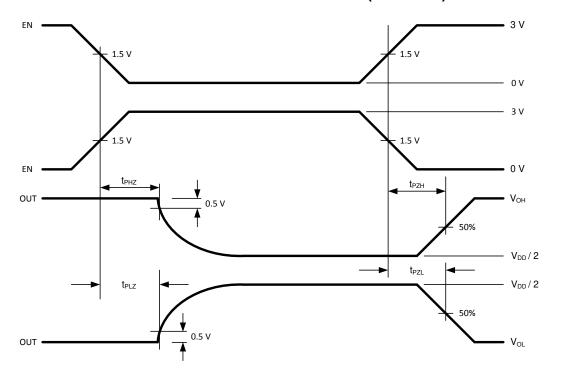

Figure 10. Receiver TRI-STATE Delay Waveforms

TEXAS INSTRUMENTS

www.ti.com

## 8 Detailed Description

The DS90LV049H integrates both low-voltage differential signaling (LVDS) line drivers, with a balanced current source design, and LVDS line receivers into a single package. This device operates from a single power supply that is nominally 3.3 V, but the supply can be as low as 3.0 V and as high as 3.6 V. The input signal to the DS90LV049H LVDS line drivers is an LVCMOS/LVTTL signal. The output of the DS90LV049H LVDS line drivers is a differential signal complying with the LVDS standard (TIA/EIA-644). The input to the DS90LV049H LVDS line drivers is a differential signal complying with the LVDS Standard (TIA/EIA-644) and the output is a 3.3-V LVCMOS/LVTTL signal. The differential output signal of the DS90LV049H LVDS line drivers operates with a signal level of 350 mV, nominally, at a common-mode voltage of 1.2 V. This low differential output voltage results in low electromagnetic interference (EMI). The differential input signal of the DS90LV049H LVDS line receivers operates with a signal level of 350 mV, nominally, at a common-mode voltage of 1.2 V. The differential nature of the LVDS outputs and inputs provides immunity to common-mode coupled signals (noise) that the driver/received signal may experience.

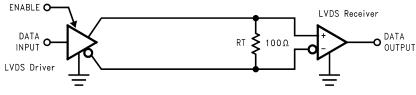

The DS90LV049H is primarily used in point-to-point configurations, as seen in Figure 11. This configuration provides a clean signaling environment for the fast edge rates of the DS90LV049H and other LVDS components. The DS90LV049H is connected through a balanced media which may be a standard twisted-pair cable, a parallel pair cable, or simply PCB traces to a LVDS receiver. Typically, the characteristic differential impedance of the media is in the range of 100  $\Omega$ . The DS90LV049H device is intended to drive a 100- $\Omega$  transmission line. The 100- $\Omega$  termination resistor is selected to match the media and is placed as close to the LVDS receiver input pins as possible.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 DS90LV049H LVDS Driver and Receiver Functionality

Table 1 shows how the LVDS driver single-ended input to differential output relationship is defined for DS90LV049H. When the driver input is left open, the differential output is undefined.

| INPUT            | OUTPUT             |                    |  |  |  |  |  |

|------------------|--------------------|--------------------|--|--|--|--|--|

| D <sub>INx</sub> | D <sub>OUTx+</sub> | D <sub>OUTx-</sub> |  |  |  |  |  |

| Н                | Н                  | L                  |  |  |  |  |  |

| L                | L                  | Н                  |  |  |  |  |  |

| Open             | ?                  | ?                  |  |  |  |  |  |

(1) x = 1,2 to indicate pin designation.

**NSTRUMENTS**

**EXAS**

Table 2 shows how the LVDS receiver differential input to single-ended output relationship is defined for DS90LV049H. The DS90LV049H receiver is capable of detecting signals as low as 100 mV, over a  $\pm$ 1-V common-mode range centered around 1.2 V.

| INPUTS                                  | OUTPUT            |

|-----------------------------------------|-------------------|

| $V_{ID} = [R_{INX+}] - [R_{INX-}]$      | R <sub>OUTx</sub> |

| $V_{ID} \ge 0 V$                        | н                 |

| V <sub>ID</sub> ≤ −0.1 V                | L                 |

| Full Fail-Safe OPEN/SHORT or Terminated | Н                 |

(1) x = 1,2 to indicate pin designation.

#### 8.3.2 Termination

Use a termination resistor that best matches the differential impedance or the transmission line. The resistor should be between 90  $\Omega$  and 130  $\Omega$ . Remember that the current mode outputs need the termination resistor to generate the differential voltage. LVDS will not work without resistor termination. Typically, connecting a single resistor across the pair at the receiver end will suffice.

Surface mount 1% to 2% resistors are best. PCB stubs, component lead, and the distance from the termination to the receiver inputs should be minimized. The distance between the termination resistor and the receiver should be < 10 mm (12 mm MAX).

#### 8.3.3 Fail-Safe Feature

The LVDS receiver is a high-gain, high-speed device that amplifies a small differential signal (20 mV) to LVCMOS/LVTTL logic levels. Due to the high gain and tight threshold of the receiver, take care to prevent noise from appearing as a valid signal. The internal fail-safe circuitry of the receiver is designed to source/sink a small amount of current, providing fail-safe protection (a stable known state of HIGH output voltage) for floating, terminated, or shorted receiver inputs.

- 1. **Open Input Pins**: It is not required to tie the receiver inputs to ground or any supply voltage. Internal failsafe circuitry will ensure a HIGH, stable output state for open inputs.

- 2. **Terminated Input**: If the driver is disconnected (cable unplugged), or if the driver is in a power-off condition, the receiver output will again be in a HIGH state, even with the end cable  $100-\Omega$  termination resistor across the input pins. The unplugged cable can become a floating antenna which can pick up noise. If the cable picks up more than 10 mV of differential noise, the receiver may see the noise as a valid signal and switch. To ensure that any noise is seen as common-mode and not differential, a balanced interconnect should be used. A twisted-pair cable will offer better balance than a flat ribbon cable.

- 3. **Shorted Inputs**: If a fault condition occurs that shorts the receiver inputs together, thus resulting in a 0-V differential input voltage, the receiver output will remain in a HIGH state. Shorted input fail-safe is not supported across the common-mode range of the device (GND to 2.4 V). It is only supported with inputs shorted and no external common-mode voltage applied.

External lower value pullup and pulldown resistors (for a stronger bias) may be used to boost fail-safe in the presence of higher noise levels. The pullup and pulldown resistors should be in the 5-k $\Omega$  to 15-k $\Omega$  range to minimize loading and waveform distortion to the driver. The common-mode bias point should be set to approximately 1.2 V (less than 1.75 V) to be compatible with the internal circuitry. The DS90LV049H is compliant to the original ANSI EIA/TIA-644 specification and is also compliant to the new ANSI EIA/TIA-644-A specification with the exception of the newly added  $\Delta$ IIN specification. Due to the internal fail-safe circuitry,  $\Delta$ IIN cannot meet the 6- $\mu$ A maximum specified. This exception will not be relevant unless more than 10 receivers are used.

Additional information on the fail-safe biasing of LVDS devices may be found in *AN-1194 Fail-Safe Biasing of LVDS Interfaces* (SNLA051).

#### 8.4 Device Functional Modes

Table 3 reflects the functional state of DS90LV049H when EN and  $\overline{EN}$  change state.

### Table 3. DS90LV049H Functional Modes

| EN        | ĒN        | LVDS Out | LVCMOS Out |

|-----------|-----------|----------|------------|

| L or Open | L or Open | OFF      | OFF        |

| Н         | L or Open | ON       | ON         |

| L or Open | Н         | OFF      |            |

| Н         | Н         | OFF      | OFF        |

TEXAS INSTRUMENTS

www.ti.com

### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

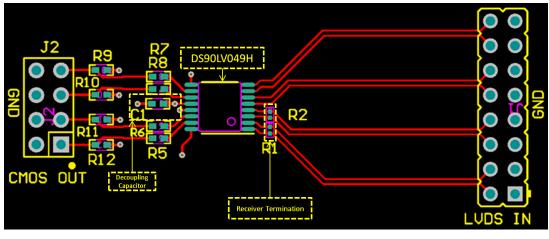

LVDS drivers and receivers are intended to be used primarily in a point-to-point configurations as is shown in Figure 11. This configuration provides a clean signaling environment for the fast edge rates of the drivers. The receiver is connected to the driver through a balanced media that may be a standard twisted pair cable, a parallel pair cable, or simply PCB traces. Typically, the characteristic differential impedance of the media is in the range of 100  $\Omega$ . A termination resistor of 100  $\Omega$  (selected to match the media), and is placed as close to the receiver input pins as possible. The termination resistor converts the driver output current (current mode) into a voltage that is detected by the receiver. Other configurations are possible such as a multi-receiver configuration, but the effects of a mid-stream connector(s), cable stub(s), and other impedance discontinuities as well as ground shifting, noise margin limits, and total termination loading must be taken into account. The TRI-STATE function allows the device outputs to be disabled, thus obtaining an even lower power state when the transmission of data is not required. The DS90LV049H has a flow-through pinout that allows for easy PCB layout. The LVDS signals on one side of the device allow for easy matching of the electrical lengths for the differential pair trace lines between the driver and the receiver, and the signal placement allows the trace lines to be close together to couple noise as common-mode. Noise isolation is achieved with the LVDS signals on one side of the device and the trace isolation is achieved with the LVDS signals on one side of the device and the trace lines to be close together to couple noise as common-mode. Noise isolation is achieved with the LVDS signals on one side of the device and the trace lines to be close together to couple noise as common-mode. Noise isolation is achieved with the LVDS signals on one side of the device and the trace lines to the device and the trace lines to be close together to couple noise as

## 9.2 Typical Application

Figure 11. Point-to-Point Application

#### 9.2.1 Design Requirements

Table 4 lists the design parameters for this example.

| Table 4. Desig | n Parameters |

|----------------|--------------|

|----------------|--------------|

| DESIGN PARAMETER                                          | EXAMPLE VALUE        |

|-----------------------------------------------------------|----------------------|

| Supply Voltage (V <sub>DD</sub> )                         | 3 to 3.6 V           |

| Single-ended Input Voltage                                | 0 to V <sub>DD</sub> |

| Signaling Rate 1 Ground shift between driver and receiver | 0 to 400 Mbps        |

| Interconnect Characteristic Impedance                     | 100 Ω                |

| Number of LVDS Channel                                    | 4                    |

| Number of Receiver/Transmitter Nodes                      | 2                    |

| Ground shift between driver and receiver                  | ±1 V                 |

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Power Decoupling Recommendations

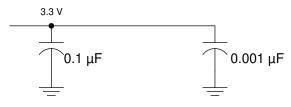

Bypass capacitors must be used on power pins. Use high frequency ceramic (surface mount is recommended) 0.1- $\mu$ F and 0.001- $\mu$ F capacitors in parallel at the power supply pin with the smallest value capacitor closest to the device supply pin.

Bypass capacitors play a key role in power distribution circuitry. Specifically, they create low-impedance paths between power and ground. At low frequencies, a good digital power supply offers very low-impedance paths between its terminals. However, as higher frequency currents propagate through power traces, the source is quite often incapable of maintaining a low-impedance path to ground. Bypass capacitors are used to address this shortcoming. Usually, large bypass capacitors (10  $\mu$ F to 1000  $\mu$ F) at the board-level do a good job up into the kHz range. Due to their size and length of their leads, they tend to have large inductance values at the switching frequencies of modern digital circuitry. To solve this problem, one must resort to the use of smaller capacitors (nF to  $\mu$ F range) installed locally next to the integrated circuit.

Multilayer ceramic chip or surface-mount capacitors (size 0603 or 0805) minimize lead inductances of bypass capacitors in high-speed environments, because their lead inductance is about 1 nH. For comparison purposes, a typical capacitor with leads has a lead inductance around 5 nH.

The value of the bypass capacitors used locally with LVDS chips can be determined by Equation 1 and Equation 2 according to Johnson<sup>(1)</sup> equations 8.18 to 8.21. A conservative rise time of 200 ps and a worst-case change in supply current of 1 A covers the whole range of LVDS devices offered by Texas Instruments. In this example, the maximum power supply noise tolerated is 200 mV. However, this figure varies depending on the noise budget available in the design. <sup>(1)</sup>

$$C_{chip} = \left(\frac{\Delta I_{Maximum Step Change Supply Current}}{\Delta V_{Maximum Power Supply Noise}}\right) \times T_{Rise Time}$$

$$C_{LVDS} = \left(\frac{1A}{0.2V}\right) \times 200 \text{ ps} = 0.001 \,\mu\text{F}$$

(2)

Figure 12 lowers lead inductance and covers intermediate frequencies between the board-level capacitor (>10  $\mu$ F) and the value of capacitance found above (0.001  $\mu$ F). TI recommends that the user place the smallest value of capacitance as close to the chip as possible.

Figure 12. Recommended LVDS Bypass Capacitor Layout

#### 9.2.2.2 PCB Transmission Lines

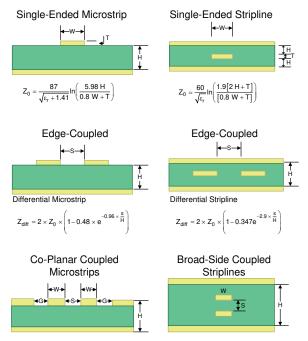

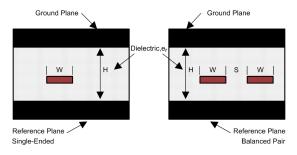

As per the *LVDS Owner's Manual Design Guide, 4th Edition* (SNLA187), Figure 13 depicts several transmission line structures commonly used in printed-circuit boards (PCBs). Each structure consists of a signal line and return path with a uniform cross section along its length. A microstrip is a signal trace on the top (or bottom) layer, separated by a dielectric layer from its return path in a ground or power plane. A stripline is a signal trace in the inner layer, with a dielectric layer in between a ground plane above and below the signal trace. The dimensions of the structure along with the dielectric material properties determine the characteristic impedance of the transmission line (also called controlled-impedance transmission line).

When two signal lines are placed close by, they form a pair of coupled transmission lines. Figure 13 shows examples of edge-coupled microstrip lines, and edge-coupled or broad-side-coupled striplines. When excited by differential signals, the coupled transmission line is referred to as a differential pair. The characteristic impedance of each line is called odd-mode impedance. The sum of the odd-mode impedances of each line is the differential pair. In addition to the trace dimensions and dielectric material properties, the

(1) Howard Johnson & Martin Graham.1993. High Speed Digital Design – A Handbook of Black Magic. Prentice Hall PRT. ISBN number 013395724.

spacing between the two traces determines the mutual coupling and impacts the differential impedance. When the two lines are immediately adjacent (like if S is less than 2 W, for example), the differential pair is called a tightly-coupled differential pair. To maintain constant differential impedance along the length, it is important to keep the trace width and spacing uniform along the length, as well as maintain good symmetry between the two lines.

Figure 13. Controlled-Impedance Transmission Lines

### 9.2.2.3 Input Fail-Safe Biasing

External pullup and pulldown resistors may be used to provide enough of an offset to enable an input fail-safe under open-circuit conditions. This configuration ties the positive LVDS input pin to VDD through a pullup resistor, and the negative LVDS input pin is tied to GND by a pulldown resistor. The pullup and pulldown resistors should be in the 5 k $\Omega$  to 15 k $\Omega$  range to minimize loading and waveform distortion to the driver. The common-mode bias point should ideally be set to approximately 1.2 V (less than 1.75 V) to be compatible with the internal circuitry. Refer to application note *AN-1194 Fail-Safe Biasing of LVDS Interfaces* (SNLA051) for more information.

### 9.2.2.4 Probing LVDS Transmission Lines on PCB

Always use high impedance (> 100 k $\Omega$ ), low capacitance (< 2 pF) scope probes with a wide bandwidth (1 GHz) scope. Improper probing will skew results.

#### 9.2.2.5 Interconnecting Media

The physical communication channel between the LVDS driver and the LVDS receiver may be any balanced and paired metal conductors meeting the requirements of the LVDS standard, the key points of which are included here. This media may be twisted-pair, twinax cables, flat ribbon cables, or PCB traces. The nominal characteristic impedance of the interconnect media should be between 100  $\Omega$  and 120  $\Omega$  with a variation of no more than 10% (90  $\Omega$  to 132  $\Omega$ ). Balanced cables (for example, twisted pair) are usually better than unbalanced cables (ribbon cable, simple coax.) for noise reduction and signal quality. Balanced cables tend to generate less EMI due to field canceling effects and also tend to pick up electromagnetic radiation a common-mode (not differential mode) noise which is rejected by the receiver. There should not introduce major impedance discontinuities in the system.

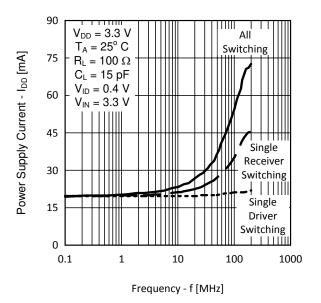

#### 9.2.3 Application Curve

Figure 14. Power Supply Current vs Frequency

### **10 Power Supply Recommendations**

The DS90LV049H LVDS transceiver is designed to operate from a single power supply with supply voltage in the range of 3.0 V to 3.6 V. In a typical point-to-point application, a driver and a receiver may be on separate boards, or even separate equipment. In these cases, separate supplies would be used at each location. The expected ground potential difference between the driver power supply and the driver power supply would be less than  $|\pm 1$  V|. Board level and local device level bypass capacitance should be used.

## 11 Layout

#### 11.1 Layout Guidelines

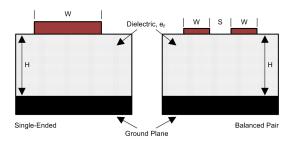

#### 11.1.1 Microstrip vs. Stripline Topologies

As per the *LVDS Application and Data Handbook* (SLLD009), printed-circuit boards usually offer designers two transmission line options: microstrip and stripline. Microstrips are traces on the outer layer of a PCB, as shown in Figure 15.

Figure 15. Microstrip Topology

#### Layout Guidelines (continued)

On the other hand, striplines are traces between two ground planes. Striplines are less prone to emissions and susceptibility problems because the reference planes effectively shield the embedded traces. However, from the standpoint of high-speed transmission, juxtaposing two planes creates additional capacitance. TI recommends routing LVDS signals on microstrip transmission lines when possible. The PCB traces allow designers to specify the necessary tolerances for  $Z_O$  based on the overall noise budget and reflection allowances. Footnotes  $1^{(2)}$ ,  $2^{(3)}$ , and  $3^{(4)}$  provide formulas for  $Z_O$  and  $t_{PD}$  for differential and single-ended traces. <sup>(2)</sup> (3) (4)

Figure 16. Stripline Topology

#### 11.1.2 Dielectric Type and Board Construction

The speeds at which signals travel across the board dictates the choice of dielectric. FR-4, or equivalent, usually provides adequate performance for use with LVDS signals. If rise or fall times of LVCMOS/LVTTL signals are less than 500 ps, empirical results indicate that a material with a dielectric constant near 3.4, such as Rogers<sup>™</sup> 4350 or Nelco N4000-13 may be desired. When the designer chooses the dielectric, there are several parameters pertaining to the board construction that can affect performance. The following set of guidelines were developed experimentally through several designs involving LVDS devices:

- Copper weight: 15 g or 1/2 oz start, plated to 30 g or 1 oz

- All exposed circuitry should be solder-plated (60/40) to 7.62  $\mu$ m or 0.0003 in (minimum).

- Copper plating should be 25.4 μm or 0.001 in (minimum) in plated-through-holes.

- Solder mask over bare copper with solder hot-air leveling

#### 11.1.3 Recommended Stack Layout

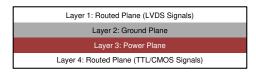

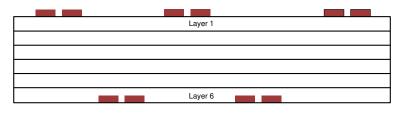

Following the choice of dielectrics and design specifications, the designer must decide how many levels to use in the stack. To reduce the LVCMOS/LVTTL to LVDS crosstalk, it is good practice to have at least two separate signal planes as shown in Figure 17.

Figure 17. Four-Layer PCB Board

#### NOTE

The separation between layers 2 and 3 should be 127  $\mu$ m (0.005 in). By keeping the power and ground planes tightly coupled, the increased capacitance acts as a bypass for transients.

- (3) Mark I. Montrose. 1996. Printed Circuit Board Design Techniques for EMC Compliance. IEEE Press. ISBN number 0780311310.

- (4) Clyde F. Coombs, Jr. Ed, Printed Circuits Handbook, McGraw Hill, ISBN number 0070127549.

<sup>(2)</sup> Howard Johnson & Martin Graham.1993. High Speed Digital Design – A Handbook of Black Magic. Prentice Hall PRT. ISBN number 013395724.

#### Layout Guidelines (continued)

| Layer 1: Routed Plane (LVDS Signals) |

|--------------------------------------|

| Layer 2: Ground Plane                |

| Layer 3: Power Plane                 |

| Layer 4: Ground Plane                |

| Layer 5: Ground Plane                |

| Layer 4: Routed Plane (TTL Signals)  |

|                                      |

One of the most common stack configurations is the six-layer board, as shown in Figure 18.

Figure 18. Six-Layer PCB Board

In this particular configuration, it is possible to isolate each signal layer from the power plane by at least one ground plane. The result is improved signal integrity, but fabrication is more expensive. Using the 6-layer board is preferable, because it offers the layout designer more flexibility in varying the distance between signal layers and referenced planes in addition to ensuring reference to a ground plane for signal layers 1 and 6.

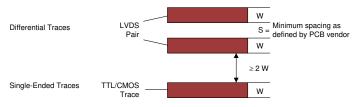

#### 11.1.4 Separation Between Traces

The separation between traces depends on several factors, but the amount of coupling that can be tolerated usually dictates the actual separation. Low-noise coupling requires close coupling between the differential pair of an LVDS link to benefit from the electromagnetic field cancellation. The traces should be  $100-\Omega$  differential and thus coupled in the manner that best fits this requirement. In addition, differential pairs should have the same electrical length to ensure that they are balanced, thus minimizing problems with skew and signal reflection.

In the case of two adjacent single-ended traces, one should use the 3-W rule, which stipulates that the distance between two traces must be greater than two times the width of a single trace, or three times its width measured from trace center to trace center. This increased separation effectively reduces the potential for crosstalk. The same rule should be applied to the separation between adjacent LVDS differential pairs, whether the traces are edge-coupled or broad-side-coupled.

Figure 19. 3-W Rule for Single-Ended and Differential Traces (Top View)

Exercise caution when using autorouters, because they do not always account for all factors affecting crosstalk and signal reflection. For instance, it is best to avoid sharp 90° turns to prevent discontinuities in the signal path. Using successive 45° turns tends to minimize reflections.

#### 11.1.5 Crosstalk and Ground Bounce Minimization

To reduce crosstalk, it is important to provide a return path to high-frequency currents that is as close to its originating trace as possible. A ground plane usually achieves this. Because the returning currents always choose the path of lowest inductance, they are most likely to return directly under the original trace, thus minimizing crosstalk. Lowering the area of the current loop lowers the potential for crosstalk. Traces kept as short as possible with an uninterrupted ground plane running beneath them emit the minimum amount of electromagnetic field strength. Discontinuities in the ground plane increase the return path inductance and should be avoided.

#### 11.1.6 Decoupling

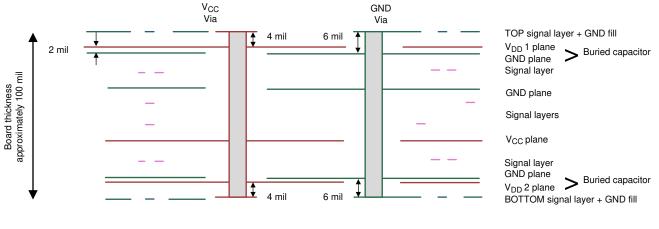

Each power or ground lead of a high-speed device should be connected to the PCB through a low inductance path. For best results, one or more vias are used to connect a power or ground pin to the nearby plane. TI recommends that the user place a via immediately adjacent to the pin to avoid adding trace inductance. Placing a power plane closer to the top of the board reduces the effective via length and its associated inductance.

#### Layout Guidelines (continued)

Typical 12-Layer PCB

Figure 20. Low Inductance, High-Capacitance Power Connection

Bypass capacitors should be placed close to  $V_{DD}$  pins. They can be placed conveniently near the corners or underneath the package to minimize the loop area. This extends the useful frequency range of the added capacitance. Small-physical-size capacitors, such as 0402 or even 0201, or X7R surface-mount capacitors should be used to minimize body inductance of capacitors. Each bypass capacitor is connected to the power and ground plane through vias tangent to the pads of the capacitor as shown in Figure 21(a).

An X7R surface-mount capacitor of size 0402 has about 0.5 nH of body inductance. At frequencies above 30 MHz or so, X7R capacitors behave as low-impedance inductors. To extend the operating frequency range to a few hundred MHz, an array of different capacitor values like 100 pF, 1 nF, 0.03 μF, and 0.1 μF are commonly used in parallel. The most effective bypass capacitor can be built using sandwiched layers of power and ground at a separation of 2 to 3 mils. With a 2-mil FR4 dielectric, there is approximately 500 pF per square inch of PCB. Refer back to Figure 13 for some examples. Many high-speed devices provide a low-inductance GND connection on the backside of the package. This center dap must be connected to a ground plane through an array of vias. The via array reduces the effective inductance to ground and enhances the thermal performance of the small Surface Mount Technology (SMT) package. Placing vias around the perimeter of the dap connection ensures proper heat spreading and the lowest possible die temperature. Placing high-performance devices on opposing sides of the PCB using two GND planes (as shown in Figure 13) creates multiple paths for heat transfer. Often thermal PCB issues are the result of one device adding heat to another, resulting in a very high local temperature. Multiple paths for heat transfer minimize this possibility. In many cases the GND dap that is so important for heat dissipation makes the optimal decoupling layout impossible to achieve due to insufficient padto-dap spacing as shown in Figure 21(b). When this occurs, placing the decoupling capacitor on the backside of the board keeps the extra inductance to a minimum. It is important to place the V<sub>DD</sub> via as close to the device pin as possible while still allowing for sufficient solder mask coverage. If the via is left open, solder may flow from the pad and into the via barrel. This will result in a poor solder connection.

Figure 21. Typical Decoupling Capacitor Layouts

#### www.tij.co.jp

#### Layout Guidelines (continued)

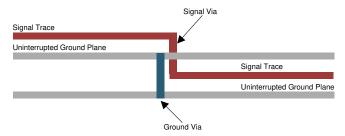

At least two or three times the width of an individual trace should separate single-ended traces and differential pairs to minimize the potential for crosstalk. Single-ended traces that run in parallel for less than the wavelength of the rise or fall times usually have negligible crosstalk. Increase the spacing between signal paths for long parallel runs to reduce crosstalk. Boards with limited real estate can benefit from the staggered trace layout, as shown in Figure 22.

Figure 22. Staggered Trace Layout

This configuration lays out alternating signal traces on different layers. Thus, the horizontal separation between traces can be less than 2 or 3 times the width of individual traces. To ensure continuity in the ground signal path, TI recommends having an adjacent ground via for every signal via, as shown in Figure 23. Note that vias create additional capacitance. For example, a typical via has a lumped capacitance effect of 1/2 pF to 1 pF in FR4.

Figure 23. Ground Via Location (Side View)

Short and low-impedance connection of the device ground pins to the PCB ground plane reduces ground bounce. Holes and cutouts in the ground planes can adversely affect current return paths if they create discontinuities that increase returning current loop areas.

To minimize EMI problems, TI recommends avoiding discontinuities below a trace (for example, holes, slits, and so on) and keeping traces as short as possible. Zoning the board wisely by placing all similar functions in the same area, as opposed to mixing them together, helps reduce susceptibility issues.

### 11.2 Layout Example

TEXAS INSTRUMENTS

www.tij.co.jp

# 12 デバイスおよびドキュメントのサポート

### 12.1 関連資料

関連資料については、以下を参照してください。

- 『LVDSオーナー・マニュアル』(SNLA187)

- 『AN-808、長い伝送ラインとデータ信号の品質』(SNLA028)

- 『AN-977、LVDS信号の品質: アイ・パターンを使用したジッタ測定のテスト・レポート #1』(SNLA166)

- 『AN-971、LVDSテクノロジの概要』(SNLA165)

- 『AN-916、ケーブル選択の実践的ガイド』(SNLA219)

- 『AN-805、差動ライン・ドライバの消費電力の計算』(SNOA233)

- 『AN-903、 差動終端技法の比較』 (SNLA034)

- 『AN-1194、LVDSインターフェイスのフェイルセーフ・バイアス法』(SNLA051)

### 12.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 12.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ TIのE2E(Engineer-to-Engineer)コミュニティ。エンジニア間の共同作 業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有 し、アイディアを検討して、問題解決に役立てることができます。

設計サポート TIの設計サポート 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることが できます。技術サポート用の連絡先情報も参照できます。

#### 12.4 商標

E2E is a trademark of Texas Instruments. Rogers is a trademark of Rogers Corporation. All other trademarks are the property of their respective owners.

#### 12.5 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 12.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device   | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|--------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| DS90LV049HMT/NOPB  | ACTIVE        | TSSOP        | PW                 | 16   | 92             | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | 90LV049<br>HMT          | Samples |

| DS90LV049HMTX/NOPB | ACTIVE        | TSSOP        | PW                 | 16   | 2500           | RoHS & Green    | SN                                   | Level-1-260C-UNLIM   | -40 to 125   | 90LV049<br>HMT          | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

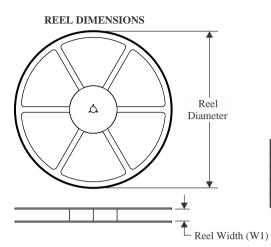

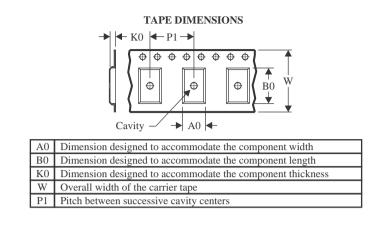

## TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| DS90LV049HMTX/NOPB          | TSSOP           | PW                 | 16 | 2500 | 330.0                    | 12.4                     | 6.95       | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

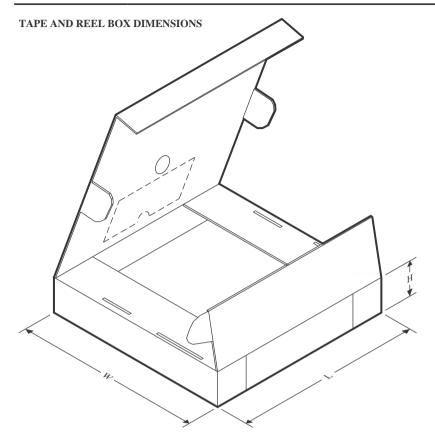

# PACKAGE MATERIALS INFORMATION

9-Aug-2022

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS90LV049HMTX/NOPB | TSSOP        | PW              | 16   | 2500 | 367.0       | 367.0      | 35.0        |

## TEXAS INSTRUMENTS

www.ti.com

9-Aug-2022

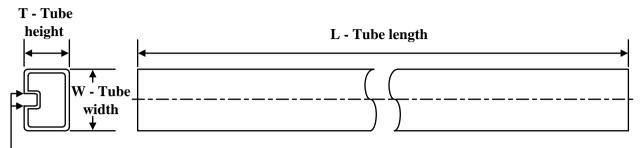

# TUBE

# - B - Alignment groove width

\*All dimensions are nominal

| Device            | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|-------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| DS90LV049HMT/NOPB | PW           | TSSOP        | 16   | 92  | 495    | 8      | 2514.6 | 4.06   |

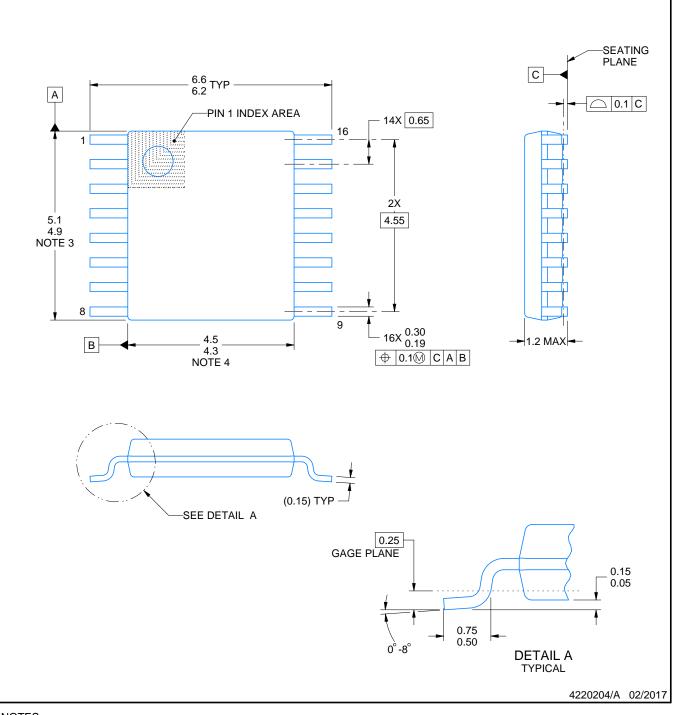

# **PW0016A**

# **PACKAGE OUTLINE**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

# PW0016A

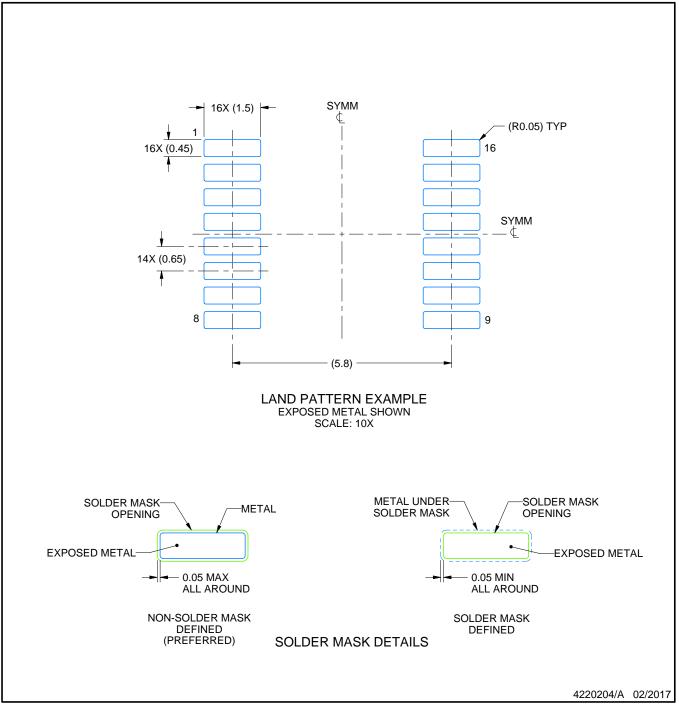

# **EXAMPLE BOARD LAYOUT**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# PW0016A

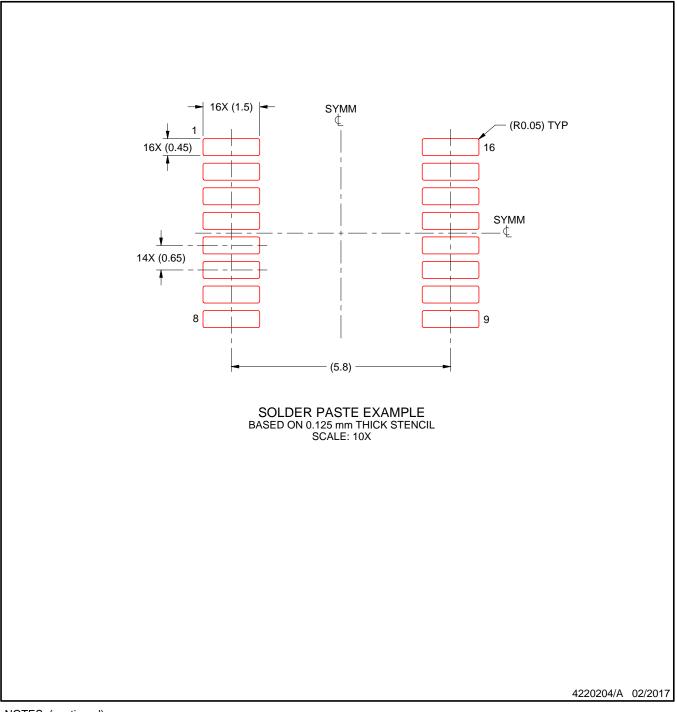

# **EXAMPLE STENCIL DESIGN**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

9. Board assembly site may have different recommendations for stencil design.

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要なお知らせと免責事項

TIは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや 設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供してお り、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的に かかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプ リケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載す ることは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを 自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022. Texas Instruments Incorporated