## LM26001

LM26001/LM26001Q 1.5A Switching Regulator with High Efficiency Sleep Mode

Literature Number: JAJSAI6

## LM26001/LM26001Q

2009年4月

## 高効率スリープ・モード機能内蔵 1.5A スイッチング・レギュレータ

#### 概要

LM26001 は、スタンバイ・モードを備えた高効率が要求されるアプリケーション用に設計されたスイッチング・レギュレータです。軽負荷条件時に高効率を維持するための低電流スリープ・モードと、広い入力電圧範囲にわたって精度の高いレギュレーションを行うための電流モード制御が特長です。 待機時電流は、シャットダウン・モード時は  $10\,\mu$  A (typ)、スリープ・モード時は  $40\,\mu$  A 未満に減少します。 スリープ・モードをオフにするための強制 PWM モードも用意されています。

LM26001 は、電流制限機能を備えており、内蔵の N チャネル・スイッチから最大 1.5A の連続負荷電流を供給できます。入力電圧範囲は  $4.0V\sim38V$  と広く、過渡時は最小で 3V の入力電圧で動作可能です。

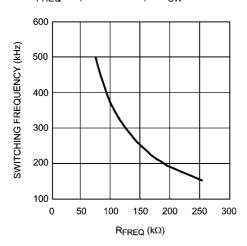

動作周波数は 1 本の抵抗で 150kHz ~ 500kHz まで調整可能であり、外部クロックと同期することできます。

その他には、パワーグッド・フラグ、調整可能なソフトスタート、イネーブルピン、入力電圧低下保護、部品点数削減のための内蔵ブートストラップ・ダイオードなどの機能があります。

#### 特長

- LM26001Q は AEC-Q100 グレード 1 認定 ( 動作時の接合 部温度範囲 - 40 ℃~+ 125 ℃ ) のオートモーティブ・グ レード製品です。

- 高効率スリープ・モード

- スリープ・モード時の Iq が 40 µ A (typ)

- シャットダウン・モード時の Iq が  $10 \mu$  A (typ)

- 最小入力電圧 3.0V

- 連続入力電圧範囲 4.0V ~ 38V

- リファレンス精度 1.5%

- サイクルごとの電流制限

- 調整可能な周波数 (150kHz ~ 500kHz)

- 外部クロックに同期可能

- パワーグッド・フラグ

- 強制 PWM 機能

- 調整可能なソフトスタート

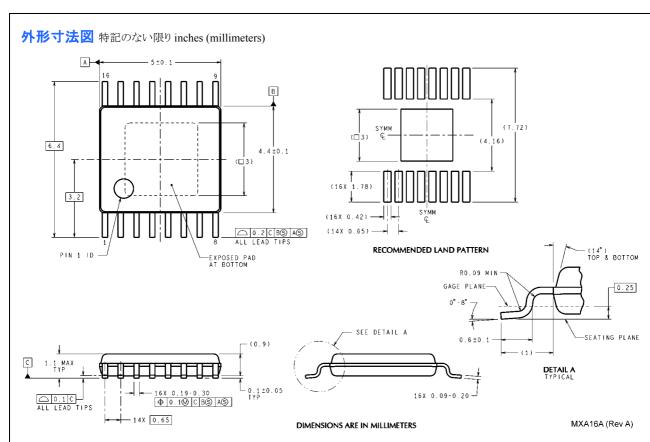

- TSSOP-16 露出型パッド・パッケージ

- サーマル・シャットダウン

## アプリケーション

- 車載用通信機器

- ナビゲーション・システム

- ダッシュボード取り付け計装機器

- バッテリ駆動アプリケーション

- ホーム・ゲートウェイ/セットトップ・ボックス向けのスタンバイ電源

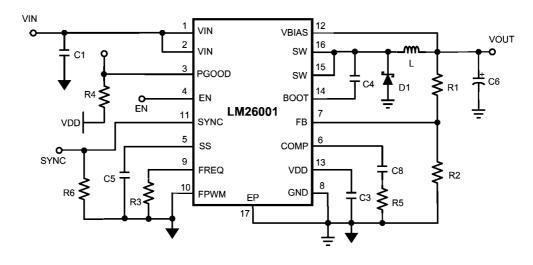

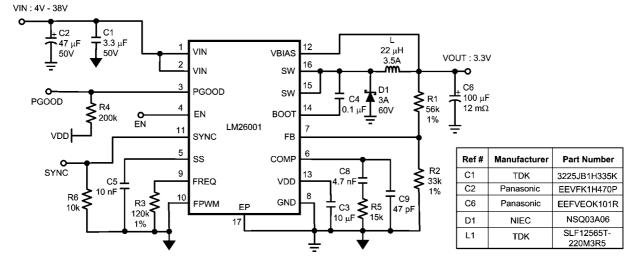

#### 代表的なアプリケーション回路

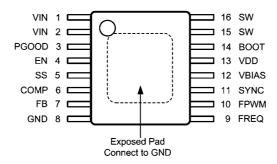

## ピン配置図

Top View 16-Lead Plastic TSSOP

## 製品情報

| Order Number | Package Type | Package | Package Marking | Supplied As                 | Features                                           |

|--------------|--------------|---------|-----------------|-----------------------------|----------------------------------------------------|

|              |              | Drawing |                 |                             |                                                    |

| LM26001MXA   | TSSOP-16EXP  | MXA16A  | LM26001MXA      | 92 Units of Rail            |                                                    |

| LM26001MXAX  | TSSOP-16EXP  | MXA16A  | LM26001MXA      | 2500 Units of Tape and Reel |                                                    |

| LM26001QMXA  | TSSOP-16EXP  | MXA16A  | LM26001QMXA     | 92 Units of Rail            | AEC-Q100 Grade 1                                   |

| LM26001QMXAX | TSSOP-16EXP  | MXA16A  | LM26001QMXA     | 2500 Units of Tape and Reel | qualified. Automotive<br>Grade Production<br>Flow* |

<sup>\*</sup>オートモーティブ・グレード (Q) 製品は、欠陥検出の技法など、自動車市場向けの高度な製造およびサポート・プロセスを採用しています。 信頼性規格については、AEC-Q100 標準で規定された要件および温度グレードに準拠します。 オートモーティブ・グレード製品は Q の文字で識別できます。 詳細については、ナショナル セミコンダクターの Web サイト http://www.national.com/automotive を参照してください。

## ピン説明

| ピン番号 | ピン名   | 説明                                                                                        |  |  |  |

|------|-------|-------------------------------------------------------------------------------------------|--|--|--|

| 1    | VIN   | 電源電圧入力ピン                                                                                  |  |  |  |

| 2    | VIN   | 電源電圧入力ピン                                                                                  |  |  |  |

| 3    | PGOOD | パワーグッドピン。オープン・ドレイン出力で、出力電圧が定格の 92% を超えると High になります。                                      |  |  |  |

| 4    | EN    | EN (イネーブル)は、アナログ・レベルの入力ピンです。 0.8V を下回ると、デバイスはシャットダウン・モードに移行します。                           |  |  |  |

| 5    | SS    | ソフトスタートピン。このピンと GND との間にコンデンサを接続して、ソフトスタート時間を設定します。                                       |  |  |  |

| 6    | COMP  | 位相補償ピン。抵抗とコンデンサのペアを接続して、制御ループの位相を補償します。                                                   |  |  |  |

| 7    | FB    | 帰還ピン。 Vout と GND の間に分圧抵抗を接続して、出力電圧を設定します。                                                 |  |  |  |

| 8    | GND   | グラウンド。                                                                                    |  |  |  |

| 9    | FREQ  | 周波数調整ピン。このピンとGNDとの間に抵抗を接続して、動作周波数を設定します。                                                  |  |  |  |

| 10   | FPWM  | FPWM は、ロジック・レベルの入力ピンです。 通常の動作では、GND に接続します。 High にプルアップすると、スリープ・モード動作はオフになります。            |  |  |  |

| 11   | SYNC  | 外部周波数同期ピン。外部同期動作の場合は、外部クロック信号に接続します。外部同期動作以外の場合は、SYNCをLowにプルダウンする必要があります。                 |  |  |  |

| 12   | VBIAS | 効率を高める場合は、3V以上の外部電源に接続して内部レギュレータをバイパスします。 使用しない場合、VBIAS は GND に接続してください。                  |  |  |  |

| 13   | VDD   | 内部レギュレータの出力。 1.0 µ F 以上のバイパス・コンデンサを接続します。                                                 |  |  |  |

| 14   | BOOT  | ブートストラップ・コンデンサ ピン。 このピンと SW ピンの間に $0.1\mu$ F 以上のセラミック・コンデンサを接続して、ゲート駆動用のブートストラップ電圧を生成します。 |  |  |  |

| 15   | SW    | スイッチング ピン。 内部の N チャネル・スイッチのソースに接続されています。                                                  |  |  |  |

| 16   | SW    | スイッチング ピン。 内部の N チャネル・スイッチのソースに接続されています。                                                  |  |  |  |

| EP   | EP    | 放熱用パッドです。 GND に接続してください。                                                                  |  |  |  |

#### 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

特に指定のない限り、表記の各ピンとGND間の電圧を表します。

VIN  $-0.3V \sim 40V$ SW (Note 7)  $-0.5V \sim +40V$ VDD  $-0.3V \sim 7V$ VBIAS  $-0.3V \sim 10V$ FB  $-0.3V \sim 6V$

BOOT  $SW - 0.3V \sim SW + 7V$

$\begin{array}{ll} \text{PGOOD} & -0.3\text{V} \sim 7\text{V} \\ \text{FREQ} & -0.3\text{V} \sim 7\text{V} \\ \text{SYNC} & -0.3\text{V} \sim 7\text{V} \\ \text{EN} & -0.3\text{V} \sim 40\text{V} \\ \text{FPWM} & -0.3\text{V} \sim 7\text{V} \end{array}$

SS  $-0.3V \sim 7V$

保存温度 - 65 ℃~+ 150 ℃

消費電力 (Note 2) 2.6W

推奨リード温度

ベーパ・フェーズ (70 秒) 215 ℃ 赤外線 (15 秒) 220 ℃

ESD 耐圧 (Note 3)

マシン・モデル200V人体モデル2KV帯電デバイス・モデル1kV

## **動作定格** (Note 1)

動作時接合部温度 -40  $\mathbb{C}\sim+125$   $\mathbb{C}$  電源電圧 (Note 4) 3.0V  $\sim$  38V

## 電気的特性

標準字体で記載された規格値は  $T_J=25$   $\mathbb C$  の場合に限ります。 **太字**で記載されたリミット値は-40  $\mathbb C$   $\sim+125$   $\mathbb C$  の接合部温度  $(T_J)$  範囲にわたって適用されます。 特記のない限り、 Vin=12V です。 最小リミット値および最大リミット値は、 試験、 設計、 または統計上の相関関係により保証されています。 代表 (Typ) 値は  $T_J=25$   $\mathbb C$  でのパラメータの最も標準と考えられる値を表し、参照を目的としてのみ提示されます。  $(Note\ 5)$

| Symbol                           | Parameter                             | Conditions                                           | Min    | Тур   | Max    | Unit |

|----------------------------------|---------------------------------------|------------------------------------------------------|--------|-------|--------|------|

| System                           |                                       |                                                      |        |       |        |      |

| I <sub>SD</sub> (Note 6)         | Shutdown Current                      | EN = 0V                                              |        | 10.8  | 20     | μΑ   |

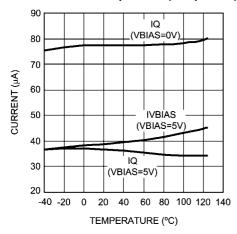

| Iq_ <sub>Sleep_VB</sub> (Note 6) | Quiescent Current                     | Sleep mode, VBIAS = 5V                               |        | 38    | 70     | μΑ   |

| Iq_ <sub>Sleep_VDD</sub>         | Quiescent Current                     | Sleep mode, VBIAS = GND                              |        | 75    | 125    | μΑ   |

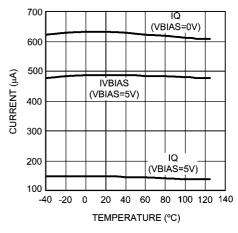

| Iq_ <sub>PWM_VB</sub>            | Quiescent Current                     | PWM mode, VBIAS = 5V                                 |        | 150   | 230    | μA   |

| Iq_ <sub>PWM_VDD</sub>           | Quiescent Current                     | PWM mode, VBIAS = GND                                |        | 0.65  | 0.85   | mA   |

| I <sub>BIAS_Sleep</sub> (Note 6) | Bias Current                          | Sleep mode, VBIAS = 5V                               |        | 33    | 85     | μA   |

| I <sub>BIAS_PWM</sub>            | Bias Current                          | PWM mode, VBIAS = 5V                                 |        | 0.5   | 0.70   | mA   |

| V <sub>FB</sub>                  | Feedback Voltage                      | 5V < Vin < 38V                                       | 1.2155 | 1.234 | 1.2525 | V    |

| I <sub>FB</sub>                  | FB Bias Current                       |                                                      |        |       | ±200   | nA   |

| $\Delta V_{OUT}/\Delta V_{IN}$   | Vout line regulation                  | 5V < Vin <38V                                        |        | 0.001 |        | %/V  |

| $\Delta V_{OUT}/\Delta I_{OUT}$  | Vout load regulation                  | 0.8V < V <sub>COMP</sub> < 1.15V                     |        | 0.07  |        | %    |

| VDD                              | VDD output voltage                    | 7V < Vin < 35V, I <sub>VDD</sub> = 0 mA to 5         | 5.50   | 5.95  | 6.50   | ٧    |

| I <sub>SS_Source</sub>           | Soft-start source current             | IIIA                                                 | 1.5    | 2.2   | 4.6    | μΑ   |

| V <sub>bias_th</sub>             | VBIAS On Voltage                      | Specified at I <sub>BIAS</sub> = 92.5% of full value | 2.64   | 2.9   | 3.07   | V    |

| Switching                        | -                                     |                                                      |        |       |        |      |

| R <sub>DS(ON)</sub>              | Switch on Resistance                  | Isw = 1A                                             | 0.12   | 0.2   | 0.42   | Ω    |

| I <sub>sw off</sub>              | Switch off state leakage current      | Vin = 38V, VSW = 0V                                  |        | 0.002 | 5.0    | μΑ   |

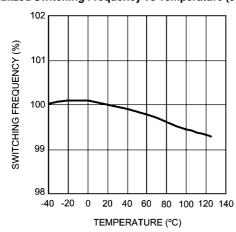

| f <sub>sw</sub>                  | Switching Frequency                   | RFREQ = 62k, 124k, 240k                              |        |       | ±10    | %    |

| V <sub>FREQ</sub>                | FREQ voltage                          |                                                      |        | 1.0   |        | ٧    |

| f <sub>SW</sub> range            | Switching Frequency range             |                                                      | 150    |       | 500    | kHz  |

| V <sub>SYNC</sub>                | Sync pin threshold                    | SYNC rising                                          |        | 1.2   | 1.6    | V    |

|                                  |                                       | SYNC falling                                         | 0.8    | 1.1   |        |      |

|                                  | Sync pin hysteresis                   |                                                      |        | 114   |        | mV   |

| I <sub>SYNC</sub>                | SYNC leakage current                  |                                                      |        | 6     |        | nA   |

| F <sub>SYNC_UP</sub>             | Upper frequency synchronization range | As compared to nominal f <sub>SW</sub>               |        |       | +30    | %    |

## 電気的特性(つづき)

標準字体で記載された規格値は  $T_J=25$   $\mathbb C$ の場合に限ります。 **太字**で記載されたリミット値は-40  $\mathbb C$   $\sim+125$   $\mathbb C$ の接合部温度  $(T_J)$  範囲にわたって適用されます。 特記のない限り、 Vin=12V です。 最小リミット値および最大リミット値は、試験、設計、または統計上の相関関係により保証されています。 代表 (Typ) 値は  $T_J=25$   $\mathbb C$  (Typ) でのパラメータの最 . も標準と考えられる値を表し、参照を目的としてのみ提示されます。 (Note 5)

| Symbol                  | Parameter                                  | Conditions                              | Min  | Тур    | Max  | Unit |

|-------------------------|--------------------------------------------|-----------------------------------------|------|--------|------|------|

| F <sub>SYNC_DN</sub>    | Lower frequency synchronization range      | As compared to nominal f <sub>SW</sub>  |      |        | -20  | %    |

| T <sub>OFFMIN</sub>     | Minimum Off-time                           |                                         |      | 365    |      | ns   |

| T <sub>ONMIN</sub>      | Minimum On-time                            |                                         |      | 155    |      | ns   |

| TH <sub>SLEEP_HYS</sub> | Sleep mode threshold hysteresis            | VFB rising, % of TH <sub>WAKE</sub>     |      | 101.2  |      | %    |

| TH <sub>WAKE</sub>      | Wake up threshold                          | Measured at falling FB, COMP = 0.6V     |      | 1.234  |      | V    |

| I <sub>BOOT</sub>       | BOOT pin leakage current                   | BOOT = 16V, SW = 10V                    |      | 0.0006 | 5.0  | μΑ   |

| Protection              |                                            |                                         |      |        |      |      |

| I <sub>LIMPK</sub>      | Peak Current Limit                         |                                         | 1.85 | 2.5    | 3.2  | Α    |

| $V_{FB\_SC}$            | Short circuit frequency foldback threshold | Measured at FB falling                  |      | 0.87   |      | V    |

| F_min_sc                | Min Frequency in foldback                  | VFB < 0.3V                              |      | 71     |      | kHz  |

| $V_{TH\_PGOOD}$         | Power Good Threshold                       | Measured at FB, PGOOD rising            | 89   | 92     | 95   | %    |

|                         | PGOOD hysteresis                           |                                         | 2    | 7      | 8    | %    |

| I <sub>PGOOD_HI</sub>   | PGOOD leakage current                      | PGOOD = 5V                              |      | 0.2    |      | nA   |

| R <sub>DS_PGOOD</sub>   | PGOOD on resistance                        | PGOOD sink current = 500 µA             |      | 64     |      | Ω    |

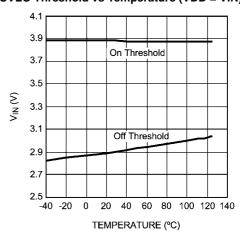

| V <sub>UVLO</sub>       | Under-voltage Lock-Out Threshold           | Vin falling , shutdown, VDD = VIN       | 2.60 | 2.9    | 3.20 | V    |

|                         |                                            | Vin rising, soft-start, VDD = VIN       | 3.60 | 3.9    | 4.20 |      |

| TSD                     | Thermal Shutdown Threshold                 |                                         |      | 160    |      | °C   |

| $\theta_{JA}$           | Thermal resistance                         | Power dissipation = 1W, 0 lfpm air flow |      | 38     |      | °C/W |

| Logic                   |                                            |                                         |      |        |      |      |

| Vth <sub>EN</sub>       | Enable Threshold voltage                   |                                         | 8.0  | 1.2    | 1.4  | V    |

|                         | Enable hysteresis                          |                                         |      | 120    |      | mV   |

| I <sub>EN_Source</sub>  | EN source current                          | EN = 0V                                 |      | 4.5    |      | μΑ   |

| $V_{TH\_FPWM}$          | FPWM threshold                             |                                         | 8.0  | 1.2    | 1.6  | V    |

| I <sub>FPWM</sub>       | FPWM leakage current                       | FPWM = 5V                               |      | 35     |      | nA   |

| EA                      |                                            |                                         |      |        |      |      |

| gm                      | Error amp trans-conductance                |                                         | 400  | 670    | 1000 | µmho |

| I <sub>COMP</sub>       | COMP source current                        | VCOMP = 0.9V                            |      | 56     |      | μΑ   |

|                         | COMP sink current                          | VCOMP = 0.9V                            |      | 56     |      | μΑ   |

| V <sub>COMP</sub>       | COMP pin voltage range                     |                                         | 0.64 |        | 1.27 | V    |

- Note 1: 「絶対最大定格」とは、この値を超えるとデバイスに破壊が発生する可能性のあるリミット値のことです。「動作定格」とはデバイスが機能する条件を示しますが、特定の性能リミット値を保証するものではありません。保証されている仕様および試験条件については、「電気的特性」を参照してください。

- Note 2: 最大許容消費電力は、最大接合部温度  $T_{J\_MAX}$ 、接合部-周囲雰囲気間熱抵抗  $\theta_{JA}$ 、周囲温度  $T_A$  の関数です。 任意の周囲温度での最大許容消費電力は次式から求めます。  $P_{D\_MAX} = (T_{J\_MAX} T_A)/\theta_{JA}$ 。 2.6W という最大消費電力の値は、  $T_A = 25$   $^{\circ}$   $^$

- Note 3: 人体モデルでは、100pF のコンデンサから直列抵抗  $1.5k\Omega$  を介して各ピンに放電させます。 マシン・モデルでは、200pF のコンデンサから抵抗を介さずに各ピンに放電させます。 帯電デバイス・モデルでは、JESD22-C101-C に従って試験を実施します。

- Note 4: 入力電圧が 4.0V に満たない場合は、 $R_{DS(ON)}$  が増加するため、消費電力は増加することがあります。このため、絶えず仕様の範囲内で動作させる場合には、最小入力電圧の 4.0V が必要になります。 起動時には、3.9V (typ) 以上の値も必要になります。

- Note 5: 室温のリミット値はすべて 100%試験されています。「動作接合部温度範囲」保証に対する各項目は、標準的な統計的品質管理 (SQC) 手法を用いた相関により保証されています。 すべてのリミット値は、平均出荷品質レベル (AOQL) の計算に使用されます。

- Note 6: Iq および ISD では、VIN ピンへの流入電流を規定しています。 IBIAS は、VBIAS 電圧が 3V を超えると VBIAS ピンへ流入する電流です。 すべての待機時電流規格値は、非スイッチング動作時に適用されます。

- Note 7: 絶対最大定格の仕様は、DC 電圧に対して適用されます。 拡張された負電圧のリミット値である -2V は最大  $1\,\mu$  s のパルスに対して適用され、 -1V は最大  $20\,\mu$  s のパルスに対して適用されます。

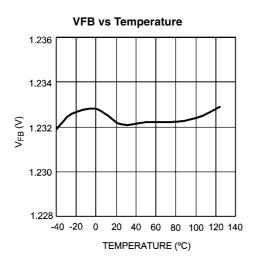

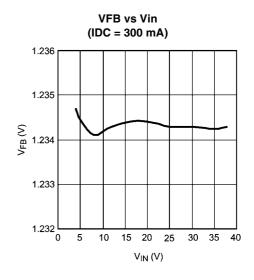

## 代表的な性能特性

特記のない限り、 Vin=12V、  $T_J=25$   $^{\circ}$   $^{\circ}$   $^{\circ}$  の条件が適用されます。

## IQ and IVBIAS vs Temperature (Sleep Mode)

## IQ and IVBIAS vs Temperature (PWM Mode)

## Normalized Switching Frequency vs Temperature (300kHz)

## UVLO Threshold vs Temperature (VDD = VIN)

## 代表的な性能特性(つづき)

特記のない限り、Vin=12V、 $T_J=25$   $\mathbb{C}$ の条件が適用されます。

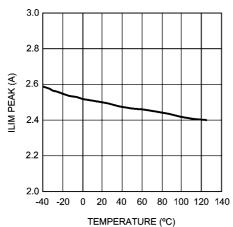

#### **Peak Current Limit vs Temperature**

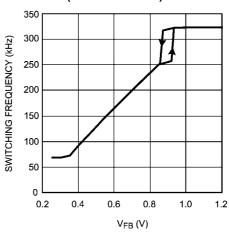

# Short Circuit Foldback Frequency vs V<sub>FB</sub> (325 kHz nominal)

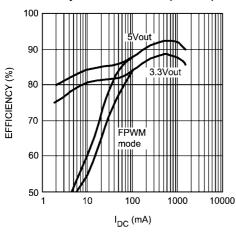

## Efficiency vs Load Current (330kHz)

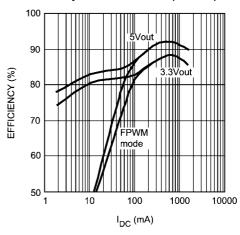

## Efficiency vs Load Current (500kHz)

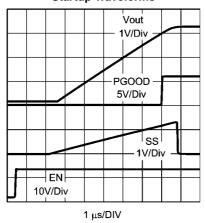

## Startup Waveforms

## **Load Transient Response**

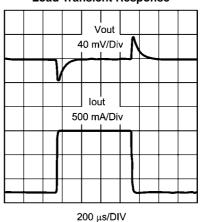

## 代表的な性能特性(つづき)

特記のない限り、Vin=12V、 $T_J=25$   $^{\circ}$ Cの条件が適用されます。

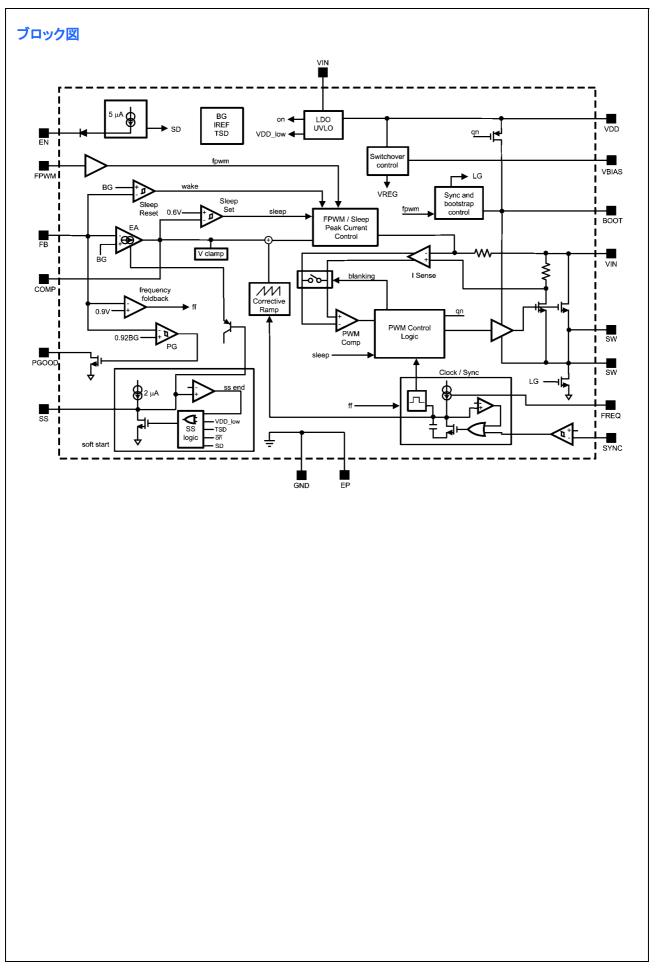

## Low Input Voltage Dropout Nominal VOUT = 5V

#### 動作説明

#### 概要

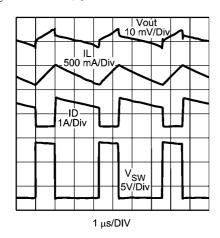

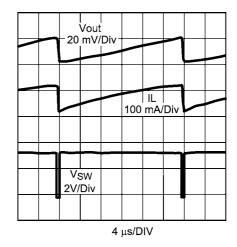

LM26001 は電流モードの PWM 制御降圧型レギュレータです。各スイッチング・サイクルにて、まず内蔵のハイサイド・スイッチがオンになり、インダクタ電流が増加します。インダクタ電流は、各スイッチング・サイクル中、IC 内部でモニタされます。インダクタ電流から得られる制御信号は、帰還電圧から得られた COMP ピンの電圧制御信号と比較されます。インダクタ電流がスレッショルドに到達すると、ハイサイド・スイッチはオフになり、インダクタ電流は減少します。スイッチがオフになっている間、電流はキャッチ・ダイオードから供給されます。このサイクルは、次のクロック・サイクルで繰り返されます。このように、デューティ・サイクルと出力電圧は、レギュレーション動作を行うインダクタ電流によって制御されます。電流モード方式は、優れたライン・レギュレーションおよび、ロード・レギュレーション特性を示します。その他にも、サイクルごとの電流制限や、単純化された位相補償などの利点があります。代表的な PWM 波形を Figure 1 に示します。

FIGURE 1. PWM Waveforms 1A Load, Vin = 12V

#### スリープ・モード

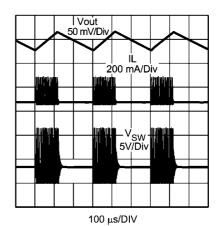

軽負荷の条件では、LM26001 は効率を向上するために自動的にスリープ・モードに切り替わります。 負荷が減少するにつれて、FB ピンの電圧は上昇し、COMP 電圧は下降します。 COMP 電圧が 0.6V (typ) のスレッショルドに到達し、FB 電圧が定格より 1% 高くなると、スリープ・モードが有効になり、スイッチングは停止します。レギュレータは、スイッチングが再開されるリセット・スレッショルドに FB 電圧が下降するまで、スリープ・モードを維持します。この 1% の FB 電圧枠により、対応する出力リップルが定格出力電圧の約 1% に制限されます。 スリープ・モードは、負荷電流が増加するまで維持されます。 Figure 2 に、スリープ・モードでの代表的なスイッチング波形と出力電圧波形を示します。

FIGURE 2. Sleep Mode Waveforms 25mA Load, Vin = 12V

スリープ・モードでは、スイッチングしていない場合、待機時電流は  $40\,\mu$  A 未満まで減少します。スリープ・モードの DC スレッショルドは、次式により求められます。

$$I_{Sleep} = \left[I_{min} + 0.13 \ \mu \left[\frac{Vin - Vout}{L}\right]\right]^{2} x \left[\frac{fsw \times L}{D \times 2 \times (Vin - Vout)}\right]$$

Imin = Ilim/16 (代表値では 2.5A/16) であり、D はデューティ・サイクルで、(Vout + Vdiode)/Vin で定義されます。

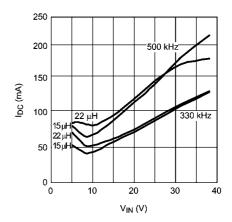

負荷電流が増加してこの制限値を超えると、LM26001 は強制的に PWM 動作に戻されます。 スリープ・モードのスレッショルドは、 Figure 3 に示すように周波数、インダクタンス、 デューティ・サイクルにより変化します。

FIGURE 3. Sleep Mode Threshold vs Vin Vout = 3.3V

#### **FPWM**

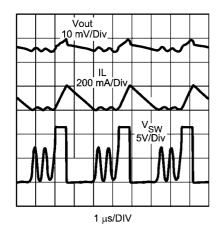

FPWM ピンを High にすると、スリープ・モードはオフになり、LM26001 は強制的に動作を PWM モードにします。PWM モードでは、軽負荷時の効率は低下しますが、スイッチング周波数は一定に維持されます。FPWM ピンは、VDD ピンに接続することで High にします。FPWM モードでは、軽負荷の時で、レギュレータは不連続モード (DCM) で動作します。不連続モードでは、インダクタに流れる電流はゼロからそのピーク値まで増加し、その後再びゼロまで減少します。次のサイクルに移るまで、インダクタ電流はゼロのままです。定格負荷電流時のFPWM モードでは、デバイスは連続モードで動作しますが、この場合には、インダクタに常時正の電流が流れます。不連続動作時の代表的な波形を次に示します。

#### 動作説明(つづき)

FIGURE 4. Discontinuous Mode Waveforms 75mA Load, Vin = 12V

FPWM モードでも、きわめて軽負荷の場合、LM26001 がスリープ・モードに移行する場合があります。これは、過電圧条件の発生を防止するためです。ただし、FPWM モードのスリープ・スレッショルドは、通常動作時よりも大幅に低い値になります。

#### イネーブル

LM26001 は EN ピンにてシャットダウン機能を提供し、出力電圧を必要としないときにデバイスをオフにします。 EN はアナログ・レベルの入力で、代表値で 120mV のヒステリシスがあります。 EN ピンが 1.2V (typ) を超えている場合、デバイスはアクティブになり、EN ピンがこのスレッショルドを下回ると、シャットダウン・モードになります。 EN が High になると、内蔵の VDD レギュレータがオンになり、VDD コンデンサを充電します。 VDD が 3.9V (typ) に達すると、ソフトスタートピンは電流の供給を開始します。 シャットダウン・モードでは、 VDD レギュレータはシャットダウンし、全待機時電流は  $10 \mu A$  (typ) まで減少します。 EN ピンは  $4.5 \mu A$  (typ) のプルアップ電流を供給するため、常時オンの動作では開放のままで構いません。 開放した場合、EN ピンは VIN ピンにプルアップされます。

EN ピンを VIN ピンに接続する場合は、 $10k\Omega$  の抵抗を接続してノイズ・スパイクを制限する必要があります。 EN ピンは、最大電圧の 38V と VIN + 15V のうち低い方の電圧で外部から駆動することもできます。

#### ソフトスタート

ソフトスタート機能を使用すると、起動時にこの機能により制御された出力電圧を得ることができます。これにより、電源投入時の突入電流が減少し、出力のオーバーシュートを除去できます。ソフトスタートピンである SS ピンは、コンデンサを介してGND に接続します。電源投入時、イネーブル時、またはUVLO復帰時に、内蔵の2.2μA(typ)電流源により、ソフトスタート・コンデンサが充電されます。ソフトスタート期間中、エラー・アンプの出力電圧は、ソフトスタート電圧とフィードバック・ループの両方によって制御されます。SS ピンの電圧が上昇すると、その上昇に比例してデューティ・サイクルが増大し、その結果出力電圧が上昇します。デューティ・サイクルが増大する率はソフトスタート・コンデンサの容量によって決まります。容量が大きいと出力電圧の上昇は緩やかになります。ソフトスタート・コンデンサの値は、次式により求められます。

$Css = \frac{Iss \times tss}{1.234V}$

tss は設定するソフトスタート時間、Iss はソフトスタートのソース 電流を表します。ソフトスタート期間中、電流制限と同期は有 効のままですが、スリープ・モードと周波数のフォールド・バッ クは無効になっています。ソフトスタート・モードは、SSピン電 圧が 1.23V (typ) に達すると終了します。この時点で、出力電 圧の制御は FB ピンに移り、SSピンは放電されます。

#### 電流制限

ピーク電流制限は、IC 内部を流れるインダクタ電流のピーク値を直接測定し、制限値は内部設定されています。 電流を正確に検出するため、 $1 \mu$  F 以上のセラミック・コンデンサを VIN ピンの直近に配置して、VIN をバイパスすることが必要です。

インダクタ電流が電流制限スレッショルドに達すると、IC 内部の FET は即座にオフになるため、インダクタ電流は次のサイクル まで減少し続けます。このデューティ・サイクルの減少は、出 力電圧も減少させます。

電流制限コンパレータは、スイッチング・ノイズに対する耐性を 向上させるため、パルスの立ち上がりで 100ns 未満のブランキ ング時間を設けています。

電流制限回路はインダクタ電流のピーク値を監視するため、負荷電流の DC 制限スレッショルドは、インダクタンスと周波数に応じて変化します。電流制限の最小値を 1.85A と仮定すると、負荷電流の最大値は次式で求めることができます。

$$Iload_{max} = 1.85A - \frac{Iripple}{2}$$

Iripple はインダクタ・リップル電流のピーク・ツー・ピーク値で、計算式を次式に示します。

Iripple =

$$\frac{(Vin - Vout) \times Vout}{fsw \times L \times Vin}$$

ワースト・ケースの電流制限スレッショルド (最小値)を求めるには、入力電圧の最大値と電流制限の最小値の規格を使用します。

出力短絡時のような高い過電流状態のとき、LM26001 は、第2 レベルの保護として周波数のフォールド・バックを採用しています。フィードバック電圧が出力短絡スレッショルドの0.9Vを下回ると、動作周波数を減少させ、スイッチ電流の平均値も減少します。この動作は、最小のオン時間の間、インダクタ電流が非常に高い値まで上昇する可能性がある、出力短絡条件で特に役立ちます。周波数の減少は、基準の周波数設定を20%下回った数値で始まります。フォールドバック・モードでの最小動作周波数は、代表値で71kHzです。

外部周波数同期動作時に FB 電圧が周波数フォールドバック・スレッショルドを下回ると、SYNC 機能はオフになります。 出力 短絡条件での動作周波数対 FB 電圧のグラフを、「代表的な性能特性」に示します。

オン時間が最小値(代表値で200ns未満)に近い条件(入力電圧とスイッチング周波数の両方が高いような条件)では、電流制限回路が正常に機能しない場合があります。これは、電流制限回路は、最小オン時間よりも小さい値にできないためで、この結果、周波数フォールドバック・モードには移行できなくなります。入力電圧が高い条件下で、正常な電流制限動作と周波数フォールドバック動作を確実に行う方法は2つあります。1つ目は、動作周波数を減少させて基準のオン時間を長くする方法です。2つ目は、インダクタ値を大きくして電流増加の速度を低下させ、ピーク時の過剰電流を低減する方法です。

#### 動作説明(つづき)

#### 周波数の調整と外部同期

LM26001 のスイッチング周波数は、1 本の外付け抵抗を使用することにより、150kHz ~ 500kHz の間で調整できます。この抵抗は、代表的なアプリケーションに示したように、FREQ ピンとグラウンドの間に接続します。抵抗値は実験的に得られた次の式から求めることができます。

$$R_{FREO} = (6.25 \times 10^{10}) \times f_{SW}^{-1.042}$$

FIGURE 5. Swtiching Frequency vs R<sub>FREQ</sub>

スイッチング周波数は、SYNCピンを使用して外部クロック信号に同期させることもできます。SYNCピンを使用すると、動作周波数を基準の周波数設定から上下に可変できます。調整範囲は基準値より30%高い値から基準値より20%低い値になります。外部同期では、SYNCピンに1.2V(typ)のピーク信号レベルが必要です。FREQピンには、基準の動作周波数を設定するために、常に抵抗を接続する必要があります。動作周波数は、SYNC入力の立ち下がりエッジで同期します。SYNC電圧がLowになると、ハイサイド・スイッチはオンになります。これにより、基準値より高い周波数に同期する場合は、同期信号として任意のデューティ・サイクルを使用できます。ただし、比較的低い周波数に同期する場合は、SYNC信号に対して最小デューティ・サイクルの要件が存在します(次式参照)。

Sync\_Dmin

$$\geq$$

1 -  $\frac{f_{\text{sync}}}{\text{fnom}}$

fnom は、FREQ に接続する抵抗で設定される基準のスイッチング周波数であり、fsync は矩形波です。 SYNC ピンを使用しない場合は、通常の動作では Low にプルダウンする必要があります。 同期信号が欠落した場合の保護のため、 $10k\Omega$  のプルダウン抵抗を推奨します。 LM26001 は最大 500kHz で動作するよう設計されていますが、温度上昇により、高い周波数では最大負荷電流が制限されることがあります。 熱に関する考慮事項のセクションを参照してください。

#### **VBIAS**

VBIASピンは、LM26001にバイアス電圧を供給する内部レギュレータをバイパスするときに使用します。VBIASピンに 3V を超える電圧を接続すると、内部レギュレータは VBIAS 入力に自動的に切り替わります。これにより、VINに流れ込む電流 (Iq)が減少し、システム効率が向上します。 VBIAS ピンを使用することにより、デバイス内部での消費電力が削減されます。

3V < Vout < 10V の大半のアプリケーションでは、 VBIAS を Vout に接続できます。 使用しない場合、 VBIAS は GND に接続してください。

VBIAS が 2.9V (typ) より小さくなると、内部バイアス電圧の供給は自動的に Vin からに切り替わります。

デバイスの全入力電流は、Iq、ゲート駆動電流、VBIAS電流と、FBピンに流れ込む電流(通常は無視できます)の和です。全入力消費電流の最小値は、次式により求められます。

$$Iinput = Iq + I_{QG} + \left(\frac{I_{BIAS} \times D}{eff}\right)$$

IOG はゲート駆動電流で、次式により求められます。

$$I_{QG} = (4.6 \times 10^{-9}) \times f_{SW}$$

全入力電源電流は、負荷、システム効率、動作周波数に応じて変動します。スリープ・モード時の入力電流の最小値を計算するには、Iq Sleep VB および  $I_{BIAS}$  SLEEP を使用します。

PWM モードでの入力電流の場合は、同じ式を使用しますが、 Iq  $_{\mathrm{PWM}}$   $_{\mathrm{VB}}$  および  $_{\mathrm{IBIAS}}$   $_{\mathrm{PWM}}$  を代入します。

VBIAS をグラウンドに接続している場合は、同じ式を使用し、Ibias の項を削除して  $Iq_{Sleep\_VDD}$  または  $Iq_{PWM\_VDD}$  を使用します。

#### 低 Vin 時の動作と UVLO

LM26001 は、入力電圧が 3.0V まで低下する可能性がある短時間の過渡時においても、動作状態を維持できるように設計されています。最小動作入力電圧の定格は、4.0V です。この電圧を下回ると、VDD からのゲート駆動電圧が低下するため、スイッチの R<sub>DS(ON)</sub> が増加します。通常動作のために必要な VDD の最小電圧は約 3.5V です。

VDD は、PGOOD や FPWM などの機能のプルアップ電圧として使用することもできます。 VDD を外部で使用する場合、このピンは 1mA 以下にしてください。

入力電圧が出力設定電圧に近づくと、出力電圧を保持するため、デューティ・サイクルは最大になります。このモードの動作では、デューティ・サイクルが最大値に到達すると、LM26001は最大で7つのオフ・パルスをスキップしてデューティ・サイクルを実質的に増加させ、これによって入出力間のドロップアウト電圧を最小限に抑えることができます。オフ・パルスをスキップしている代表的な波形を次に示します。

FIGURE 6. Off-pulse Skipping Waveforms Vin = 3.5V, Vnom = 3.3V, fnom = 305kHz

#### 動作説明(つづき)

UVLO は VIN と VDD の両方で検知され、いずれかの電圧が 2.9V (typ)を下回ると起動します。 VDD は、通常は VIN よりも 200mV 小さい値ですが、 VIN を介して放電することはありません。このため、 VIN 電圧が急激に降下すると、特にスリープ・モード時には、 VDD が高い電圧で保持されます。過渡的な入力電圧の低下が発生した場合、 VDD ピンに比較的容量の大きいコンデンサを接続しておくと、 VDD の放電時間が長くなるため、 UVLO シャットダウンを防止するのに役立ちます。 容量の大きいコンデンサを接続すると、 VDD を保持することになるため、低 VIN の条件下で R<sub>DS(ON)</sub> (およびドロップアウト電圧)を低減します。 代わりに、重負荷条件下では、 VDD 電圧が VIN より数百 mV 低下することがあります。 この場合は、 VIN 電圧が UVLO スレッショルドより高い場合でも、 UVLO は VDD によって起動します。

UVLO が起動すると、LM26001 は、VDD の充電状態が保持されるスタンバイ状態に移行します。 入力電圧と VDD 電圧が上昇して 3.9V (typ) を超えると、LM26001 はソフトスタート・モードから再起動します。

#### **PGOOD**

パワーグッドピン (PGOOD) は、出力電圧の状態を監視する目的で使用できます。このピンは IC 内部でオープン・ドレインの MOSFET に接続されており、出力電圧が動作範囲内に入っている場合にはオープン状態となります。 PGOOD は、出力が定格の 85% を下回るか、EN が Low に設定されると、Low (グラウンドに対して低インピーダンス) に移行します。出力電圧が定格の 92% 以内に復帰すると、PGOOD は High 状態に戻ります。 ノイズ耐性を改善するため、PGOOD がスレッショルドに達してから PGOOD ピンが Low に移行するまでの間には、 $5\mu$ s の遅延時間が設けられています。

#### 設計情報

#### 回路例

Figure 7 に、代表的なアプリケーション回路の全体図を示します。 部品の選定は、以降のセクションでの説明が基準になっています。

FIGURE 7. Example Circuit 1.5A Max, 305 kHz

#### 出力電圧の設定

出力電圧は、「代表的なアプリケーション回路」に示すように、 FBピンでの出力電圧の分圧比によって設定します。 抵抗値は 以下の式から求めます。

$$R2 = \frac{R1}{\left(\frac{Vout}{Vfb} - 1\right)}$$

Vfb の代表値は 1.234V です。

R1とR2の和については、最大値である150k $\Omega$ を推奨します。

入力電圧が減少し、出力電圧の定格に近づくと、「低 Vin 時の動作と UVLO」のセクションで説明したように、LM26001 は7 つのオフ・パルスをスキップする場合があります。 低出力電圧のアプリケーションにて、オン時間が Ton<sub>MIN</sub> に達すると、LM26001 はオン時間をスキップしてレギュレーションを維持します。 スキップするパルスの数に制限はありません。 ただし、このモードの動作では、出力リップル電圧がわずかに増加する場合があります。

#### インダクタ

出力インダクタは、インダクタのリップル電流を基準にして選定します。負荷電流と比較したインダクタのリップル電流の値、つまりリップル率は、Iripple/Iload で定義されます。リップル率は40%未満にする必要があります。インダクタのリップル電流(Iripple)は、次式により求められます。

Iripple =

$$\frac{(Vin - Vout) \times Vout}{fsw \times L \times Vin}$$

リップル率が高いと、インダクタでの損失が増加し、 有効な電流制限値が減少します。

インダクタンスの値を大きくすると出力リップル電圧が小さくなり、効率が高くなりますが、過渡応答特性が若干低下します。インダクタンスの値を小さくするとケースのサイズを小型化できますが、リップルが増加するため有効な電流制限スレッショルドは低下します。

Figure 3 に示したように、インダクタの値は、スリープ・モードのスレッショルドにも影響することに注意してください。

#### 設計情報(つづき)

インダクタを選択する場合は、飽和電流定格がインダクタの最大ピーク電流よりも大きい必要があります。また、電流のRMS値の定格が最大負荷電流より大きいものを選択してください。インダクタのピーク電流 Ipeak は、次式により求められます。

$$lpeak = lload + \frac{lripple}{2}$$

例えば、負荷電流が最大の 1.5A でリップル率が 40% である場合、インダクタ電流のピーク値は 1.8A となりますが、この値は電流制限の最小値である 1.85A を確実に下回っています。インダクタのサイズを大きくすることにより、リップル率とインダクタのピーク電流は低下するため、電流制限のマージンは増加します。

出力インダクタのサイズは、目標とするリップル電圧 Vrip を使用して決定することもできます。Vrip に基づいて最小のインダクタンス値を求める式は次のとおりです。

$$L_{MIN} = \frac{(Vin - Vout) \times Vout \times Re}{Vin \times fsw \times Vrip}$$

Re は出力コンデンサの ESR で、Vrip はピーク・ツー・ピーク 値です。この式では、出力コンデンサに一定の大きさの ESR が存在することを前提にしています。 セラミック製の出力コンデンサには適用できません。

この方法を使用する場合も、リップル率が 40% 未満になることを求められます。

#### 出力コンデンサ

出力コンデンサを選択する場合の主な基準は、等価直列抵抗、つまり ESR です。

ESR (Re) は、出力リップル電圧と過渡応答の要件に基づいて 選択できます。 インダクタの値を選択したら、前述の Lmin の 式を使用して、特定の Re のリップル電圧を計算できます。ESR の値が小さいと、出力リップルも小さくなります。

Re は次式から求めることもできます。

$$Re_{MAX} = \frac{\Delta Vt}{\Delta It}$$

$\Delta$ Vt は、過負荷電流発生時の許容電圧偏移を表し、 $\Delta$ It は、予想される過負荷電流の最大値を表します。

ESR の合計値が大きすぎる場合は、出力コンデンサの容量をいかに大きくしても過負荷電流の要件を満たすことはできません。

リップル電圧と過渡電圧偏移に関する ESR の基準を満たすことができない場合は、 追加のコンデンサを並列に接続します。

セラミック以外のコンデンサの場合、最小出力容量の重要度は 副次的なものであり、この容量は過渡負荷電流の要件によって のみ決まります。

コンデンサの容量が不充分であると、最大 ESR の要件を満たしている場合でも、出力電圧偏移は許容最大値を超えてしまいます。 最小容量は次の式で求められます。

$$C_{MIN} = \frac{L \times \left( \Delta Vt - \sqrt{(\Delta Vt)^2 - (\Delta It \times R_e)^2} \right)}{V_{Aut} \times R_e^2}$$

ESR の合計である Re が Re<sub>MAX</sub> を超えることはないと仮定しています。さらに、L が選択済みであることも前提になっています。

#### 入力コンデンサ

スイッチング・コンバータでは、きわめて高速のスイッチング・パルス電流が入力電源ラインから流れます。このため、LM26001の入力には、ノイズ、EMI、リップルを低減するために入力コンデンサが必要です。入力コンデンサは、動作周囲温度が最高の場合に、リップル電流のRMS最大値と最大入力電圧を扱えるものを選択しなければなりません。入力リップル電流のRMS値を求めるための式は、次のとおりです。

$$Irms = \frac{Iload \times \sqrt{Vout \times (Vin - Vout)}}{Vin}$$

ノイズを抑制するには、 $1.0\,\mu$  F  $\sim 10\,\mu$  F の範囲内のセラミック・コンデンサをできる限り VIN ピンの近くに配置します。

ESR 値の高い大型の入力コンデンサも合わせて使用します。このコンデンサを推奨する理由は、電源投入時の入力電圧スパイクを抑えるためと、過渡電圧発生時に入力電圧を保持するためです。入力電圧が低いアプリケーションでは、入力容量が不十分な場合、電源の過渡電圧が UVLO スレッショルドを下回ることがあります。 大容量コンデンサには、タンタル・コンデンサと電解コンデンサの両方の種類が適しています。 ただし、入力電圧が高い場合は大型のタンタル・コンデンサを入手できない場合があります。 また、タンタル・コンデンサの定格は、動作電圧の 2 倍以上を必要とします。

#### ブートストラップ

内部スイッチの駆動電圧は、BOOTピンを介して供給されます。このピンには、セラミック・コンデンサ Cboot をスイッチ・ノードから接続する必要があります。 Cboot は、代表的なアプリケーション回路では C4 と表示されています。 LM26001 は内部で VDD 電圧を供給しているため、外付けダイオードは必要ありません。 Cboot の値は  $0.1\,\mu$  F 以上を推奨します。 値を小さくすると駆動電圧の保持時間が不十分になり、消費電力が増加します。

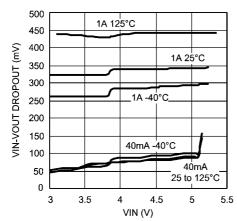

低 Vin 時の動作では、オン時間を長くすると、ブートストラップ・コンデンサの電荷が放電されてしまう危険性があります。 Cboot コンデンサが放電されて、その電圧が約 2.5V を下回ると、LM26001 は高周波数の再充電モードに移行します。Cboot コンデンサは、ブロック図に示す LG 同期整流 FET を介して再充電されます。Cboot コンデンサが再充電されると、スイッチングは通常状態に戻ります。

#### キャッチ・ダイオード

IC 内部のスイッチがオフになっている場合、出力電流はキャッチ・ダイオードから流れます。一方、スイッチがオンになっている場合、キャッチ・ダイオードには Vin と同じ値の逆方向電圧が印加されます。このため、キャッチ・ダイオードを選択する上で重要なパラメータは、ピーク電流とピーク逆耐圧です。キャッチ・ダイオードを流れる平均電流は次式により求められます。

$$ID_{AVE} = Iload \times (1 - D)$$

D は Vout/Vin で定義されるデューティ・サイクルです。キャッチ・ダイオードは、デューティ・サイクルが最小のときに最大の電流を供給します。このため、IDAVE は最大入力電圧を前提として計算します。キャッチ・ダイオードの定格は、この電流を連続して流すことができるものにします。過電流や出力短絡の条件では、キャッチ・ダイオードの定格を、電流制限のピーク値に等しいピーク電流を流すことができるものにしてください。

#### 設計情報(つづき)

キャッチ・ダイオードのピーク逆電圧定格は、最大入力電圧よりも大きい値にする必要があります。

必ずショットキ・ダイオードを使用してください。ショットキ・ダイオードの順方向電圧は小さいため、効率や BOOT 電圧が最大になるだけでなく、負の大電圧スパイクから SW ピンを保護する役割も果たしています。

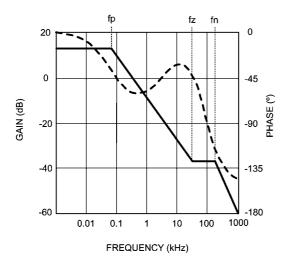

#### 位相補償

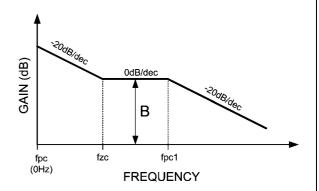

ループ補償の目的は、安定した動作を確保しながら動的な性能を維持することです。安定性はループ・ゲイン測定器を使用して解析できますが、動的な性能はループ・ゲインと過負荷電流応答の両方で解析します。ループ・ゲインは、制御 - 出力間伝達関数(パワー段)と帰還伝達関数(位相補償回路網)の積に等しくなります。

安定性を確保するには、きわめて低い周波数からクロスオーバー周波数を超える周波数まで、傾きが - 20dB/dec のループ・ゲイン特性を得ることが目標になります。また、クロスオーバー周波数はスイッチング周波数の 1/5 以下にします。つまり、スイッチング周波数が 300kHz の場合は 60kHz 以下です。

動的な性能を向上することが目的の場合は、帯域幅を広くすることにより、負荷過渡応答が高速になります。DC ゲインが大きいと、DC レギュレーション精度が高くなります (すなわち、負荷変動または電源電圧変動に対するDC電圧変化が小さいという意味です)。このループ・ゲインを達成するには、位相補償用部品を制御 - 出力間ボーデ線図の形に応じて設定します。代表的な図を Figure 8 に示します。

FIGURE 8. Control-Output Transfer Function

制御 - 出力間伝達関数は、1 つのポール (fp)、1 つのゼロ (fz)、fn (x)、x) での x0 つのポールから構成されます。

Figure 8 を参照しながら以下の操作手順で、 — 20dB/dec のループ・ゲイン減衰特性を設計します。

- 1. ポールの周波数を 0Hz (fpc) に決めます。

- 2. ゼロの周波数を fp (fzc) に決めます。

- 3. 第2ポールの周波数を fz (fpc1) に決めます。

作成される帰還(位相補償)ボーデ線図を Figure 9 に示します。制御 - 出力間応答をフ帰還応答に加えると、ほぼ連続した-20dB/decの傾きが得られます。

FIGURE 9. Feedback Transfer Function

制御-出力間のコーナー周波数の概算値は、次式により求められます。

$$fz = \frac{1}{2\pi \times \text{Re} \times \text{Co}}$$

$$fp = \frac{1}{10 \times \pi \times \text{Ro} \times \text{Co}} + \frac{0.5}{2 \times \pi \times \text{L} \times \text{fsw} \times \text{Co}}$$

$$fn = \frac{\text{fsw}}{2}$$

Co は出力容量、Ro は負荷抵抗、Re は出力コンデンサの ESR、fsw はスイッチング周波数を表します。この式には、スロープ補償の効果と電流センス・ゲインの効果が盛り込まれています。ただし、この式はループ補償計算を簡略化するための近似式です。正確な伝達関数を求めるには、センス・アンプのゲインを0.2V/V、スロープ補償を36mVp-pにしてください。

fp は出力の回路網で決まるため、負荷によってシフトします。まず、想定される負荷の全範囲にわたって周波数の範囲 (fpmin/max)を決めます。次に、以下に説明し、Figure 10 に示すように、補償用部品の値を決めます。

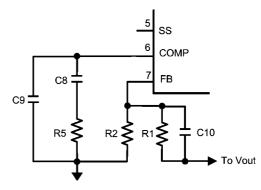

FIGURE 10. Compensation Network

- 1. 補償回路網により、0Hzに近い低周波側のポール (fpc) が自動的に決まります。

- 2. fp の範囲が決まったら、次式によって R5 を求めます。

$$R5 = \frac{B}{gm} \times \left( \frac{R1 + R2}{R2} \right)$$

## 設計情報(つづき)

B は fp と fz 間に設定する帰還ゲイン (単位: V/V)、gm はエラー・アンプのトランスコンダクタンスを表します。 設計の出発点としては、通常、10dB (3.3V/V) 付近のゲイン値が適しています。 帯域幅は、R5 の値が増加するにつれて広がります。

3. 次に、C8 を使用して fp 付近にゼロ (fzc) を作成します。 C8 は次式により求められます。

$$C8 = \frac{1}{2 \times \pi \times fP_{MAX} \times R5}$$

C8 の選択値により、fzc は、fpmax の  $1/10 \sim 10$  倍までの間で、かつ fpmin より高い周波数の範囲内に入ります。 通常は C8 の値が大きい (fpmin に近い) 方が安定したループが得られますが、この値が大きすぎると過渡応答時間が長くなります。逆に、C8 の値が小さいと過渡応答は高速になりますが、位相マージンは小さくなります。

4. 第2ポール (fpc1) も fz に設定してかまいません。このポールは、1つのコンデンサ C9 により作成できます。このコンデンサの最小値は次式から求められます。

$$C9 = \frac{1}{2 \times \pi \times fz \times R5}$$

C9 は、必ずしもすべてのアプリケーションで必要なわけではありません。ただし、定格周波数より低い動作周波数で外部同期が行われる場合には、C9 の接続を推奨します。C9 は、安定性確保のためには必要ありませんが、ノイズを抑える場合に非常に役立ちます。

位相の進みコンデンサを追加することによって位相マージンやゲイン・マージンを増やすこともできます。位相の進みコンデンサは、入力電圧の高いアプリケーションや、定格より高い周波数に外部同期する場合などに最も役立ちます。Figure 10でC10として示されるこのコンデンサは、上側の帰還抵抗 R1と並列に配置します。C10は、位相補償回路網に新たなゼロおよびポールを作り出します。これらの周波数は、次式により求められます。

$$fzff = \frac{1}{2 \times \pi \times R1 \times C10}$$

$$fpff = \frac{fzff \times Vout}{Vfb}$$

位相の進みコンデンサは、ゼロ周波数領域周辺のループ位相を持ち上げます。fzffは、C9によって設定される周波数 fpzlよりも多少低い値に設定します。ただし、C10 が大きすぎる場合、C9の効果はありません。

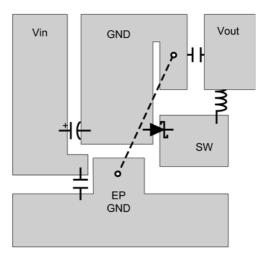

#### プリント基板レイアウト

LM26001 などのスイッチング・レギュレータでは、良好な基板レイアウトが重要です。第1に、グラウンド・パターン領域は放熱の目的を十分に果たすことのできる広さである必要があります。第2に、スイッチング・ノイズの影響を低減するための適切な基準に従っている必要があります。

スイッチ・モード・コンバータは、きわめて高速なスイッチング・デバイスです。このようなデバイスでは、入力電流の急激な増加と配線の寄生インダクタンスが相まって、SWノードとVINノードの両方で不要な Ldi/dt ノイズ・スパイクが発生します。このノイズの大きさは出力電流が増加するにつれて大きくなる傾向があります。寄生スパイク・ノイズは不要な電磁放射 (EMI) を招

く場合があり、またチップ性能に問題を与えるときがあります。 したがって、このスイッチング・ノイズの影響を最小限に抑える ために注意が必要です。

電流モード・デバイスでの電流検出回路は、スイッチング・ノイズの影響を容易に受ける可能性があります。このノイズは、スペクトル・ノイズの増大につながるデューティ・サイクル・ジッタを引き起こすことがあります。このノイズを無視するため、LM26001では各サイクルの先頭に100nsのブランキング時間を設けていますが、ブランキング時間後もある程度のノイズが残留することがあります。以下に示す重要な指針に従うと、スイッチング・ノイズ自体と電流センス時におけるノイズの影響を最小限に抑えるのに役立ちます。

スイッチ・ノード領域は、できる限り小さくします。キャッチ・ダイオード、入力コンデンサ、出力コンデンサは、大面積のグラウンド・パターンに接地します。その際、大容量の入力コンデンサは、キャッチ・ダイオードのアノードにできる限り近づけて接地します。さらに、キャッチ・ダイオードと大容量入力コンデンサ間のグラウンド領域はきわめてノイズが多いため、その他のグラウンド・パターンからはある程度分離することが必要です。

入力のセラミック・コンデンサは、できる限り VIN ピンの近くで接続し、GND ピンの近くで接地する必要があります。多くの場合、このコンデンサはプリント配線基板の裏面に配置するのが最も容易な部品です。GND ピンの近くに配置することが現実的でない場合、入力のセラミック・コンデンサはキャッチ・ダイオードのグラウンドに近い場所で接地することもできます。これまでに説明したレイアウトの推奨事項を Figure 11 に図で示します。

FIGURE 11. Example PCB Layout

EP、GNDピン、小信号回路部品 (COMP、FB、FREQ) は、(Figure 11 では EP GND として示され、回路図では信号グラウンド記号で示されている)別個のグラウンド・パターンに接続するのが賢明です。露出型パッドと GNDピンは、両方ともグラウンドに接続する必要があります。このノイズの少ない方のパターンは、ノイズの少ない箇所、つまり Figure 11 において点線で示されているとおり、なるべく Vout 近辺のグラウンド・パターンで大電流側のグラウンド・パターンに接続します。

EP GND パターンは放熱にも利用されるため、できる限り広くします。 他の層を利用できる場合は、他の層への熱の流れを増加させるため、EP の直下にいくつかのスルーホールを設けることができます。 スルーホールの直径の推奨値は 0.3mm です。

FBピンから分圧抵抗までの配線は短くしてください。また、FBピンまでの配線全体は、インダクタ・ノードおよびスイッチ・ノードに近づけないようにする必要があります。スイッチング・レギュレータのプリント配線基板レイアウトの詳細については、アプリケーション・ノート AN-1229 を参照してください。

## 熱に関する考慮事項とサーマル・シャットダウン

LM26001 は電流制限回路を内蔵していますが、周囲温度が80℃を超えると、実際の最大負荷電流はデバイス温度の上昇によって制限される場合があります。このため、最大許容負荷電流を求めるには、温度上昇を考慮する必要があります。

温度上昇は、デバイス内部での消費電力の関数です。消費電力 (PD) と温度上昇を計算するには、次式を使用します。 PD の合計は、FET のスイッチング損失、 FET の DC 損失、駆動損失、 Iq、 VBIAS 損失の和になります。

$$PD_{TOTAL} = Psw_{AC} + Psw_{DC} + PQG + P_{Iq} + P_{VBIAS}$$

$$Psw_{AC} = Vin x Iload x fsw x \left(\frac{Vin x 10^{-9}}{1.33}\right)$$

$$\begin{aligned} \text{Psw}_{\text{DC}} &= \text{D} \times \text{Iload}^2 \times (0.2 + 0.00065 \times (\text{T}_{\text{j}} - 25)) \\ \text{P}_{\text{QG}} &= \text{Vin} \times 4.6 \times 10^{-9} \times \text{fsw} \\ \text{P}_{\text{Iq}} &= \text{Vin} \times \text{Iq} \\ \text{P}_{\text{VBIAS}} &= \text{Vbias} \times \text{I}_{\text{VBIAS}} \end{aligned}$$

この消費電力合計値が求められると、接合部温度は次式により求められます。

$$Tj = Ta + (PD_{TOTAL} \times \theta_{JA})$$

大面積の銅パターン領域がある多層基板を使用した場合は、 $\theta_{\rm JA}=38\,^{\circ}{\rm C}\,/{\rm W}$  (typ) になります。  $\theta_{\rm JA}$  は、基板の種類や金属被覆部分の面積により変化します。

最大許容消費電力を求めるには、 $T_j = 125$   $\mathbb{C}$ と仮定します。接合部温度が動作温度の最大定格である 125  $\mathbb{C}$ を超えないようにするには、予想される最大の動作周波数、最大周囲温度、最小入力電圧および最大入力電圧で消費電力を確認します。計算した最大負荷電流は連続動作を基準にしているため、過渡条件時にはこの値を超えることがあります。

消費電力が最大許容レベルを超えたままになっていると、デバイス温度は上昇し続けます。接合部温度が最大値を超えると、LM26001 はサーマル・シャットダウン (TSD) モードに移行します。TSDモードでは、接合部温度が降下して通常の動作制限範囲内に戻るまで、IC はシャットダウン状態を維持します。この状態では、デバイスはソフトスタート・モードで再起動します。

eTSSOP-16 Package 16-Lead Exposed Pad TSSOP Package NS Package Number MXA16A

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の割品を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用または供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社 は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

#### 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

をいるしているとん。 ここで、生命維持装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは 支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与 えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不 具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいい ます。

National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2009 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

## ナショナル セミコンダクター ジャパン株式会社

本社/〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上