# LMH6580,LMH6581

LMH6580/LMH6581 8x4 500 MHz Analog Crosspoint Switch, Gain of 1, Gain of 2

Literature Number: JAJSAR2

National Semiconductor 2007年9月

# LMH6580/LMH6581

8 x 4 500MHz アナログ・クロスポイント・スイッチ、 ゲイン 1/ ゲイン 2

## 概要

LMH® 製品ファミリに、新たにノンブロッキング・アーキテクチャを 持つ高速アナログ・クロスポイント・スイッチ LMH6580/LMH6581 が加わりました。高解像度ビデオ(UXGA以上)などの高速、DC 結合のアナログ信号用に設計された LMH6580/LMH6581 は、8 個の入力と4個の出力を備えています。 ノンブロッキング・アーキ テクチャにより、既に他の出力で選択済みの入力も含め、任意の 出力を任意の入力に接続できます。入力は完全にバッファされて いるため、どのようなソース・インピーダンスに対してもマッチングが 可能です。出力もバッファされており、2系統のバック終端された ビデオ負荷を駆動できます(75 負荷)。また入出力を高インピー ダンスの非アクティブ状態にできるため、2 つのデバイスを組み合 わせれば、性能を落とさずに入出力を8 x 8 や 16 x 4 などのア レイ・サイズに拡張できます。 LMH6580/LMH6581 は、4 ピンの シリアル・インタフェースによって制御します。このインタフェースは 3 線式インタフェースとして構成できます。シリアル・モードとアドレ ス指定モードを搭載しています。

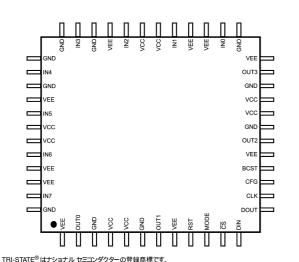

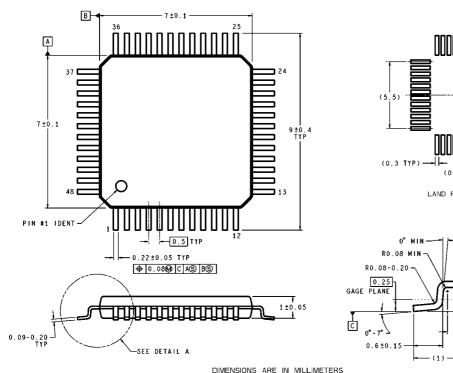

LMH6580/LMH6581 は、48 ピンの TQFP パッケージにて提供されます。 基板の両面実装や拡張時のピン接続を容易にするために対角線対称にピンを割り当ててあります。

# 特長

8入力および4出力

48 ピン TQFP パッケージ

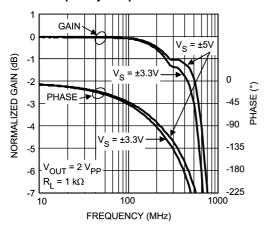

- 3dB 帯域幅 (V<sub>OUT</sub> = 2V<sub>PP</sub>、R<sub>L</sub> = 1k ) 500MHz

- 3dB 帯域幅 (V<sub>OUT</sub> = 2V<sub>PP</sub>、R<sub>L</sub> = 150 ) 450MHz

高速スルーレート 2100V/µs

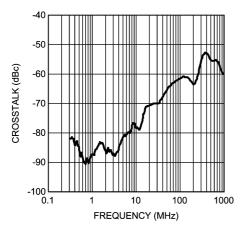

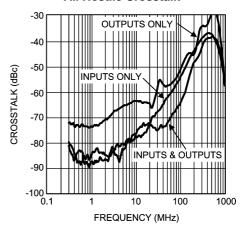

チャネル間クロストーク (10/100MHz) - 70/ - 52dBc

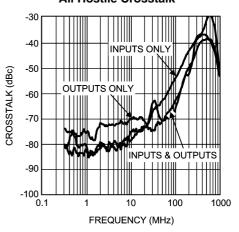

All-Hostile クロストーク (10/100MHz) - 55/ - 45dBc

使いやすいシリアル・プログラミング 4 線バス

2 つのプログラミング・モード

シリアル・モードとアドレス指定モード

拡張容易な対称ピン配置

出力電流  $\pm 70$ mA 2 つのゲイン・オプション  $A_V = 1$  または  $A_V = 2$

# アプリケーション

スタジオ・モニタ/製作用ビデオ・システム 会議室用マルチメディア・ビデオ・システム KVM(キーボード/ビデオ/マウス)システム セキュリティ/監視システム マルチアンテナ・ダイバシティ・ラジオ ビデオ・テスト機器 医療用画像処理

広帯域ルータおよびスイッチ

#### ピン配置図

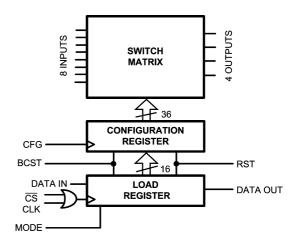

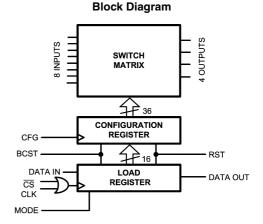

# ブロック図

LMH® はナショナル セミコンダクターの登録商標です。

絶対最大定格 (Note 1) 保存温度範囲 - 65 ~ + 150 本データシートには軍用・航空宇宙用の規格は記載されていません。 ハンダ付け条件 関連する電気的信頼性試験方法の規格を参照ください。 赤外線または対流方式(20秒) 235 流動ハンダ付け(10秒) 260 ESD 耐圧 (Note 2) 人体モデル 2000V 動作定格 (Note 1) マシン・モデル 200V - 40 ~+ 85  $V_S$ ± 6V 温度範囲 (Note 4) I<sub>IN</sub>(入力ピン)  $\pm 20 \text{mA}$ 電源電圧範囲  $\pm 3V \sim \pm 5.5V$  $I_{OUT}$ (Note 3) V - V +入力電圧範囲 熱抵抗 JA 48 🖒 TQFP 44 /W 12 /W 最大接合部温度 +150

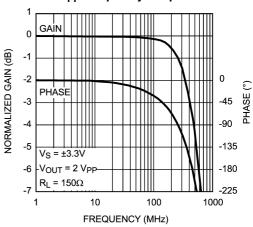

# ± 3.3V 電気的特性 (Note 5)

特記のない限り代表値は、 $T_A$  = 25 、 $A_V$  = + 2、 $V_S$  = ± 3.3V、 $R_L$  = 100 に対するものです。 太字のリミット値は、全温度範囲に対して適用されます。

| Symbol                    | Parameter                           | Conditions                                                                   | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8) | Units  |

|---------------------------|-------------------------------------|------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--------|

| Frequency                 | Domain Performance                  |                                                                              | 1.`             |                 | , ,             | l .    |

| SSBW                      | -3 dB Bandwidth                     | $V_{OUT} = 0.5 V_{PP}$                                                       |                 | 425             |                 |        |

| LSBW                      | 1                                   | LMH6580 V <sub>OUT</sub> = 1 V <sub>PP</sub> ,                               |                 | 500             |                 |        |

|                           |                                     | LMH6581 V <sub>OUT</sub> = 2 V <sub>PP</sub> , R <sub>L</sub> = 1 k $\Omega$ |                 |                 |                 | MHz    |

|                           |                                     | LMH6580 V <sub>OUT</sub> = 1 V <sub>PP</sub> ,                               |                 | 450             |                 |        |

|                           |                                     | LMH6581 $V_{OUT} = 2 V_{PP}, R_{L} = 150\Omega$                              |                 |                 |                 |        |

| GF                        | 0.1 dB Gain Flatness                | LMH6580 V <sub>OUT</sub> = 1 V <sub>PP</sub> ,                               |                 | 70              |                 |        |

|                           |                                     | LMH6581 V $_{OUT}$ = 2 $V_{PP}$ , $R_{L}$ = 150 $\Omega$                     |                 |                 |                 | MHz    |

| Time Dom                  | ain Response                        |                                                                              |                 |                 |                 |        |

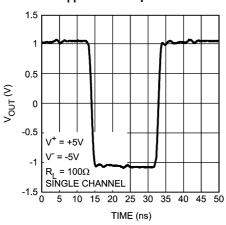

| t <sub>r</sub>            | Rise Time                           | LMH6580 1V Step, LMH6581                                                     |                 | 3.1             |                 | ns     |

|                           |                                     | 2V Step, 10% to 90%                                                          |                 |                 |                 |        |

| t <sub>f</sub>            | Fall Time                           | LMH6580 1V Step, LMH6581                                                     |                 | 1.4             |                 | ns     |

| 00                        | Overalloss                          | 2V Step, 10% to 90%                                                          |                 |                 |                 |        |

| OS Overshoot SR Slew Rate |                                     | 2V Step                                                                      |                 | <1              |                 | %      |

| Sh  Sie                   | Slew Rate                           | LMH6580, 2 V <sub>PP</sub> , 40% to 60%<br>(Note 6)                          |                 | 900             |                 | V/µs   |

|                           | Slew Rate                           | LMH6581, 2 V <sub>PP</sub> , 40% to 60%                                      |                 | 1700            |                 | V/µs   |

|                           | Siew Hate                           | (Note 6)                                                                     |                 | 1700            |                 | V/μS   |

| t <sub>s</sub>            | Settling Time                       | 2V Step, V <sub>OUT</sub> within 0.5%                                        |                 | 7               |                 | ns     |

| Distortion                | And Noise Response                  |                                                                              | <u> </u>        |                 | <b>I</b>        | L      |

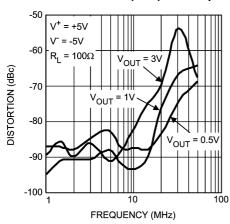

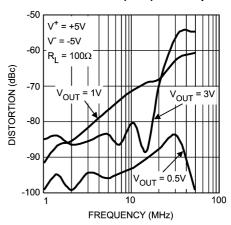

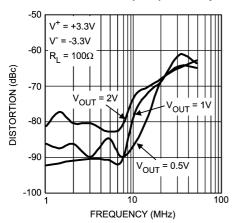

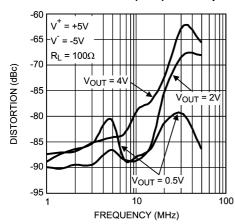

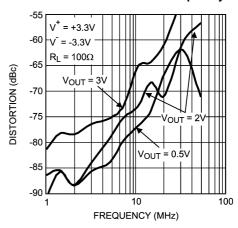

| HD2                       | 2 <sup>nd</sup> Harmonic Distortion | 2 V <sub>PP</sub> , 10 MHz                                                   |                 | -76             |                 | dBc    |

| HD3                       | 3rd Harmonic Distortion             | 2 V <sub>PP</sub> , 10 MHz                                                   |                 | -76             |                 | dBc    |

| e <sub>n</sub>            | Input Referred Voltage Noise        | >1 MHz                                                                       |                 | 12              |                 | nV/√Hz |

| i <sub>n</sub>            | Input Referred Noise Current        | >1 MHz                                                                       |                 | 2               |                 | pA/√Hz |

| XTLK                      | Crosstalk                           | All Hostile, f = 100 MHz                                                     |                 | -45             |                 | dBc    |

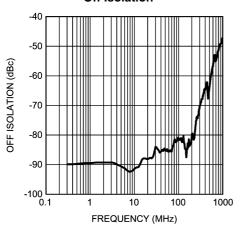

| ISOL                      | Off Isolation                       | f = 100 MHz                                                                  |                 | -60             |                 | dBc    |

| Static, DC                | Performance                         |                                                                              | I               | l               | L               |        |

| A <sub>V</sub>            | Gain                                | LMH6581                                                                      | 1.986           | 2.00            | 2.014           |        |

| •                         |                                     | LMH6580                                                                      | 0.994           | 1.00            | 1.005           |        |

| V <sub>os</sub>           | Input Offset Voltage                |                                                                              |                 | ±3              | ±17             | mV     |

| TCV <sub>os</sub>         | Input Offset Voltage Average Drift  | (Note 10)                                                                    |                 | 38              |                 | μV/°C  |

| I <sub>B</sub>            | Input Bias Current                  | Non-Inverting (Note 9)                                                       |                 | -5              |                 | μA     |

| TCIB                      | Input Bias Current Average Drift    | Non-Inverting (Note 10)                                                      |                 | -12             |                 | nA/°C  |

www.national.com/jpn/ 2

# ± 3.3V 電気的特性 (Note 5)(つづき)

特記のない限り代表値は、 $T_A$  = 25 、 $A_V$  = + 2、 $V_S$  = ± 3.3V、 $R_L$  = 100 に対するものです。 太字のリミット値は、全温度範囲に対して適用されます。

| Symbol          | Parameter                          | Conditions                                 | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8) | Units |  |

|-----------------|------------------------------------|--------------------------------------------|-----------------|-----------------|-----------------|-------|--|

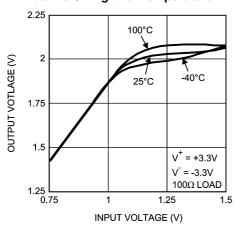

| v <sub>o</sub>  | Output Voltage Range               | LMH6581, $R_L = 100\Omega$                 | ±1.8            | ±2.1            |                 |       |  |

|                 |                                    | LMH6580, $R_L = 100\Omega$                 |                 |                 | V               |       |  |

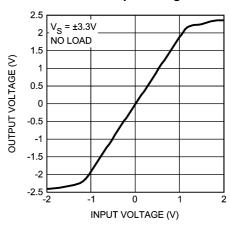

| $v_o$           | Output Voltage Range               | LMH6581, $R_L = \infty \Omega$ , (Note 11) | ±2.08           | ±2.2            |                 |       |  |

|                 |                                    | LMH6580 R <sub>L</sub> = $\infty\Omega$ ,  | ±1.25           | ±1.3            |                 | V     |  |

| PSRR            | Power Supply Rejection Ratio       |                                            |                 | -45             |                 | dBc   |  |

| I <sub>cc</sub> | Positive Supply Current            | R <sub>L</sub> = ∞                         |                 | 50              | 60              | mA    |  |

| I <sub>EE</sub> | Negative Supply Current            | R₁ = ∞                                     |                 | 50              | 56              | mA    |  |

|                 | Tri State Supply Current           | RST Pin > 2.0V                             |                 | 10              | 13              | mA    |  |

| Miscellan       | eous Performance                   |                                            |                 |                 |                 |       |  |

| R <sub>IN</sub> | Input Resistance                   | Non-Inverting                              |                 | 100             |                 | kΩ    |  |

| C <sub>IN</sub> | Input Capacitance                  | Non-Inverting                              |                 | 1               |                 | pF    |  |

| Ro              | Output Resistance Enabled          | Closed Loop, Enabled                       |                 | 300             |                 | mΩ    |  |

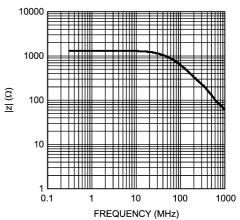

| R <sub>o</sub>  | Output Resistance Disabled         | LMH6580                                    |                 | 50              |                 | l.O   |  |

|                 |                                    | LMH6581                                    | 1100            | 1350            | 1500            | kΩ    |  |

| CMVR            | Input Common Mode Voltage<br>Range |                                            |                 | ±1.3            |                 | V     |  |

| I <sub>o</sub>  | Output Current                     | Sourcing, V <sub>O</sub> = 0 V             |                 | ±50             |                 | mA    |  |

| Digital Co      | ntrol                              |                                            |                 | ,               |                 |       |  |

| V <sub>IH</sub> | Input Voltage High                 |                                            | 2.0             |                 |                 | ٧     |  |

| V <sub>IL</sub> | Input Voltage Low                  |                                            |                 |                 | 0.8             | ٧     |  |

| V <sub>OH</sub> | Output Voltage High                |                                            |                 | >2.0            |                 | ٧     |  |

| V <sub>OL</sub> | Output Voltage Low                 |                                            |                 | <0.4            |                 | ٧     |  |

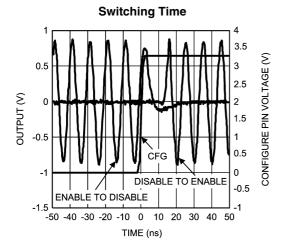

|                 | Switching Time                     |                                            |                 | 15              |                 | ns    |  |

| T <sub>s</sub>  | Setup Time                         |                                            |                 | 7               |                 | ns    |  |

| T <sub>S</sub>  | Hold Time                          |                                            |                 | 7               |                 | ns    |  |

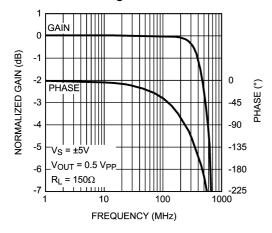

# ± 5V 電気的特性 (Note 5)

特記のない限り代表値は、 $T_A$  = 25 、 $A_V$  = + 2、 $V_S$  = ± 5V、 $R_L$  = 100 に対するものです。太字のリミット値は、全温度範囲に対して適用されます。

| Symbol         | Parameter            | Conditions                                          | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8) | Units |

|----------------|----------------------|-----------------------------------------------------|-----------------|-----------------|-----------------|-------|

| Frequenc       | y Domain Performance |                                                     |                 |                 |                 |       |

| SSBW           | -3 dB Bandwidth      | V <sub>OUT</sub> = 0.5 V <sub>PP</sub> (Note 11)    |                 | 450             |                 |       |

|                |                      | LMH6580 $V_{OUT} = 1 V_{PP}$ ,                      |                 | 500             |                 |       |

|                |                      | LMH6581 $V_{OUT} = 2 V_{PP}$ , $R_L = 1 k\Omega$    |                 |                 |                 | MHz   |

| LSBW           |                      | LMH6580 $V_{OUT} = 1 V_{PP}$                        |                 | 450             |                 |       |

|                |                      | LMH6581 $V_{OUT} = 2 V_{PP}, R_{L} = 150\Omega$     |                 |                 |                 |       |

| GF             | 0.1 dB Gain Flatness | LMH6580, $V_{OUT} = 1 V_{PP}$ ,                     |                 | 100             |                 | MHz   |

|                |                      | LMH6581, $V_{OUT} = 2 V_{PP}$ , $R_{L} = 150\Omega$ |                 |                 |                 |       |

| DG             | Differential Gain    | $R_L = 150\Omega$ , 3.58 MHz/4.43 MHz               |                 | .05             |                 | %     |

| DP             | Differential Phase   | $R_L = 150\Omega$ , 3.58 MHz/4.43 MHz               |                 | .05             |                 | deg   |

| Time Dom       | nain Response        |                                                     |                 |                 |                 |       |

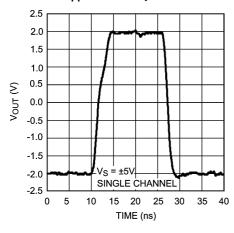

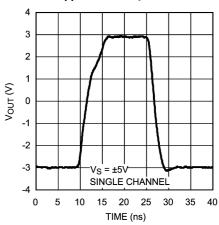

| t <sub>r</sub> | Rise Time            | LMH6580 2V, Step, 10% to 90%                        |                 | 2.8             |                 | no    |

| ·              |                      | LMH6581 2V, Step, 10% to 90%                        |                 | 1.2             |                 | ns    |

| t <sub>f</sub> | Fall Time            | 2V Step, 10% to 90%                                 |                 | 1.6             |                 | ns    |

| os             | Overshoot            | 2V Step                                             |                 | <1              |                 | %     |

# ± **5V** 電気的特性 (Note 5)(つづき)

特記のない限り代表値は、 $T_A$  = 25 、 $A_V$  = + 2、 $V_S$  = ± 5V、 $R_L$  = 100 に対するものです。太字のリミット値は、全温度範囲に対して適用されます。

| Symbol                       | Parameter                                           | Conditions                                               | *Min<br>(Note 8)       | Typ<br>(Note 7)         | Max<br>(Note 8) | Units<br>V/µs                         |  |

|------------------------------|-----------------------------------------------------|----------------------------------------------------------|------------------------|-------------------------|-----------------|---------------------------------------|--|

| SR                           | Slew Rate                                           | LMH6580, 2 V <sub>PP</sub> , 40% to 60%<br>(Note 6)      |                        | 1200                    |                 |                                       |  |

| SR                           | Slew Rate                                           | LMH6581, 6 V <sub>PP</sub> , 40% to 60%                  | · ·                    | 2100                    |                 | V/µs                                  |  |

| <b>,</b>                     | Settling Time                                       | (Note 6)<br>2V Step, V <sub>OUT</sub> Within 0.5%        | ,                      | 6                       |                 | ns                                    |  |

| l <sub>s</sub><br>Distortion | And Noise Response                                  | ZV Step, V <sub>OUT</sub> Within 0.3%                    |                        |                         |                 | 115                                   |  |

| HD2                          | 2 <sup>nd</sup> Harmonic Distortion                 | 2 V <sub>PP</sub> , 5 MHz                                | <u> </u>               | -80                     |                 | dBc                                   |  |

| HD3                          | 3rd Harmonic Distortion                             | 2 V <sub>PP</sub> , 5 MHz                                |                        | -70                     |                 | dBc                                   |  |

| e <sub>n</sub>               | Input Referred Voltage Noise                        | >1 MHz                                                   |                        | 12                      |                 | nV√Hz                                 |  |

| -n<br>I <sub>n</sub>         | Input Referred Noise Current                        | >1 MHz                                                   |                        | 2                       |                 | pA/√Hz                                |  |

| n<br>XTLK                    | ·                                                   |                                                          |                        | -45                     |                 | dBc                                   |  |

| AILK                         | Cross Talk                                          | All Hostile, f = 100 MHz Channel to Channel, f = 100 MHz |                        | - <del>4</del> 5<br>-52 |                 | dBc                                   |  |

| SOL                          | Off Isolation                                       | f = 100 MHz                                              | -                      | -65                     |                 | dBc                                   |  |

|                              | Performance                                         | 1 - 100 14112                                            |                        |                         | İ               | l dbo                                 |  |

| A <sub>V</sub>               | Gain                                                | LMH6581                                                  | 1.986                  | 2.00                    | 2.014           | <u> </u>                              |  |

|                              |                                                     | LMH6580                                                  | 0.995                  | 1.00                    | 1.005           |                                       |  |

| V <sub>os</sub>              | Input Offset Voltage                                |                                                          |                        | ±2                      | ±17             | mV                                    |  |

| TCV <sub>os</sub>            | Input Offset Voltage Average Drift                  | (Note 10)                                                |                        | 38                      |                 | μV/°C                                 |  |

| В                            | Input Bias Current                                  | Non-Inverting (Note 9)                                   |                        | -5                      | ±12             | μA                                    |  |

| ГСІ <sub>В</sub>             | Input Bias Current Average Drift                    | Non-Inverting (Note 10)                                  |                        | -12                     |                 | nA/°C                                 |  |

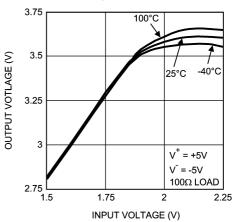

| v <sub>o</sub>               | Output Voltage Range                                | LMH681, $R_L = 100\Omega$                                | ±3.4                   | ±3.6                    |                 |                                       |  |

|                              |                                                     | LMH6580, $R_L = 100\Omega$                               | ±2.9                   | ±3.0                    |                 | \ \                                   |  |

| v <sub>o</sub>               | Output Voltage Range                                | LMH6581, $R_L = \infty \Omega$                           | ±3.7                   | ±3.9                    |                 |                                       |  |

|                              | Capacitangs   Image                                 |                                                          | ±2.9                   | ±3.0                    |                 | <b>┤</b> ∨                            |  |

| PSRR                         | Power Supply Pojection Potio                        | LMH6580, $R_L = \infty \Omega$                           | -42                    | -45                     |                 | dBc                                   |  |

| XTLK                         | Power Supply Rejection Ratio DC Crosstalk Rejection | DC, Channel to Channel                                   | - <del>42</del><br>-62 | - <del>45</del>         |                 | dBc                                   |  |

| OISO                         | DC Off Isloation                                    | DC                                                       | -60                    | -90                     |                 | dBc                                   |  |

| l <sub>cc</sub>              | Positive Supply Current                             | R <sub>L</sub> = ∞                                       | +                      | 54                      | 66              | mA                                    |  |

|                              | Negative Supply Current                             | /                                                        |                        | 50                      | 62              | mA                                    |  |

| EE                           | 1,1,2                                               | R <sub>L</sub> = ∞                                       | -                      | 14                      |                 | <b>!</b>                              |  |

| Miscellane                   | Tri State Supply Current                            | N31 FIII > 2.0V                                          |                        | 1 14                    | 17              | mA                                    |  |

| R <sub>IN</sub>              | Input Resistance                                    | Non-Inverting                                            |                        | 100                     | I               | kΩ                                    |  |

| C <sub>IN</sub>              | Input Capacitance                                   | Non-Inverting                                            |                        | 1                       |                 | pF                                    |  |

| R <sub>o</sub>               | Output Resistance Enabled                           | Closed Loop, Enabled                                     |                        | 300                     |                 | mΩ                                    |  |

| R <sub>o</sub>               | Output Resistance Disabled                          | LMH6580, Resistance to Ground                            | -                      | 50                      |                 | 11132                                 |  |

| 0                            |                                                     | LMH6581, Resistance to Ground                            | 1100                   | 1300                    | 1500            | kΩ                                    |  |

| CMVR                         | Input Common Mode Voltage<br>Range                  | ,                                                        |                        | ±3.0                    |                 | V                                     |  |

| l <sub>o</sub>               | Output Current                                      | Sourcing, V <sub>O</sub> = 0 V                           | ±60                    | ±70                     |                 | mA                                    |  |

| Digital Co                   | ntrol                                               |                                                          |                        | <b>.</b>                |                 | · · · · · · · · · · · · · · · · · · · |  |

| V <sub>IH</sub>              | Input Voltage High                                  |                                                          | 2.0                    |                         |                 | V                                     |  |

| v <sub>IL</sub>              | Input Voltage Low                                   |                                                          |                        |                         | 0.8             | V                                     |  |

| V <sub>OH</sub>              | Output Voltage High                                 |                                                          |                        | >2.4                    |                 | V                                     |  |

| V <sub>OL</sub>              | Output Voltage Low                                  |                                                          |                        | <0.4                    |                 | V                                     |  |

| JL .                         | Switching Time                                      |                                                          |                        | 15                      |                 | ns                                    |  |

| T <sub>s</sub>               | Setup Time                                          |                                                          | 1                      | 5                       |                 | ns                                    |  |

| T <sub>H</sub>               | Hold Time                                           |                                                          |                        | 5                       |                 | ns                                    |  |

www.national.com/jpn/ 4

- Note 1: 絶対最大定格とは、デバイスに破壊が発生する可能性のあるリミット値をいいます。動作定格はデバイスが機能する条件を示しますが、特定の性能を保証するものではありません。 仕様および試験条件の保証値に関して「電気的特性」を参照してください。

- Note 2: 人体モデル適用規格、MIL-STD-883、Method 3015.7。 マシン・モデル適用規格、JESD22-A115-A (ESD MM std. of JEDEC)。 電場 (界) 誘導帯電モデル適用規格、JESD22-C101-C (ESD FICDM std. of JEDEC)。

- Note 3: 最大出力電流 (I<sub>OUT</sub>) はデバイスの最大消費電力で決ま)ます。

- Note 4: 最大消費電力は、 $T_{J\,(MAX)}$ 、 $J_A$  の関数として求めることができます。任意の周囲温度での最大許容電力損失は、 $P_D=(T_{J\,(MAX)}-T_A)/J_A$  です。 すべての数値は、プリント基板に直接ハンダ付けしたパッケージを対象とします。

- Note 5: 「電気的特性」の値は、記載温度の工場出荷試験条件にのみ適用されます。電気的特性の表記載のパラメータの性能は、試験条件と異なる条件下では保証されません。

- Note 6: スルーレートは立ち上がり/立ち下がりエッジの平均値です。

- Note 7: 代表 (typ) 値は特性評価時におけるパラメータの標準値 (norm) を表します。 実際の代表値は、経時的に変化するとともに、アプリケーションや構成にも依存します。 この代表値はテストされた値ではなく、出荷済みの製品材料に対する保証値ではありません。

- Note 8:室温リミナー値は、25で製品の全数検査を行っています。工場試験条件で生じる自己発熱は、TJ = TA となる程度にきわめてわずかです。動作温度範囲内のリミナー値は、統計的品質管理 (SQC:Statistical Quality Control) 手法を使用した相関関係に基づいて保証されます。

- Note 9: 負の入力電流にはデバイスから流れ出る電流が含まれます。

- Note 10: ドリフトは、2点の温度間で生じたパラメータの変化量を、2点の温度間の温度差で除算したものです。

- Note 11: このパラメータは、設計や特性評価によって保証されており、製造工程ではテストされません。

#### 製品情報

| Package    | Part Number | Package Marking | Transport Media | NSC Drawing |

|------------|-------------|-----------------|-----------------|-------------|

| 48-Pin QFP | LMH6580VS   | LMH6580VS       | 250 Units/Tray  | VBC48A      |

|            | LMH6581VS   | LMH6581VS       | 250 Units/Tray  | VDC46A      |

www.national.com/jpn/

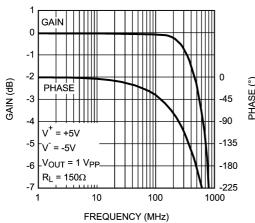

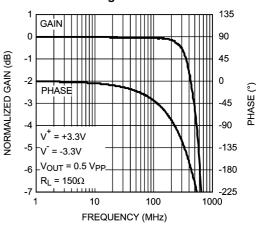

# 代表的な性能特性 LMH6580

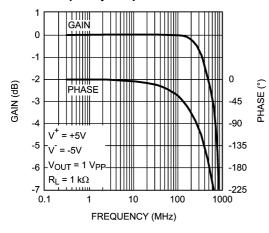

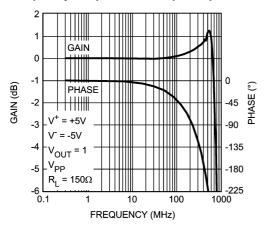

# 1 V<sub>PP</sub> Frequency Response

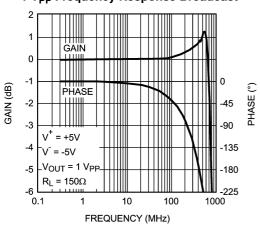

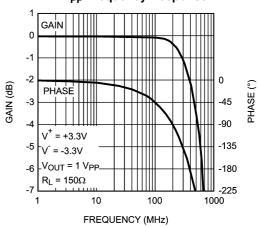

# 1 V<sub>PP</sub> Frequency Response Broadcast

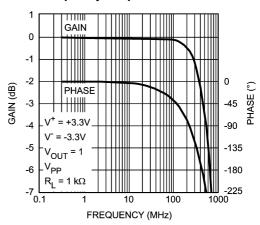

## Frequency Response 1 k Load

# 1 V<sub>PP</sub> Frequency Response

## 1 V<sub>PP</sub> Frequency Response Broadcast

#### Frequency Response 1k Load

## **Frequency Response with Input Expansion**

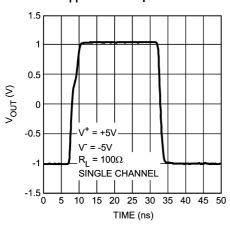

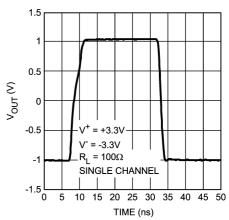

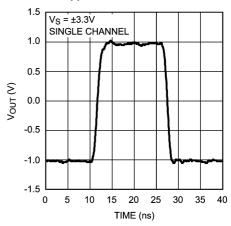

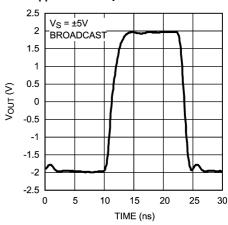

## 2 V<sub>PP</sub> Pulse Response

## 2 V<sub>PP</sub> Pulse Response, Broadcast Mode

# Frequency Response with Input Expansion

2 V<sub>PP</sub> Pulse Response

## 2 V<sub>PP</sub> Pulse Response, Broadcast Mode

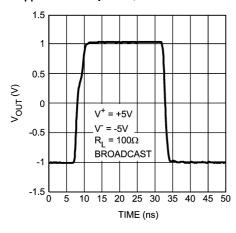

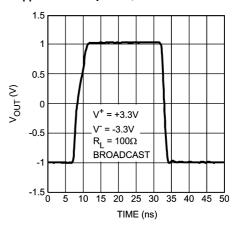

# 1 V<sub>PP</sub> Pulse Response

# SINGLE CHANNEL -0.75 L

5

V = -3.3V

$R_L = 100\Omega$

0.75

0.5

0.25

-0.25

-0.5

V<sub>OUT</sub> (V)

# **Channel to Channel Crosstalk**

# **All Hostile Crosstalk**

10 15 20 25 30 35 40 45 50

TIME (ns)

1 V<sub>PP</sub> Pulse Response

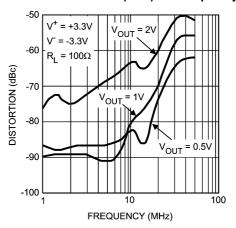

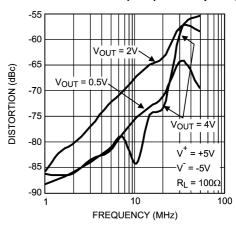

## Second Order Distortion (HD2) vs. Frequency

Third Order Distortion (HD3) vs. Frequency

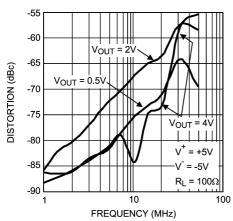

## Second Order Distortion (HD2) vs. Frequency

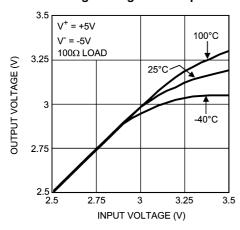

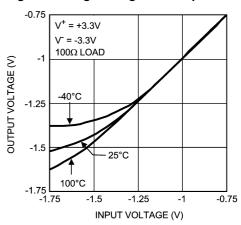

## **Positive Voltage Swing over Temperature**

#### **Positive Voltage Swing over Temperature**

# Third Order Distortion (HD3) vs. Frequency

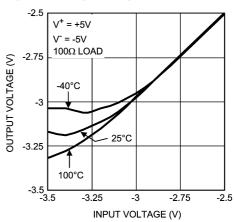

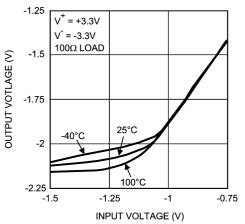

## **Negative Voltage Swing over Temperature**

#### **Negative Voltage Swing over Temperature**

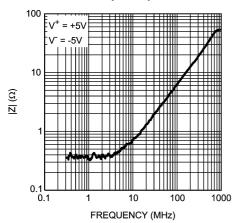

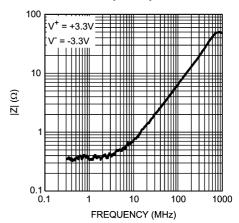

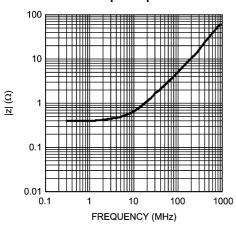

# **Enabled Output Impedance**

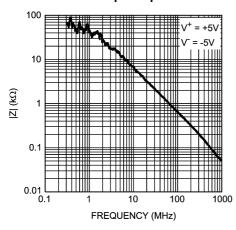

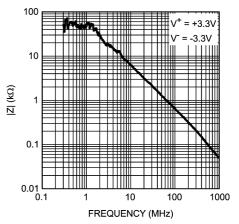

# **Disabled Output Impedance**

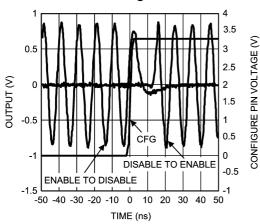

# **Switching Time**

# **Enabled Output Impedance**

# **Disabled Output Impedance**

# 代表的な性能特性 LMH6581

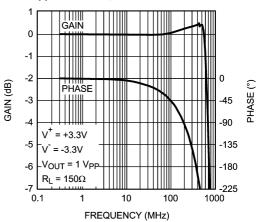

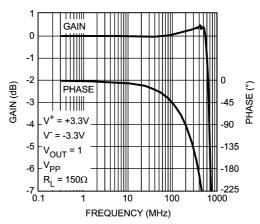

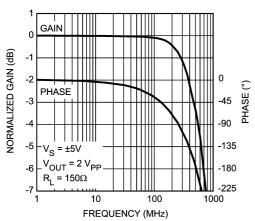

# 2 V<sub>PP</sub> Frequency Response

# **Large Signal Bandwidth**

## **Small Signal Bandwidth**

# 2 V<sub>PP</sub> Frequency Response

# Large Signal Bandwidth

## **Small Signal Bandwidth**

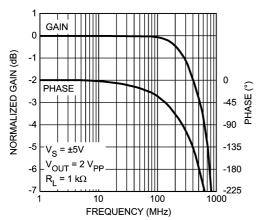

## Frequency Response 1 k Load

## 2 V<sub>PP</sub> Pulse Response

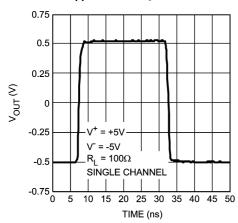

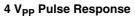

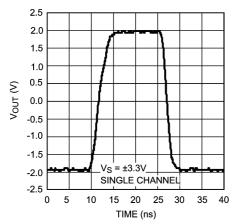

# 4 V<sub>PP</sub> Pulse Response

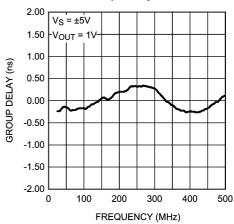

# **Group Delay**

# 2 V<sub>PP</sub> Pulse Response

# 4 V<sub>PP</sub> Pulse Response Broadcast

# Off Isolation

# Second Order Distortion (HD2) vs. Frequency

# 6 V<sub>PP</sub> Pulse Response

# **All Hostile Crosstalk**

# Third Order Distortion (HD3) vs. Frequency

# Second Order Distortion vs. Frequency

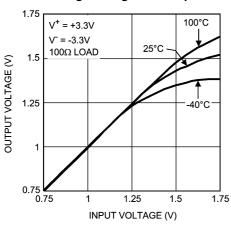

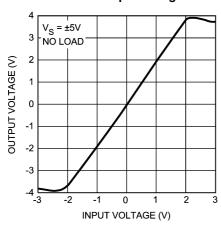

## **No Load Output Swing**

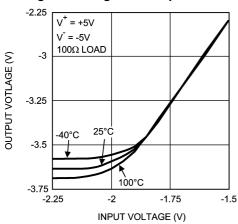

## **Negative Swing Over Temperature**

## Third Order Distortion vs. Frequency

## **Positive Swing over Temperature**

## **No Load Output Swing**

# **Positive Swing over Temperature**

# **Enabled Output Impedance**

# **Negative Swing over Temperature**

# **Disabled Output Impedance**

# アプリケーション情報

#### はじめに

LMH6580/LMH6581 は、入出力を完全にバッファした、ノンブロッキング・アーキテクチャの高速クロスポイント・スイッチです。入力を完全にバッファしているため、負荷を気にすることなく、低インピーダンスから高インピーダンスまであらゆる信号源を接続できます。また、出力も完全にバッファされていることから、75 または50 のバック終端した伝送ラインの駆動には、終端抵抗以外の部品を必要としません。無効化された出力は高インピーダンス状態になります。LMH6580/LMH6581 の入力は、すべて任意の出力(または全出力)に接続可能です。これに対し、1 つの出力には1 つの入力しか接続できません。

#### 入出力の拡張

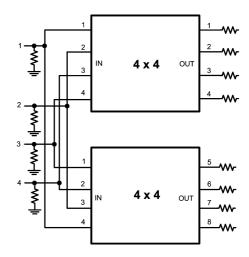

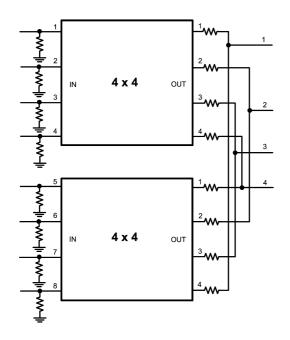

LMH6580/LMH6581 は、入出力とも高インピーダンスの非アクティ ブ状態にすることができるため、クロスポイントの拡張時にすぐれ た柔軟性が得られます。またピンが対角対称に配置されているた め、基板裏面に実装した部品とピンどうしを直接接続できます。 例えば、1 枚の基板上で LMH6580/LMH6581 を 2 チップ組み合 わせ、8 x 8 または 16 x 4 クロスポイントを構成できます。8 x 8 クロスポイントを構成するには、入力ピン8本を互いにすべて結線 します(表面の入力0と裏面の入力7を結線するなど)。一方、 4 本の出力ピンは表面と裏面を接続せず、独立させておきます。 16 x 4 クロスポイントとするには、4 本の出力を結線し、16 本の 入力はすべて独立したままにします。 16 × 4 構成で注意すべき は、結線した2つの出力が同時にアクティブにならないようにする ことです。これに対して8×8構成では結線した2本の入力ピン を同時にアクティブにできます。ここまでに説明したクロスポイント 拡張方法の利点は、信号が1個所のクロスポイントのみを流れる ことです。カスケード接続によって拡張する方法は、並列接続に よる拡張の場合のわずかな負荷の影響に比べて、帯域幅が著し く損なわれます。

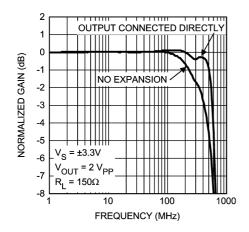

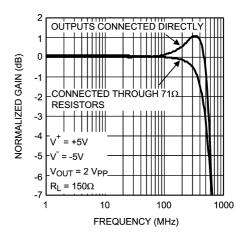

Figure 1 に示すように、出力の拡張はさわめて単純です。2 つのクロスポイント・スイッチの入力を接続しても、性能に対する影響はわずかです。入力の拡張は、さらに検討が必要です。Figure 2 と Figure 3 の入力の拡張方法が示すように、クロスポイント・スイッチの出力の結線には 2 つの方法があります。 Figure 2 では、クロスポイント・スイッチの 2 つの出力は直接結合されて 1 つの終端抵抗を共用します。これは最も簡単な実装構成ですが、1 つだけ欠点があります。一度に 1 出力しかアクティブにできないので、使用されていないクロスポイントのディスエーブルされた出力が持つわずかな容量のために、アクティブ・クロスポイントの周波数応答にピーキングが現れます。これを Figure 4 と Figure 5 に示します。ほとんどの場合、このピーキングは少量なので問題になりません。

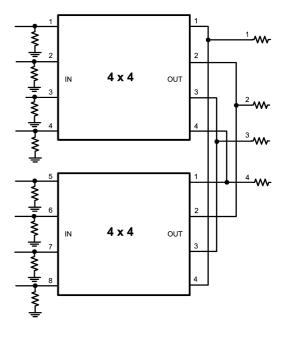

Figure 3 に示すように、各クロスポイント出力に個別の終端抵抗を配置できます。これによって、周波数応答は拡張しない場合とはとんど同じになります。ゲイン 2 のクロスポイントにはゲイン・エラーという欠点が 1 つあります。75 の終端抵抗を使用すると、ディスエーブルされたクロスポイント出力の 1250 の抵抗はゲイン・エラーを引き起こします。これに対処するには、両方のクロスポイントの終端抵抗を、約80 に調整する必要があります。この方法により良好なマッチングが実現できますが、システムのゲインの正確さがクロスポイント抵抗の製造工程のばらつき(約±20%の変動)に依存することになります。

FIGURE 1. Output Expansion

FIGURE 2. Input Expansion with Shared Termination Resistors

# アプリケーション情報(つづき)

FIGURE 3. Input Expansion with Separate Termination Resistors

FIGURE 4. Input Expansion Frequency Response

FIGURE 5. Input Expansion Frequency Response

#### 容量性負荷の駆動

容量性負荷を駆動する用途では、直列出力抵抗  $R_{OUT}$  を使用すると効果的です。 $5\sim120 \mathrm{pF}$  の容量性負荷は、リンギング、周波数応答のピーキング、発振などが発生するため、最も注意を要します。容量性負荷のほとんどは意図しない寄生容量に起因するため、通常、容量性負荷の正確な値はわかりません。まず  $R_{OUT}$  を控えめな値から始めて、帯域幅がわずかなピーキングを示す時点まで値を減らしていくのが最適な方法です。この時点での分離抵抗の値は、最終的にフラットな周波数応答を目指すのか、または最大の帯域幅を目指すのかにより決まります。 $R_{OUT}$  の値が小さければピーキングが発生しますが、最大の帯域幅を得られます。一方、抵抗値が大きくなると、帯域幅が減少し、ピーキングが抑制されます。

初めの値として、5pF の容量性負荷では分離抵抗をおよそ 75 にします。 120pF では約 12 が必要です。 伝送ラインを駆動するときは、出力終端抵抗で通常は十分です。

# アプリケーション情報(つづき)

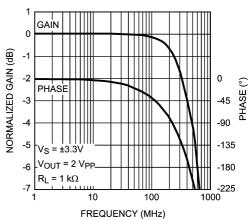

#### 出力バッファを使用した帯域幅の拡大と信頼性の向上

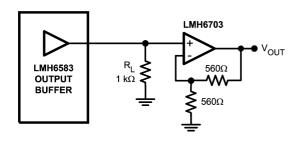

LMH6580/LMH6581 クロスポイント・スイッチは、出力に外部バッファを使用すると帯域幅が拡大され、信頼性が向上します。出力を無負荷にして、外部バッファの高インピーダンスを駆動することにより、帯域幅が拡大されます。出力の負荷を減らしたときの帯域幅の改善については、「代表的な性能」の "Frequency Response 1k Load"のグラフを参照してください。この手法の利点を最大限に活用するには、LMH6703 などの高速アンプを使用する必要があります。 Figure 6 に示すように、抵抗 R<sub>L</sub>をクロスポイント出力とバッファ・アンプの間に配置します。この抵抗はクロスポイント出力がツファに負荷を与え、バッファ入力容量に起因するピーキングを減らします。 R<sub>L</sub> の推奨値は500~1000 です。R<sub>L</sub> の値が大きければ帯域幅は広がりますがピーキングも大きくなります。 R<sub>L</sub> の最適値は、バッファ・アンプの基板レイアウトと入力容量に大きく依存します。

帯域幅の拡大に加えて、外部バッファの使用によりシステムの信頼性が高まります。第1の利点は、クロスポイント・スイッチの熱負荷の減少です。これはダイ(接合部)温度を下げるので、結果としてクロスポイントの寿命が延びます。第2の利点は、ESD信頼性の向上です。起こり得るあらゆるESD事象に対する耐性を持つ高速デバイスを作ることはさわめて困難です。外部バッファを使用すると、外部システム・コネクタでのESD事象からクロスポイント・スイッチを分離できます。

FIGURE 6. Buffered Output

#### クロストーク

ビデオ・ルータなどの大型システムを設計する場合、クロストーク は重大な問題になります。 ナショナル セミコンダクターのラボでの 大規模な試験の結果、クロストークの大部分はクロスポイント・ス イッチの内部で発生するのではなく、基板のレイアウトに関連する ことが判明しています。基板レイアウトに起因するクロストークを減 らす方法は多数あります。制御されたインピーダンス線路を使用 することが、まず重要です。 十分にデカップリングされた電源ブ レーンとグラウンド・プレーンを使用するのも有効です。クロスポイ ント・スイッチ内で発生するクロストークは、多くの場合、電源ピン に信号が結合することに起因します。この種の結合を減らすに は、適切な電源バイパスが効果的です。他の方法としては、入 力信号トレースと出力信号トレースの間にできるだけ多くのグラウ ンドされた銅箔を置くことです。ただし、シールドの銅箔が近すぎ て信号トレースのインピーダンスに影響が出ないように、配置には 注意が必要です。さらに考慮すべき点は、シールド銅箔を信号ト レースに近づけるほど、インピーダンスの過度な低下を防ぐために トレースを縮小する必要があることです。薄い信号トレースを使用 すると、トレース抵抗のために許容できない損失が起こります。こ の損失は、高周波数では表皮効果のためにさらに顕著になりま す。表皮効果により、高周波数になるほどトレースの有効な厚さ が減少するからです。目的の信号が周波数が高くなるにつれて 減衰し、逆にクロストークは高周波数で増加するので、抵抗損失 はクロストークをさらに悪化させてしまいます。

#### デジタル制御

FIGURE 7.

## 論理ピン

| Pin Name    | Level<br>Sensitive | Edge<br>Triggered | Triggered by     |

|-------------|--------------------|-------------------|------------------|

| CLK         | Yes                |                   |                  |

| CS          |                    | Yes               | CLK rising edge  |

| DATA IN     |                    | Yes               | CLK falling edge |

| DATA<br>OUT |                    | Yes               | CLK rising edge  |

| CFG         | Yes                |                   |                  |

| MODE        | Yes                |                   |                  |

| RST         | Yes                |                   |                  |

| BCST        | Yes                |                   |                  |

LMH6580/LMH6581 には、2 つのプログラミング・モード、すなわちシリアル・モードとアドレス指定モードがあります。 LMH6580/LMH6581 には、クロスポイント・スイッチのプログラム状態を保存する内部制御レジスタがあります。 プログラミングの柔軟性を最大限に高めるために 2 段構成のロジックを使用しています。 制御ロジックの第 1 段はクロスポイント・スイッチ・マトリックスに直結しています。このロジックは、デバイスの各出力に対して 1 つのレジスタを持ち、各レジスタにはオン / オフ状態と入力の接続先を示すアドレスが保存されます。 ユーザーはこれらのレジスタに直接アクセスはできません。 ロジックの第 2 段には、第 1 段と同じレジスタがもう 1 つバンク搭載されています。 ただし、このレジスタはシフト・レジスタ構成になっています。 ユーザーはシリアル入力バスを介して、このレジスタにアクセスできます。

プログラミングは、シリアル入力バスと他のデジタル制御ピン4本を用いて行います。シリアル・バスはクロック・ピン (CLK)、シリアル・データ入力ピン (DIN)、シリアル・データ出力ピン (DOUT) から構成されます。シリアル・バスはチップ選択ピン (CS) によりゲートされます。チップ選択ピンはアクティブ Low です。チップ選択ピンが High の間は、シリアル入力ピン上のデータおよびクロック・ピンはすべて無視されます。チップ選択ピンを Low にすると、クロック信号が最初に Low から High に遷移する (0 1) タイミングで、データ受信開始のための内部ロジック設定が行われます。チップ選択ピンは、クロック信号の最初の立ち上がリエッジの少なくとも 5ns 前には Low になっている必要があります。クロック信号が次に High から Low に遷移する (1 0) タイミングで、最初のデータ・ビットが取り込まれます。入力データは、すべてクロック信号の立ち下がリエッジでバスから読み込まれます。有効なデータをすべて取り込み終わったら、チップ選択ピンを High にするか、クロックに

## 論理ピン(つづき)

ク信号を停止する必要があります。これを行わないと、無効データがチップに取り込まれる可能性があります。チップに読み込まれたデータは、CFG ピンが High になるまでクロスポイント・マトリクスには転送されません。この条件は MODE ピンの状態にかかわらず常に有効です。 CFG ピンは、チップ選択ピンの状態には依存しません。チップに新たにデータが取り込まれない限り、CFG ピンにパルスを印加してもデバイス動作には何の影響もありません。

プログラミング時に入力するシリアル・データのフォーマットは MODE ピンによって選択します。MODE ピンが High の場合、変更する出力のアドレスを含む文字列データを入力することにより、1 出力ずつクロスポイントをプログラムできます (アドレス指定モード)。MODE ピンが Low の場合はシリアル・モードになります。このモードでは 16 ビットのアレイ・データを入力し、すべての出力をプログラムできます。いずれのモードで入力した場合も、CFG ピンに High パルスが加わるまで、入力データによってチップ動作が変わることはありません。CFG ピンと MODE ピンはチップ選択ピンに依存しません。

#### 3線式制御と4線式制御

シリアル・データ・ピンの接続方法は2つあります。4つのピンをすべて個別に制御する方法と、CFG ピンと CS ピンを一緒に接続して3線式インタフェースにする方法です。4線式インタフェースでは、チップを CS ピンとは独立して設定できる利点があります。この利点は、複数のクロスポイント・チップをすべてあらかじめプログラムしてから、同時に設定するシステムにおいて有効です。4線式ソリューションは、CLK ピンにフリー・ランニング・クロックを用いるシステムにも適しています。この場合、有効なデータ・ビットをすべて取り込んだ後に CS ピンを High にして、無効なデータがチップに取り込まれるのを防ぐ必要があります。

3 線式では、制御するピンを1つ減らせる反面、CFG ピンの自由 度が減ってしまいます。この自由度の減少を回避するには、クロッ ク信号を FPGA またはマイクロコントローラで生成し、データが取り込まれた後でクロック信号を停止させる方法があります。この場合、クロック信号の有無に基づいてチップ選択機能が働きます。

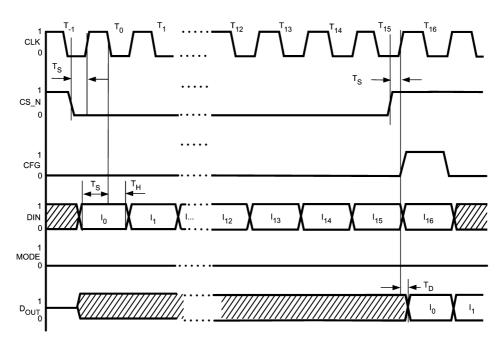

#### シリアル・プログラミング・モード

シリアル・プログラミング・モードは、MODE ピンを Low にすると選択されます。このモードでは 16 ビットのストリームによってクロスポイントの 4 つの出力をすべてプログラムします。データは、下記の「Serial Mode Data Frame」表のようにチップに入力されます(データ・フレーム全体を示すために 2 つの表が必要です)。この表では、クロスポイントのレジスタに最初に取り込まれるビットをビット番号 0としています。プロック図に記載された"Load Register"という名前のレジスタはシフト・レジスタです。チップへの有効なデータのシフト入力が完了したにもかかわらず、チップ選択ピンをLow のままにしてクロック信号を駆動しつづけると、余分なデータがレジスタに取り込まれ、目的のデータがシフトアウトされてしまいます。

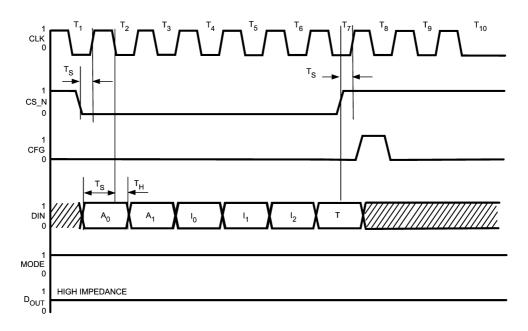

また下記の「Timing Diagram for Serial Mode」のタイミング図では、デジタル・ピンのタイミングの関係を示します。データ・ピンとクロック・ピンのタイミングだけではなく、すべてのピンのタイミング関係が重要であることに注意してください。例えば、チップ選択ピン(CS)はクロック信号の最初の立ち上がリエッジの前に Lowに遷移している必要があります。これによって内部のタイミング回路が同期し、データが次の立ち下がリエッジで入力されます。次に、データ・ビットの入力が完了した後で、別のクロック信号が立ち上がる前にチップ選択ピンは High に遷移して、無効なデータがチップに取り込まれることを防ぐ必要があります。同じ状態を作り出すには、クロック・ピンを Low 状態にして、必要な数のパレスだけ開始および終了してクロック・ピンをストローブする方法もあります。CFG ピンのタイミングはそれほど重要ではありませんが、このピンはすべてのデータがクロスポイント・レジスタにシフトされるまで Lowの状態にしておく必要があります。

**Timing Diagram for Serial Mode**

# シリアル・モードのデータ・フレーム (最初の2ワード)

| 出力 0  | 出力 0 |     |       | 出力 1  |     |   |       |

|-------|------|-----|-------|-------|-----|---|-------|

| 入力アドレ | ス    |     | オン= 0 | 入力アドレ | ス   |   | オン= 0 |

| LSB   |      | MSB | オフ= 1 | LSB   | LSB |   | オフ= 1 |

| 0     | 1    | 2   | 3     | 4     | 5   | 6 | 7     |

Off = TRi-STATE®、ビット0はデバイスに取り込まれる最初のビットです。

# シリアル・モードのデータ・フレーム (つづき)

| 出力 2   |   |     |       | 出力 3   |    |     |       |

|--------|---|-----|-------|--------|----|-----|-------|

| 入力アドレス |   |     | オン= 0 | 入力アドレス |    |     | オン= 0 |

| LSB    |   | MSB | オフ= 1 | LSB    |    | MSB | オフ= 1 |

| 8      | 9 | 10  | 11    | 12     | 13 | 14  | 15    |

#### アドレス指定プログラミング・モード

アドレス指定プログラミング・モードでは、1度に1つの出力レジスタを変更します。このモードを使用するにはMODE ピンを Highにする必要があります。その他のピン機能は、シリアル・プログラミング・モードと同じです。ただし、クロック入力するワードは5ビットで、指定した出力に対するもののみになります。アドレス指定モードのデータ・フォーマットを、下表「アドレス指定モードのワードのフォーマット」に示します。

また下記の「Timing Diagram for Addressed Mode」のタイミング 図では、デジタル・ピンのタイミングの関係を示します。 データ・ピ ンとクロック・ピンのタイミングだけではなく、すべてのピンのタイミン グ関係が重要であることに注意してください。 例えば、チップ選 択じつ(CS)はクロック信号の最初の立ち上がりエッジの前に Low に遷移している必要があります。これによって内部のタイミング回路が同期し、データが次の立ち下がりエッジで入力されます。次に、データ・ビットの入力が完了した後で、別のクロック信号が立ち上がる前にチップ選択ピンは High に遷移して、無効なデータがチップに取り込まれることを防ぐ必要があります。またアドレス指定モードでは、チップ選択ピンが High になった後で、クロック信号が Low から High に遷移する必要があります。チップ選択ピンが High になった後でクロックの Low から High への遷移が起こらなかった場合、後続のデータはチップに正しく入力されません。CFG ピンのタイミングはそれほど重要ではありませんが、このピンは、すべてのデータがクロスポイント・レジスタにシフトされるまで Low の状態にしておく必要があります。

**Timing Diagram for Addressed Mode**

## アドレス指定モードのワードのフォーマット

| 出力アドレ | ス   | 入力アドレス |   |     | TRI-STATE     |

|-------|-----|--------|---|-----|---------------|

| LSB   | MSB | LSB    |   | MSB | 1 = TRI-STATE |

|       |     |        |   |     | 0 =オン         |

| 0     | 1   | 2      | 3 | 4   | 5             |

ビット () はデバイスに取り込まれる最初のビットです。

#### シリアル・モードのデイジー・チェーン・オプション

LMH6580/LMH6581 は、複数チップのデイジー・チェーン接続 によるシリアル・データ・ストリームに対応しています。この機能は シリアル・プログラミング・モードに対してのみ適用可能です。こ の機能を使用するには、最初のチップの  $D_{IN}$  ピンにシリアル・デー タをクロック入力し、2番目のチップの D<sub>IN</sub> とうには最初のチップの DOUT ピンを接続します。 チップ選択信号は両方のチップで共用 するか、あるいは2番目のチップを個別に選択できます。両チッ プのチップ選択ピンを Low にした後、最初のチップに 2 倍長の ワードをクロック入力します。最初のチップに最初のワードをクロッ ク入力する間に、2 番目のチップには元は最初のチップのシフト・ レジスタに保存されていたデータ (無効なデータ)が送られます。 16 ビットのデータがすべて最初のチップに入力されると、次のク ロック・サイクルからは、2 番目のチップに新しい設定データの最 初のフレームが転送されます。32 クロック・サイクル後、両チップ への有効なデータの入力が完了したら、両チップのチップ選択ピ ンを High にして無効なデータによるオーバーシュートが生じないよ うにします。 CFG ピンにパルスを印加すると、新しい設定を両方 のチップで同時にアクティブ化できます。あるいは、チップごとに独 立してアクティブ化することもできます。 両チップのモード(MODE)、 チップ選択 (CS)、設定 (CFG)、クロック (CLK) の各ピンを両チッ プで共有すれば、同じ信号源で駆動することも可能です。

#### 特殊制御ピン

LMH6580/LMH6581 には、シリアル制御バスとは独立して機能する2 つの特殊な制御ピンがあります。そのうちの1 つがリセット・ピン(RST)です。RSTピンはアクティブ High です。すなわちロジック・レベル1を与えると、すべての出力がディスエーブルされ、チップが高インピーダンス状態になります。RSTピンにより、すべてのレジスタが入力アドレス0に設定され、すべての出力がオフになります。この設定では、デバイスに流れる電流がわずか11mAになります。このため、RSTピンを消費電力を低減するためのシャットダウン機能に使用できます。もう1 つの特殊制御ピンはブロードキャスト・ピン(BCST)です。BCSTピンセアクティブ Highです。すべての出力をオン状態にし入力0に接続します。このモードがブロードキャスト・モードと呼ばれる場合があるのは、入力0の値が8つの出力すべてにブロードキャストされるためです。

#### サーマル・マネジメント

LMH6580/LMH6581 は、大量の熱を発生する高性能デバイスで す。 ± 5V の電源を使用し、すべての出力を有効に設定した場 合、LMH6580/LMH6581 は約 0.5W の待機電力を消費します。 待機電力は、50mA (typ) の消費電流と10V の電源電圧を基に して計算されています。この消費電力は、製造工程のばらつき により 0.4W ~ 0.6W の範囲の変動があります。 さらに、出力に 接続された等価ビデオ負荷 (150 ) あたり 30mW の消費電力を 見込む必要があります。 各出力にビデオ負荷が 1 つ接続される 一般的な用途では、この電力の総計は 0.62W になります。 が 44 /W であるため、シリコンは周囲温度よりも27 高温にな ります。さらに過酷な用途で、各出力に2系統のビデオ負荷を接 続した場合、消費電力は 0.74W となり、温度上昇は 33 に達 します。さらに重い負荷を接続する場合、外部ヒート・シンクと強 制空冷を使用すると、TQFP パッケージの熱特性が著しく改善し ます。また、システム筐体内で動作するすべてのデバイスの発熱 による周囲温度の上昇も考慮する必要があります。大出力のデ バイスであることから、サーマル・マネジメントについては回路設 計プロセスのごく初期から検討することを推奨します。 受動的で あっても十分な換気が得られる構造、および垂直方向に基板を実 装することにより、ファン冷却やヒート・シンクが不要になる場合も あります。また、LMH6580/LMH6581 は± 3.3V 電源でも動作可 能です。これによって消費電力は著しく削減される一方、帯域幅 は約10%(2V<sub>PP</sub>出力)削減するだけです。LMH6580/LMH6581 は、電力の削減が要求されるアプリケーション用に、± 3.3V 電 源条件で完全に仕様が定められ工場試験が実施されています。

#### プリント基板のレイアウト

一般的に、適正な高周波レイアウトでは、電源トレースとグラウンド・トレースを入出力ピンから離します。これらのノードの寄生容量(対グラウンド)は、周波数応答にピークをつくったり、回路発振を起こしたりする原因となります(「アプリケーション・ノート OA-15」を参照)。デジタル制御ラインとアナログ信号ライン(特に入力)を交差させなければならない場合は、垂直に交差させるようにします。高周波用レイアウトの基準として、またデバイスの試験や特性測定の補助手段として、次の評価用ボードの利用を推奨します。

デバイス パッケージ 評価用ボード部品番号 LMH6580 48 ピン LMH730164EF

#### 外形寸法図 単位は millimeters

(5.5)

(5.5)

(6.6)

TYP

(9.8)

TYP

(0.5 TYP)

(1.6 TYP)

LAND PATTERN RECOMMENDATION

RO.08 MIN

RO.08-0-20-

0° MIN

R0.08 MIN

R0.08-0.20

GAGE PLANE

0.05-0.15

0.6 ± 0.15

0.6 ± 0.15

DETAIL A

VBC48A (Rev A)

48-Pin QFP NS Package Number VBC48A

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社 は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

## 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

高の方が、生命維持装置またはシステムとは(a)体内に外科的に使用されることを意図されたもの、または(b)生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

-National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2008 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

## ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1 熱霊気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上