LMR24210

JAJSHL5H - OCTOBER 2011 - REVISED JUNE 2019

# LMR24210 42V<sub>IN</sub>、1A 降圧型レギュレータ、DSBGA パッケージ

# 1 特長

入力電圧範囲:4.5V~42V出力電圧範囲:0.8V~24V

出力電流:最大 1A

R<sub>DS(ON)</sub> の小さい同期整流 MOSFET により高効率 を実現

• スイッチング周波数:最高 1MHz

• 低いシャットダウン Io: 25µA (標準値)

プログラム可能なソフト・スタート

• ループ補償が不要

• COT と ERM を組み合わせたアーキテクチャ

ソリューション全体の小型化によりシステムのコストを削減

内蔵の同期整流 MOSFET により低い出力電圧で も高効率を実現

• 低 ESR コンデンサで安定

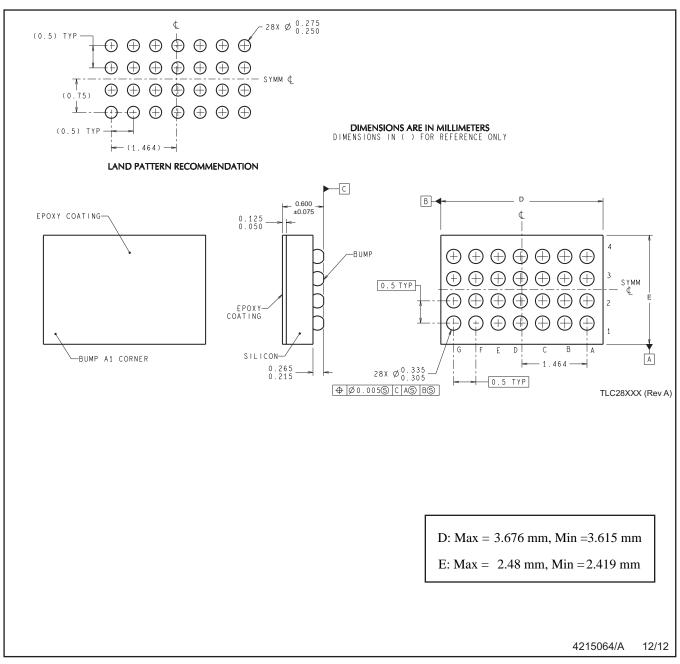

• 28 バンプ DSBGA パッケージ

WEBENCH® Power Designer により、LMR24010 を使用するカスタム設計を作成

### 2 アプリケーション

5V、12V、24V レールからのポイント・オブ・ ロード変換

- スペースに制約のあるアプリケーション

- 産業用分散電源アプリケーション

- 電力計

### 3 概要

LMR24210 同期整流降圧型コンバータは、高効率でコスト効果の高い降圧型レギュレータを実現するために必要なすべての機能を備えています。最小 0.8V の出力電圧で1A の負荷電流を供給でき、デュアル N チャネル同期整流 MOSFET スイッチにより、外付け部品点数を削減できるため、設計を簡素化し、基板スペースを最小限に抑えられます。

LMR24210 は、他の COT 方式のレギュレータと異なり、出力コンデンサの ESR にかかわらず安定性を確保でき、ESR が非常に小さい出力コンデンサ (セラミック・コンデンサなど)を使った場合でも極めて良好に動作するように設計されています。ループ補償が必要ないため、高速な負荷過渡応答が得られ、回路の実装が簡単になります。入力電圧とオン時間は反比例の関係にあるため、入力電圧の変動に対して動作周波数はほぼ一定に維持されます。動作周波数は外付け部品による設定が可能で、最大1MHzです。保護機能には、V<sub>CC</sub> 低電圧誤動作防止、出力過電圧保護、サーマル・シャットダウン、ゲート駆動低電圧誤動作防止が含まれます。LMR24210 は小型のDSBGA 薄型チップスケール・パッケージで供給されます。

#### 製品情報(1)

| 型番       | パッケージ      | 本体サイズ(最大)        |  |  |  |

|----------|------------|------------------|--|--|--|

| LMR24010 | DSBGA (28) | 3.676mm × 2.48mm |  |  |  |

(1) 提供されているすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

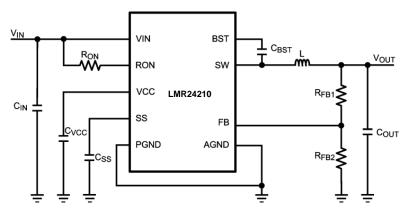

### 代表的なアプリケーション

|   | 目                                 | 次  |                                |    |

|---|-----------------------------------|----|--------------------------------|----|

| 1 | 特長1                               |    | 7.3 Feature Description        | 10 |

| 2 | アプリケーション1                         | 8  | Application and Implementation | 14 |

| 3 | 概要1                               |    | 8.1 Application Information    | 14 |

| 4 | 改訂履歴                              |    | 8.2 Typical Application        | 14 |

| 5 | Pin Configuration and Functions3  | 9  | Layout                         | 18 |

| 6 | Specifications4                   |    | 9.1 Layout Considerations      | 18 |

| • | 6.1 Absolute Maximum Ratings      |    | 9.2 Layout Examples            | 18 |

|   | 6.2 ESD Ratings                   |    | 9.3 Package Considerations     | 19 |

|   | 6.3 Recommended Operating Ratings | 10 | デバイスおよびドキュメントのサポート             |    |

|   | 6.4 Electrical Characteristics    |    | 10.1 デバイス・サポート                 | 20 |

|   | 6.5 Typical Characteristics       |    | 10.2 ドキュメントの更新通知を受け取る方法        | 20 |

| 7 | Detailed Description 9            |    | 10.3 コミュニティ・リソース               | 20 |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

Detailed Description ...... 9

7.2 Functional Block Diagram ...... 9

| Revision G (April 2013) から Revision H に変更                    | Page |

|--------------------------------------------------------------|------|

| • 編集上の変更のみ、WEBENCH のリンクを追加                                   | 1    |

| Revision E (April 2013) から Revision F に変更                    | Page |

| <ul><li>ナショナル セミコンダクターのデータシートのレイアウトを TI フォーマットに 変更</li></ul> | 1    |

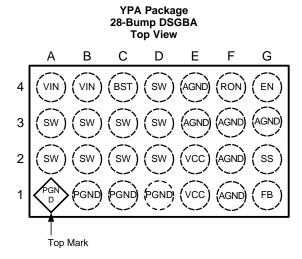

# 5 Pin Configuration and Functions

### **Pin Descriptions**

| DI                                       | PIN  |                                    |                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|------------------------------------------|------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| PI                                       | IN   |                                    | DESCRIPTION                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| NO.                                      | NAME |                                    | 5-00/m /10/m                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| A2, A3, B2,<br>B3, C2, C3,<br>D2, D3, D4 | SW   | Switching node                     | Internally connected to the source of the main MOSFET and the drain of the Synchronous MOSFET. Connect to the inductor.                         |  |  |  |  |  |  |  |  |  |

| A4, B4                                   | VIN  | Input supply voltage               | Supply pin to the device. Nominal input range is 4.5 V to 42 V.                                                                                 |  |  |  |  |  |  |  |  |  |

| C4                                       | BST  | Connection for bootstrap capacitor | Connect a 33-nF capacitor from the SW pin to this pin. An internal diode charges the capacitor during the main MOSFET off-time.                 |  |  |  |  |  |  |  |  |  |

| E3, E4, F1,<br>F2, F3, G3                | AGND | Analog ground                      | Ground for all internal circuitry other than the PGND pin.                                                                                      |  |  |  |  |  |  |  |  |  |

| G2                                       | SS   | Soft start                         | An 8-µA internal current source charges an external capacitor to provide the soft- start function.                                              |  |  |  |  |  |  |  |  |  |

| G1                                       | FB   | Feedback                           | Internally connected to the regulation and over-voltage comparators. The regulation setting is 0.8V at this pin. Connect to feedback resistors. |  |  |  |  |  |  |  |  |  |

| G4                                       | EN   | Enable                             | Connect a voltage higher than 1.26V to enable the regulator. Leaving this input open circuit enables the device at internal UVLO level.         |  |  |  |  |  |  |  |  |  |

| F4                                       | RON  | On-time control                    | An external resistor from the VIN pin to this pin sets the main MOSFET on-time.                                                                 |  |  |  |  |  |  |  |  |  |

| E1, E2                                   | VCC  | Start-up regulator output          | Nominally regulated to 6 V. Connect a capacitor of not less than 680 nF between the VCC and AGND pins for stable operation.                     |  |  |  |  |  |  |  |  |  |

| A1, B1, C1,<br>D1                        | PGND | Power ground                       | Synchronous MOSFET source connection. Tie to a ground plane.                                                                                    |  |  |  |  |  |  |  |  |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

See notes (1)(2)

| -0.3V to 43.5V  |

|-----------------|

| -0.3V to 43.5V  |

| -2V (< 100ns)   |

| -0.3V to 43.5V  |

| -0.3V to 7V     |

| -0.3V to 7V     |

| -65°C to +150°C |

| 150°C           |

|                 |

<sup>(1)</sup> Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For ensured specifications and test conditions, see *Electrical Characteristics*.

# 6.2 ESD Ratings

|                    |                         |                                                        | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000 | ٧    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Ratings

See note(1)

| Supply Voltage Range (VIN)                                         | 4.5V to 42V     |

|--------------------------------------------------------------------|-----------------|

| Junction Temperature Range (T <sub>J</sub> )                       | -40°C to +125°C |

| Thermal Resistance (θ <sub>JA</sub> ) 28-ball DSBGA <sup>(2)</sup> | 50°C/W          |

| For soldering specifications see SNOA549                           |                 |

<sup>(1)</sup> Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For ensured specifications and test conditions, see *Electrical Characteristics*.

<sup>(2)</sup> If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

<sup>(2)</sup>  $\theta_{JA}$  calculations were performed in general accordance with JEDEC standards JESD51-1 to JESD51-11.

# 6.4 Electrical Characteristics

Specifications with standard type are for  $T_J = 25^{\circ}\text{C}$  only; limits in **boldface type** apply over the full operating junction temperature  $(T_J)$  range. Minimum and Maximum limits are ensured through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 18V$ ,  $V_{OUT} = 3.3 \ V.^{(1)}$

| START-UP REGULA                   | ATOR, V <sub>CC</sub>                                  |                                                                       |                                       |       |          |    |

|-----------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------|-------|----------|----|

|                                   |                                                        |                                                                       |                                       |       |          |    |

|                                   | V <sub>CC</sub> output voltage                         | C <sub>CC</sub> = 680nF, no load                                      | 5.0                                   | 6.0   | 7.2      | V  |

| V <sub>IN</sub> - V <sub>CC</sub> | V <sub>IN</sub> - V <sub>CC</sub> dropout voltage      | I <sub>CC</sub> = 20mA                                                |                                       | 350   |          | mV |

| I <sub>VCCL</sub>                 | V <sub>CC</sub> current limit <sup>(2)</sup>           | V <sub>CC</sub> = 0V                                                  | 40                                    | 65    |          | mA |

| V <sub>CC-UVLO</sub>              | V <sub>CC</sub> under-voltage lockout threshold (UVLO) | V <sub>IN</sub> increasing                                            | 3.55                                  | 3.75  | 3.95     | V  |

| V <sub>CC-UVLO-HYS</sub>          | V <sub>CC</sub> UVLO hysteresis                        | V <sub>IN</sub> decreasing – DSBGA package                            |                                       | 150   |          | mV |

| t <sub>VCC-UVLO-D</sub>           | V <sub>CC</sub> UVLO filter delay                      |                                                                       |                                       | 3     |          | μs |

| I <sub>IN</sub>                   | I <sub>IN</sub> operating current                      | No switching, V <sub>FB</sub> = 1V                                    |                                       | 0.7   | 1        | mA |

| I <sub>IN-SD</sub>                | I <sub>IN</sub> operating current, Device shutdown     | $V_{EN} = 0V$                                                         |                                       | 25    | 40       | μΑ |

| SWITCHING CHARA                   | ACTERISTICS                                            |                                                                       | · · · · · · · · · · · · · · · · · · · |       |          |    |

| R <sub>DS-UP-ON</sub>             | Main MOSFET R <sub>DS(on)</sub>                        |                                                                       |                                       | 0.18  | 0.375    | Ω  |

| R <sub>DS-DN-ON</sub>             | Syn. MOSFET R <sub>DS(on)</sub>                        |                                                                       |                                       | 0.11  | 0.225    | Ω  |

| $V_{G-UVLO}$                      | Gate drive voltage UVLO                                | V <sub>BST</sub> - V <sub>SW</sub> increasing                         |                                       | 3.3   | 4        | V  |

| SOFT START                        |                                                        |                                                                       |                                       |       | <u>'</u> |    |

| I <sub>SS</sub>                   | SS pin source current                                  | $V_{SS} = 0.5V$                                                       |                                       | 11    |          | μA |

| CURRENT LIMIT                     |                                                        |                                                                       |                                       |       | <u>'</u> |    |

| I <sub>CL</sub>                   | Syn. MOSFET current limit threshold                    | LMR24210                                                              | 1.2                                   | 1.8   | 2.6      | Α  |

| ON/OFF TIMER                      |                                                        |                                                                       |                                       |       |          |    |

| t <sub>on</sub>                   | ON timer pulse width                                   | $V_{IN} = 10V, R_{ON} = 100 k\Omega$                                  |                                       | 1.38  |          | μs |

|                                   |                                                        | $V_{IN} = 30V, R_{ON} = 100 k\Omega$                                  |                                       | 0.47  |          |    |

| t <sub>on-MIN</sub>               | ON timer minimum pulse width                           |                                                                       |                                       | 150   |          | ns |

| t <sub>off</sub>                  | OFF timer pulse width                                  |                                                                       |                                       | 260   |          | ns |

| ENABLE INPUT                      |                                                        |                                                                       | 1                                     |       |          |    |

| V <sub>EN</sub>                   | EN Pin input threshold                                 | V <sub>EN</sub> rising                                                | 1.13                                  | 1.18  | 1.23     | V  |

| V <sub>EN-HYS</sub>               | Enable threshold hysteresis                            | V <sub>EN</sub> falling                                               |                                       | 90    |          | mV |

|                                   | OVERVOLTAGE COMPARATOR                                 | •                                                                     |                                       |       |          |    |

| V <sub>FB</sub>                   | In-regulation feedback voltage                         | $V_{SS} \ge 0.8V$<br>$T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C$ | 0.784                                 | 0.8   | 0.816    | V  |

| $V_{FB-OV}$                       | Feedback overvoltage threshold                         |                                                                       | 0.888                                 | 0.920 | 0.945    | V  |

| I <sub>FB</sub>                   | FB pin current                                         |                                                                       |                                       | 5     |          | nA |

| THERMAL SHUTDO                    | OWN                                                    |                                                                       |                                       |       |          |    |

| T <sub>SD</sub>                   | Thermal shutdown temperature                           | T <sub>J</sub> rising                                                 |                                       | 165   |          | °C |

| T <sub>SD-HYS</sub>               | Thermal shutdown temperature hysteresis                | T <sub>J</sub> falling                                                |                                       | 20    |          | °C |

<sup>(1)</sup> Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

<sup>(2)</sup> V<sub>CC</sub> provides self bias for the internal gate drive and control circuits. Device thermal limitations limit external loading.

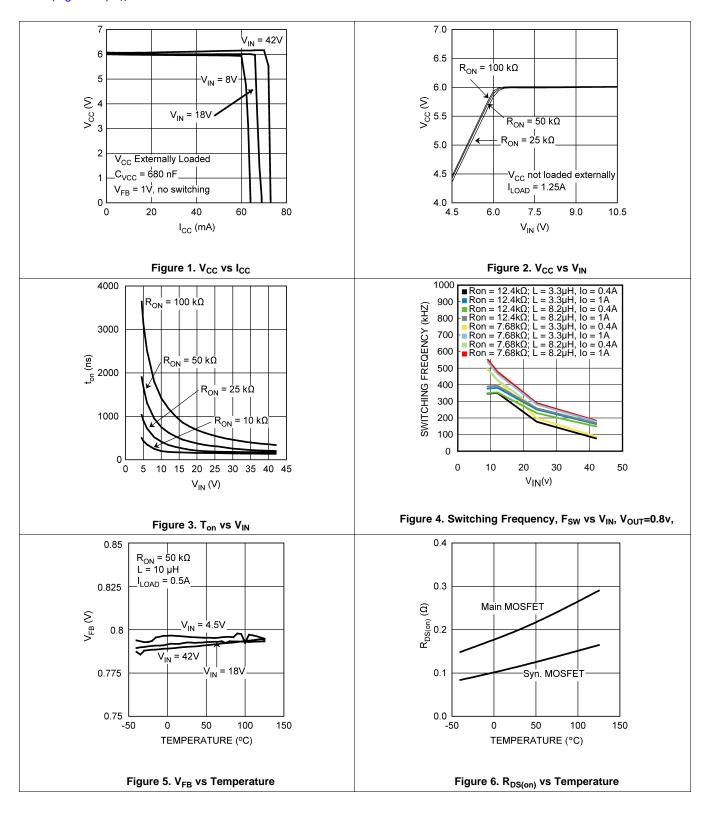

# 6.5 Typical Characteristics

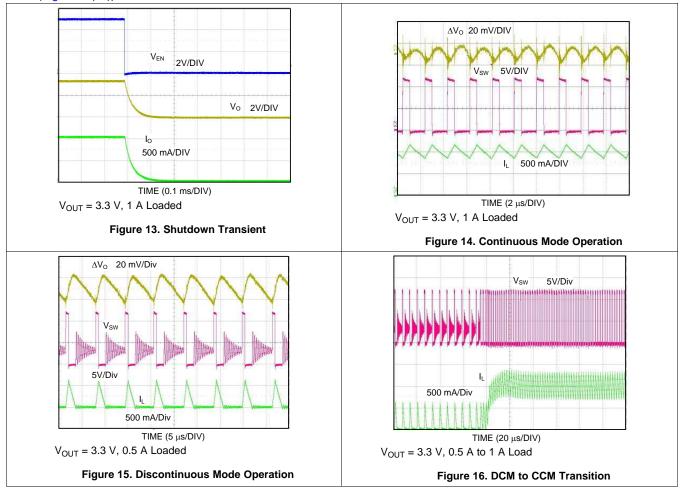

Unless otherwise specified all curves are taken at  $V_{IN} = 18 \text{ V}$  with the configuration in the typical application circuit for  $V_{OUT} = 3.3 \text{ V}$  (Figure 26)  $T_A = 25 ^{\circ}\text{C}$ .

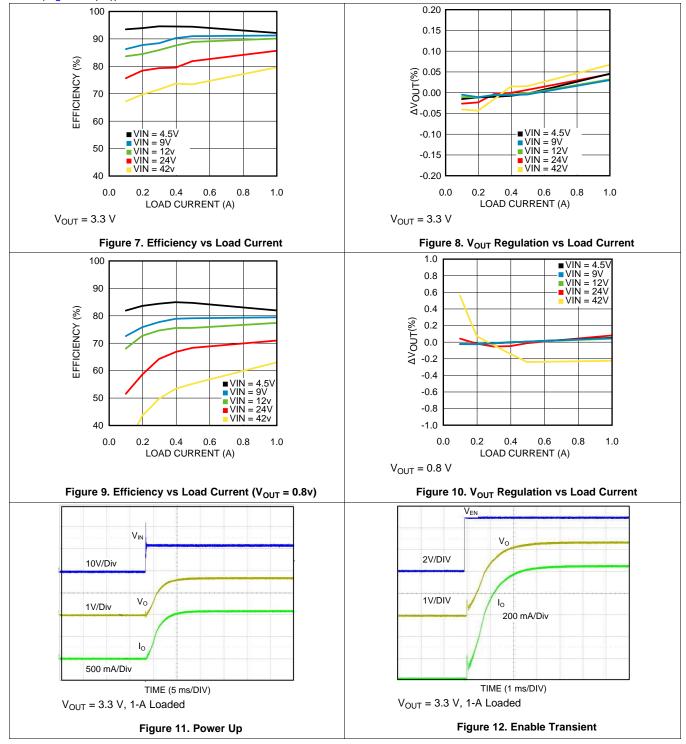

# **Typical Characteristics (continued)**

Unless otherwise specified all curves are taken at  $V_{IN}$  = 18 V with the configuration in the typical application circuit for  $V_{OUT}$  = 3.3 V (Figure 26)  $T_A$  = 25°C.

# **Typical Characteristics (continued)**

Unless otherwise specified all curves are taken at  $V_{IN}$  = 18 V with the configuration in the typical application circuit for  $V_{OUT}$  = 3.3 V (Figure 26)  $T_A$  = 25°C.

# 7 Detailed Description

#### 7.1 Overview

The LMR24210 step-down switching regulator features all required functions to implement a cost effective, efficient buck power converter capable of supplying 1 A to a load. It contains dual N-channel main and synchronous MOSFETs. The constant on-time (COT) regulation scheme requires no loop compensation, results in fast load transient response and simple circuit implementation. The regulator can function properly even with an all ceramic output capacitor network, and does not rely on the output capacitor's ESR for stability. The operating frequency remains constant with line variations due to the inverse relationship between the input voltage and the on-time. The valley current limit detection circuit, with the limit set internally at 1.8 A, inhibits the main MOSFET until the inductor current level subsides.

The LMR24210 can be applied in numerous applications and can operate efficiently for inputs as high as 42 V. Protection features include output overvoltage protection, thermal shutdown,  $V_{CC}$  undervoltage lockout and gatedrive undervoltage lockout. The LMR24210 is available in a small DSBGA chip-scale package.

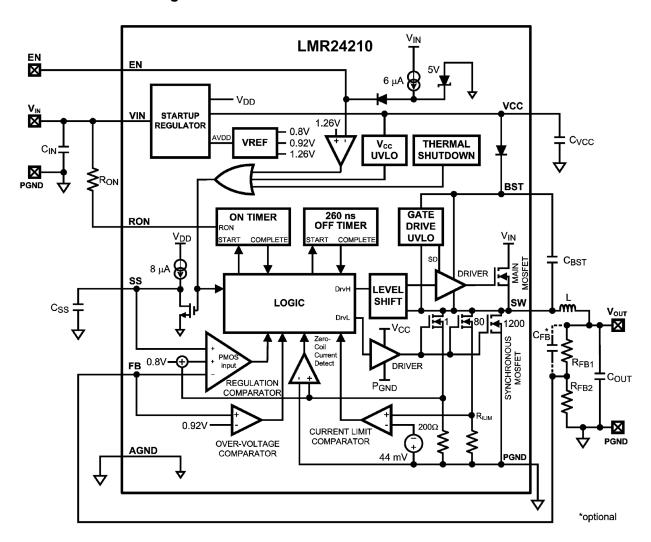

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 COT Control Circuit Overview

COT control is based on a comparator and a one-shot on-timer, with the output voltage feedback (feeding to the FB pin) compared with an internal reference of 0.8 V. If the voltage of the FB pin is below the reference, the main MOSFET is turned on for a fixed on-time determined by a programming resistor  $R_{ON}$  and the input voltage  $V_{IN}$ , upon which the on-time varies inversely. Following the on-time, the main MOSFET remains off for a minimum of 260 ns. Then, if the voltage of the FB pin is below the reference, the main MOSFET is turned on again for another on-time period. The switching will continue to achieve regulation.

The regulator will operate in the discontinuous conduction mode (DCM) at a light load, and the continuous conduction mode (CCM) with a heavy load. In the DCM, the current through the inductor starts at zero and ramps up to a peak during the on-time, and then ramps back to zero before the end of the off-time. It remains zero and the load current is supplied entirely by the output capacitor. The next on-time period starts when the voltage at the FB pin falls below the internal reference. The operating frequency in the DCM is lower and varies larger with the load current as compared with the CCM. Conversion efficiency is maintained since conduction loss and switching loss are reduced with the reduction in the load and the switching frequency respectively. The operating frequency in the DCM can be calculated approximately as follows:

$$f_{SW} = \frac{V_{OUT} (V_{IN} - 1) \times L \times 1.18 \times 10^{20} \times I_{OUT}}{(V_{IN} - V_{OUT}) \times R_{ON}^{2}}$$

(1)

In the CCM, the current flows through the inductor in the entire switching cycle, and never reaches zero during the off-time. The operating frequency remains relatively constant with load and line variations. The CCM operating frequency can be calculated approximately as follows:

$$f_{SW} = \frac{V_{OUT}}{1.3 \times 10^{-10} \times R_{ON}}$$

(2)

Consider and Equation 5 when choosing the switching frequency.

The output voltage is set by two external resistors R<sub>FB1</sub> and R<sub>FB2</sub>. The regulated output voltage is

$$V_{OUT} = 0.8 \text{ V} \times (R_{FB1} + R_{FB2}) / R_{FB2}$$

(3)

# 7.3.2 Start-up Regulator (V<sub>CC</sub>)

A start-up regulator is integrated within the LMR24210. The input pin VIN can be connected directly to a line voltage up to 42 V. The  $V_{CC}$  output regulates at 6 V, and is current limited to 65 mA. Upon power up, the regulator sources current into an external capacitor  $C_{VCC}$ , which is connected to the VCC pin. For stability,  $C_{VCC}$  must be at least 680 nF. When the voltage on the VCC pin is higher than the undervoltage lockout (UVLO) threshold of 3.75 V, the main MOSFET is enabled and the SS pin is released to allow the soft-start capacitor  $C_{SS}$  to charge.

The minimum input voltage is determined by the dropout voltage of the regulator and the  $V_{CC}$  UVLO falling threshold ( $\approx 3.7$  V). If  $V_{IN}$  is less than  $\approx 4$  V, the regulator shuts off and  $V_{CC}$  goes to zero.

### 7.3.3 Regulation Comparator

The feedback voltage at the FB pin is compared to a 0.8-V internal reference. In normal operation (the output voltage is regulated), an on-time period is initiated when the voltage at the FB pin falls below 0.8 V. The main MOSFET stays on for the on-time, causing the output voltage and consequently the voltage of the FB pin to rise above 0.8 V. After the on-time period, the main MOSFET stays off until the voltage of the FB pin falls below 0.8V again. Bias current at the FB pin is nominally 5 nA.

### 7.3.4 Zero Coil Current Detect

The current of the synchronous MOSFET is monitored by a zero coil current detection circuit which inhibits the synchronous MOSFET when its current reaches zero until the next on-time. This circuit enables the DCM operation, which improves the efficiency at a light load.

### Feature Description (continued)

### 7.3.5 Overvoltage Comparator

The voltage at the FB pin is compared to a 0.92-V internal reference. If it rises above 0.92 V, the on-time is immediately terminated. This condition is known as overvoltage protection (OVP). It can occur if the input voltage or the output load changes suddenly. Once the OVP is activated, the main MOSFET remains off until the voltage at the FB pin falls below 0.92 V. The synchronous MOSFET stays on to discharge the inductor until the inductor current reduces to zero, and then switches off.

### 7.3.6 On-Time Timer, Shutdown

The on-time of the LMR24210 main MOSFET is determined by the resistor  $R_{ON}$  and the input voltage  $V_{IN}$ . It is calculated as follows:

$$t_{on} = \frac{1.3 \times 10^{-10} \times R_{ON}}{V_{IN}}$$

(4)

The inverse relationship of  $t_{on}$  and  $V_{IN}$  gives a nearly constant frequency as  $V_{IN}$  is varied.  $R_{ON}$  should be selected such that the on-time at maximum  $V_{IN}$  is greater than 150 ns. The on-timer has a limiter to ensure a minimum of 150 ns for  $t_{on}$ . This limits the maximum operating frequency, which is governed by the following equation:

$$f_{SW(MAX)} = \frac{V_{OUT}}{V_{IN(MAX)} \times 150 \text{ ns}}$$

(5)

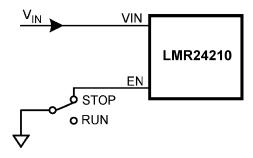

The LMR24210 can be remotely shutdown by pulling the voltage of the EN pin below 1 V. In this shutdown mode, the SS pin is internally grounded, the on-timer is disabled, and bias currents are reduced. Releasing the EN pin allows normal operation to resume because the EN pin is internally pulled up.

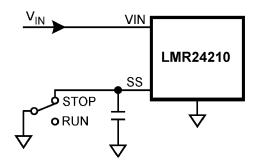

Figure 17. Shutdown Implementation

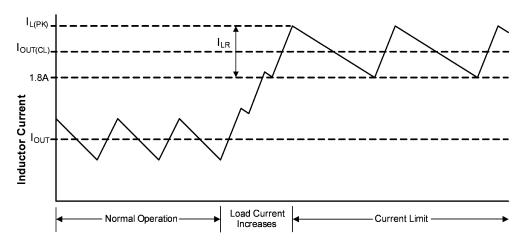

### 7.3.7 Current Limit

Current limit detection is carried out during the off-time by monitoring the re-circulating current through the synchronous MOSFET. Referring to the *Functional Block Diagram*, when the main MOSFET is turned off, the inductor current flows through the load, the PGND pin and the internal synchronous MOSFET. If this current exceeds 1.8 A, the current limit comparator toggles, and as a result disabling the start of the next on-time period. The next switching cycle starts when the re-circulating current falls back below 1.8 A (and the voltage at the FB pin is below 0.8 V). The inductor current is monitored during the on-time of the synchronous MOSFET. As long as the inductor current exceeds 1.8 A, the main MOSFET remains inhibited to achieve current limit. The operating frequency is lower during current limit due to a longer off-time.

Figure 18 illustrates an inductor current waveform. On average, the output current  $I_{OUT}$  is the same as the inductor current  $I_L$ , which is the average of the rippled inductor current. In case of current limit (the current limit portion of Figure 18), the next on-time will not initiate until the current drops below 1.8A (assume the voltage at the FB pin is lower than 0.8 V). During each on-time the current ramps up an amount equal to:

$$I_{LR} = \frac{(V_{IN} - V_{OUT}) \times t_{on}}{L}$$

(6)

During current limit, the LMR24210 operates in a constant current mode with an average output current  $I_{OUT(CL)}$  equal to 1.8 A +  $I_{LR}$  / 2.

### **Feature Description (continued)**

Figure 18. Inductor Current - Current Limit Operation

#### 7.3.8 N-Channel Mosfet and Driver

The LMR24210 integrates an N-channel main MOSFET and an associated floating high voltage main MOSFET gate driver. The gate drive circuit works in conjunction with an external bootstrap capacitor  $C_{BST}$  and an internal high voltage diode.  $C_{BST}$  connecting between the BST and SW pins powers the main MOSFET gate driver during the main MOSFET on-time. During each off-time, the voltage of the SW pin falls to approximately -1 V, and  $C_{BST}$  charges from  $V_{CC}$  through the internal diode. The minimum off-time of 260 ns provides enough time for charging  $C_{BST}$  in each cycle.

### 7.3.9 Soft Start

The soft-start feature allows the converter to gradually reach a steady state operating point, thereby reducing startup stresses and current surges. Upon turnon, after  $V_{CC}$  reaches the undervoltage threshold, an 8- $\mu$ A internal current source charges up an external capacitor  $C_{SS}$  connecting to the SS pin. The ramping voltage at the SS pin (and the non-inverting input of the regulation comparator as well) ramps up the output voltage  $V_{OUT}$  in a controlled manner.

The soft start time duration to reach steady state operation is given by the formula:

$$t_{SS} = V_{REF} \times C_{SS} / 8 \, \mu A = 0.8 \, V \times C_{SS} / 8 \, \mu A$$

(7)

This equation can be rearranged as follows:

$$C_{SS} = t_{SS} \times 8 \,\mu\text{A} / 0.8 \,\text{V}$$

(8)

Use of a 4.7-nF capacitor results in a 0.5-ms soft-start duration. This is a recommended value. Note that high values of  $C_{SS}$  capacitance causes more output voltage drop when a load transient goes across the DCM-CCM boundary. If a fast load transient response is desired for steps between DCM and CCM mode the softstart capacitor value must be less than 18 nF (which corresponds to a soft-start time of 1.8 ms).

An internal switch grounds the SS pin if any of the following three cases happens: (i)  $V_{CC}$  is below the UVLO threshold; (ii) a thermal shutdown occurs; or (iii) the EN pin is grounded. Alternatively, the output voltage can be shut off by connecting the SS pin to ground using an external switch. Releasing the switch allows the SS pin to ramp up and the output voltage to return to normal. The shutdown configuration is shown in Figure 19.

# **Feature Description (continued)**

Figure 19. Alternate Shutdown Implementation

### 7.3.10 Thermal Protection

The junction temperature of the LMR24210 should not exceed the maximum limit. Thermal protection is implemented by an internal Thermal Shutdown circuit, which activates (typically) at 165°C to make the controller enter a low power reset state by disabling the main MOSFET, disabling the on-timer, and grounding the SS pin. Thermal protection helps prevent catastrophic failures from accidental device overheating. When the junction temperature falls back below 145°C (typical hysteresis = 20°C), the SS pin is released, and normal operation resumes.

### 7.3.11 Thermal Derating

Temperature rise increases with frequency, load current, input voltage and smaller board dimensions. On a typical board, the LMR24210 is capable of supplying 1 A below an ambient temperature of 90°C under worst case operation with input voltage of 42 V. Figure 20 shows a thermal derating curve for the output current without thermal shutdown against ambient temperature up to 125°C. Obtaining 1-A output current is possible at higher temperature by increasing the PCB ground plane area, adding airflow or reducing the input voltage or operating frequency.

$\theta_{JA}$ =40°C/W,  $V_{OUT}$  = 3.3 V,  $f_{SW}$  = 500 kHz. (tested on the evaluation board)

Figure 20. Thermal Derating Curve

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The LMR24210 voltage regulator features all required functions to implement a highly efficient and cost-effective buck regulator. It is capable of supplying 1 A to loads with an output voltage as low as 0.8 V. Dual N-channel synchronous MOSFET switches allow a low component count, thus reducing complexity and minimizing board size.

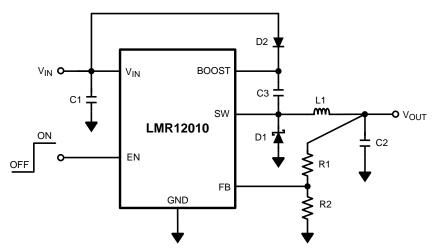

### 8.2 Typical Application

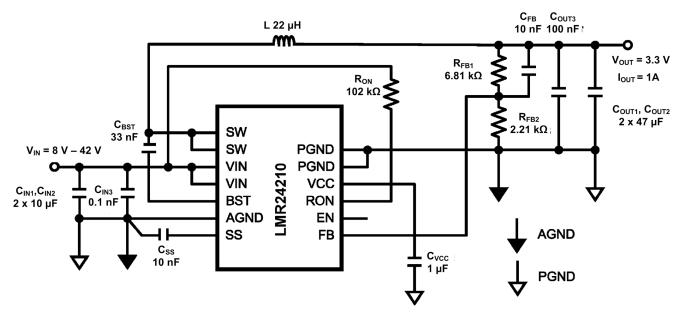

Figure 21. Typical Application Schematic

### 8.2.1 Detailed Design Procedure

### 8.2.1.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LMR24010 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OLIT</sub>), and output current (I<sub>OLIT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

### Typical Application (continued)

### 8.2.1.2 External Components

The following guidelines can be used to select external components.

$R_{FB1}$  and  $R_{FB2}$ : Choose these resistors from standard values in the range of 1 k $\Omega$  to 10 k $\Omega$ , satisfying the following ratio:

$$R_{EB1} / R_{EB2} = (V_{OUT} / 0.8 \text{ V}) - 1$$

(9)

For  $V_{OUT}$  = 0.8 V, the FB pin can be connected to the output directly with a pre-load resistor drawing more than 20  $\mu$ A. This is needed because the converter operation needs a minimum inductor current ripple to maintain good regulation when no load is connected.

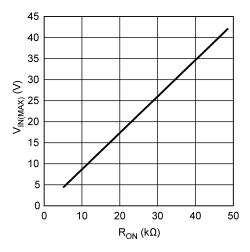

$R_{ON}$ : Equation 2 can be used to select  $R_{ON}$  if a desired operating frequency is selected. But the minimum value of  $R_{ON}$  is determined by the minimum on-time. It can be calculated as follows:

$$R_{ON} \ge \frac{V_{IN(MAX)} \times 150 \text{ ns}}{1.3 \times 10^{-10}}$$

(10)

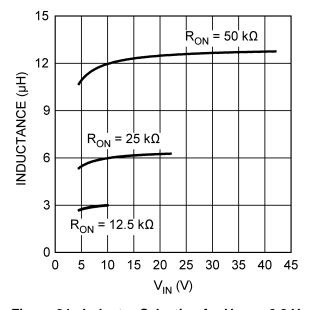

If  $R_{ON}$  calculated from Equation 2 is smaller than the minimum value determined in Equation 10, select a lower frequency to re-calculate  $R_{ON}$  by Equation 2. Alternatively,  $V_{IN(MAX)}$  can also be limited in order to keep the frequency unchanged. The relationship of  $V_{IN(MAX)}$  and  $R_{ON}$  is shown in Figure 22.

On the other hand, the minimum off-time of 260 ns can limit the maximum duty ratio.

Figure 22. Maximum V<sub>IN</sub> For Selected R<sub>ON</sub>

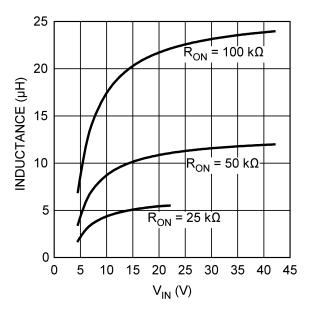

L: The main parameter affected by the inductor is the amplitude of inductor current ripple ( $I_{LR}$ ). Once  $I_{LR}$  is selected, L can be determined by:

$$L = \frac{V_{OUT} x (V_{IN} - V_{OUT})}{I_{LR} x f_{SW} x V_{IN}}$$

where

- V<sub>IN</sub> is the maximum input voltage and

- f<sub>SW</sub> is determined from Equation 2.

If the output current  $I_{OUT}$  is determined, by assuming that  $I_{OUT} = I_L$ , the higher and lower peak of  $I_{LR}$  can be determined. Beware that the higher peak of  $I_{LR}$  should not be larger than the saturation current of the inductor and current limits of the main and synchronous MOSFETs. Also, the lower peak of  $I_{LR}$  must be positive if CCM operation is required.

(11)

# **Typical Application (continued)**

Figure 23. Inductor Selection for  $V_{OUT} = 3.3 \text{ V}$

Figure 24. Inductor Selection for  $V_{OUT} = 0.8 \text{ V}$

Figure 23 and Figure 24 show curves on inductor selection for various  $V_{OUT}$  and  $R_{ON}$ . For small  $R_{ON}$ , according to Equation 10,  $V_{IN}$  is limited. Some curves are therefore limited as shown in the figures.

$C_{VCC}$ : The capacitor on the  $V_{CC}$  output provides not only noise filtering and stability, but also prevents false triggering of the  $V_{CC}$  UVLO at the main MOSFET on/off transitions.  $C_{VCC}$  should be no smaller than 680 nF for stability, and should be a good quality, low ESR, ceramic capacitor.

$C_{OUT}$  and  $C_{OUT3}$ :  $C_{OUT}$  should generally be no smaller than 10  $\mu$ F. Experimentation is usually necessary to determine the minimum value for  $C_{OUT}$ , as the nature of the load may require a larger value. A load which creates significant transients requires a larger  $C_{OUT}$  than a fixed load.

$C_{\text{OUT3}}$  is a small value ceramic capacitor located close to the LMR24210 to further suppress high frequency noise at  $V_{\text{OUT}}$ . TI recommends a 100-nF capacitor.

# **Typical Application (continued)**

$C_{IN}$  and  $C_{IN3}$ : The function of  $C_{IN}$  is to supply most of the main MOSFET current during the on-time, and limit the voltage ripple at the VIN pin, assuming that the voltage source connecting to the VIN pin has finite output impedance. If the voltage source's dynamic impedance is high (effectively a current source),  $C_{IN}$  supplies the average input current, but not the ripple current.

At the maximum load current, when the main MOSFET turns on, the current to the VIN pin suddenly increases from zero to the lower peak of the inductor's ripple current and ramps up to the higher peak value. It then drops to zero at turn-off. The average current during the on-time is the load current. For a worst case calculation,  $C_{IN}$  must be capable of supplying this average load current during the maximum on-time.  $C_{IN}$  is calculated from:

$$C_{IN} = \frac{I_{OUT} \ x \ t_{on}}{\Delta V_{IN}}$$

where

- I<sub>OUT</sub> is the load current

- t<sub>on</sub> is the maximum on-time

- $\Delta V_{IN}$  is the allowable ripple voltage at  $V_{IN}$

(12)

The purpose of the  $C_{IN3}$  is to help avoid transients and ringing due to long lead inductance at the VIN pin. A low ESR 0.1- $\mu$ F ceramic chip capacitor located close to the LMR24210 is recommended.

$C_{BST}$ : A 33-nF high-quality ceramic capacitor with low ESR is recommended for  $C_{BST}$  since it supplies a surge current to charge the main MOSFET gate driver at turnon. Low ESR also helps ensure a complete recharge during each off-time.

**C**<sub>SS</sub>: The capacitor at the SS pin determines the soft-start time; that is, the time for the reference voltage at the regulation comparator and the output voltage to reach their final value. The time is determined from Equation 13:

$$t_{SS} = \frac{C_{SS} \times 0.8V}{8 \,\mu\text{A}} \tag{13}$$

$C_{FB}$ : If the output voltage is higher than 1.6 V,  $C_{FB}$  is needed in the DCM to reduce the output ripple. The recommended value for  $C_{FB}$  is 10 nF.

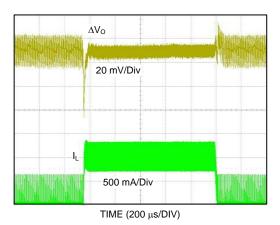

### 8.2.2 Application Curve

$V_{OUT} = 3.3 \text{ V}, 0.2 \text{ A to 1 A Load}$

Figure 25. Load Transient

# 9 Layout

### 9.1 Layout Considerations

The LMR24210 regulation, overvoltage, and current limit comparators are very fast and may respond to short duration noise pulses. Layout is therefore critical for optimum performance. It must be as neat and compact as possible, and all external components must be as close to their associated pins of the LMR24210 as possible. Refer to the Functional Block Diagram, the loop formed by CIN, the main and synchronous MOSFET internal to the LMR24210, and the PGND pin must be as small as possible. The connection from the PGND pin to CIN must be as short and direct as possible. Add vias to connect the ground of CIN to a ground plane, located as close as possible to the capacitor. The bootstrap capacitor  $C_{\mathsf{BST}}$  should be connected as close to the SW and BST pins as possible, and the connecting traces should be thick. The feedback resistors and capacitor R<sub>FB1</sub>, R<sub>FB2</sub>, and C<sub>FB</sub> must be close to the FB pin. A long trace running from V<sub>OUT</sub> to R<sub>FB1</sub> is generally acceptable since this is a low impedance node. Ground R<sub>FB2</sub> directly to the AGND pin. Connect the output capacitor C<sub>OUT</sub> to the load and tied directly to the ground plane. Connect the inductor L close to the SW pin with as short a trace as possible to reduce the potential for EMI (electromagnetic interference) generation. If it is expected that the internal dissipation of the LMR24210 produces excessive junction temperature during normal operation, making good use of the PC board's ground plane can help considerably to dissipate heat. Additionally the use of thick traces. where possible, can help conduct heat away from the LMR24210. Judicious positioning of the PC board within the end product, along with the use of any available air flow (forced or natural convection) can help reduce the junction temperature.

### 9.2 Layout Examples

Figure 26. Typical Application Schematic for  $V_{OUT} = 3.3 \text{ V}$

# **Layout Examples (continued)**

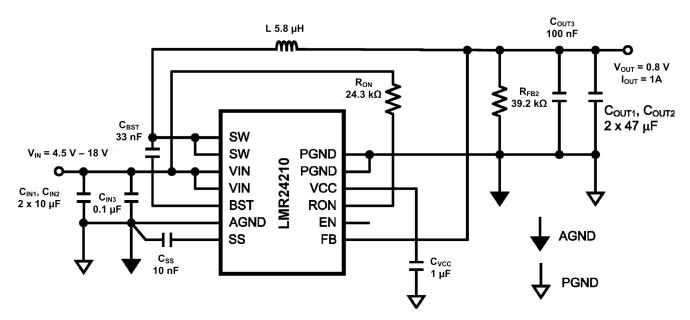

Figure 27. Typical Application Schematic for  $V_{OUT} = 0.8 \text{ V}$

### 9.3 Package Considerations

The die has exposed edges and can be sensitive to ambient light. For applications with direct high intensitive ambient red, infrared, LED or natural light TI recommends shielding the device from the light source to avoid abnormal behavior.

# 10 デバイスおよびドキュメントのサポート

# 10.1 デバイス・サポート

### 10.1.1 開発サポート

### 10.1.1.1 WEBENCH®ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、LMR24010 を使用するカスタム設計を作成できます。

- 1. 最初に、入力電圧(V<sub>IN</sub>)、出力電圧(V<sub>OUT</sub>)、出力電流(I<sub>OUT</sub>)の要件を入力します。

- 2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designerでは、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的なCADフォーマットで出力する。

- 設計のレポートをPDFで印刷し、設計を共有する。

WEBENCHツールの詳細は、www.ti.com/WEBENCHでご覧になれます。

### 10.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 10.4 商標

E2E is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 10.5 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

### 10.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| LMR24210TL/NOPB  | ACTIVE | DSBGA        | YPA                | 28   | 250            | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 125   | SJ5B                    | Samples |

| LMR24210TLX/NOPB | ACTIVE | DSBGA        | YPA                | 28   | 1000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 125   | SJ5B                    | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# PACKAGE MATERIALS INFORMATION

www.ti.com 21-Oct-2021

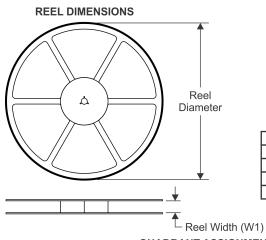

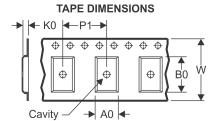

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

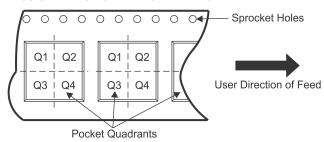

| P1 | Pitch between successive cavity centers                   |

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMR24210TL/NOPB  | DSBGA           | YPA                | 28 | 250  | 178.0                    | 12.4                     | 2.64       | 3.84       | 0.76       | 8.0        | 12.0      | Q1               |

| LMR24210TLX/NOPB | DSBGA           | YPA                | 28 | 1000 | 178.0                    | 12.4                     | 2.64       | 3.84       | 0.76       | 8.0        | 12.0      | Q1               |

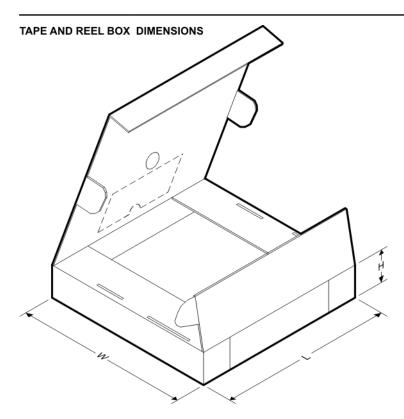

www.ti.com 21-Oct-2021

### \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMR24210TL/NOPB  | DSBGA        | YPA             | 28   | 250  | 208.0       | 191.0      | 35.0        |

| LMR24210TLX/NOPB | DSBGA        | YPA             | 28   | 1000 | 208.0       | 191.0      | 35.0        |

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994. B. This drawing is subject to change without notice.

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated