**SN65HVDA195-Q1** JAJSO47C - JULY 2009 - REVISED JUNE 2022

# SN65HVDA195-Q1 LIN および MOST ECL 物理層インターフェイス

# 1 特長

- LIN 物理層仕様 レビジョン 2.0、および SAEJ2602 LIN 用推奨プラクティスに準拠

- LIN バスの速度は最大 20kbps (LIN 仕様最大および MOST ECL 速度)、最小 0 ボーまで

- ISO9141 (K-LINE) をサポート

- 車載アプリケーション認定済み

- スリープ・モード: 超低消費電流で、LIN バス、ウェーク アップ入力 (外部スイッチ)、ホスト・マイクロコントローラ からのウェークアップ・イベントが可能

- 高速受信に対応

- ±12kV (人体モデル) までの ESD 保護 (LIN ピン)

- LIN ピンは -40V~40V の電圧を入力可能

- 車載環境での過渡的なストレス (ISO 7637) への耐性

- 動作可能電源範囲 7V~27V DC に拡張 (LIN 仕様 7V~18V)

- 5V または 3.3V I/O ピンで MCU と接続

- RXDピンでのウェイクアップ要求

- 外部電圧レギュレータの制御 (INH ピン)

- LIN レスポンダ・アプリケーション向けのプルアップ抵 抗と直列ダイオードを内蔵

- 低い電磁放射 (EME)、高い電磁耐性 (EMI)

- バス端子はバッテリへの短絡、グランドへの短絡に対し て保護

- 熱保護

- システム・レベルでグランド切断に対してフェイルセー

- システム・レベルでのグランド・シフト動作

- 電源オフのノードはネットワークに影響なし

# 2 アプリケーション

- 車載用

- 産業用センシング

- 大型家電製品の分散制御

## 3 概要

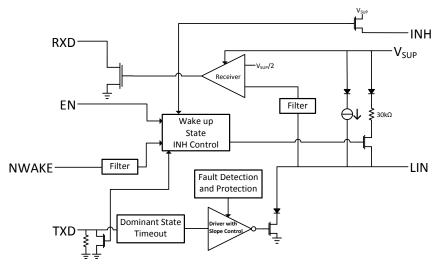

SN65HVDA195 デバイスは、LIN (Local Interconnect Network) 物理層インターフェイスおよび MOST ECL イ ンターフェイスであり、ウェイクアップおよび保護機能付き シリアル・トランシーバを内蔵しています。このバスは、最 大 20kbps のデータ・レートの低速車載ネットワークでー 般的に使用されている単線式双方向バスです。このデバ イスは、ドミナント状態タイムアウトを持たないので、有効デ ータ・レート Okbps で送信できます。 LIN 物理層仕様 レビ ジョン 2.0 で規定されているように、TXD 上のプロトコル出 カデータ・ストリームは、SN65HVDA195 によって、電流 制限波形整形ドライバを通してバス信号に変換されます。 このレシーバは、バスからのデータ・ストリームを変換し、 RXD 経由でデータ・ストリームを出力します。バスには、ド ミナント状態 (グランドに近い電圧) とリセッシブ状態 (バッ テリに近い電圧)という2つの状態があります。リセッシブ 状態では、バスは SN65HVDA195 の内部プルアップ抵 抗と直列ダイオードによって HIGH にプルアップされるた め、レスポンダ用途では外付けプルアップ部品は不要で す。コマンダ用途では、LIN 仕様に従って外付けプルアッ プ抵抗  $(1k\Omega)$  と直列ダイオードが必要です。

#### 制品情報

|                | ₩CHH IH TIX          |                 |

|----------------|----------------------|-----------------|

| 部品番号           | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

| SN65HVDA195-Q1 | SOIC (8)             | 4.90mm × 3.91mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

概略ブロック図

## **Table of Contents**

| 1 特長                                                 | 1              | 9.1 Overview                                    | 10    |

|------------------------------------------------------|----------------|-------------------------------------------------|-------|

| 2アプリケーション                                            |                | 9.2 Functional Block Diagram                    | 10    |

| 3 概要                                                 |                | 9.3 Feature Description                         | 10    |

| 4 Revision History                                   |                | 9.4 Device Functional Modes                     | 12    |

| 5 概要 (続き)                                            |                | 10 Application and Implementation               |       |

| 6 Pin Configuration and Functions                    |                | 10.1 Application Information                    |       |

| 7 Specifications                                     |                | 11 Device and Documentation Support             |       |

| 7.1 Absolute Maximum Ratings                         |                | 11.1 Receiving Notification of Documentation Up |       |

| 7.2 ESD Ratings                                      |                | 11.2 サポート・リソース                                  |       |

| 7.3 Recommended Operating Conditions                 |                | 11.3 Trademarks                                 |       |

| 7.4 Thermal Information                              |                | 11.4 Electrostatic Discharge Caution            |       |

| 7.5 Electrical Characteristics                       | <mark>5</mark> | 11.5 Glossary                                   | 18    |

| 7.6 Typical Characteristics                          | 8              | 12 Mechanical, Packaging, and Orderable         |       |

| 8 Parameter Measurement Information                  |                | Information                                     | 18    |

| 9 Detailed Description                               | 10             |                                                 |       |

| <b>4 Revision History</b><br>資料番号末尾の英字は改訂を表しています。 その | の改訂履歴          | は英語版に準じています。                                    |       |

| Changes from Revision B (March 2015) to              | Revision (     | C (June 2022)                                   | Page  |

| <ul><li>旧式の用語を使っている場合、すべてコマン。</li></ul>              | ダおよびレン         | スポンダに変更                                         | 1     |

| Changes from Revision A (October 2009) t             | to Revisio     | n B (March 2015)                                | Page  |

| <ul><li>「ピン構成および機能」セクション、「ESD 定格</li></ul>           |                | を説明」セクション、「 <i>デバイスの機能モード</i> 」セクション            | ン、「アプ |

|                                                      |                | セクション、「 <i>レイアウト</i> 」セクション、「 <i>デバイスおよ</i> し   |       |

|                                                      |                | てび注文情報」セクションを追加                                 |       |

|                                                      |                |                                                 |       |

| •   <i>                   </i>                       |                |                                                 | 3     |

## 5 概要 (続き)

スリープ・モードでは、SN65HVDA195 は、ウェイクアップ回路がアクティブの状態のままですが、わずかな静止電流を必要とするだけです。これにより、LIN バスを介したリモート・ウェイクアップ、または NWake もしくは EN ピンを介したローカル・ウェイクアップが可能になります。

SN65HVDA195 は、過酷な車載用環境で動作するよう設計されています。このデバイスは、40V からグランドまでの LIN バス電圧のスイングを処理でき、-40V に耐えられます。また、グランド・シフトや電源電圧切断が発生した場合でも、電流が LIN 経由で電源入力へ逆流することを防止します。このデバイスは、低電圧、過熱、グランド喪失保護機能も備えています。フォルト条件が発生した場合、出力は即座にオフになり、フォルト条件が解消するまでオフに維持されます。

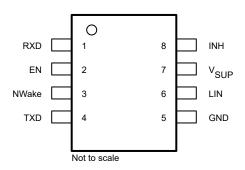

### **6 Pin Configuration and Functions**

図 6-1. D (SOIC) Package 8-Pin (Top View)

表 6-1. Pin Functions

| PIN |                  | TYPE(1) | DESCRIPTION                                                                                 |  |  |  |  |

|-----|------------------|---------|---------------------------------------------------------------------------------------------|--|--|--|--|

| NO. | NAME             | ITPE\"  | DESCRIPTION                                                                                 |  |  |  |  |

| 1   | RXD              | 0       | RXD output (open drain) interface reporting state of LIN bus voltage                        |  |  |  |  |

| 2   | EN               | I       | Enable input                                                                                |  |  |  |  |

| 3   | NWake            | I       | High voltage input for device wake up                                                       |  |  |  |  |

| 4   | TXD              | I       | TXD input interface to control state of LIN output                                          |  |  |  |  |

| 5   | GND              | GND     | Ground                                                                                      |  |  |  |  |

| 6   | LIN              | I/O     | LIN bus single-wire transmitter and receiver                                                |  |  |  |  |

| 7   | V <sub>SUP</sub> | Supply  | Device supply voltage (connected to battery in series with external reverse blocking diode) |  |  |  |  |

| 8   | INH              | 0       | Inhibit controls external voltage regulator with inhibit input                              |  |  |  |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground.

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                          |                                                                            | PARAMETER    | MIN                    | MAX | UNIT |

|--------------------------|----------------------------------------------------------------------------|--------------|------------------------|-----|------|

| V <sub>SUP</sub> (2)     | Supply line supply voltage <sup>(3)</sup>                                  |              | 0                      | 40  | V    |

| V <sub>NWake</sub>       | NWake DC and transient input                                               | -0.3         | 40                     | ]   |      |

| I <sub>NWake</sub>       | N <sub>Wake</sub> current if due to ground must be limited through a seria |              | -3.6                   | mA  |      |

| V <sub>INH</sub>         | INH voltage                                                                | -0.3         | V <sub>SUP</sub> + 0.3 |     |      |

| V <sub>Logic_Input</sub> | Logic pin input voltage                                                    | RXD, TXD, EN | -0.3                   | 5.5 | V    |

| $V_{LIN}$                | LIN DC-input voltage                                                       |              | -40                    | 40  |      |

| T <sub>A</sub>           | Operational free-air temperatu                                             | re           | -40                    | 125 | °C   |

| TJ                       | Junction temperature                                                       |              | -40                    | 150 | °C   |

| T <sub>SD</sub>          | Thermal shutdown                                                           |              | 200                    | °C  |      |

| T <sub>SD_HYS</sub>      | Thermal shutdown hysteresis                                                |              | 25                     | °C  |      |

| T <sub>stg</sub>         | Storage temperature                                                        |              | -40                    | 165 | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to GND.

- (3) The device is specified for operation in the range of V<sub>SUP</sub> from 7 V to 27 V. Operating the device more than 27 V may significantly raise the junction temperature of the device and system level thermal design must be considered.

- (4) The human body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin.

### 7.2 ESD Ratings

|                    |               |                                                         |                               | VALUE  | UNIT |

|--------------------|---------------|---------------------------------------------------------|-------------------------------|--------|------|

|                    |               |                                                         | All pins except LIN and NWake | ±4000  |      |

|                    | Electrostatic | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | Pin LIN                       | ±12000 |      |

| V <sub>(ESD)</sub> | discharge     | Q.100 002                                               | Pin NWake                     | ±11000 | V    |

|                    | -             | Charged-device model (CDM), per AEC Q100-011            | All pins                      | ±1500  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  | MIN | MAX | UNIT |

|------------------|-----|-----|------|

| V <sub>SUP</sub> | 7   | 27  | V    |

| T <sub>AMB</sub> | -40 | 125 | °C   |

### 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | UNIT |

|-----------------------|----------------------------------------------|----------|------|

|                       | I HERMAL ME I RIC***                         | 8 PINS   | UNII |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 112.5    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 66.3     | °C/W |

| R <sub>eJB</sub>      | Junction-to-board thermal resistance         | 52.9     | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 19.3     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 52.4     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 7.5 Electrical Characteristics

$V_{SUP} = 7 \text{ V to } 27 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                            | PARAMETER                                 | TEST CONDITIONS                                                                                                                                                                                | MIN                  | TYP <sup>(1)</sup> | MAX                    | UNIT |

|----------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|------------------------|------|

| SUPPL                      | Y                                         |                                                                                                                                                                                                |                      |                    |                        |      |

|                            | Operational supply voltage <sup>(2)</sup> | Device is operational beyond the LIN 2.0 defined nominal supply line voltage range of 7 V ≤ V <sub>SUP</sub> ≤ 18 V                                                                            | 7                    | 14                 | 27                     |      |

|                            | Naminal aumply line voltage               | Normal and standby modes                                                                                                                                                                       | 7                    | 14                 | 18                     | V    |

|                            | Nominal supply line voltage               | Sleep mode                                                                                                                                                                                     | 7                    | 12                 | 18                     |      |

|                            | V <sub>SUP</sub> undervoltage threshold   |                                                                                                                                                                                                |                      | 4.8                | 6                      |      |

|                            |                                           | Normal mode, EN = High, Bus dominant (total bus load where $R_{LIN} \ge 500~\Omega$ and $C_{LIN} \le 10~nF$ (see $\boxtimes$ 8-1) <sup>(3)</sup> , INH = $V_{SUP}$ , NWake = $V_{SUP}$         |                      | 1.2                | 7.5                    | mA   |

|                            |                                           | Standby mode, EN = low, Bus dominant (total bus load where $R_{LIN} \ge 500~\Omega$ and $C_{LIN} \le 10~nF$ (see $\boxtimes 8-1)^{(3)}$ , INH = $V_{SUP}$ , NWake = $V_{SUP}$                  |                      | 1                  | 2.1                    | ША   |

| loup                       | Supply current                            | Normal mode, EN = High, Bus recessive, LIN = $V_{SUP}$ , INH = $V_{SUP}$ , NWake = $V_{SUP}$                                                                                                   |                      | 450                | 775                    |      |

| I <sub>SUP</sub>           | опрыу санста                              | Standby mode, EN = Low, Bus recessive, LIN = $V_{SUP}$ , INH = $V_{SUP}$ , NWake = $V_{SUP}$                                                                                                   |                      | 450                | 775                    |      |

|                            |                                           | Sleep mode, EN = 0, $T_A = -40$ °C to 95°C,<br>7 V < $V_{SUP} \le 12$ V, LIN = $V_{SUP}$ ,<br>NWake = $V_{SUP}$                                                                                |                      | 13                 | 26                     | μA   |

|                            |                                           | Sleep mode, EN = 0, $T_A = -40$ °C to 95°C,<br>12 V < $V_{SUP}$ < 18 V, LIN = $V_{SUP}$ ,<br>NWake = $V_{SUP}$                                                                                 |                      |                    | 35                     | ,    |

| ΔI <sub>SUP</sub>          | Delta supply current in sleep mode        | Sleep mode, EN = 0, $T_A$ = -40°C to 95°C, Supply line voltage range of 7 V $\leq$ V <sub>SUP</sub> $\leq$ 18 V, LIN bus voltage: V <sub>SUP</sub> - 1.85 V $\leq$ LIN $\leq$ V <sub>SUP</sub> |                      |                    | 20                     |      |

| RXD O                      | UTPUT PIN                                 |                                                                                                                                                                                                |                      |                    | '                      |      |

| Vo                         | Output voltage                            |                                                                                                                                                                                                | -0.3                 |                    | 5.5                    | V    |

| I <sub>OL</sub>            | Low-level output current, open drain      | LIN = 0 V, RXD = 0.4 V                                                                                                                                                                         | 3.5                  |                    |                        | mA   |

| I <sub>IKG</sub>           | Leakage current, high-level               | LIN = V <sub>SUP</sub> , RXD = 5 V                                                                                                                                                             | -5                   | 0                  | 5                      | μA   |

| TXD IN                     | PUT PIN                                   |                                                                                                                                                                                                |                      |                    |                        |      |

| $V_{IL}$                   | Low-level input voltage                   |                                                                                                                                                                                                | -0.3                 |                    | 8.0                    | V    |

| V <sub>IH</sub>            | High-level input voltage                  |                                                                                                                                                                                                | 2                    |                    | 5.5                    | · ·  |

| $V_{IT}$                   | Input threshold hysteresis voltage        |                                                                                                                                                                                                | 30                   |                    | 500                    | mV   |

|                            | Pulldown resistor                         |                                                                                                                                                                                                | 125                  | 350                | 800                    | kΩ   |

| I <sub>IL</sub>            | Low-level input current                   | TXD = Low                                                                                                                                                                                      | -5                   | 0                  | 5                      | μΑ   |

| LIN PIN                    | (REFERENCED TO V <sub>SUP</sub> )         |                                                                                                                                                                                                |                      |                    |                        |      |

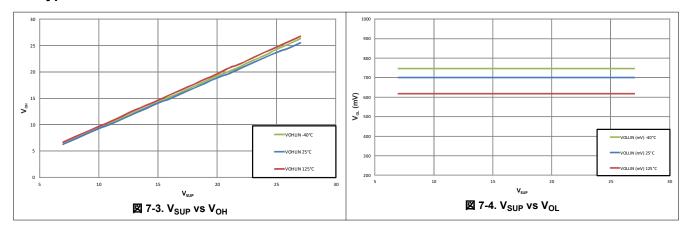

| V <sub>OH</sub>            | High-level output voltage                 | LIN recessive, TXD = High,<br>I <sub>O</sub> = 0 mA, V <sub>SUP</sub> = 14 V                                                                                                                   | V <sub>SUP</sub> – 1 |                    |                        | V    |

| V <sub>OL</sub>            | Low-level output voltage                  | LIN dominant, TXD = Low,<br>I <sub>O</sub> = 40 mA, V <sub>SUP</sub> = 14 V                                                                                                                    | 0                    |                    | 0.2 × V <sub>SUP</sub> | V    |

| R <sub>respon</sub><br>der | Pullup resistor to V <sub>SUP</sub>       | Normal and standby modes                                                                                                                                                                       | 20                   | 30                 | 60                     | kΩ   |

|                            | Pullup current source to V <sub>SUP</sub> | Sleep mode, V <sub>SUP</sub> = 14 V, LIN = GND                                                                                                                                                 | -2                   |                    | -20                    | μA   |

| ı                          | Limiting ourront                          | TXD = 0 V                                                                                                                                                                                      |                      |                    | 220                    | m ^  |

| IL                         | Limiting current                          | TXD = 0 V, T <sub>A</sub> = -10°C to 125°C                                                                                                                                                     |                      |                    | 200                    | mA   |

## 7.5 Electrical Characteristics (continued)

$V_{SUP}$  = 7 V to 27 V,  $T_A$  = -40°C to 125°C (unless otherwise noted)

|                  | PARAMETER                             | TEST CONDITIONS                                                                                                                                                                                                                                                                                 | MIN                     | TYP <sup>(1)</sup>     | MAX                         | UNIT |

|------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|-----------------------------|------|

| I <sub>LKG</sub> | Leakage current                       | LIN = V <sub>SUP</sub>                                                                                                                                                                                                                                                                          | -5                      | 0                      | 5                           |      |

|                  | Leakage current, loss of              | 7 V < LIN ≤ 12 V, V <sub>SUP</sub> = GND                                                                                                                                                                                                                                                        |                         |                        | 5                           | μΑ   |

| I <sub>LKG</sub> | supply                                | 12 V < LIN < 18 V, V <sub>SUP</sub> = GND                                                                                                                                                                                                                                                       |                         |                        | 10                          |      |

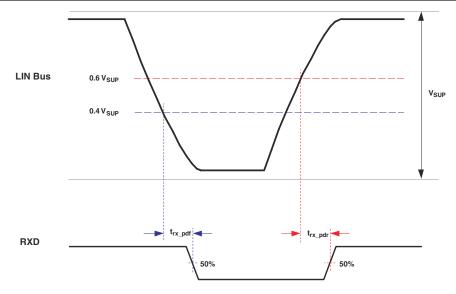

| V <sub>IL</sub>  | Low-level input voltage               | LIN dominant                                                                                                                                                                                                                                                                                    |                         |                        | 0.4 × V <sub>SUP</sub>      |      |

| V <sub>IH</sub>  | High-level input voltage              | LIN recessive                                                                                                                                                                                                                                                                                   | 0.6 × V <sub>SUP</sub>  |                        |                             |      |

| V <sub>IT</sub>  | Input threshold voltage               |                                                                                                                                                                                                                                                                                                 | 0.4 × V <sub>SUP</sub>  | 0.5 × V <sub>SUP</sub> | 0.6 × V <sub>SUP</sub>      |      |

| V <sub>hys</sub> | Hysteresis voltage                    |                                                                                                                                                                                                                                                                                                 | 0.05 × V <sub>SUP</sub> |                        | 0.175 ×<br>V <sub>SUP</sub> | V    |

| V <sub>IL</sub>  | Low-level input voltage for wakeup    |                                                                                                                                                                                                                                                                                                 |                         |                        | 0.4 × V <sub>SUP</sub>      |      |

| EN PI            | N                                     |                                                                                                                                                                                                                                                                                                 |                         |                        |                             |      |

| V <sub>IL</sub>  | Low-level input voltage               |                                                                                                                                                                                                                                                                                                 | -0.3                    |                        | 0.8                         | V    |

| V <sub>IH</sub>  | High-level input voltage              |                                                                                                                                                                                                                                                                                                 | 2                       |                        | 5.5                         | V    |

| V <sub>hys</sub> | Hysteresis voltage                    |                                                                                                                                                                                                                                                                                                 | 30                      |                        | 500                         | mV   |

|                  | Pulldown resistor                     |                                                                                                                                                                                                                                                                                                 | 125                     | 350                    | 800                         | kΩ   |

| I <sub>IL</sub>  | Low-level input current               | EN = Low                                                                                                                                                                                                                                                                                        | -5                      | 0                      | 5                           | μA   |

| INH P            | IN                                    |                                                                                                                                                                                                                                                                                                 |                         |                        |                             |      |

| Vo               | DC output voltage                     |                                                                                                                                                                                                                                                                                                 | -0.3                    |                        | V <sub>SUP</sub> + 0.3      | V    |

| R <sub>on</sub>  | On state resistance                   | Between V <sub>SUP</sub> and INH, INH = 2-mA drive,<br>Normal or standby mode                                                                                                                                                                                                                   |                         | 35                     | 85                          | Ω    |

| I <sub>IKG</sub> | Leakage current                       | Low-power mode, 0 < INH < V <sub>SUP</sub>                                                                                                                                                                                                                                                      | -5                      | 0                      | 5                           | μA   |

| NWA              | (E PIN                                |                                                                                                                                                                                                                                                                                                 | 1                       |                        | '                           |      |

| V <sub>IL</sub>  | Low-level input voltage               |                                                                                                                                                                                                                                                                                                 | -0.3                    |                        | V <sub>SUP</sub> – 3.3      |      |

| V <sub>IH</sub>  | High-level input voltage              |                                                                                                                                                                                                                                                                                                 | V <sub>SUP</sub> – 1    |                        | V <sub>SUP</sub> + 0.3      | V    |

|                  | Pullup current                        | NWake = 0 V                                                                                                                                                                                                                                                                                     | -45                     | -10                    | -2                          |      |

| I <sub>IKG</sub> | Leakage current                       | V <sub>SUP</sub> = NWake                                                                                                                                                                                                                                                                        | -5                      | 0                      | 5                           | μA   |

| THER             | MAL SHUTDOWN                          |                                                                                                                                                                                                                                                                                                 |                         |                        |                             |      |

|                  | Shutdown junction thermal temperature |                                                                                                                                                                                                                                                                                                 |                         | 190                    |                             | °C   |

| AC CI            | HARACTERISTICS                        |                                                                                                                                                                                                                                                                                                 | •                       |                        | '                           |      |

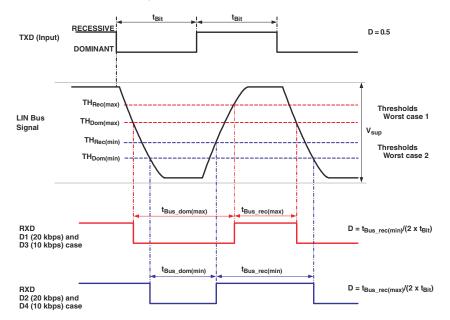

| D1               | Duty cycle 1 <sup>(4)</sup>           | $ \begin{array}{l} TH_{REC(max)} = 0.744 \times V_{SUP}, \ TH_{DOM(max)} = 0.581 \times \\ V_{SUP}, \\ V_{SUP} = 7 \ V \ to \ 18 \ V, \\ t_{BIT} = 50 \ \mu s \ (20 \ kbps), \\ D1 = t_{Bus\_rec(min)} / \ (2 \times t_{BIT}). \\ See \ \ \hline{\ensuremath{\mathbb{Z}}} \ 7-1 \end{array} $   | 0.396                   |                        |                             |      |

| D2               | Duty cycle 2 <sup>(4)</sup>           | $ \begin{array}{l} TH_{REC(min)} = 0.422 \times V_{SUP}, \ TH_{DOM(min)} = 0.284 \times \\ V_{SUP}, \\ V_{SUP} = 7.6 \ V \ to \ 18 \ V, \\ t_{BIT} = 50 \ \mu s \ (20 \ kbps), \\ D2 = t_{Bus\_rec(max)} / \ (2 \times t_{BIT}). \\ See \ \ \hline{\ensuremath{\mathbb{Z}}} \ 7-1 \end{array} $ |                         |                        | 0.581                       |      |

| D3               | Duty cycle 3 <sup>(4)</sup>           | TH <sub>REC(max)</sub> = 0.778 × V <sub>SUP</sub> , TH <sub>DOM(max)</sub> = 0.616 × V <sub>SUP</sub> , V <sub>SUP</sub> = 7 V to 18 V, $t_{BIT}$ = 96 µs (10.4 kbps), D3 = $t_{Bus\_rec(min)}$ / (2 × $t_{BIT}$ ). See $\boxtimes$ 7-1                                                         | 0.417                   |                        |                             |      |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

### 7.5 Electrical Characteristics (continued)

$V_{SUP}$  = 7 V to 27 V,  $T_A$  = -40°C to 125°C (unless otherwise noted)

|                                | PARAMETER                                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                    | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|--------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| D4 Duty cycle 4 <sup>(4)</sup> |                                                                          | $ \begin{array}{c} \text{TH}_{\text{REC(min)}} = 0.389 \times \text{V}_{\text{SUP}},  \text{TH}_{\text{DOM(min)}} = 0.251 \times \\ \text{V}_{\text{SUP}}, \\ \text{V}_{\text{SUP}} = 7.6  \text{V to } 18  \text{V}, \\ \text{t}_{\text{BIT}} = 96  \mu \text{s}  (10.4  \text{kbps}), \\ \text{D4} = t_{\text{Bus\_rec(max)}} /  (2 \times t_{\text{BIT}}). \\ \text{See}  \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |     |                    |     |      |

| t <sub>rx_pdr</sub>            | Receiver rising propagation delay time                                   | $R_{RXD}$ = 2.4 kΩ, $C_{RXD}$ = 20 pF<br>See $\boxtimes$ 7-2<br>See $\boxtimes$ 8-1                                                                                                                                                                                                                                                                                                                                                                |     |                    | 6   |      |

| t <sub>rx_pdf</sub>            | Receiver falling propagation delay time                                  | $R_{RXD}$ = 2.4 k $\Omega$ , $C_{RXD}$ = 20 pF<br>See $\boxtimes$ 7-2<br>See $\boxtimes$ 8-1                                                                                                                                                                                                                                                                                                                                                       |     |                    | 6   |      |

| t <sub>rx_sym</sub>            | Symmetry of receiver propagation delay time                              | rising edge with respect to falling edge ( $t_{rx\_sym}$ = $t_{rx\_pdf} - t_{rx\_pdr}$ ) $R_{RXD} = 2.4 \text{ k}\Omega$ , $C_{RXD}$ = 20 pF See $\boxtimes$ 7-2 See $\boxtimes$ 8-1                                                                                                                                                                                                                                                               | -2  |                    | 2   | μs   |

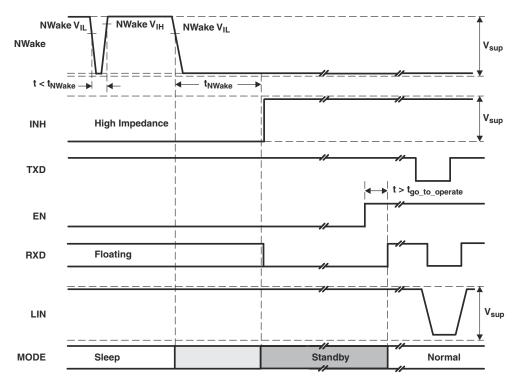

| t <sub>NWake</sub>             | NWake filter time for local wakeup                                       | See ⊠ 9-4                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25  | 50                 | 150 |      |

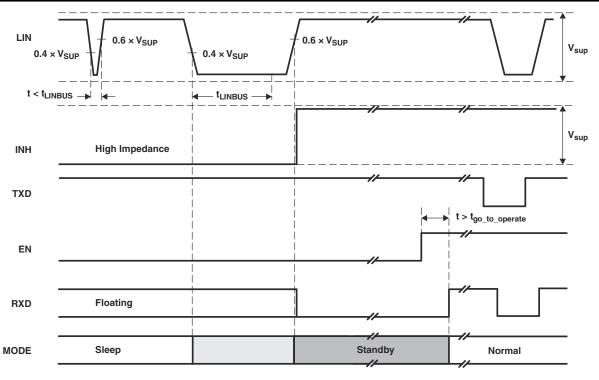

| t <sub>LINBUS</sub>            | LIN wake-up filter time<br>(dominant time for wakeup<br>through LIN bus) | See ⊠ 9-3                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25  | 50                 | 150 |      |

| t <sub>go_to_op</sub>          | perate                                                                   | See ⊠ 9-2 to ⊠ 9-3                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 0.5                | 1   |      |

- (1) Typical values are given for V<sub>SUP</sub> = 14 V at 25°C, except for low power mode where typical values are given for V<sub>SUP</sub> = 12 V at 25°C.

- (2) All voltages are defined with respect to ground; positive currents flow into the SN65HVDA195 device.

- (3) In the dominant state, the supply current increases as the supply voltage increases due to the integrated LIN responder termination resistance. At higher voltages the majority of supply current is through the termination resistance. The minimum resistance of the LIN responder termination is 20 kΩ, so the maximum supply current attributed to the termination is:

I<sub>SUP</sub> (dom) max termination \* (V<sub>SUP</sub> (V<sub>LIN</sub> Dominant + 0.7 V) / 20 kΩ

- (4) Duty cycles: LIN driver bus load conditions (C<sub>LINBUS</sub>, R<sub>LINBUS</sub>): Load1 = 1 nF, 1 kΩ; Load2 = 10 nF, 500 Ω. Duty cycles 3 and 4 are defined for 10.4-kbps operation. The SN65HVDA195 also meets these lower data rate requirements, while it is capable of the higher speed 20-kbps operation as specified by Duty cycles 1 and 2. SAEJ2602 derives propagation delay equations from the LIN 2.0 duty cycle definitions, for details see the SAEJ2602 specification.

図 7-1. Definition of Bus Timing Parameters

図 7-2. Propagation Delay

# 7.6 Typical Characteristics

## **8 Parameter Measurement Information**

図 8-1. Test Circuit for AC Characteristics

### 9 Detailed Description

### 9.1 Overview

The SN65HVDA195-Q1 LIN transceiver is a LIN (Local Interconnect Network) physical layer transceiver which integrates a serial transceiver with wake up and protection features. The LIN bus is a single wire, bi-directional bus that typically is used in low speed in vehicle networks with data rates that range from 2.4 kbps to 20 kbps

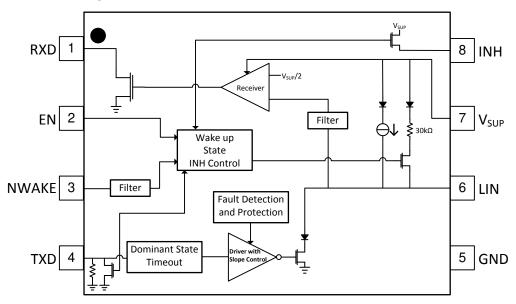

### 9.2 Functional Block Diagram

#### 9.3 Feature Description

#### 9.3.1 Local Interconnect Network (LIN) Bus

This I/O pin is the single-wire LIN bus transmitter and receiver.

### 9.3.1.1 Transmitter Characteristics

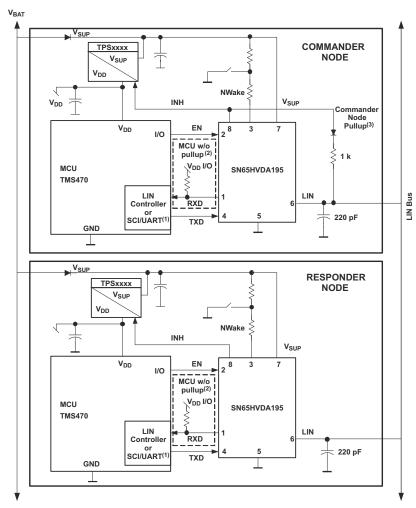

The driver is a low-side transistor with internal current limitation and thermal shutdown. There is an internal  $30-k\Omega$  pullup resistor with a serial diode structure to  $V_{SUP}$ , so no external pullup components are required for LIN responder mode applications. An external pullup resistor of 1  $k\Omega$ , plus a series diode to  $V_{SUP}$  must be added when the device is used for commander node applications.

Voltage on LIN can go from -40-V to 40-V DC without any currents other than through the pullup resistance. There are no reverse currents from the LIN bus to supply  $(V_{SUP})$ , even in the event of a ground shift or loss of supply  $(V_{SUP})$ .

The LIN thresholds and AC parameters are LIN Protocol Specification Revision 2.0 compliant.

During a thermal shut down condition, the driver is disabled.

#### 9.3.1.2 Receiver Characteristics

The receiver's characteristic thresholds are ratio-metric with the device supply pin. Typical thresholds are 50%, with a hysteresis from 5% to 17.5% of supply.

The receiver is capable of receiving higher data rates (>100 kbps) than supported by LIN or SAEJ2602 specifications. This allows the SN65HVDA195 to be used for high-speed downloads at end-of-line production or other applications. The actual data rates achievable depend on system time constants (bus capacitance and pullup resistance) and driver characteristics used in the system.

### 9.3.2 Transmit Input (TXD)

TXD is the interface to the MCU's LIN protocol controller or SCI/UART used to control the state of the LIN output. When TXD is low, the LIN output is dominant (near ground). When TXD is high, the LIN output is recessive (near battery). The TXD input structure is compatible with microcontrollers with 3.3-V and 5-V I/O. TXD has an internal pulldown resistor. This device does not have a TXD dominant time-out protection circuit so that low data rates may be used.

### 9.3.3 Receive Output (RXD)

RXD is the interface to the MCU's LIN protocol controller or SCI/UART, which reports the state of the LIN bus voltage. LIN recessive (near battery) is represented by a high level on RXD and LIN dominant (near ground) is represented by a low level on RXD. The RXD output structure is an open-drain output stage. This allows the SN65HVDA195 to be used with 3.3-V and 5-V I/O microcontrollers. If the microcontroller's RXD pin does not have an integrated pullup, an external pullup resistor to the microcontroller I/O supply voltage is required.

#### 9.3.3.1 RXD Wake-Up Request

When the SN65HVDA195 has been in low-power mode and encounters a wake-up event from the LIN bus or NWake pin, RXD goes low, while the device enters and remains in standby mode (until EN is reasserted high and the device enters normal mode).

### 9.3.4 Supply Voltage (V<sub>SUP</sub>)

$V_{SUP}$  is the SN65HVDA195 device power supply pin.  $V_{SUP}$  is connected to the battery through an external reverse battery blocking diode. The characterized operating voltage range for the SN65HVDA195 is from 7 V to 27 V.  $V_{SUP}$  is protected for harsh automotive conditions up to 40 V.

The device contains a reset circuit to avoid false bus messages during undervoltage conditions when  $V_{SUP}$  is less than  $V_{SUP}$  UNDER.

### 9.3.5 Ground (GND)

GND is the SN65HVDA195 device ground connection. The SN65HVDA195 can operate with a ground shift as long as the ground shift does not reduce  $V_{SUP}$  below the minimum operating voltage. If there is a loss of ground at the ECU level, the SN65HVDA195 does not have a significant current consumption on LIN bus.

#### 9.3.6 Enable Input (EN)

EN controls the operation mode of the SN65HVDA195 (normal or sleep mode). When EN is high, the SN65HVDA195 is in normal mode allowing a transmission path from TXD to LIN and from LIN to RXD. When EN is low, the device is put into sleep mode and there are no transmission paths available. The device can enter normal mode only after being woken up. EN has an internal pulldown resistor to make sure the device remains in low-power mode even if EN floats.

#### 9.3.7 NWake Input (NWake)

NWake is a high-voltage input used to wake up the SN65HVDA195 from low-power mode. NWake is usually connected to an external switch in the application. A low on NWake that is asserted longer than the filter time  $(t_{NWAKE})$  results in a local wakeup. NWake provides an internal pullup source to  $V_{SUP}$ .

### 9.3.8 Inhibit Output (INH)

INH is used to control an external voltage regulator that has an inhibit input. When the SN65HVDA195 is in normal operating mode, the inhibit high-side switch is enabled and the external voltage regulator is activated. When SN65HVDA195 is in low-power mode, the inhibit switch is turned off, which disables the voltage regulator. A wake-up event on for the SN65HVDA195 returns INH to  $V_{SUP}$  level. INH can also drive an external transistor connected to an MCU interrupt input.

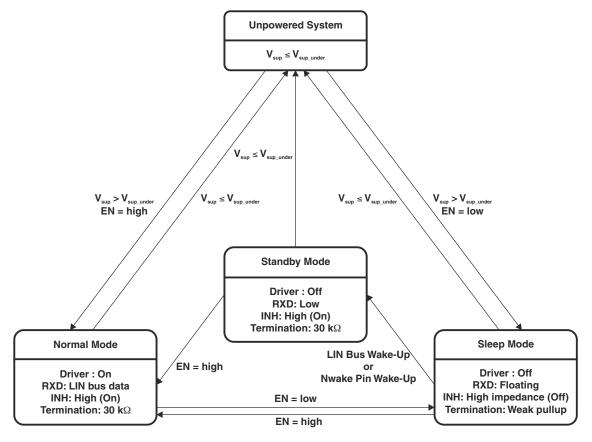

#### 9.4 Device Functional Modes

#### 9.4.1 Operating Modes

図 9-1. Operating States Diagram

表 9-1. Operating Modes

| MODE    | EN   | RXD          | LIN BUS<br>TERMINATION | INH            | TRANSMITTER | COMMENTS                                         |

|---------|------|--------------|------------------------|----------------|-------------|--------------------------------------------------|

| Sleep   | Low  | Floating     | Weak current pullup    | High impedance | Off         |                                                  |

| Standby | Low  | Low          | 30 kΩ (typ)            | High           | Off         | Wake-up event detected, waiting on MCU to set EN |

| Normal  | High | LIN bus data | 30 kΩ (typ)            | High           | On          | LIN transmission up to 20 kbps                   |

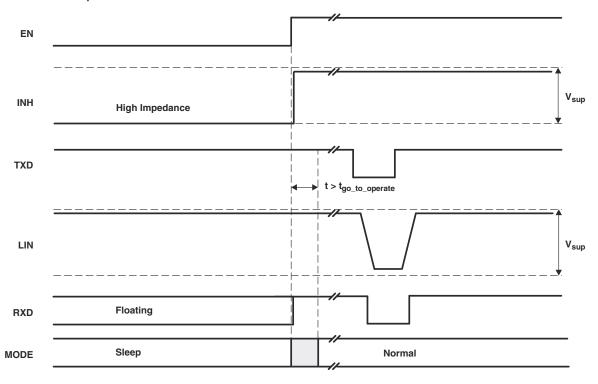

#### 9.4.2 Normal Mode

This is the normal operational mode, in which the receiver and driver are active, and LIN transmission up to the LIN specified maximum of 20 kbps is supported. The receiver detects the data stream on the LIN bus and outputs it on RXD for the LIN controller, where recessive on the LIN bus is a digital high, and dominate on the LIN bus is digital low. The driver transmits input data on TXD to the LIN bus. Normal mode is entered as EN transitions high while the SN65HVDA195 is in sleep or standby mode.

#### 9.4.3 Sleep Mode

Sleep mode is the power saving mode for the SN65HVDA195 and the default state after power up (assuming EN is low during power up). Even with the extremely low current consumption in this mode, the SN65HVDA195 can still wake up from LIN bus through a wake-up signal, a low on NWake, or if EN is set high. The LIN bus and NWake are filtered to prevent false wake-up events. The wake-up events must be active for their respective time periods ( $t_{\text{LINBUS}}$ ,  $t_{\text{NWake}}$ ).

The sleep mode is entered by setting EN low.

While the device is in sleep mode, the following conditions exist:

- The LIN bus driver is disabled and the internal LIN bus termination is switched off (to minimize power loss if LIN is short-circuited to ground). However, the weak current pullup is active to prevent false wake-up events in case an external connection to the LIN bus is lost.

- · The normal receiver is disabled.

- · INH is high impedance.

- · EN input, NWake input, and the LIN wake-up receiver are active.

#### 9.4.4 Wake-Up Events

There are three ways to wake up the SN65HVDA195 from sleep mode:

- Remote wakeup through recessive (high) to dominant (low) state transition on LIN bus. The dominant state

must be held for t<sub>LINBUS</sub> filter time and then the bus must return to the recessive state (to eliminate false

wake-ups from disturbances on the LIN bus or if the bus is shorted to ground).

- Local wakeup through a low on NWake, which is asserted low longer than the filter time t<sub>NWake</sub> (to eliminate false wake-ups from disturbances on NWake)

- · Local wakeup through EN being set high

### 9.4.5 Standby Mode

This mode is entered whenever a wake-up event occurs through LIN bus or NWake while the SN65HVDA195 is in sleep mode. The LIN bus responder termination circuit and INH are turned on when standby mode is entered. The application system powers up once INH is turned on, assuming the system is using a voltage regulator connected through INH. Standby mode is signaled through a low level on RXD.

When EN is set high while the SN65HVDA195 is in standby mode the device returns to normal mode and the normal transmission paths from TXD to LIN bus and LIN bus to RXD are enabled.

図 9-2. Wakeup Through EN

図 9-3. Wakeup Through LIN

図 9-4. Wakeup Through NWake

### 10 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 10.1 Application Information

The SN65HVDA195-Q1 can be used as both a responder device and a commander device in a LIN network. It comes with the ability to support both remote wake-up requests and local wake-up requests.

#### 10.1.1 Typical Application

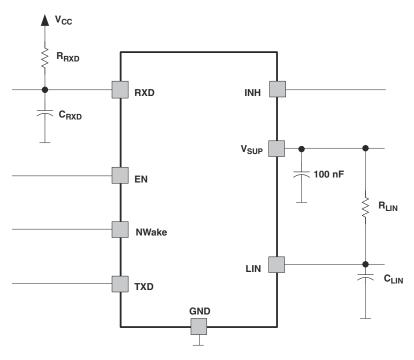

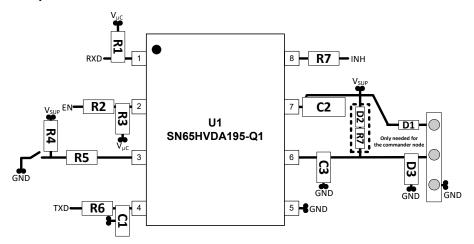

The device comes with an integrated 30-k $\Omega$  pullup resistor and series diode for responder applications, and for commander applications an external 1-k $\Omega$  pullup with series blocking diode can be used.  $\boxtimes$  10-1 shows the device being used in both types of applications.

- A. RXD on MCU or LIN responder has internal pullup, no external pullup resistor is needed.

- B. RXD on MCU or LIN responder without internal pullup, requires external pullup resistor.

- c. Commander node applications require an external  $1-k\Omega$  pullup resistor and serial diode.

図 10-1. SN65HVDA195-Q1 Application Diagram

#### 10.1.1.1 Design Requirements

For this design, use these requirements:

- RXD on MCU or LIN responder has internal pullup, no external pullup resistor is needed.

- RXD on MCU or LIN responder without internal pullup, requires external pullup resistor.

- Commander node applications require an external 1-k $\Omega$  pullup resistor and serial diode

#### 10.1.1.2 Detailed Design Procedure

The RXD output structure is an open-drain output stage. This allows the SN65HVDA195-Q1 to be used with 3.3-V and 5-V I/O microcontrollers. If the RXD pin of the microcontroller does not have an integrated pullup, an external pullup resistor to the microcontroller I/O supply voltage is required.

The  $V_{SUP}$  pin of the device should be decoupled with a 100-nF capacitor as close to the supply pin of the device as possible.

The NWAKE pin is a high voltage wake-up input to the device. If this pin is not being used it should be tied to  $V_{SUP}$ .

### 10.1.1.3 Application Curves

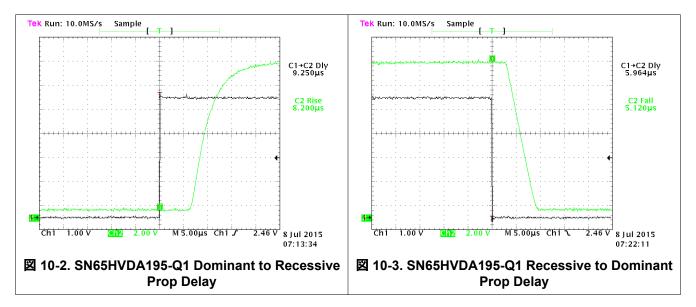

☑ 10-2 and ☑ 10-3 show the propagation delay from the TXD pin to the LIN pin for both the recessive to dominant and dominant to recessive states under lightly loaded conditions.

#### **Power Supply Recommendations**

The SN65HVDSA195-Q1 was designed to operate directly off a car battery, or any other DC supply ranging from 7 V to 27 V. A100-nF decoupling capacitor should be placed as close to the V<sub>SUP</sub> pin of the device as possible.

### 10.1.2 Layout

#### 10.1.2.1 Layout Guidelines

Pin 1 is the RXD output of the SN65HVDA195-Q1. It is an open-drain output and requires an external pullup resistor in the range of 1-k $\Omega$  to 10 k $\Omega$  to function properly. If the micro-processor paired with the transceiver does not have an integrated pullup and external resistor should be placed between RXD and the regulated voltage supply for the micro-processor.

Pin 2 is the EN input pin for the device that is used to place the device in low power sleep mode. If this feature is not used on the device, the pin should be pulled high to the regulated voltage supply of the microprocessor through a series  $1-k\Omega$  to  $10-k\Omega$  series resistor. Additionally, a series resistor may be placed on the pin to limit the current on the digital lines in the case of an overvoltage fault.

Pin 3 is a high-voltage local wake up input pin. The device is typically externally controlled by a normally open switch tied between NWAKE and ground. When the momentary switch is pressed the NWAKE pin is pulled to ground signaling a local wake-up event. A series resistor between  $V_{BATT}$  and the switch, and NWAKE and the switch should be placed to limit current. If the NWAKE local wake-up feature is not used, the pin can be tied to  $V_{SUP}$  through a 1-k $\Omega$  to 10-k $\Omega$  pullup resistor.

Pin 4 is the transmit input signal to the device. A series resistor can be placed to limit the input current to the device in the case of an overvoltage on this pin. Also a capacitor to ground can be placed close to the input pin of the device to filter noise.

Pin 5 is the ground connection of the device. This pin should be tied to a ground plane through a short trace with the use of two vias to limit total return inductance.

Pin 6 is the LIN bus connection of the device. For responder applications a 220-pF bus capacitor is implemented. For commander applications an additional series resistor and blocking diode should be placed between the LIN pin and the  $V_{SUP}$  pin.

Pin 7 is the supply pin for the device. A 100-nF decoupling capacitor should be placed as close to the device as possible.

Pin 8 is a high-voltage output pin that may be used to control the local power supplies. If this feature is not used the pin may be left floating.

注

All ground and power connections should be made as short as possible and use at least two vias to minimize the total loop inductance.

#### 10.1.2.2 Layout Example

図 10-4. Layout Example

### 11 Device and Documentation Support

## 11.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 11.2 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 11.3 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 11.5 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

www.ti.com 17-Feb-2022

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| SN65HVDA195QDRQ1 | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | A195Q                   | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

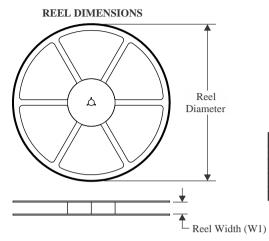

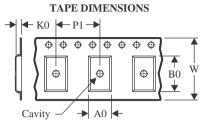

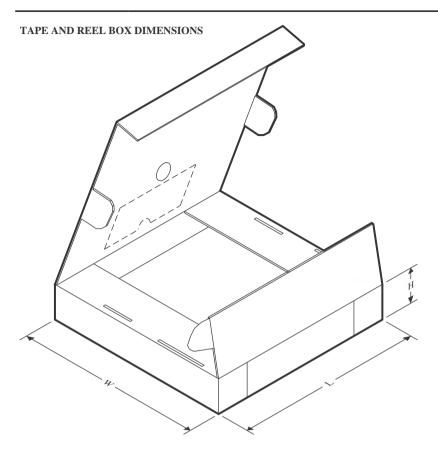

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

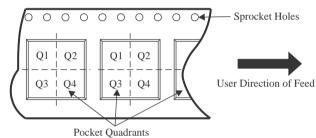

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           |      | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65HVDA195QDRQ1 | SOIC | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

### \*All dimensions are nominal

| Ì | Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|------------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ı | SN65HVDA195QDRQ1 | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |  |

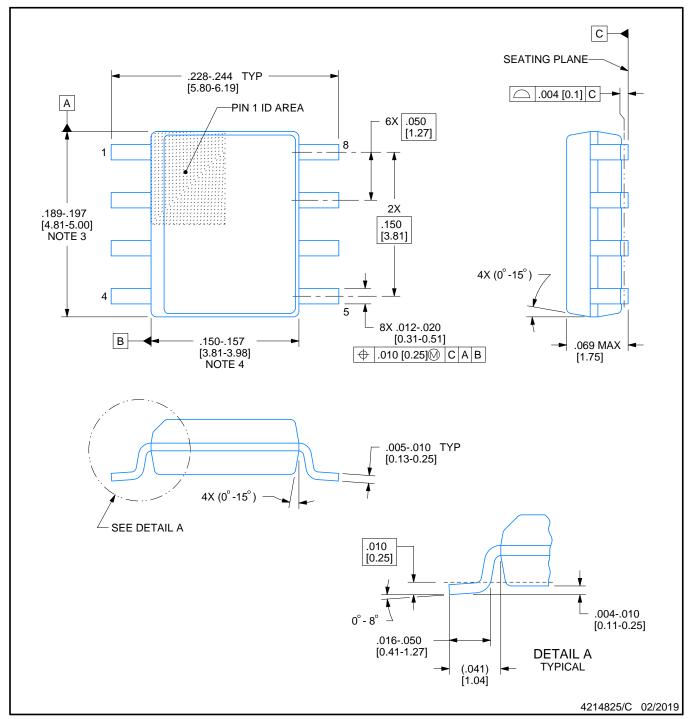

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

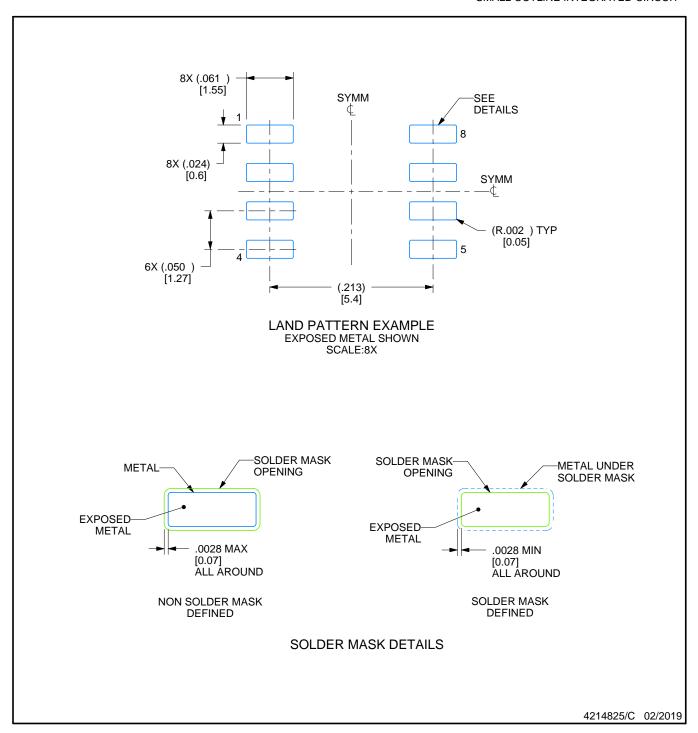

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

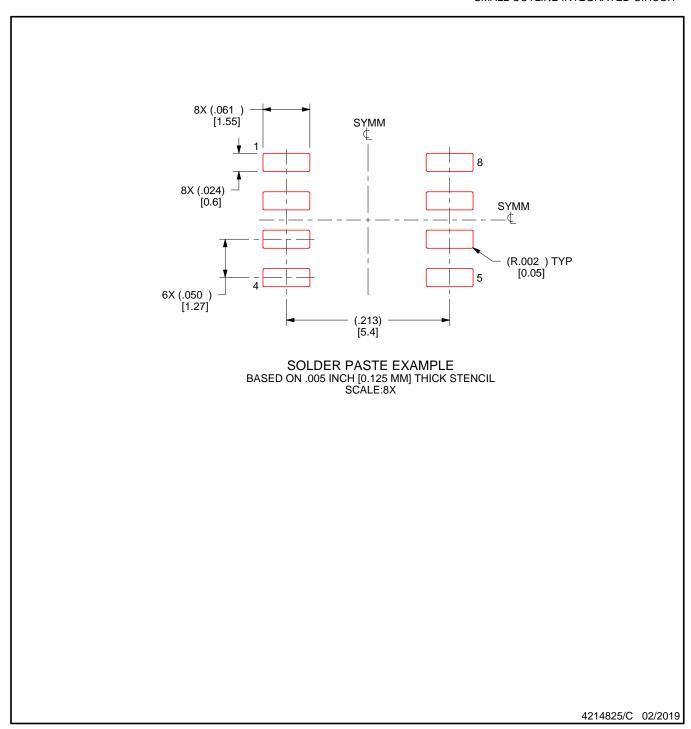

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TI はそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022. Texas Instruments Incorporated