🕳 Order

Now

**TAS5414C**

JAJSCS5-DECEMBER 2016

参考資料

# TAS5414C 4チャネル、アフターマーケット車載用クラスDアンプ

Technical

Documents

## 1 特長

- 4チャネルのシングル・エンド・アナログ入力、 クラスDオーディオ・アンプ

- 10% THD+N時の標準出力電力

- 14.4Vで4Ωに対して28W/Ch

- 14.4Vで2Ωに対して50W/Ch

- 24Vで4Ωに対して79W/Ch

- 24Vで2Ωに対して150W/Ch (PBTL)

- チャネルのパラレル化(PBTL)によって大電流アプ リケーションに対応

- THD+N < 0.02%、1kHz、4Ωに対して1W

- ポップ音およびクリック音低減テクノロジ(特許取 得済み)

- ソフト・ミュートとゲイン・ランプ制御

- 同相ランプ

- AM干渉防止(特許取得済み)

- サイクル単位電流制限(特許取得済み)

- 75dB PSRR

- 4アドレスのI<sup>2</sup>Cシリアル・インターフェイスによるデバイス構成と制御

- チャネル・ゲイン: 12dB、20dB、26dB、32dB

- 負荷診断機能:

- 出力開路および負荷短絡

- 出力と電源、出力とグランドの間の短絡

- ツイータ検出(特許取得済み)

- 保護および監視機能:

- 短絡保護

- ロード・ダンプ保護(50V)

- 偶発的なグランド・オープン/電源オープンへの耐性

- 音楽再生中の出力DCレベル検出(特許取得済み) 過熱保護

- 迥然休暖

- 過電圧および電圧低下

- クリップ検出

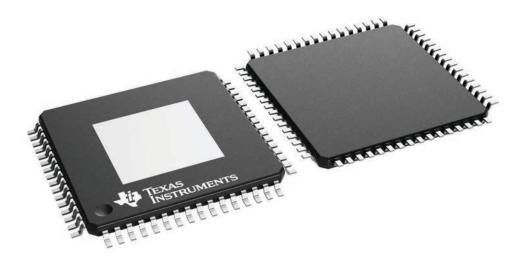

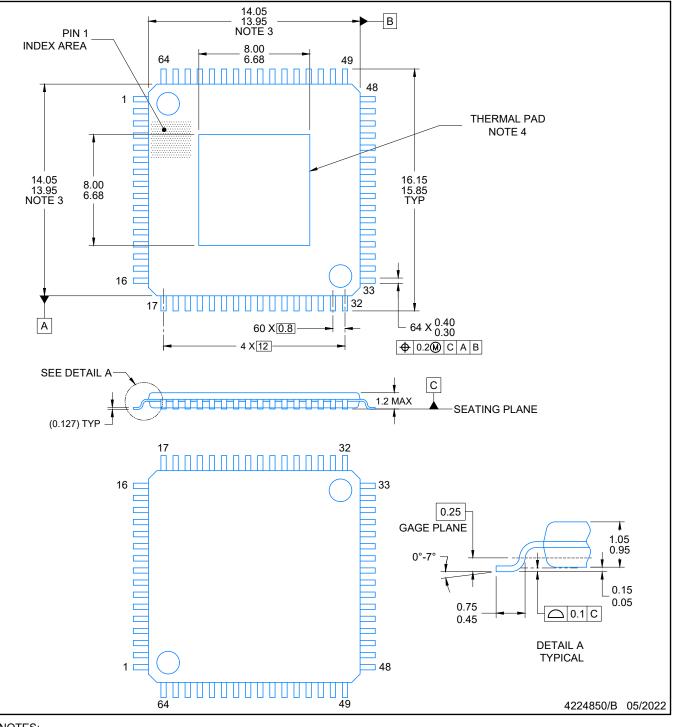

- 64ピンのQFP (PHD)パワー・パッケージ、ヒート・スラグ付き

- 周囲温度範囲 -20℃~105℃

- 2 アプリケーション

- アフターマーケット用ヘッドユニット

- アフターマーケット用外部オーディオ・アンプ

## 3 概要

🥭 Tools &

Software

TAS5414Cは4チャネルのクラスDオーディオ・アンプで、 車載用ヘッド・ユニットおよび外部アンプ・モジュール用に 設計されています。14.4V電源から1%未満のTHD+Nで、 4Ωに対して連続的に23Wを4チャネルで供給できます。 各チャネルは、1%のTHD+Nで2Ωへ38Wを供給すること もできます。TAS5414Cはシングル・エンドのアナログ入力 を使用します。デバイスのクラスDのPWMトポロジにより、 従来のリニア・アンプ・ソリューションと比べて効率が劇的 に向上します。これによって、一般的な音楽再生の状況に おいて、アンプの消費電力が約10分の1に低減します。デ バイスには負荷診断機能が組み込まれており、出力の誤 接続を検出して診断できるため、製造プロセスにおいてテ スト時間を短縮するために役立ちます。

Support &

Community

22

#### 製品情報<sup>(1)</sup>

| 型番       | パッケージ      | 本体サイズ(公称)       |

|----------|------------|-----------------|

| TAS5414C | HTQFP (64) | 14.00mm×14.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

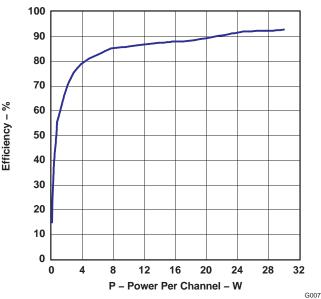

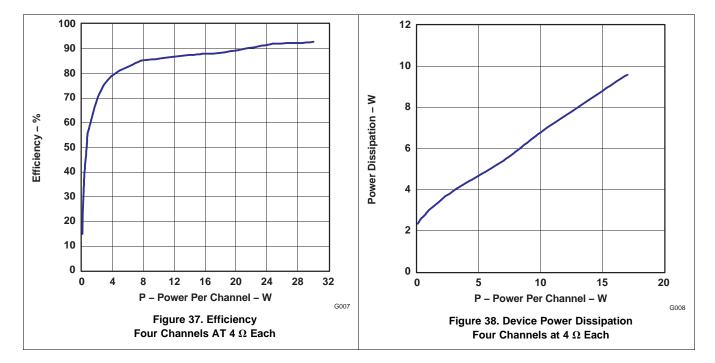

## チャネルごとの出力と効率との関係

# 目次

| 1 | 特長   |                                                               |

|---|------|---------------------------------------------------------------|

| 2 | アプ   | リケーション 1                                                      |

| 3 | 概要   | Ę 1                                                           |

| 4 | 改訂   | `履歴2                                                          |

| 5 | Pin  | Configuration and Functions 3                                 |

| 6 |      | cifications5                                                  |

|   | 6.1  | Absolute Maximum Ratings 5                                    |

|   | 6.2  | ESD Ratings5                                                  |

|   | 6.3  | Recommended Operating Conditions 5                            |

|   | 6.4  | Thermal Information 6                                         |

|   | 6.5  | Electrical Characteristics 6                                  |

|   | 6.6  | Timing Requirements for I <sup>2</sup> C Interface Signals 10 |

|   | 6.7  | Typical Characteristics 11                                    |

| 7 | Deta | ailed Description 13                                          |

|   | 7.1  | Overview 13                                                   |

|   | 7.2  | Functional Block Diagram 13                                   |

|   | 7.3  | Feature Descption 14                                          |

|   | 7.4  | Device Functional Modes 20                                    |

|   | 7.5  | Programming 24                                                |

|   |      |                                                               |

| 7.6  | Register Maps                                                                                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | -                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | -                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

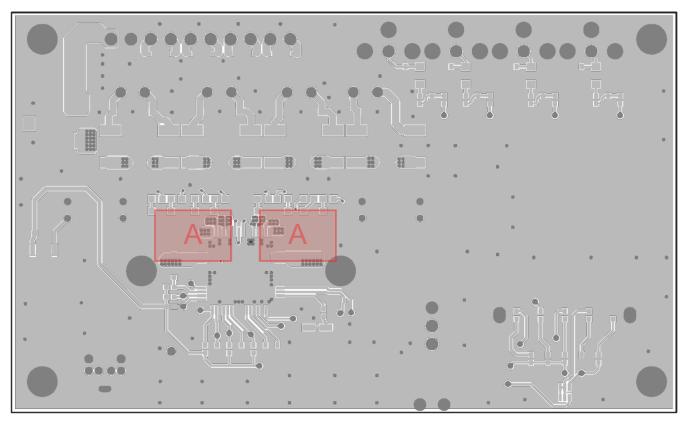

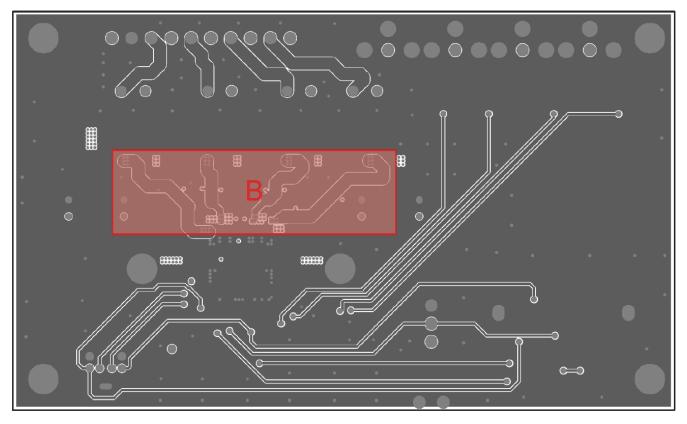

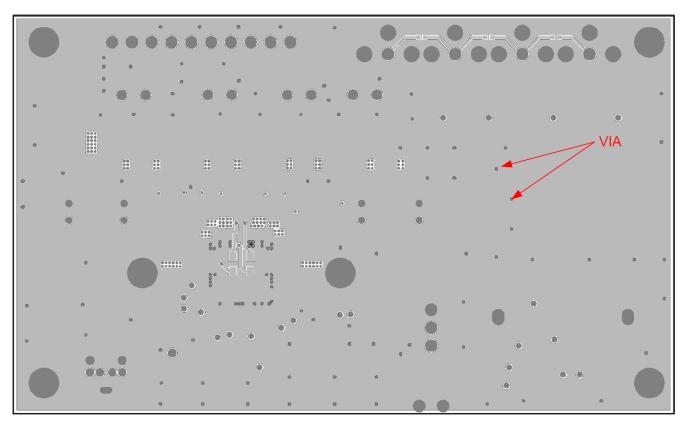

| Layo | out                                                                                                                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.1 | Layout Guidelines                                                                                                        | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.2 | Layout Example                                                                                                           | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.3 | Thermal Consideration                                                                                                    | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.4 | Electrical Connection of Heat Slug and Heat                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5    | Sink                                                                                                                     | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.5 | EMI Considerations                                                                                                       | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| デバ   | イスおよびドキュメントのサポート                                                                                                         | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11.1 | デバイス・サポート                                                                                                                | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11.2 | ドキュメントのサポート                                                                                                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11.3 |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11.4 | 商標                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11.5 | 静電気放電に関する注意事項                                                                                                            | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11.6 | 用語集                                                                                                                      | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

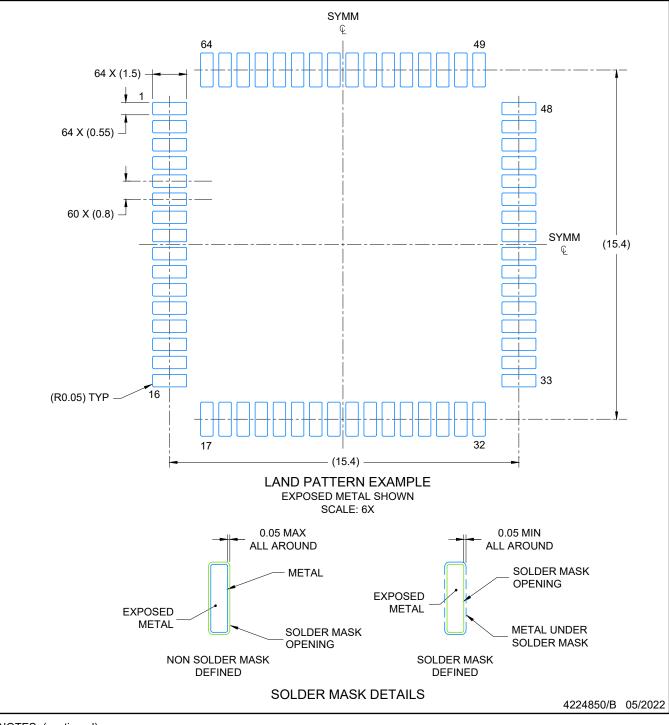

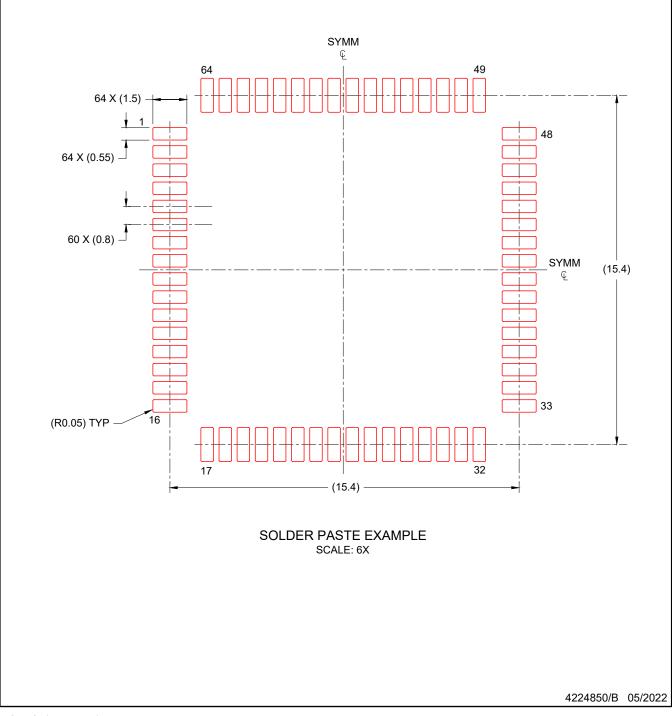

| メカニ  | ニカル、パッケージ、および注文情報                                                                                                        | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Appl<br>8.1<br>8.2<br>Powe<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>デバ<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6 | Application and Implementation         8.1 Application Information         8.2 Typical Application         Power Supply Recommendations         Layout         10.1 Layout Guidelines         10.2 Layout Example         10.3 Thermal Consideration         10.4 Electrical Connection of Heat Slug and Heat Sink         10.5 EMI Considerations         デバイスおよびドキュメントのサポート         11.1 デバイス・サポート         11.2 ドキュメントのサポート         11.3 コミュニティ・リソース         11.4 商標         11.5 静電気放電に関する注意事項         11.6 用語集 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付       | 改訂内容 | 注  |

|----------|------|----|

| 2016年12月 | *    | 初版 |

www.ti.com

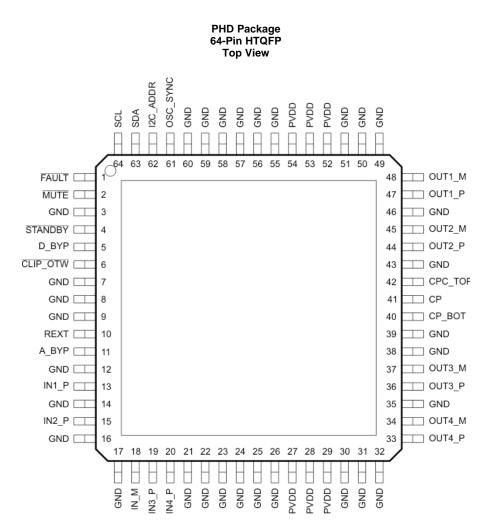

## 5 Pin Configuration and Functions

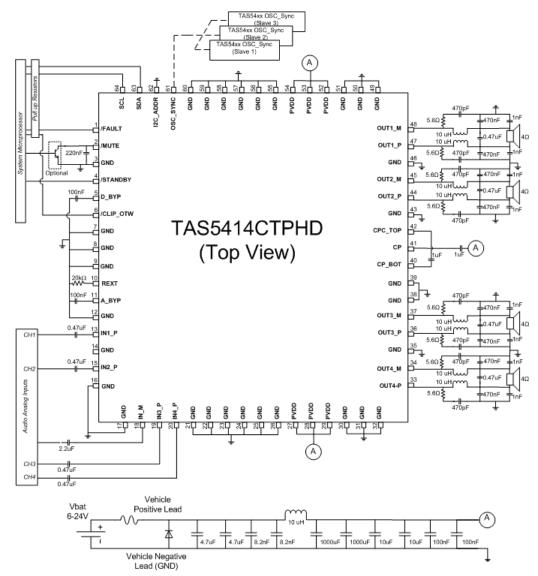

The pin assignments are shown as follows.

TAS5414C JAJSCS5 – DECEMBER 2016

www.ti.com

Texas Instruments

|          | PIN                                                                                                                                |                     |                                                                                               |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

|          |                                                                                                                                    |                     |                                                                                               |  |  |  |  |

| NAME     | TAS5414C<br>PHD Package<br>NO.                                                                                                     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                   |  |  |  |  |

| A_BYP    | 11                                                                                                                                 | PBY                 | Bypass pin for the AVDD analog regulator                                                      |  |  |  |  |

| CLIP_OTW | 6                                                                                                                                  | DO                  | Reports CLIP, OTW, or both. It also reports tweeter detection during tweeter mode. Open-drain |  |  |  |  |

| СР       | 41                                                                                                                                 | CP                  | Top of main storage capacitor for charge pump (bottom goes to PVDD)                           |  |  |  |  |

| CPC_BOT  | 40                                                                                                                                 | CP                  | Bottom of flying capacitor for charge pump                                                    |  |  |  |  |

| CPC_TOP  | 42                                                                                                                                 | CP                  | Top of flying capacitor for charge pump                                                       |  |  |  |  |

| D_BYP    | 5                                                                                                                                  | PBY                 | Bypass pin for DVDD regulator output                                                          |  |  |  |  |

| FAULT    | 1                                                                                                                                  | DO                  | Global fault output (open drain): UV, OV, OTSD, OCSD, DC                                      |  |  |  |  |

| GND      | 3, 7, 8, 9, 12, 14, 16, 17,<br>21, 22, 23, 24, 25, 26, 30,<br>31, 32, 35, 38, 39, 43, 46,<br>49, 50, 51, 55, 56, 57, 58,<br>59, 60 | GND                 | Ground                                                                                        |  |  |  |  |

| I2C_ADDR | 62                                                                                                                                 | AI                  | I <sup>2</sup> C address bit                                                                  |  |  |  |  |

| IN1_P    | 13                                                                                                                                 | AI                  | Non-inverting analog input for channel 1                                                      |  |  |  |  |

| IN2_P    | 15                                                                                                                                 | AI                  | Non-inverting analog input for channel 2                                                      |  |  |  |  |

| IN3_P    | 19                                                                                                                                 | AI                  | Non-inverting analog input for channel 3                                                      |  |  |  |  |

| IN4_P    | 20                                                                                                                                 | AI                  | Non-inverting analog input for channel 4                                                      |  |  |  |  |

| IN_M     | 18                                                                                                                                 | ARTN                | Signal return for the four analog channel inputs (TAS5414C only)                              |  |  |  |  |

| MUTE     | 2                                                                                                                                  | AI                  | Gain ramp control: mute (low), play (high)                                                    |  |  |  |  |

| OSC_SYNC | 61                                                                                                                                 | DI/DO               | Oscillator input from master or output to slave amplifiers                                    |  |  |  |  |

| OUT1_M   | 48                                                                                                                                 | PO                  | - polarity output for bridge 1                                                                |  |  |  |  |

| OUT1_P   | 47                                                                                                                                 | PO                  | + polarity output for bridge 1                                                                |  |  |  |  |

| OUT2_M   | 45                                                                                                                                 | PO                  | - polarity output for bridge 2                                                                |  |  |  |  |

| OUT2_P   | 44                                                                                                                                 | PO                  | + polarity output for bridge 2                                                                |  |  |  |  |

| OUT3_M   | 37                                                                                                                                 | PO                  | - polarity output for bridge 3                                                                |  |  |  |  |

| OUT3_P   | 36                                                                                                                                 | PO                  | + polarity output for bridge 3                                                                |  |  |  |  |

| OUT4_M   | 34                                                                                                                                 | PO                  | - polarity output for bridge 4                                                                |  |  |  |  |

| OUT4_P   | 33                                                                                                                                 | PO                  | + polarity output for bridge 4                                                                |  |  |  |  |

| PVDD     | 27, 28, 29, 52, 53, 54                                                                                                             | PWR                 | PVDD supply                                                                                   |  |  |  |  |

| REXT     | 10                                                                                                                                 | AI                  | Precision resistor pin to set analog reference                                                |  |  |  |  |

| SCL      | 64                                                                                                                                 | DI                  | I <sup>2</sup> C clock input from system I <sup>2</sup> C master                              |  |  |  |  |

| SDA      | 63                                                                                                                                 | DI/DO               | I <sup>2</sup> C data I/O for communication with system I <sup>2</sup> C master               |  |  |  |  |

| STANDBY  | 4                                                                                                                                  | DI                  | Active-low STANDBY pin. Standby (low), power up (high)                                        |  |  |  |  |

(1) DI = digital input, DO = digital output, AI = analog input, ARTN = analog signal return, PWR = power supply, PBY = power bypass, PO = power output, GND = ground, CP = charge pump.

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

|                                   |                                                                                  |                                            | MIN  | MAX   | UNIT |

|-----------------------------------|----------------------------------------------------------------------------------|--------------------------------------------|------|-------|------|

| PVDD                              | DC supply voltage range                                                          | Relative to GND                            | -0.3 | 30    | V    |

| PVDD <sub>MAX</sub>               | Pulsed supply voltage range                                                      | t ≤ 100 ms exposure                        | -1   | 50    | V    |

| PVDD <sub>RAMP</sub>              | Supply voltage ramp rate                                                         |                                            |      | 15    | V/ms |

| I <sub>PVDD</sub>                 | Externally imposed dc supply current per PVDD or GND pin                         |                                            |      | ±12   | А    |

| I <sub>PVDD_MAX</sub>             | Pulsed supply current per PVDD pin (one shot)                                    | t < 100 ms                                 |      | 17    | А    |

| I <sub>O</sub>                    | Maximum allowed dc current per output pin                                        |                                            |      | ±13.5 | А    |

| I <sub>O_MAX</sub> <sup>(1)</sup> | Pulsed output current per output pin (single pulse)                              | t < 100 ms                                 |      | ±17   | А    |

| I <sub>IN_MAX</sub>               | Maximum current, all digital and analog input pins <sup>(2)</sup>                | DC or pulsed                               |      | ±1    | mA   |

| I <sub>MUTE_MAX</sub>             | Maximum current on MUTE pin                                                      | DC or pulsed                               |      | ±20   | mA   |

| I <sub>IN_ODMAX</sub>             | Maximum sink current for open-drain pins                                         |                                            |      | 7     | mA   |

| V <sub>LOGIC</sub>                | Input voltage range for pin relative to GND (SCL, SDA, I2C_ADDR pins)            | Supply voltage range:<br>6V < PVDD < 24 V  | -0.3 | 6     | V    |

| V <sub>MUTE</sub>                 | Voltage range for MUTE pin relative to GND                                       | Supply voltage range:<br>6 V < PVDD < 24 V | -0.3 | 7.5   | V    |

| V <sub>STANDBY</sub>              | Input voltage range for STANDBY pin                                              | Supply voltage range:<br>6 V < PVDD < 24 V | -0.3 | 5.5   | V    |

| V <sub>OSC_SYNC</sub>             | Input voltage range for OSC_SYNC pin relative to GND                             | Supply voltage range:<br>6 V < PVDD < 24 V | -0.3 | 3.6   | V    |

| V <sub>GND</sub>                  | Maximum voltage between GND pins                                                 |                                            |      | ±0.3  | V    |

| V <sub>AIN_AC_MAX</sub>           | Maximum ac-coupled input voltage for TAS5414C <sup>(2)</sup> , analog input pins | Supply voltage range:<br>6 V < PVDD < 24 V |      | 1.9   | Vrms |

| TJ                                | Maximum operating junction temperature range                                     |                                            | -55  | 150   | °C   |

| T <sub>stg</sub>                  | Storage temperature                                                              |                                            | -55  | 150   | °C   |

(1) Pulsed current ratings are maximum survivable currents externally applied to the device. The device may encounter high currents during reverse-battery, fortuitous open-ground, and fortuitous open-supply fault conditions.

(2) See the Application Information section for information on analog input voltage and ac coupling.

### 6.2 ESD Ratings

|                    |                         |                                                                |                                               | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------|-----------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per AEC                                | Q100-002 <sup>(1)</sup>                       | ±2500 | V    |

|                    |                         |                                                                | Corner pins excluding SCL                     | ±750  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM),<br>per AEC Q100-011<br>PHD Package | All pins (including SCL) except CP and CP_Top | ±600  | V    |

|                    |                         |                                                                | CP and CP_Top pins                            | ±400  |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions<sup>(1)</sup>

|                                 |                                         |                                                                               | MIN | TYP  | MAX                   | UNIT |

|---------------------------------|-----------------------------------------|-------------------------------------------------------------------------------|-----|------|-----------------------|------|

| PVDD <sub>OP</sub>              | DC supply voltage range relative to GND |                                                                               | 6   | 14.4 | 24                    | V    |

| V <sub>AIN</sub> <sup>(2)</sup> | Analog audio input signal level         | AC-coupled input voltage                                                      | 0   |      | 0.25–1 <sup>(3)</sup> | Vrms |

| T <sub>A</sub>                  | Ambient temperature                     |                                                                               | -20 |      | 105                   | °C   |

| TJ                              | Junction temperature                    | An adequate heat sink is required to keep $T_{\rm J}$ within specified range. | -40 |      | 115                   | °C   |

| RL                              | Nominal speaker load impedance          |                                                                               | 2   | 4    |                       | Ω    |

(1) The *Recommended Operating Conditions* table specifies only that the device is functional in the given range. See the *Electrical Characteristics* table for specified performance limits.

(2) Signal input for full unclipped output with gains of 32 dB, 26 dB, 20 dB, and 12 dB

(3) Maximum recommended input voltage is determined by the gain setting.

Copyright © 2016, Texas Instruments Incorporated

# Recommended Operating Conditions<sup>(1)</sup> (continued)

|                             |                                                                                                                                 |                                                                               | MIN  | TYP      | MAX  | UNIT |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|----------|------|------|

| V <sub>PU</sub>             | Pullup voltage supply (for open-drain logic outputs)                                                                            |                                                                               | 3    | 3.3 or 5 | 5.5  | V    |

| R <sub>PU_EXT</sub>         | External pullup resistor on open-drain logic outputs                                                                            | Resistor connected between open-drain logic output and $V_{\text{PU}}$ supply | 10   |          | 50   | kΩ   |

| R <sub>PU_I2C</sub>         | I <sup>2</sup> C pullup resistance on SDA and SCL pins                                                                          |                                                                               | 1    | 4.7      | 10   | kΩ   |

| R <sub>I2C_ADD</sub>        | Total resistance of voltage divider for I <sup>2</sup> C address<br>slave 1 or slave 2, connected between D_BYP and<br>GND pins |                                                                               | 10   |          | 50   | kΩ   |

| R <sub>REXT</sub>           | External resistance on REXT pin                                                                                                 | 1% tolerance required                                                         | 19.8 | 20       | 20.2 | kΩ   |

| $C_{D\_BYP}$ , $C_{A\_BYP}$ | External capacitance on D_BYP and A_BYP pins                                                                                    |                                                                               | 10   |          | 120  | nF   |

| C <sub>OUT</sub>            | External capacitance to GND on OUT_X pins                                                                                       |                                                                               |      | 150      | 680  | nF   |

| C <sub>IN</sub>             | External capacitance to analog input pin in series<br>with input signal                                                         |                                                                               |      | 0.47     |      | μF   |

| C <sub>FLY</sub>            | Flying capacitor on charge pump                                                                                                 |                                                                               | 0.47 | 1        | 1.5  | μF   |

| C <sub>P</sub>              | Charge pump capacitor                                                                                                           | 50V needed for Load Dump                                                      | 0.47 | 1        | 1.5  | μF   |

| C <sub>MUTE</sub>           | MUTE pin capacitor                                                                                                              |                                                                               | 100  | 220      | 1000 | nF   |

| C <sub>OSCSYNC_MAX</sub>    | Allowed loading capacitance on OSC_SYNC pin                                                                                     |                                                                               |      | 75       |      | pF   |

## 6.4 Thermal Information

|                | PARAMETER                                                       | VALUE (Typical)                                                                                                                                          | UNIT |

|----------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $R_{\thetaJC}$ | Junction-to-case (heat slug) thermal<br>resistance, PHD package | 1.2                                                                                                                                                      | °C/W |

| $R_{	hetaJA}$  | Junction-to-ambient thermal resistance                          | This device is not intended to be used without a heatsink. Therefore, $R_{\theta JA}$ is not specified. Refer to the <i>Thermal Information</i> section. | °C/W |

## 6.5 Electrical Characteristics

|                        | PARAMETER                         | TEST CONDITIONS                                                                      | MIN | ТҮР   | MAX  | UNIT |

|------------------------|-----------------------------------|--------------------------------------------------------------------------------------|-----|-------|------|------|

| OPERATING              | CURRENT                           |                                                                                      |     |       |      |      |

| I <sub>PVDD_IDLE</sub> | PVDD idle current                 | All four channels in MUTE mode                                                       |     | 170   | 220  | mA   |

| I <sub>PVDD_Hi-Z</sub> |                                   | All four channels in Hi-Z mode                                                       |     | 93    |      | mA   |

| I <sub>PVDD_STBY</sub> | PVDD standby current              | STANDBY mode, $T_J \le 85^{\circ}C$                                                  |     | 2     | 10   | μA   |

| OUTPUT PO              | WER                               |                                                                                      |     |       |      |      |

|                        |                                   | 4 $\Omega$ , PVDD = 14.4 V, THD+N ≤ 1%, 1 kHz, T <sub>c</sub> = 75°C                 |     | 23    |      |      |

|                        |                                   | 4 Ω, PVDD = 14.4 V, THD+N = 10%, 1 kHz, $T_c = 75^{\circ}C$                          | 25  | 28    |      |      |

|                        |                                   | 4 $\Omega$ , PVDD = 24 V, THD+N = 10%, 1 kHz, T <sub>c</sub> = 75°C                  | 63  | 79    |      |      |

|                        |                                   | 2 Ω, PVDD = 14.4 V, THD+N = 1%, 1 kHz, $T_c = 75^{\circ}C$                           |     | 38    |      |      |

| P <sub>OUT</sub>       | Output power per channel          | 2 Ω, PVDD = 14.4 V, THD+N = 10%, 1 kHz, T <sub>c</sub> = 75°C                        | 40  | 50    |      | W    |

|                        |                                   | PBTL 2- $\Omega$ operation, PVDD = 24 V, THD+N = 10%, 1 kHz, T <sub>c</sub> = 75°C   |     | 150   |      |      |

|                        |                                   | PBTL 1- $\Omega$ operation, PVDD = 14.4 V, THD+N = 10%, 1 kHz, T <sub>c</sub> = 75°C |     | 90    |      |      |

| EFF <sub>P</sub>       | Power efficiency                  | 4 channels operating, 23-W output power/ch, L = 10 $\mu$ H, T <sub>J</sub> ≤ 85°C    |     | 90%   |      |      |

| AUDIO PERI             | FORMANCE                          |                                                                                      |     |       | ļ    |      |

| V <sub>NOISE</sub>     | Noise voltage at output           | Zero input, and A-weighting                                                          |     | 60    | 100  | μV   |

|                        | Channel crosstalk                 | $P = 1 W$ , f = 1 kHz, enhanced crosstalk enabled via $I^2C$ (reg. 0x10)             | 70  | 85    |      | dB   |

| PSRR                   | Power-supply rejection ratio      | PVDD = 14.4 Vdc + 1 Vrms, f = 1 kHz                                                  | 60  | 75    |      | dB   |

| THD+N                  | Total harmonic distortion + noise | P = 1 W, f = 1 kHz                                                                   |     | 0.02% | 0.1% |      |

|                        |                                   |                                                                                      | 336 | 357   | 378  |      |

| f <sub>S</sub>         | Switching frequency               | Switching frequency selectable for AM interference<br>avoidance                      | 392 | 417   | 442  | kHz  |

|                        |                                   |                                                                                      | 470 | 500   | 530  |      |

## **Electrical Characteristics (continued)**

|                                                    | PARAMETER                                         | TEST CONDITIONS                                                | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

| R <sub>AIN</sub>                                   | Analog input resistance                           | Internal shunt resistance on each input pin                    | 63   | 85   | 106  | kΩ   |

| V <sub>IN_CM</sub>                                 | Common-mode input voltage                         | AC-coupled common-mode input voltage (zero differential input) |      | 1.3  |      | Vrms |

| V <sub>CM_INT</sub>                                | Internal common-mode input bias voltage           | Internal bias applied to IN_M pin                              |      | 3.3  |      | V    |

|                                                    |                                                   |                                                                | 11   | 12   | 13   |      |

| G                                                  | Voltage gain (V <sub>O</sub> /V <sub>IN</sub> )   | Source impedance = 0 $\Omega$ , gain measurement taken at 1    | 19   | 20   | 21   | dB   |

| 9                                                  |                                                   | W of power per channel                                         | 25   | 26   | 27   | uВ   |

|                                                    |                                                   |                                                                | 31   | 32   | 33   |      |

| G <sub>CH</sub>                                    | Channel-to-channel variation                      | Any gain commanded                                             | -1   | 0    | 1    | dB   |

| PWM OUTPUT S                                       | TAGE                                              |                                                                |      |      |      |      |

| R <sub>DS(on)</sub>                                | FET drain-to-source resistance                    | Not including bond wire resistance, $T_J = 25^{\circ}C$        |      | 65   | 90   | mΩ   |

| V <sub>O_OFFSET</sub>                              | Output offset voltage                             | Zero input signal, G = 26 dB                                   |      | ±10  | ±50  | mV   |

| PVDD OVERVOL                                       | TAGE (OV) PROTECTION                              |                                                                |      |      |      |      |

| V <sub>OV_SET</sub>                                | PVDD overvoltage shutdown set                     |                                                                | 24.6 | 26.4 | 28.2 | V    |

| V <sub>OV_CLEAR</sub>                              | PVDD overvoltage shutdown clear                   |                                                                | 24.4 | 25.9 | 27.4 | V    |

|                                                    | DLTAGE (UV) PROTECTION                            |                                                                |      |      | 1    |      |

| V <sub>UV_SET</sub>                                | PVDD undervoltage shutdown set                    |                                                                | 4.9  | 5.3  | 5.6  | V    |

| V <sub>UV_CLEAR</sub>                              | PVDD undervoltage shutdown clear                  |                                                                | 6.2  | 6.6  | 7    | V    |

| AVDD                                               |                                                   |                                                                | •    |      | I    |      |

| V <sub>A_BYP</sub>                                 | A_BYP pin voltage                                 |                                                                |      | 6.5  |      | V    |

| V <sub>A_BYP_UV_SET</sub>                          | A_BYP UV voltage                                  |                                                                |      | 4.8  |      | V    |

| V <sub>A_BYP_UV_CLEAR</sub>                        | Recovery voltage A_BYP UV                         |                                                                |      | 5.3  |      | V    |

| DVDD                                               |                                                   |                                                                | 1    |      |      |      |

| V <sub>D_BYP</sub>                                 | D_BYP pin voltage                                 |                                                                |      | 3.3  |      | V    |

| POWER-ON RES                                       | SET (POR)                                         |                                                                | 1    |      |      |      |

| V <sub>POR</sub>                                   | PVDD voltage for POR                              | I <sup>2</sup> C active above this voltage                     |      |      | 4    | V    |

| V <sub>POR HY</sub>                                | PVDD recovery hysteresis voltage for POR          |                                                                |      | 0.1  |      | V    |

| REXT                                               |                                                   |                                                                | 1    | -    |      |      |

| V <sub>REXT</sub>                                  | Rext pin voltage                                  |                                                                |      | 1.27 |      | V    |

| CHARGE PUMP                                        |                                                   | 1                                                              |      |      |      |      |

| V <sub>CPUV_SET</sub>                              | CP undervoltage                                   |                                                                |      | 4.8  |      | V    |

| V <sub>CPUV_CLEAR</sub>                            | Recovery voltage for CP UV                        |                                                                |      | 4.9  |      | V    |

|                                                    | TURE (OT) PROTECTION                              | 1                                                              | 1    | -    |      |      |

| T <sub>OTW1_CLEAR</sub>                            |                                                   |                                                                | 96   | 112  | 128  | °C   |

| T <sub>OTW1_SET</sub> /<br>T <sub>OTW2_CLEAR</sub> | -                                                 |                                                                | 106  | 122  | 138  | °C   |

| T <sub>OTW2_SET</sub> /<br>T <sub>OTW3_CLEAR</sub> | Junction temperature for overtemperature warning  |                                                                | 116  | 132  | 148  | °C   |

| T <sub>OTW3_SET</sub> /<br>T <sub>OTSD_CLEAR</sub> | 1                                                 |                                                                | 126  | 142  | 158  | °C   |

| T <sub>OTSD</sub>                                  | Junction temperature for overtemperature shutdown |                                                                | 136  | 152  | 168  | °C   |

| T <sub>FB</sub>                                    | Junction temperature for overtemperature foldback | Per channel                                                    | 130  | 150  | 170  | °C   |

| CURRENT LIMIT                                      | ING PROTECTION                                    |                                                                |      |      |      |      |

|                                                    | Current limit (lood oursest)                      | Level 1                                                        | 5.5  | 7.3  | 9    | ^    |

| ILIM                                               | Current limit (load current)                      | Level 2 (default)                                              | 10.6 | 12.7 | 15   | A    |

| OVERCURRENT                                        | (OC) SHUTDOWN PROTECTION                          |                                                                |      |      |      |      |

|                                                    |                                                   | Level 1                                                        | 7.8  | 9.8  | 12.2 |      |

| I <sub>MAX</sub>                                   | Maximum current (peak output current)             | Level 2 (default), Any short to supply, ground, or other       | 44.0 | 44.0 | 477  | А    |

|                                                    |                                                   | channels                                                       | 11.9 | 14.8 | 17.7 |      |

## **Electrical Characteristics (continued)**

|                         | PARAMETER                                                                     | TEST CONDITIONS                                             | MIN | TYP | MAX | UNIT |

|-------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| TWEETER DET             | ECT                                                                           |                                                             |     |     |     |      |

| I <sub>TH_TW</sub>      | Load-current threshold for tweeter detect                                     |                                                             | 330 | 445 | 560 | mA   |

| I <sub>LIM_TW</sub>     | Load-current limit for tweeter detect                                         |                                                             |     | 2.1 |     | А    |

| STANDBY MOD             | )E                                                                            | ·                                                           |     |     |     |      |

| V <sub>IH</sub>         | STANDBY input voltage for logic-level high                                    |                                                             | 2   |     |     | V    |

| V <sub>IL</sub>         | STANDBY input voltage for logic-level low                                     |                                                             |     |     | 0.7 | V    |

| I <sub>STBY</sub>       | STANDBY pin current                                                           |                                                             |     | 0.1 | 0.2 | μA   |

| MUTE MODE               |                                                                               |                                                             |     |     |     |      |

| G <sub>MUTE</sub>       | Output attenuation                                                            | MUTE pin ≤ 0.5 V for 200ms or I <sup>2</sup> C Mute Enabled |     | 100 |     | dB   |

| DC DETECT               |                                                                               |                                                             | 1   |     |     | -    |

| V <sub>TH_DC_TOL</sub>  | DC detect threshold tolerance                                                 |                                                             |     | 25% |     | -    |

| t <sub>DCD</sub>        | DC detect step-response time for four channels                                |                                                             |     |     | 5.3 | S    |

| CLIP_OTW REP            | PORT                                                                          |                                                             |     |     |     |      |

| V <sub>OH_CLIPOTW</sub> | CLIP_OTW pin output voltage for logic level<br>high (open-drain logic output) |                                                             | 2.4 |     |     | V    |

| V <sub>OL_CLIPOTW</sub> | CLIP_OTW pin output voltage for logic level low (open-drain logic output)     | External 47-k $\Omega$ pullup resistor to 3 V–5.5 V         |     |     | 0.5 | V    |

| tDELAY_CLIPDET          | CLIP_OTW signal delay when output<br>clipping detected                        |                                                             |     |     | 20  | μS   |

| FAULT REPOR             | т                                                                             |                                                             |     |     |     |      |

| V <sub>OH_FAULT</sub>   | FAULT pin output voltage for logic-level high (open-drain logic output)       |                                                             | 2.4 |     |     | V    |

| V <sub>OL_FAULT</sub>   | FAULT pin output voltage for logic-level low (open-drain logic output)        | External 47-kΩ pullup resistor to 3 V–5.5 V                 |     |     | 0.5 | v    |

## **Electrical Characteristics (continued)**

|                                     | PARAMETER                                                              | TEST CONDITIONS                                                                  | MIN  | TYP  | MAX  | UNIT               |

|-------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|--------------------|

| OPEN, SHORT                         | DIAGNOSTICS                                                            |                                                                                  |      |      |      |                    |

| R <sub>S2P</sub> , R <sub>S2G</sub> | Maximum resistance to detect a short from OUT pin(s) to PVDD or ground |                                                                                  |      |      | 200  | Ω                  |

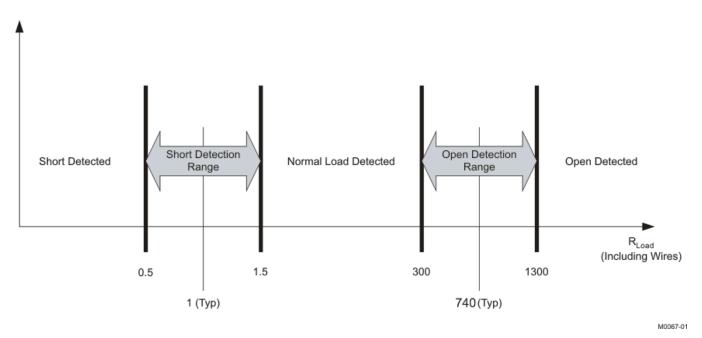

| R <sub>OPEN_LOAD</sub>              | Minimum load resistance to detect open<br>circuit                      | Including speaker wires                                                          | 300  | 740  | 1300 | Ω                  |

| R <sub>SHORTED_LOAD</sub>           | Maximum load resistance to detect short<br>circuit                     | Including speaker wires                                                          | 0.5  | 1    | 1.5  | Ω                  |

| I <sup>2</sup> C ADDRESS D          | ECODER                                                                 |                                                                                  |      |      |      |                    |

| t <sub>LATCH_I2CADDR</sub>          | Time delay to latch I <sup>2</sup> C address after POR                 |                                                                                  |      | 300  |      | μS                 |

|                                     | Voltage on I2C_ADDR pin for address 0                                  | Connect to GND                                                                   | 0%   | 0%   | 15%  |                    |

| N/                                  | Voltage on I2C_ADDR pin for address 1                                  | External resistors in series between D_BYP and GND as                            | 25%  | 35%  | 45%  | V                  |

| V <sub>I2C_ADDR</sub>               | Voltage on I2C_ADDR pin for address 2                                  | a voltage divider                                                                | 55%  | 65%  | 75%  | V <sub>D_BYP</sub> |

|                                     | Voltage on I2C_ADDR pin for address 3                                  | Connect to D_BYP                                                                 | 85%  | 100% | 100% |                    |

| l <sup>2</sup> C                    |                                                                        |                                                                                  |      |      |      |                    |

| t <sub>HOLD_I2C</sub>               | Power-on hold time before I <sup>2</sup> C communication               | STANDBY high                                                                     |      | 1    |      | ms                 |

| f <sub>SCL</sub>                    | SCL clock frequency                                                    |                                                                                  |      |      | 400  | kHz                |

| V <sub>IH</sub>                     | SCL pin input voltage for logic-level high                             | $R_{PU_{12C}} = 5 \cdot k\Omega$ pullup, supply voltage = 3.3 V or 5 V           |      |      | 5.5  | V                  |

| V <sub>IL</sub>                     | SCL pin input voltage for logic-level low                              |                                                                                  |      |      | 1.1  | V                  |

| V <sub>OH</sub>                     | SDA pin output voltage for logic-level high                            | $I^{2}C$ read, $R_{I2C} = 5 \cdot k\Omega$ pullup, supply voltage = 3.3 V or 5 V | 2.4  |      |      | V                  |

| Vo                                  | SDA pin output voltage for logic-level low                             | I <sup>2</sup> C read, 3-mA sink current                                         |      |      | 0.4  | V                  |

| V <sub>IH</sub>                     | SDA pin input voltage for logic-level high                             | $I^2C$ write, $R_{I2C} = 5-k\Omega$ pullup,<br>supply voltage = 3.3 V or 5 V     | 2.1  |      | 5.5  | V                  |

| V <sub>IL</sub>                     | SDA pin input voltage for logic-level low                              | $I^2$ C write, $R_{I2C}$ = 5-kΩ pullup,<br>supply voltage = 3.3 V or 5 V         | -0.5 |      | 1.1  | V                  |

| Cı                                  | Capacitance for SCL and SDA pins                                       |                                                                                  |      |      | 10   | pF                 |

| OSCILLATOR                          |                                                                        |                                                                                  |      |      |      |                    |

| V <sub>OH</sub>                     | OSC_SYNC pin output voltage for logic-<br>level high                   |                                                                                  | 2.4  |      |      | V                  |

| V <sub>OL</sub>                     | OSC_SYNC pin output voltage for logic-<br>level low                    | I2C_ADDR pin set to MASTER mode                                                  |      |      | 0.5  | V                  |

| V <sub>IH</sub>                     | OSC_SYNC pin input voltage for logic-level<br>high                     | I2C_ADDR pin set to SLAVE mode                                                   |      |      |      | V                  |

| V <sub>IL</sub>                     | OSC_SYNC pin input voltage for logic-level low                         |                                                                                  |      |      | 0.8  | V                  |

|                                     |                                                                        | I2C_ADDR pin set to MASTER mode, $f_S = 500 \text{ kHz}$                         | 3.76 | 4    | 4.24 |                    |

| f <sub>OSC_SYNC</sub>               | OSC_SYNC pin clock frequency                                           | I2C_ADDR pin set to MASTER mode, f <sub>S</sub> = 417 kHz                        |      | 3.33 | 3.63 | MHz                |

|                                     |                                                                        | I2C_ADDR pin set to MASTER mode, f <sub>S</sub> = 357 kHz                        | 2.68 | 2.85 | 3.0  |                    |

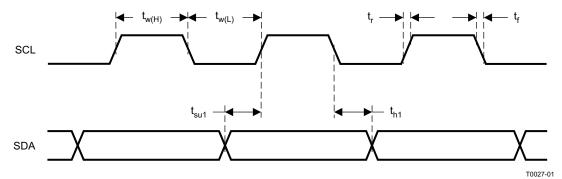

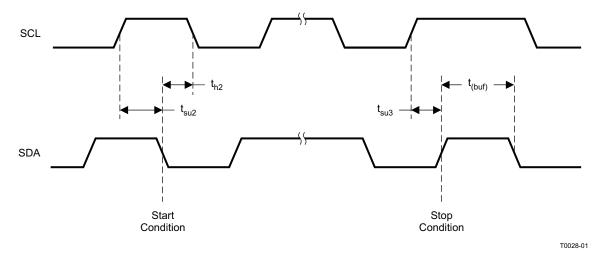

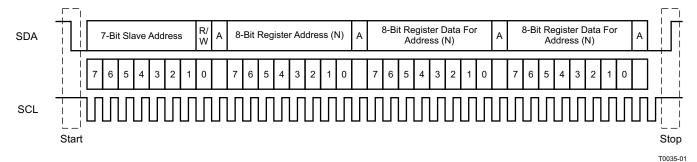

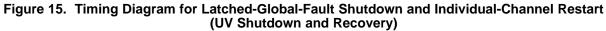

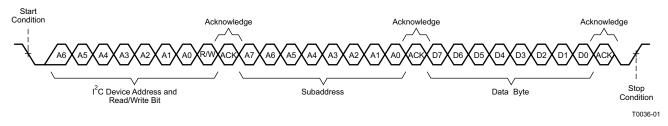

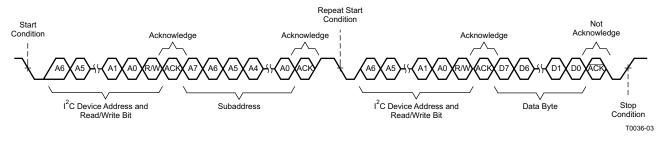

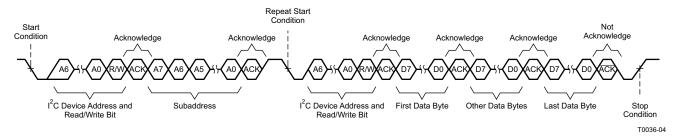

## 6.6 Timing Requirements for I<sup>2</sup>C Interface Signals

over recommended operating conditions (unless otherwise noted)

|                   |                                                                 | MIN              | TYP I | ΛAΧ | UNIT |

|-------------------|-----------------------------------------------------------------|------------------|-------|-----|------|

| t <sub>r</sub>    | Rise time for both SDA and SCL signals                          |                  |       | 300 | ns   |

| t <sub>f</sub>    | Fall time for both SDA and SCL signals                          |                  |       | 300 | ns   |

| t <sub>w(H)</sub> | SCL pulse duration, high                                        | 0.6              |       |     | μS   |

| t <sub>w(L)</sub> | SCL pulse duration, low                                         | 1.3              |       |     | μs.  |

| t <sub>su2</sub>  | Setup time for START condition                                  | 0.6              |       |     | μS   |

| t <sub>h2</sub>   | START condition hold time until generation of first clock pulse | 0.6              |       |     | μS   |

| t <sub>su1</sub>  | Data setup time                                                 | 100              |       |     | ns   |

| t <sub>h1</sub>   | Data hold time                                                  | 0 <sup>(1)</sup> |       |     | ns   |

| t <sub>su3</sub>  | Setup time for STOP condition                                   | 0.6              |       |     | μS   |

| C <sub>B</sub>    | Load capacitance for each bus line                              |                  |       | 400 | pF   |

(1) A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

Figure 1. SCL and SDA Timing

Figure 2. Timing for Start and Stop Conditions

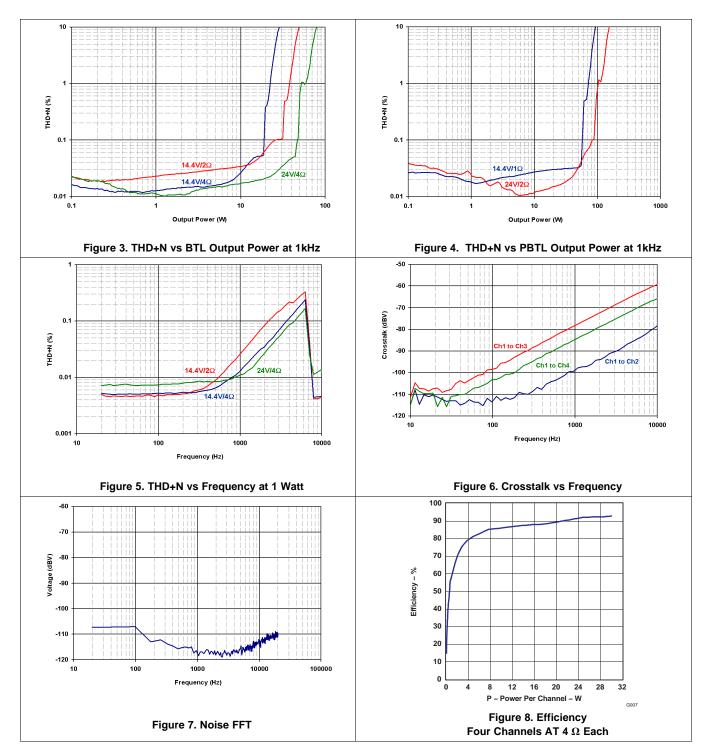

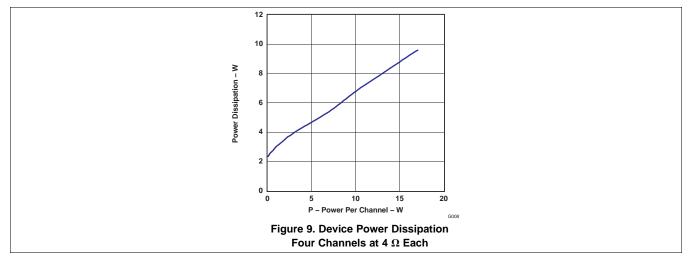

## 6.7 Typical Characteristics

TAS5414C JAJSCS5 – DECEMBER 2016 Texas Instruments

www.ti.com

# **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

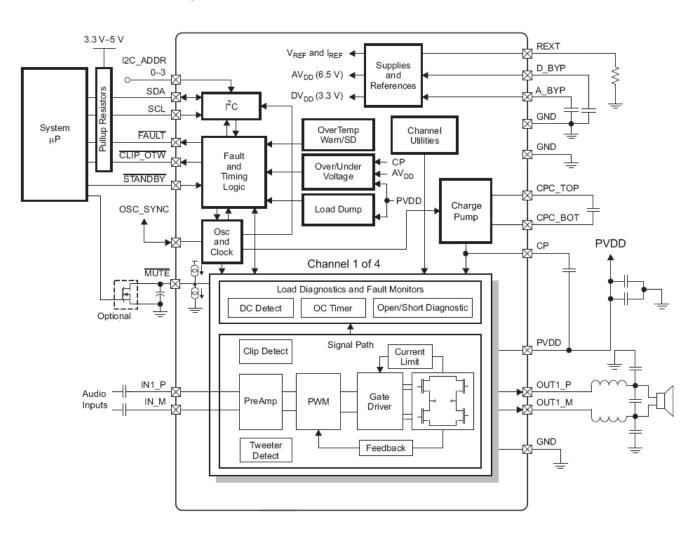

The TAS5414C is a single-chip, four-channel, analog-input audio amplifier. The design uses an ultra-efficient class-D technology developed by Texas Instruments. This technology allows for reduced power consumption, reduced heat, and reduced peak currents in the electrical system. The device realizes an audio sound system design with smaller size and lower weight than traditional class-AB solutions.

There are eight core design blocks:

- Preamplifier

- PWM

- Gate drive

- Power FETs

- Diagnostics

- Protection

- Power supply

- I<sup>2</sup>C serial communication bus

### 7.2 Functional Block Diagram

### 7.3 Feature Descption

#### 7.3.1 Preamplifier

The preamplifier is a high-input-impedance, low-noise, low-offset-voltage input stage with adjustable gain. The high input impedance allows the use of low-cost input capacitors while still achieving extended low-frequency response. A dedicated, internally regulated supply pwoers the preamplifier, giving it excellent noise immunity and channel separation. The preamplifier also includes:

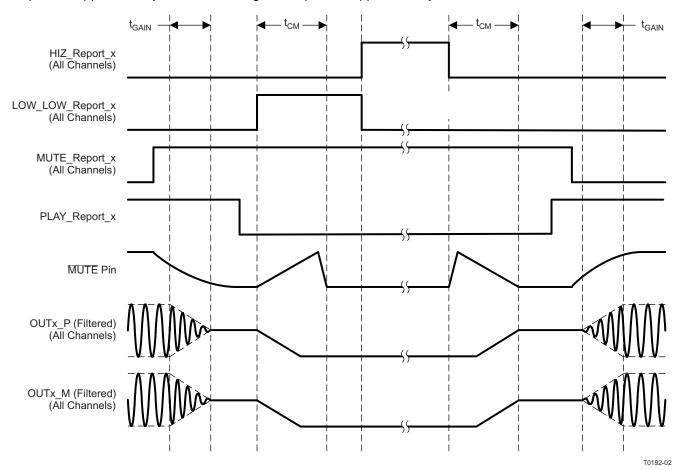

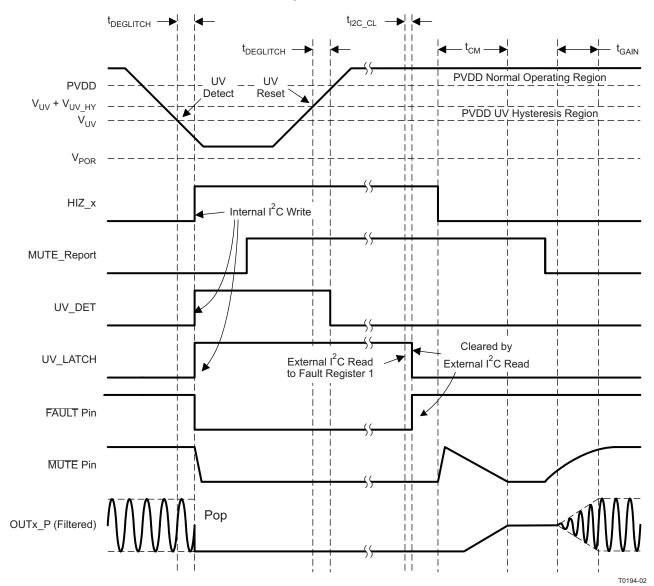

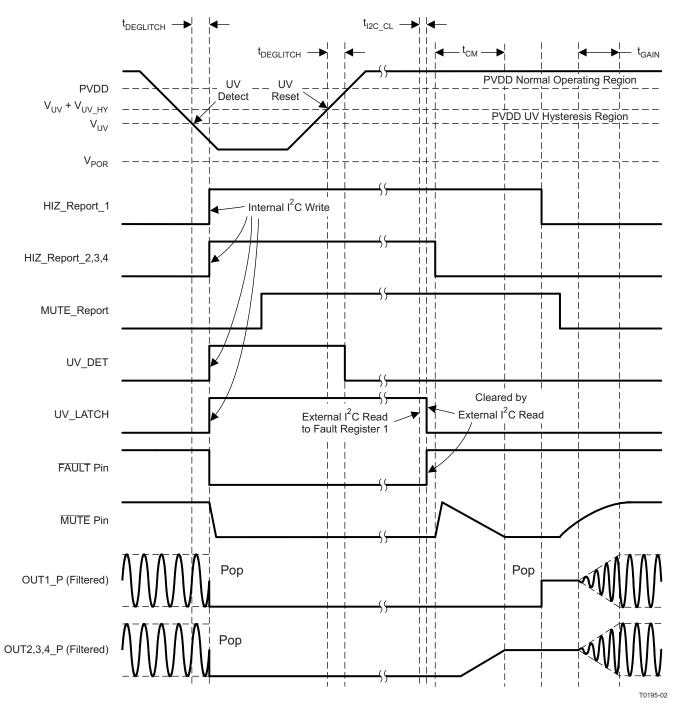

- 1. **Mute Pop-and-Click Control** The device ramps the gain gradually when receiving a mute or play command. The start or stopping of switching in a class-D amplifier can cause another form of click and pop. The TAS5414C incorporates a patented method to reduce the pop energy during the switching startup and shutdown sequence. Fault conditions require rapid protection response by the TAS5414C, which does not have time to ramp the gain down in a pop-free manner. The <u>device transitions</u> into Hi-Z mode when encountering an OV, UV, OC, OT, or dc fault. Also, activation of the STANDBY pin may not be pop-free.

- 2. **Gain Control** Setting of gains for the four channels occurs in the preamplifier via I<sup>2</sup>C control registers, outside of the global feedback resistors of the device, thus allowing for stability of the system at all gain settings with properly loaded conditions.

#### 7.3.2 Pulse-Width Modulator (PWM)

The PWM converts the analog signal from the preamplifier into a switched signal of varying duty cycle. This is the critical stage that defines the class-D architecture. In the TAS5414C, the modulator is an advanced design with high bandwidth, low noise, low distortion, excellent stability, and full 0–100% modulation capability. The patented PWM uses clipping recovery circuitry to eliminate the deep saturation characteristic of PWMs when the input signal exceeds the modulator waveform.

#### 7.3.3 Gate Drive

The gate driver accepts the low-voltage PWM signal and level-shifts it to drive a high-current, full-bridge, power FET stage. The device uses proprietary techniques to optimize EMI and audio performance.

#### 7.3.4 Power FETs

The BTL output for each channel comprises four rugged N-channel 30-V 65-m $\Omega$  FETs for high efficiency and maximum power transfer to the load. These FETs can handle large voltage transients during load dump.

#### 7.3.5 Load Diagnostics

The device incorporates load diagnostic circuitry designed to help pinpoint the nature of output misconnections during installation. The TAS5414C includes functions for detecting and determining the status of output connections. The device supports the following diagnostics:

- Short to GND

- Short to PVDD

- Short across load

- Open load

- Tweeter detection

Reporting to the system of the presence of <u>any of the short</u> or open conditions occurs via I<sup>2</sup>C register read. One can read the tweeter-detect status from the CLIP\_OTW pin when properly configured.

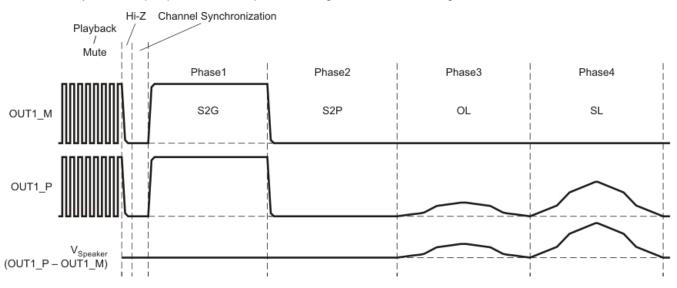

1. **Output Short and Open Diagnostics** — The device contains circuitry designed to detect shorts and open conditions on the outputs. Invocation of the load diagnostic function can only occur when the output is in the Hi-Z mode. There are four phases of test during load diagnostics and two levels of test. In the full level, all channels must be in the Hi-Z state. Testing covers all four phases on each channel, all four channels at the same time. When fewer than four channels are in Hi-Z, the reduced level of test is the only available option. In the reduced level, the only tests available are short to PVDD and short to GND. Load diagnostics can occur at power up before moving the amplifier out of Hi-Z mode. If the amplifier is already in play mode, it must *Mute* and then *Hi-Z* before performing the load diagnostics. By performing the mute function, the normal pop- and click-free transitions occur before the diagnostics begin. Performance of the diagnostics is as shown in Figure 10. Figure 11 shows the impedance ranges for the open-load and shorted-load diagnostics. Reading the results of the diagnostics is from the diagnostic register via I<sup>2</sup>C for each channel. With the default settings and MUTE capacitor, the S2G and S2P phase take approximately 20 ms each, the OL phase

#### Feature Descption (continued)

takes approximately 100 ms, and the SL takes approximately 230 ms. In I<sup>2</sup>C register 0x10, bit D4 can extend the test time for S2P and S2G to 80 ms each. To prevent false S2G and S2P faults, this time extension is necessary if the output pins have a capacitance higher than 680 nF to ground .

Figure 10. Load Diagnostics Sequence of Events

Figure 11. Open- and Shorted-Load Detection

2. Tweeter Detection — Tweeter detection is an alternate operating mode used to determine the proper connection of a frequency-dependent load (such as a speaker with a crossover). Invoking of weeter detection is via l<sup>2</sup>C, with individual testing of all four channels recommended. Tweeter detection uses the average cycle-by-cycle current limit circuit (see CBC section) to measure the current delivered to the load. The proper implementation of this diagnostic function depends on the amplitude of a user-supplied test signal and on the impedance-versus-frequency curve of the acoustic load. The system (external to the TAS5414C) must generate a signal to which the load responds. The frequency and amplitude of this signal must be calibrated by the user to result in a current draw that is greater than the tweeter detection threshold when the load

T0188-01

#### **Feature Descption (continued)**

under test is present, and less than the detection threshold if the load is unconnected. The current level for the tweeter detection threshold, as well as the maximum current that can safely be delivered to a load when in tweeter-detection mode, is in the Electrical Characteristics section of the data sheet. Reporting of the tweeter-detection results is on the CLIP\_OTW pin during the application of the test signal. With tweeter detection activated (indicating that the tested load is present), pulses on the CLIP\_OTW pin begin to toggle. The pulses on the CLIP\_OTW pins report low whenever the current exceeds the detection threshold, and the pin remains low until the current no longer exceeds the threshold. The minimum low-pulse period that one can expect is equal to one period of the switching frequency. Having an input signal that increases the duration of detector activation (for example, increasing the amplitude of the input signal) increases the for reports amount of time which the pin low. NOTE: Because tweeter detection is an alternate operating mode, place the channels to be tested in Play mode (via register 0x0C) after tweeter detection has been activated in order to commence the detection process. Additionally, set up the CLIP\_OTW pin via register 0x0A to report the results of tweeter detection.

#### 7.3.6 Protection and Monitoring

- Cycle-By-Cycle Current Limit (CBC) The CBC current-limiting circuit terminates each PWM pulse to limit the output current flow to the average current limit (I<sub>LIM</sub>) threshold. The overall effect on the audio in the case of a current overload is quite similar to a voltage-clipping event, temporarily limiting power at the peaks of the musical signal and normal operation continues without disruption on removal of the overload. The TAS5414C does not prematurely shut down in this condition. All four channels continue in play mode and pass signal.

- 2. Overcurrent Shutdown (OCSD) Under severe short-circuit events, such as a short to PVDD or ground, the device uses a peak-current detector, and the affected channel shuts down in 200 µs to 390 µs if the conditions are severe enough. The shutdown speed depends on a number of factors, such as the impedance of the short circuit, supply voltage, and switching frequency. Only the shorted channels shut down in such a scenario. The user may restart the affected channel via I<sup>2</sup>C. An OCSD event activates the fault pin, and the I<sup>2</sup>C fault register saves a record of the affected channels. If the supply or ground short is strong enough to exceed the peak current threshold but not severe enough to trigger the OCSD, the peak current limiter prevents excess current from damaging the output FETs, and operation returns to normal after the short is removed.

- 3. DC Detect—This circuit detects a dc offset at the output of the amplifier continuously during normal operation. If the dc offset reaches the level defined in the l<sup>2</sup>C registers for the specified time period, the circuit triggers. By default, a dc detection event does not shut the output down. Disabling and enabling the shutdown function is via l<sup>2</sup>C. If enabled, the triggered channel shuts down, but the others remain playing, but with the FAULT pin asserted. The l<sup>2</sup>C registers define the dc level.

- 4. Clip Detect—The clip detect circuit alerts the user to the presence of a 100% duty-cycle PWM due to a clipped waveform. When this occurs, a signal passed to the CLIP\_OTW pin asserts it until the 100% duty-cycle PWM signal is no longer present. All four channels connect to the same CLIP\_OTW pin. Through I<sup>2</sup>C, one can change the CLIP\_OTW signal clip-only, OTW-only, or both. A fourth mode, used only during diagnostics, is the option to report tweeter detection events on this pin (see the *Tweeter Detection* section). The microcontroller in the system can monitor the signal at the CLIP\_OTW pin, and may have a configuration that reduces the volume to all four channels in an active clipping-prevention circuit.

- 5. Overtemperature Warning (OTW), Overtemperature Shutdown (OTSD) and Thermal Foldback By default, the CLIP\_OTW pin setting indicates an OTW. One can make changes via I<sup>2</sup>C commands. If selected to indicate a temperature warning, CLIP\_OTW pin assertion occurs when the die temperature reaches warning level 1 as shown in the electrical specifications. The OTW has three temperature thresholds with a 10°C hysteresis. I<sup>2</sup>C register 0x04 indicates each threshold in bits 5, 6, and 7. The device still functions until the temperature reaches the OTSD threshold, at which time the outputs go into Hi-Z mode and the device asserts the FAULT pin. I<sup>2</sup>C is still active in the event of an OTSD, and one can read the registers for faults, but all audio ceases abruptly. After the OTSD resets, one can turn the device back on through I<sup>2</sup>C. The OTW indication remains until the temperature drops below warning level 1. The thermal foldback decreases the channel gain.