Now Documents

TAS5722L

JAJSCW0A-MAY 2016-REVISED DECEMBER 2016

# TAS5722L 15Wデジタル入力、モノラルClass-Dオーディオ・アンプ

### 1 特長

- モノラルClass-Dアンプ

- 4Ω、17V、0.02% THDで連続的に15W

- 90%を超える効率のClass-D動作によりヒートシンクが不要

- オーディオ性能(PVDD = 16.5V、RSPK = 4Ω)

- アイドル・チャネル・ノイズ =  $45\mu$ VRMS (A-Wtd)

- THD+N = 0.04% (1W、1kHzのとき)

- SNR=106dB A-Wtd (THD+N = 1%を基準)

- I<sup>2</sup>S入力: 32kHz~96kHz

- TDMオーディオ入力

- 最大8チャネル(32ビット、96kHz)

- I<sup>2</sup>C制御、8個のI<sup>2</sup>Cアドレスを選択可能

- 電源

- パワー・アンプ: 4.5V~17V

- デジタルI/O: 1.8V

- 堅牢性機能

- クロック誤差検出器、DCオフセットおよび短絡保護

- 過電圧、低電圧、過熱保護

# 2 アプリケーション

- サブウーファー、ブーム・ボックス、サウンド バー、ビルディング・オートメーション

- 電源内蔵スピーカ、パーソナル・コンピュータ

- サラウンド・サウンド・システム、1チャネル・ オーディオ・システム

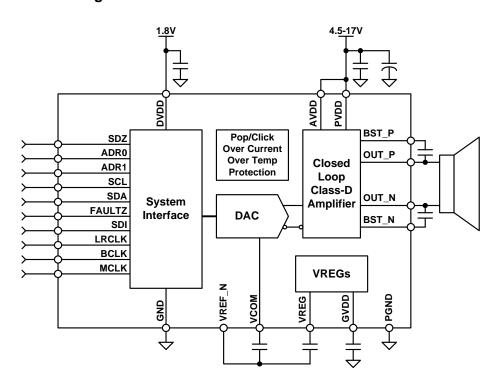

### 3 概要

TAS5722Lデバイスは高効率のモノラルClass-Dオーディオ・パワー・アンプで、デジタル出力クリッパ、複数のゲイン・オプション、広い動作電源範囲が特長です。4.5V~17VDCの公称電源電圧で動作します。

TAS5722L は、高い過渡電力耐性を持ち、小型スピーカーの動的な電力ヘッドルームを活用するよう最適化されています。4Ωスピーカーへ連続的に15W以上を供給できます。

デジタル時分割多重化(TDM)インターフェイスにより、最大8個のデバイスが同じバスを共有できます。

TAS5722Lデバイスは、4mm×4mm、32ピンのQFNパッケージで供給されます。

### 製品情報(1)

| 型番       | パッケージ    | 本体サイズ   |  |  |  |  |

|----------|----------|---------|--|--|--|--|

| TAS5722L | QFN (32) | 4mm×4mm |  |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

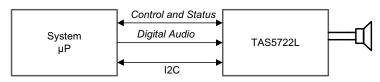

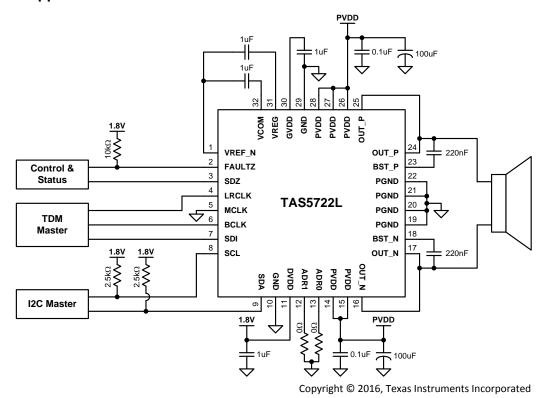

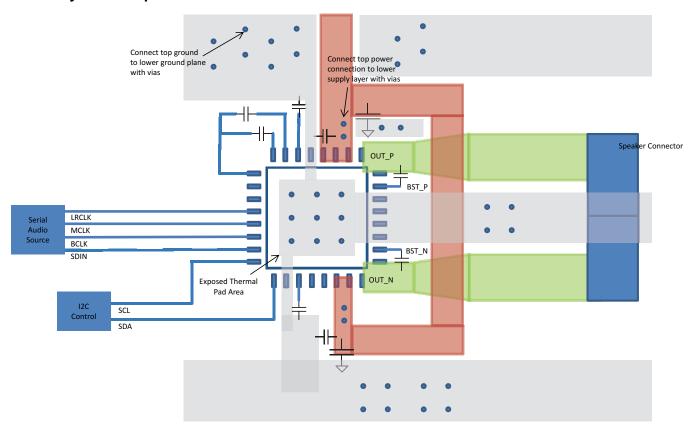

### 概略回路図

Copyright © 2016, Texas Instruments Incorporated

# 目次

| 1 | 特長1                                  |    | 7.3 Feature Description         | 17         |

|---|--------------------------------------|----|---------------------------------|------------|

| 2 | アプリケーション1                            |    | 7.4 Device Functional Modes     | <u>2</u> 9 |

| 3 | 概要1                                  |    | 7.5 Register Maps               | 31         |

| 4 | 改訂履歴2                                | 8  | Applications and Implementation | 39         |

| 5 | Pin Configuration and Functions      |    | 8.1 Application Information     | 39         |

| 6 | Specifications5                      |    | 8.2 Typical Application         | 39         |

| U | 6.1 Absolute Maximum Ratings         | 9  | Power Supply Recommendations    | 41         |

|   | 6.2 ESD Ratings                      | 10 | Layout                          |            |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines          |            |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example             |            |

|   | 6.5 Electrical Characteristics       | 11 | デバイスおよびドキュメントのサポート              |            |

|   | 6.6 Timing Requirements9             |    | 11.1 商標                         | 43         |

|   | 6.7 Typical Characteristics          |    | 11.2 静電気放電に関する注意事項              | 43         |

| 7 | Detailed Description                 |    | 11.3 用語集                        | 43         |

| • | 7.1 Overview                         | 12 | メカニカル、パッケージ、および注文情報             | 44         |

|   | 7.2 Functional Block Diagram         |    | 12.1 Package Option Addendum    |            |

|   |                                      |    |                                 |            |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 2016年5月発行のものから更新 |             |   |  |

|------------------|-------------|---|--|

| •                | 製品を量産データへ変更 | 1 |  |

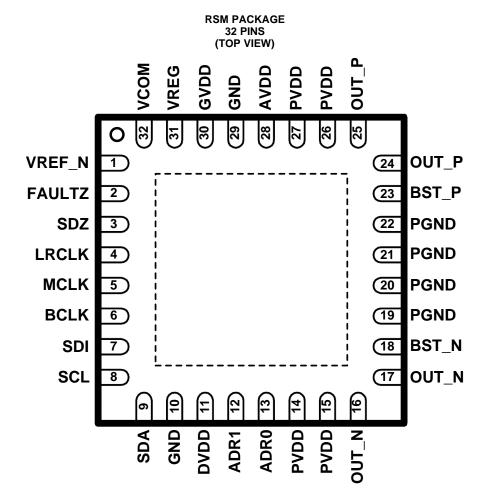

# 5 Pin Configuration and Functions

Pin Functions<sup>(1)</sup>

| PIN I/O/P <sup>(2)</sup> |     |           | DESCRIPTION                                                                                                    |  |  |  |

|--------------------------|-----|-----------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                     | NO. | I/O/F · / | JESCRIP HON                                                                                                    |  |  |  |

| ADR1                     | 12  | I         | $1^2$ C address inputs. Each pin can detect a short to DVDD, a short to GND, a 22-k $\Omega$ connection to GND |  |  |  |

| ADR0                     | 13  | I         | and a 22-k $\Omega$ connection to DVDD.                                                                        |  |  |  |

| AVDD                     | 28  | Р         | Analog power supply input. Connect directly to PVDD.                                                           |  |  |  |

| BCLK                     | 6   | I         | TDM Interface serial bit clock.                                                                                |  |  |  |

| BST_N                    | 18  | Р         | Class-D Amplifier negative bootstrap. Connect a capacitor between BST_N and OUT_N.                             |  |  |  |

| BST_P                    | 23  | Р         | Class-D Amplifier positive bootstrap. Connect a capacitor between BST_P and OUT_P.                             |  |  |  |

| DVDD                     | 11  | Р         | Digital power supply. Connect to 1.8-V supply with external decoupling capacitor.                              |  |  |  |

| FAULTZ                   | 2   | 0         | Open drain active low fault flag. Pull up on PCB with resistor to DVDD.                                        |  |  |  |

| GND                      | 10  | Р         | Ground. Connect to PCB ground plane.                                                                           |  |  |  |

| GND                      | 29  | Г         | Ground. Connect to PCB ground plane.                                                                           |  |  |  |

| GVDD                     | 30  | 0         | Class-D amplifier gate drive regulator output. Connect decoupling cap to PCB ground plane.                     |  |  |  |

| LRCLK                    | 4   | I         | TDM interface left/right clock.                                                                                |  |  |  |

| MCLK                     | 5   | I         | Device master clock.                                                                                           |  |  |  |

<sup>(1)</sup> Connect exposed thermal pad to PCB ground plane

<sup>(2)</sup> I = input, O = output, P = power, I/O = bi-directional

# Pin Functions<sup>(1)</sup> (continued)

| PI                                                                                          | N   | I/O/P <sup>(2)</sup>                                                             | DESCRIPTION                                                                             |  |  |

|---------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| NAME                                                                                        | NO. | 1/0/P(-/                                                                         | DESCRIPTION                                                                             |  |  |

|                                                                                             | 19  |                                                                                  |                                                                                         |  |  |

| PGND                                                                                        | 20  | Р                                                                                | Power ground. Connect to PCB ground plane.                                              |  |  |

| FGND                                                                                        | 21  |                                                                                  | Power ground. Connect to PCB ground plane.                                              |  |  |

|                                                                                             | 22  |                                                                                  |                                                                                         |  |  |

|                                                                                             | 14  |                                                                                  |                                                                                         |  |  |

| PVDD                                                                                        | 15  | Р                                                                                | Class-D amplifier power supply input. Connect to PVDD supply and decouple externally.   |  |  |

| I VDD                                                                                       | 26  | '                                                                                | Class-D amplifier power supply input. Conflect to 1 VDD supply and decouple externally. |  |  |

|                                                                                             | 27  |                                                                                  |                                                                                         |  |  |

| OUT_N                                                                                       | 16  | 0                                                                                | Class-D amplifier negative output.                                                      |  |  |

| 001_11                                                                                      | 17  | 0                                                                                | Class-D amplifier negative output.                                                      |  |  |

| OUT P                                                                                       | 24  | 0                                                                                | Class-D amplifier positive output.                                                      |  |  |

| 001_1                                                                                       | 25  |                                                                                  | Olass D amplinor positive output.                                                       |  |  |

| SCL                                                                                         | 8   | I                                                                                | $I^2$ C clock Input. Pull up on PCB with a 2.4-k $\Omega$ resistor.                     |  |  |

| SDA                                                                                         | 9   | I/O                                                                              | l <sup>2</sup> C bi-directional data. Pull up on PCB with a 2.4-kΩ resistor.            |  |  |

| SDI                                                                                         | 7   | I                                                                                | TDM interface data input.                                                               |  |  |

| SDZ 3 I Active low shutdown signal. Assert low to hold device inactive.                     |     | Active low shutdown signal. Assert low to hold device inactive.                  |                                                                                         |  |  |

| VCOM                                                                                        | 32  | 0                                                                                | Common mode reference output. Connect decoupling capacitor to the VREF_N pin.           |  |  |

| VREF_N 1 P Negative reference for analog. Connect to VCOM and VREG capacitor negative pins. |     | Negative reference for analog. Connect to VCOM and VREG capacitor negative pins. |                                                                                         |  |  |

| VREG                                                                                        | 31  | 0                                                                                | Analog regulator output. Connect decoupling capacitor to the VREF_N pin.                |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                               |                                          | MIN  | MAX                     | UNIT |

|------------------|-------------------------------|------------------------------------------|------|-------------------------|------|

| V <sub>CC</sub>  | Supply voltage <sup>(2)</sup> | PVDD, AVDD                               | -0.3 | 20                      | V    |

|                  | Supply voltage 7              | DVDD                                     | -0.3 | 2.25                    |      |

|                  | Digital input voltage         | Digital inputs referenced to DVDD supply | -0.5 | V <sub>DVDD</sub> + 0.5 | V    |

| T <sub>A</sub>   | Ambient operating temperature |                                          | -25  | 85                      | °C   |

| T <sub>stg</sub> | Storage temperature range     | prage temperature range                  |      | 125                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±750  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                  | MIN  | TYP        | MAX | UNIT |

|------------------|----------------------------------|------|------------|-----|------|

| PVDD<br>AVDD     | Power supply voltage             | 4.5  |            | 17  | V    |

| DVDD             | Power supply voltage             | 1.65 | 1.8        | 2   | V    |

| $V_{IH(DR)}$     | High-level digital input voltage |      | $V_{DVDD}$ |     | V    |

| $V_{IL(DR)}$     | Low-level digital input voltage  |      | 0          |     | V    |

| R <sub>SPK</sub> | Minimum speaker load             | 3.2  |            |     | Ω    |

| T <sub>A</sub>   | Operating free-air temperature   | -25  |            | 85  | °C   |

| $T_{J}$          | Operating junction temperature   | -25  |            | 150 | °C   |

<sup>(2)</sup> All voltages are with respect to network ground pin.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Thermal Information

|                    |                                                           | TAS5722L  |       |

|--------------------|-----------------------------------------------------------|-----------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                             | RSM (QFN) | UNIT  |

|                    |                                                           | 32 PINS   |       |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance (2)                | 37.3      |       |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance <sup>(3)</sup>  | 30.4      |       |

| $R_{\theta JB}$    | Junction-to-board thermal resistance (4)                  | 7.9       | °C/M/ |

| ΨЈТ                | Junction-to-top characterization parameter <sup>(5)</sup> | 0.4       | °C/W  |

| ΨЈВ                | Junction-to-board characterization parameter (6)          | 7.7       |       |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance (7)          | 2.5       |       |

- (1) 従来および新しい熱測定値の詳細については、『Semiconductor and IC Package Thermal Metrics』アプリケーション・レポート (SPRA953)を参照してください。

- 自然対流における、接合部と周囲の空気との間の熱抵抗は、JESD51-2aに記述されている環境において、JESD51-7で規定されている JEDEC標準のHigh-Kボード上でのシミュレーションによって求められます。

- (3) 接合部とケース(上面)との間の熱抵抗は、パッケージ上面での冷却板試験のシミュレーションによって求められます。JEDEC規格試験 では規定されていませんが、ANSIが策定したSEMI規格のG30-88に類似した記述があります。

- (4) 接合部と基板との間の熱抵抗は JESD51-8で説明されているように、PCB温度を制御するリング型冷却板冶具で環境をシミュレーショ ンすることにより求められます。

- (5) 接合部とケース上部との間の特性パラメータ $\psi_{JT}$ は、実際のシステムにおけるデバイスの接合部温度を推定するもので、JESD51-2a (セクション6および7)に記述されている手順を用いて、 $R_{0JA}$ を求めるためのシミュレーションデータから抽出されます。 (6) 接合部と基板との間の特性パラメータ $\psi_{JB}$ は、実際のシステムにおけるデバイスの接合部温度を推定するもので、JESD51-2a (セクショ

- ン6および7)に記述されている手順を用いて、 $R_{ exttt{ hetaJA}}$ を求めるためのシミュレーションデータから抽出されます。

- 接合部とケース(底面)との間の熱抵抗は、露出したパッド(Power PAD)上での冷却板試験のシミュレーションによって求められます。 JEDEC規格試験では規定されていませんが、ANSIが策定したSEMI規格のG30-88に類似した内容があります。

## 6.5 Electrical Characteristics

$V_{PVDD}$  = 16.5 V,  $V_{DVDD}$  = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{PWM}$  = 576 kHz, 22-Hz to 20- kHz Bandwidth, AP AUX-0025 + AES17 Filter (unless otherwise noted)

|                         | PARAMETER                                                 | CONDITIONS                                        | MIN  | TYP | MAX            | UNIT |

|-------------------------|-----------------------------------------------------------|---------------------------------------------------|------|-----|----------------|------|

| DIGITAL INP             | UT AND OUTPUT                                             |                                                   |      |     |                |      |

| $V_{\text{IH}}$         | High-level digital input logic voltage threshold          | All digital pins                                  | 70%  |     |                |      |

| V <sub>IL</sub>         | Low-level digital input logic voltage threshold           | All digital pins                                  |      |     | 30%            |      |

| I <sub>IH</sub>         | Input logic "high" leakage for digital inputs             | All digital pins, excluding SDZ                   |      |     | 15             | μΑ   |

| I <sub>IL</sub>         | Input logic "low" leakage for digital inputs              | All digital pins, excluding SDZ                   |      |     | -15            | μΑ   |

| I <sub>IH(SDZ)</sub>    | Input logic "high" leakage for SDZ inputs                 | SDZ                                               |      |     | 1              | μΑ   |

| I <sub>IL(SDZ)</sub>    | Input logic "low" leakage for SDZ inputs                  | SDZ                                               |      |     | -1             | μΑ   |

| V <sub>OL</sub>         | Output logic "low" for FAULTZ open drain Output           | I <sub>OL</sub> = −2 mA                           |      |     | $V_{\rm DVDD}$ |      |

| C <sub>IN</sub>         | Input capacitance for digital inputs                      | All digital pins                                  |      | 5   |                | pF   |

| MASTER CLO              | эск                                                       |                                                   |      |     |                |      |

| D <sub>MCLK</sub>       | Allowable MCLK duty cycle                                 |                                                   | 45%  | 50% | 55%            |      |

|                         | MCLK input frequency                                      |                                                   |      |     | 25             | MHz  |

| f <sub>MCLK</sub>       | Supported single-speed MCLK frequencies                   | values: 64, 128, 256 and 512                      | 2.8  |     | 24.6           | MHz  |

|                         | Supported double-speed MCLK frequencies                   | values: 64, 128 and 256                           | 5.6  |     | 24.6           | MHz  |

| SERIAL AUD              | IO PORT                                                   |                                                   |      |     |                |      |

| $D_{BCLK}$              | Allowable BCLK duty cycle                                 |                                                   | 45%  | 50% | 55%            |      |

|                         | BCLK input frequency                                      |                                                   |      |     | 25             | MHz  |

| f <sub>BCLK</sub>       | Supported single-speed BCLK frequencies                   | values: 64, 96, 128, 192 and 256                  | 2.8  |     | 12.3           | MHz  |

|                         | Supported double-speed BCLK frequencies                   | values: 64, 96, 128, 192 and 256                  | 5.6  |     | 24.6           | MHz  |

| £                       | Supported single-speed input sample rates                 | values: 44.1 and 48                               | 44.1 |     | 48             | kHz  |

| f <sub>S</sub>          | Supported double-speed input sample rates                 | values: 88.2 and 96                               | 88.2 |     | 96             | kHz  |

| I <sup>2</sup> C CONTRO | L PORT                                                    |                                                   |      |     |                |      |

| C <sub>L(I2C)</sub>     | Allowable load capacitance for each I <sup>2</sup> C Line |                                                   |      |     | 400            | pF   |

| f <sub>SCL</sub>        | SCL frequency                                             | No wait states                                    |      |     | 400            | kHz  |

| PROTECTION              | N                                                         | -                                                 |      |     |                |      |

| OTE <sub>THRESH</sub>   | Over-temperature error (OTE) threshold                    |                                                   |      | 150 |                | °C   |

| OTE <sub>HYST</sub>     | Over-temperature error (OTE) hysteresis                   |                                                   |      | 15  |                | °C   |

| OCE <sub>THRESH</sub>   | overcurrent error (OCE) threshold                         | V <sub>PVDD</sub> = 16.5 V, T <sub>A</sub> = 25°C |      | 5   |                | Α    |

| DCE <sub>THRESH</sub>   | DC error (DCE) threshold                                  | V <sub>PVDD</sub> = 16.5V, TA = 25°C              |      | 2.6 |                | V    |

## **Electrical Characteristics (continued)**

$V_{PVDD}$  = 16.5 V,  $V_{DVDD}$  = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{PWM}$  = 576 kHz, 22-Hz to 20- kHz Bandwidth, AP AUX-0025 + AES17 Filter (unless otherwise noted)

|                        | PARAMETER                      | CONDITIONS                                                                                                                                                                        | MIN TYP             | MAX   | UNIT  |

|------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|-------|

| AMPLIFIER              | PERFORMANCE                    |                                                                                                                                                                                   |                     |       |       |

|                        |                                | $R_L$ = 8 $\Omega$ +33 $\mu$ H, 1% THD+N, $V_{PVDD}$ = 12 V, $f_{IN}$ = 1 kHz                                                                                                     | 8.2                 |       |       |

| P <sub>OUT</sub>       | Continuous average power       | $R_L$ = 8 $\Omega + 33~\mu H,~1\%$ THD+N, $V_{PVDD}$ = 16.5 V, $f_{IN}$ = 1 kHz                                                                                                   | 15.25               |       | W     |

| 1 001                  | Continuous average power       | $R_L$ = 4 $\Omega + 33~\mu H,~1\%$ THD+N, $V_{PVDD}$ = 12 V, $f_{IN}$ = 1 kHz                                                                                                     | 14.25               |       | VV    |

|                        |                                | $R_{L} = 4~\Omega + 33~\mu H,~1\%~THD + N,~V_{PVDD} = 16.5~V, \\ f_{IN} = 1~kHz$                                                                                                  | 16                  |       |       |

|                        |                                | R <sub>L</sub> = 8 $\Omega$ +33 $\mu$ H, V <sub>PVDD</sub> = 12 V, P <sub>OUT</sub> = 4.25 W, 20 Hz $\leq$ f <sub>IN</sub> $\leq$ 20 kHz                                          | 0.05%               |       |       |

| THD+N                  | Total harmonic distortion plus | $R_L$ = 8 Ω+33 μH, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 4.25 W, 20 Hz ≤ $f_{IN}$ ≤ 20 kHz                                                                                             | 0.05%               |       |       |

| THEFIN                 | noise                          | $R_L$ = 4 Ω+33 μH, $V_{PVDD}$ = 12 V, $P_{OUT}$ = 8.25 W, 20 Hz ≤ $f_{IN}$ ≤ 20 kHz                                                                                               | 0.05%               |       |       |

|                        |                                | $R_L$ = 4 Ω+33 μH, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 8.25 W, 20 Hz ≤ $f_{IN}$ ≤ 20 kHz                                                                                             | 0.06%               |       |       |

| D                      | Power efficiency               | $R_L$ = 8 $\Omega$ +33 $\mu$ H, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 10 W                                                                                                             | 90%                 |       |       |

| P <sub>EFF</sub>       | Fower emciency                 | $R_L$ = 4 Ω+33 μH, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 14 W                                                                                                                          | 87%                 |       |       |

| $V_N$                  | Integrated noise floor voltage | A-Weighted, Gain = 20.7dBV, $R_L$ = 8 $\Omega$ +33 $\mu H$                                                                                                                        | 50                  |       | μVrms |

| KCP                    | Click-pop performance          | Into and out of HW reset, into and out of SW shutdown, when SAIF clocks are applied or removed and during power rail cycling.  Measured using Maxim click-pop measurement method. | -60                 |       | dB    |

| Фсс                    | Channel-to-channel phase shift | Output phase shift between multiple devices from 20 Hz to 20 kHz. Across all sample frequencies and SAIF operating modes.                                                         | 0.2                 |       | deg   |

|                        |                                | AC, $5.5 \text{ V} \le \text{V}_{\text{PVDD}} \le 16.5 \text{ V}$ , DVDD = 1.8 V+200 mV <sub>P-P</sub> , f <sub>RIPPLE</sub> from 20 Hz to 20 kHz                                 | 69                  |       |       |

| PSRR                   | Power supply rejection ratio   | AC, $V_{PVDD}$ = 16.5 V+200 mV <sub>P-P</sub> , $f_{RIPPLE}$ from 20 Hz to 5 kHz                                                                                                  | 64                  |       | dB    |

|                        |                                | AC, $V_{PVDD}$ = 16.5 V+100 mV <sub>P-P</sub> , $f_{RIPPLE}$ from 5 kHz to 20 kHz                                                                                                 | 60                  |       |       |

| $AV_{00}$              |                                | ANALOG_GAIN[1:0] register bits set to "00"                                                                                                                                        | 19.2                |       | dBV   |

| AV <sub>01</sub>       | Amplifier analog gain (1)      | ANALOG_GAIN[1:0] register bits set to "01"                                                                                                                                        | 20.7                |       | dBV   |

| AV <sub>10</sub>       | Amplifier analog gain          | ANALOG_GAIN[1:0] register bits set to "10"                                                                                                                                        | 23.5                |       | dBV   |

| AV <sub>11</sub>       |                                | ANALOG_GAIN[1:0] register bits set to "11"                                                                                                                                        | 26.3                |       | dBV   |

| AV <sub>ERROR</sub>    | Amplifier analog gain error    |                                                                                                                                                                                   |                     | ±0.15 | dB    |

| Vos                    | DC output offset voltage       | Measured between OUTP and OUTN                                                                                                                                                    | 1.5                 |       | mV    |

| A <sub>RIPPLE</sub>    | Frequency response             | Maximum deviation above or below passband gain.                                                                                                                                   | ±0.15               |       | dB    |

| $f_{LP}$               | -3 dB Output Cutoff Frequency  |                                                                                                                                                                                   | 0.47×f <sub>S</sub> |       | Hz    |

| R <sub>DS(on)FET</sub> | Power stage FET on-resistance  | T <sub>A</sub> = 25°C                                                                                                                                                             | 120                 |       | mΩ    |

<sup>(1)</sup> When PVDD is less than 5.5 V, the voltage regulator that operates the analog circuitry does not have enough headroom to maintain the nominal 5.4-V internal voltage. The lack of headroom causes a direct reduction in gain (approximately –0.8 dB at 5 V and –1.74 dB at 4.5 V), but the device functions properly down to V<sub>PVDD</sub> = 4.5 V. For operation below 5.5V, the VREG\_LVL bit (register 0x14, bit 2) can be set high, which reduces the internal voltage regulator output voltage to prevent variation in gain. When the bit is set high, all gain settings are reduced by 3dB.

# **Electrical Characteristics (continued)**

$V_{PVDD}$  = 16.5 V,  $V_{DVDD}$  = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{PWM}$  = 576 kHz, 22-Hz to 20- kHz Bandwidth, AP AUX-0025 + AES17 Filter (unless otherwise noted)

| PARAMETER              |                                                    | CONDITIONS                              | MIN | TYP | MAX | UNIT |

|------------------------|----------------------------------------------------|-----------------------------------------|-----|-----|-----|------|

| R <sub>DS(on)TOT</sub> | Power stage total on-resistance (FET+bond+package) | T <sub>A</sub> = 25°C                   |     | 150 |     | mΩ   |

| I <sub>P-P</sub>       | Peak output current                                | T <sub>A</sub> = 25°C                   |     | 5   |     | Α    |

| $f_{PWM}$              | PWM switching frequency                            | values: 6, 8, 10, 12, 14, 16, 20 and 24 | 6   |     | 24  | MHz  |

# 6.6 Timing Requirements

|                     | -                       |                                                                                                                    | MIN | NOM                  | MAX | UNIT |

|---------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|-----|----------------------|-----|------|

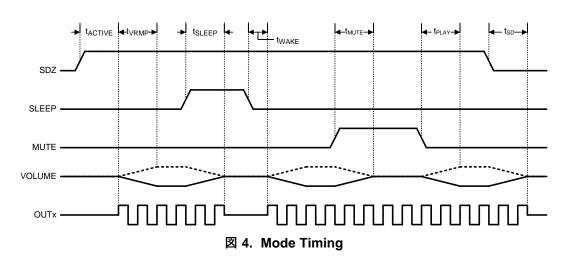

| t <sub>ACTIVE</sub> | Shutdown to Active Time | From deassertion of SDZ (both pin and I <sup>2</sup> C register bit) until the Class-D amplifier begins switching. |     | 25                   |     | ms   |

| t <sub>WAKE</sub>   | Wake Time               | From the deassertion of SLEEP until the Class-D amplifier starts switching.                                        |     | 1                    |     | ms   |

| t <sub>SLEEP</sub>  | Sleep Time              | From the assertion of SLEEP until the Class-D amplifier stops switching.                                           |     | t <sub>vrmp</sub> +1 |     | ms   |

| t <sub>MUTE</sub>   | Play to Mute Time       | From the assertion of MUTE until the volume has ramped to the minimum.                                             |     | $t_{\text{vrmp}}$    |     | ms   |

| t <sub>PLAY</sub>   | Un-Mute to Play Time    | From the deassertion of MUTE until the volume has returned to its current setting.                                 |     | $t_{\rm vrmp}$       |     | ms   |

| t <sub>SD</sub>     | Active to Shutdown Time | From the assertion of SDZ (pin or I <sup>2</sup> C register bit) until the Class-D amplifier stops switching.      |     | t <sub>vrmp</sub> +1 |     | ms   |

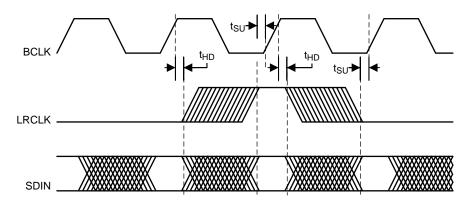

# **Timing Requirements (continued)**

|                                    |                                                     |                                                                | MIN | NOM | MAX | UNIT |

|------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|-----|-----|-----|------|

| SERIAL AU                          | DIO PORT                                            |                                                                |     |     |     |      |

| t <sub>H_L</sub>                   | Time High/Low, BCLK, LRCLK, SDI inputs              |                                                                | 10  |     |     | ns   |

|                                    |                                                     | Input t <sub>RISE</sub> ≤ 1 ns, input t <sub>FALL</sub> ≤ 1 ns | 5   |     |     |      |

| t <sub>SU</sub> / t <sub>HLD</sub> | Setup and hold time. LRCLK, SDI input to BCLK edge. | Input t <sub>RISE</sub> ≤ 4 ns, input t <sub>FALL</sub> ≤ 4ns  | 8   |     |     | ns   |

|                                    | input to Bolik edge.                                | Input t <sub>RISE</sub> ≤ 8 ns, input t <sub>FALL</sub> ≤ 8ns  | 12  |     |     |      |

| t <sub>RISE</sub>                  | Rise-time BCLK, LRCLK, SDI inputs                   |                                                                |     |     | 8   | ns   |

| t <sub>FALL</sub>                  | Fall-time BCLK, LRCLK, SDI inputs                   |                                                                |     |     | 8   | ns   |

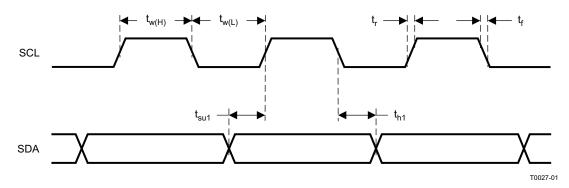

| I <sup>2</sup> C CONTRO            | OL PORT                                             |                                                                |     |     | •   |      |

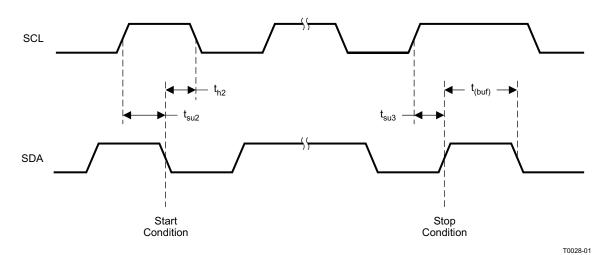

| t <sub>BUF</sub>                   | Bus free time between start and stop conditions     |                                                                | 1.3 |     |     | μs   |

| t <sub>H1(I2C)</sub>               | Hold Time, SCL to SDA                               |                                                                | 0   |     |     | ns   |

| t <sub>H2(I2C)</sub>               | Hold Time, start condition to SCL                   |                                                                | 0.6 |     |     | μs   |

| t <sub>START(I2C)</sub>            | I2C Startup Time after DVDD Power On Reset          |                                                                |     |     | 12  | ms   |

| t <sub>R(I2C)</sub>                | Rise Time, SCL and SDA                              |                                                                |     |     | 300 | ns   |

| t <sub>F(I2C)</sub>                | Fall Time, SCL and SDA                              |                                                                |     |     | 300 | ns   |

| t <sub>SU1(I2C)</sub>              | Setup, SDA to SCL                                   |                                                                | 100 |     |     | ns   |

| t <sub>SU2(I2C)</sub>              | Setup, SCL to start condition                       |                                                                | 0.6 |     |     | μs   |

| t <sub>SU3(I2C)</sub>              | Setup, SCL to stop condition                        |                                                                | 0.6 |     |     | μs   |

| $t_{\text{W(H)}}$                  | Required pulse duration, SCL "HIGH"                 |                                                                | 0.6 |     |     | μs   |

| t <sub>W(L)</sub>                  | Required pulse duration, SCL "LOW"                  |                                                                | 1.3 |     |     | μs   |

| PROTECTIO                          | ON                                                  |                                                                | •   |     | '   |      |

|                                    | A samilifier facultations and marks                 | DC detect error                                                |     | 650 |     | ms   |

| t <sub>FAULTZ</sub>                | Amplifier fault time-out period                     | OTE or OCE fault                                               |     | 1.3 |     | S    |

|                                    |                                                     |                                                                |     |     |     |      |

図 1. SAIF Timing

図 2. SCL and SDA Timing

図 3. Start and Stop Conditions Timing

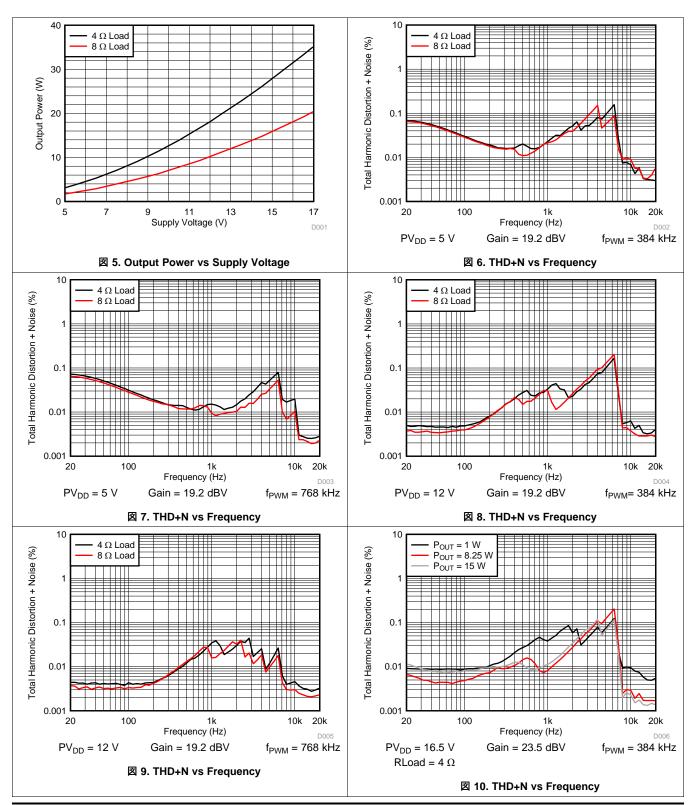

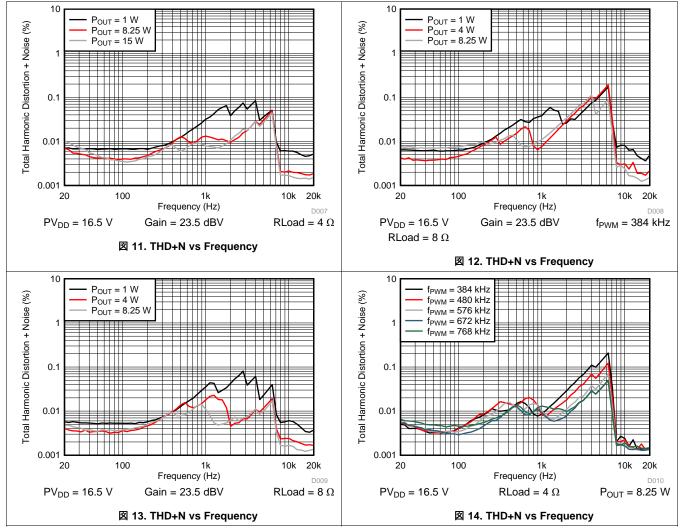

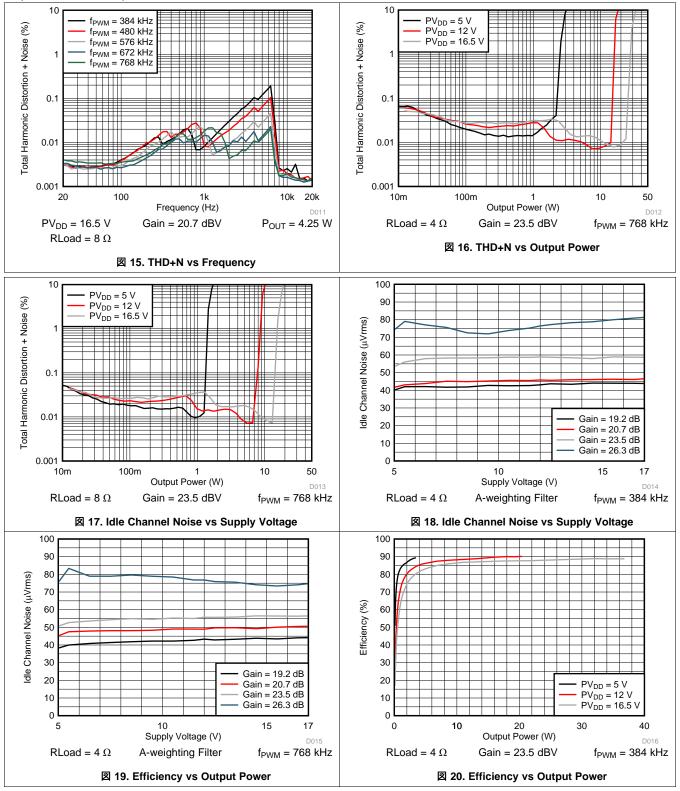

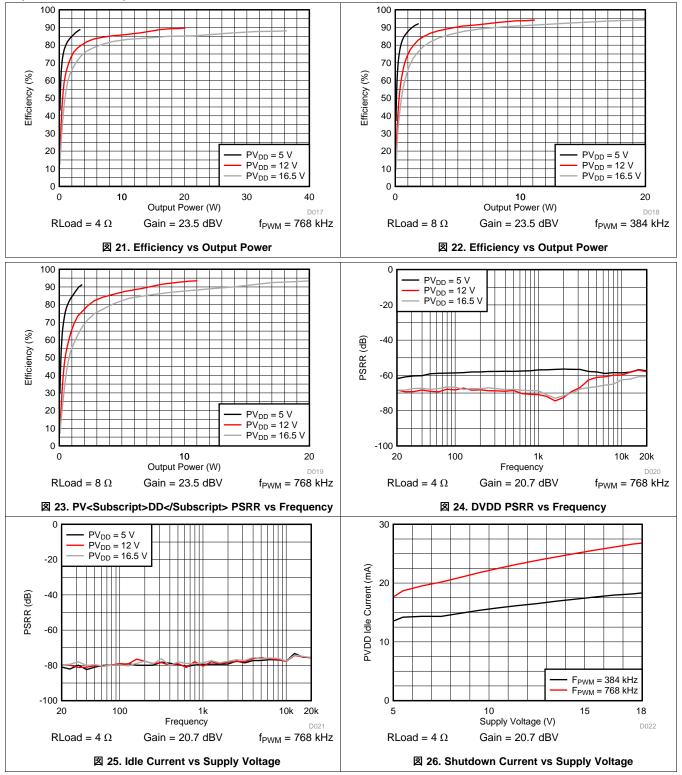

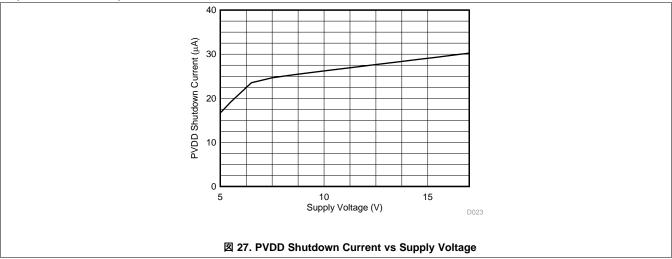

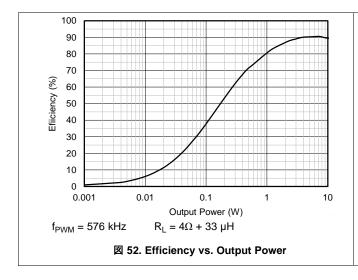

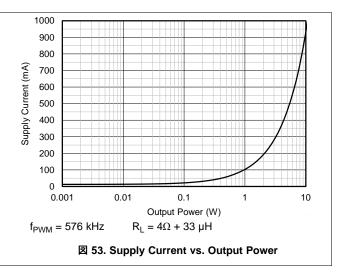

## 6.7 Typical Characteristics

$T_A$  = 25°C,  $V_{DVDD}$  = 1.8 V,  $f_{IN}$  = 1 kHz,  $f_{PWM}$  768 kHz,  $f_s$  = 48 kHz, Gain = 20.7 dBV, SDZ = 1, Measured using TAS5722LEVM with an Audio Precision SYS-2722 and AUX-0025 filter with 22-Hz-to-20- kHz un-weighted bandwidth using the 20- kHz pre-analyzer filter + 20- kHz brick-wall filter (unless otherwise specified). 33  $\mu$ H inductors were added in series with 4  $\Omega$  loads and 68  $\mu$ H inductors were placed in series with 8  $\Omega$  loads due to the ferrite bead filters.

$T_A$  = 25°C,  $V_{DVDD}$  = 1.8 V,  $f_{IN}$  = 1 kHz,  $f_{PWM}$  768 kHz,  $f_s$  = 48 kHz, Gain = 20.7 dBV, SDZ = 1, Measured using TAS5722LEVM with an Audio Precision SYS-2722 and AUX-0025 filter with 22-Hz-to-20- kHz un-weighted bandwidth using the 20- kHz pre-analyzer filter + 20- kHz brick-wall filter (unless otherwise specified). 33  $\mu$ H inductors were added in series with 4  $\Omega$  loads and 68  $\mu$ H inductors were placed in series with 8  $\Omega$  loads due to the ferrite bead filters.

$T_A = 25^{\circ}C$ ,  $V_{DVDD} = 1.8$  V,  $f_{IN} = 1$  kHz,  $f_{PWM}$  768 kHz,  $f_s = 48$  kHz, Gain = 20.7 dBV, SDZ = 1, Measured using TAS5722LEVM with an Audio Precision SYS-2722 and AUX-0025 filter with 22-Hz-to-20- kHz un-weighted bandwidth using the 20- kHz pre-analyzer filter + 20- kHz brick-wall filter (unless otherwise specified). 33  $\mu$ H inductors were added in series with 4  $\Omega$  loads and 68  $\mu$ H inductors were placed in series with 8  $\Omega$  loads due to the ferrite bead filters.

$T_A$  = 25°C,  $V_{DVDD}$  = 1.8 V,  $f_{IN}$  = 1 kHz,  $f_{PWM}$  768 kHz,  $f_s$  = 48 kHz, Gain = 20.7 dBV, SDZ = 1, Measured using TAS5722LEVM with an Audio Precision SYS-2722 and AUX-0025 filter with 22-Hz-to-20- kHz un-weighted bandwidth using the 20- kHz pre-analyzer filter + 20- kHz brick-wall filter (unless otherwise specified). 33  $\mu$ H inductors were added in series with 4  $\Omega$  loads and 68  $\mu$ H inductors were placed in series with 8  $\Omega$  loads due to the ferrite bead filters.

$T_A$  = 25°C,  $V_{DVDD}$  = 1.8 V,  $f_{IN}$  = 1 kHz,  $f_{PWM}$  768 kHz,  $f_s$  = 48 kHz, Gain = 20.7 dBV, SDZ = 1, Measured using TAS5722LEVM with an Audio Precision SYS-2722 and AUX-0025 filter with 22-Hz-to-20- kHz un-weighted bandwidth using the 20- kHz pre-analyzer filter + 20- kHz brick-wall filter (unless otherwise specified). 33  $\mu$ H inductors were added in series with 4  $\Omega$  loads and 68  $\mu$ H inductors were placed in series with 8  $\Omega$  loads due to the ferrite bead filters.

## 7 Detailed Description

#### 7.1 Overview

The TAS5722L device is a high-efficiency mono Class-D audio power amplifier optimized for high-transient power capability to utilize the dynamic power headroom of small loudspeakers. The TAS5722L device is capable of delivering more than 14 W continuously into a  $4-\Omega$  speaker.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

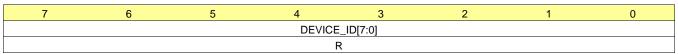

### 7.3.1 Adjustable I<sup>2</sup>C Address

The TAS5722L device has two address pins, which allow up to 8  $I^2C$  addressable devices to share a common TDM bus.  $\frac{1}{8}$  1 lists each  $I^2C$  Device ID setting.

注

The I<sup>2</sup>C Device ID is the 7 most significant bits of the 8-bit address transaction on the bus (with the read/write bit being the least significant bit). For example, a Device ID of 0x6C would be read as 0xD8 when the read/write bit is 0.

| 表 1. I <sup>*</sup> C Device Id | entifier (ID) Generation |

|---------------------------------|--------------------------|

|---------------------------------|--------------------------|

| ADR1         | ADR0                 | I2C_DEV_ID | DEFAULT TDM<br>SLOT |

|--------------|----------------------|------------|---------------------|

|              | Short to GND         | 0x6C       | 0                   |

| Short to GND | 22-k $\Omega$ to GND | 0x6D       | 1                   |

|              | 22-kΩ to DVDD        | 0x6E       | 2                   |

|              | Short to DVDD        | 0x6F       | 3                   |

| 表 1. I <sup>2</sup> C Device Identifi | r (ID) | Generation ( | (continued) | ) |

|---------------------------------------|--------|--------------|-------------|---|

|---------------------------------------|--------|--------------|-------------|---|

| ADR1         | ADR0                  | I2C_DEV_ID | DEFAULT TDM<br>SLOT |

|--------------|-----------------------|------------|---------------------|

| 22-kΩ to GND | Short to GND          | 0x70       | 4                   |

|              | 22-k $\Omega$ to GND  | 0x71       | 5                   |

|              | 22-k $\Omega$ to DVDD | 0x72       | 6                   |

|              | Short to DVDD         | 0x73       | 7                   |

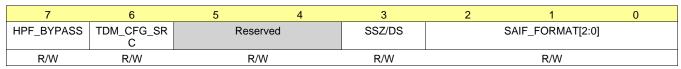

Use a 22-k $\Omega$  resistor with a 5% (or better) tolerance as a pull-up or pull-down resistor. By default, the device uses the TDM time slot equal to its offset from the base I<sup>2</sup>C Device ID (see  $\frac{1}{8}$  1). The TDM slot can also be manually configured by setting the TDM\_CFG\_SRC bit high (bit 6, reg 0x02) and programming the TDM SLOT SELECT[3:0] bits to the desired slot (bits 0-3, reg 0x03).

For 2-channel, I<sup>2</sup>S operation, TDM slot 0 and 1 correspond to the right and left channels respectively. For left and right justified formats, TDM slot 0 and 1 correspond to left and right channels respectively.

#### 7.3.2 I<sup>2</sup>C Interface

The TAS5722L device has a bidirectional I<sup>2</sup>C interface that is compatible with the Inter-Integrated Circuit (I<sup>2</sup>C) bus protocol and supports both 100 kHz and 400 kHz data transfer rates. The slave-only device does not support a multi-master bus environment or wait-state insertion. The control interface is used to program the registers of the device and to read device status.

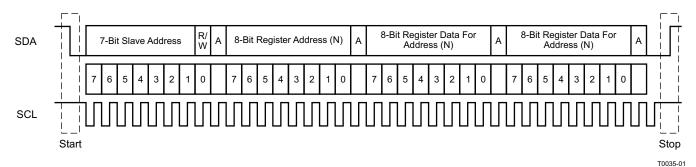

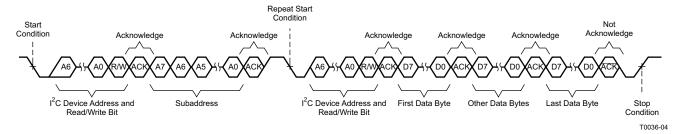

The I²C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially, one bit at a time. The address and data can be transferred in byte (8-bit) format, with the most-significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data pin (SDA) while the clock (SCL) is "HIGH" to indicate start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period. These conditions are shown in 22. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The TAS5722L device holds SDA "LOW" during the acknowledge clock period to indicate an acknowledgment. When the hold occurs, the master transmits the next byte of the sequence. All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pull-up resistor must be used for the SDA and SCL signals to set the "HIGH" level for the bus.

図 28. Typical I<sup>2</sup>C Timing Sequence

The number of bytes that can be transmitted between start and stop conditions is unlimited. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in 28.

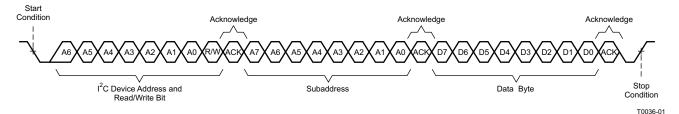

### 7.3.2.1 Writing to the $f^2$ C Interface

As shown 29, a single-byte data-write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C bit and the read/write bit. The read/write bit determines the direction of the data transfer. For a data-write transfer, the read/write bit is a 0. After receiving the correct I<sup>2</sup>C bit and the read/write bit, the TAS5722L device responds with an acknowledge bit. Next, the master transmits the address byte corresponding to the TAS5722L device register being accessed. After receiving the address byte, the TAS5722L device again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte, the TAS5722L device again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data-write transfer.

図 29. Single Byte Write Transfer Timing

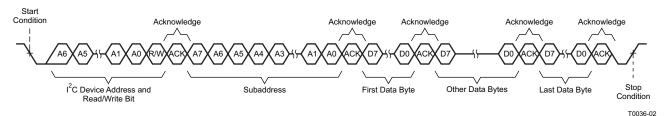

A multi-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted as shown in 30. After receiving each data byte, the TAS5722L device responds with an acknowledge bit. Sequential data bytes are written to sequential addresses.

図 30. Multi-Byte Write Transfer Timing

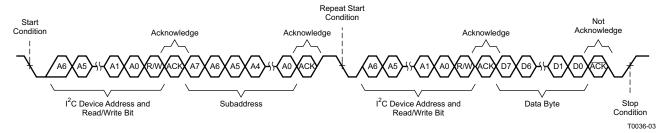

### 7.3.2.2 Reading from the $^{\rho}$ C Interface

As shown in 30, a data-read transfer begins with the master device transmitting a start condition, followed by the I² device address and the read/write bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte of the internal register to be read. As a result, the read/write bit becomes a 0. After receiving the TAS5722L device address and the read/write bit, TAS5722L device responds with an acknowledge bit. In addition, after sending the internal memory address byte or bytes, the master device transmits another start condition followed by the TAS5722L device address and the read/write bit again. Then the read/write bit becomes a 1, indicating a read transfer. After receiving the address and the read/write bit, the TAS5722L device again responds with an acknowledge bit. Next, the TAS5722L device transmits the data byte from the register being read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the data-read transfer.

図 31. Single Byte Read Transfer Timing

A multiple-byte data read transfer is identical to a single-byte data read transfer except that multiple data bytes are transmitted by the TAS5722L to the master device as shown 32. Except for the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

図 32. Multi-Byte Read Transfer Timing

### 7.3.3 Serial Audio Interface (SAIF)

The TAS5722L device SAIF supports a variety of standard stereo serial audio formats including I<sup>2</sup>S, Left Justified and Right Justified. It also supports a time division multiplexed (TDM) format that is capable of transporting up to 8 channels of audio data on a single bus. LRCLK and SDIN are sampled on the rising edge of BCLK.

For the stereo formats (I<sup>2</sup>S, Left Justified and Right Justified), the TAS5722L device supports BCLK to LRCLK ratios of 32, 48 and 64. If the BCLK to LRCLK ratio is 64, MCLK can be derived from BCLK internally. The MCLK\_PIN\_CFG bit (register 0x13, bit 1) controls the source of MCLK and by default derives MCLK from an internal version of BCLK. In this case connect the MCLK pin to a valid logic low value.

If the BCLK to LRCLK ratio is 32 or 48, MCLK must be externally driven. The valid MCLK to LRCLK ratios are 64, 128, 256 and 512 as long as the frequency of MCLK is 37 MHz or less. If the BCLK to LRCLK ratio is 64, it is also acceptable to connect BCLK to MCLK and set the MCLK\_PIN\_CFG bit high.

For TDM operation, the TAS5722L device supports 4 and 8 times slots at both single speed (44.1 kHz or 48 kHz) and double speed (88.2/96 kHz) sample rates. 表 2 lists the supported TDM frame configurations. For 16 and 32-bits per TDM slot, MCLK can be connected to BCLK internally by leaving the MCLK\_PIN\_CFG bit (register 0x13, bit 1) to its default value of 0. For 24-bit time slot operation, MCLK must be externally driven with a valid ratio of 64, 128, 256 or 512 as long as MCLK is less than 37 MHz.

|                         |              |                            |           | 3           |              |

|-------------------------|--------------|----------------------------|-----------|-------------|--------------|

| SAMPLE<br>RATE<br>(kHz) | TDM<br>SLOTS | BITS<br>PER<br>TDM<br>SLOT | SUPPORTED | MCLK = BCLK | TDM_SLOT_16B |

|                         |              | 16                         | Yes       | Yes         | 1            |

|                         | 4            | 24                         | Yes       | No          | 0            |

| 44.4/40                 |              | 32                         | Yes       | Yes         | 0            |

| 44.1/48                 |              | 16                         | Yes       | Yes         | 1            |

|                         | 8            | 24                         | Yes       | No          | 0            |

|                         |              | 32                         | Yes       | Yes         | 0            |

|                         |              | 16                         | Yes       | Yes         | 1            |

|                         | 4            | 24                         | Yes       | No          | 0            |

| 00.0/00                 |              | 32                         | Yes       | Yes         | 0            |

| 88.2/96                 |              | 16                         | Yes       | Yes         | 1            |

|                         | 8            | 24                         | Yes       | No          | 0            |

|                         |              | 32                         | Yes       | Yes         | 0            |

表 2. TDM Frame Configurations

If 16-bit time slots are utilized, set the TDM\_SLOT\_16B register bit (register 0x13, bit 2) to a 1. The SAIF auto detects 24-bit vs. 32-bit time slot widths if TDM\_SLOT\_16B is set to a 0.

The TAS5722L device selects the channel for playback based on either its  $I^2C$  base address offset or based on a dedicated time slot selection register. See the *Adjustable f^2C Address* section for more information.

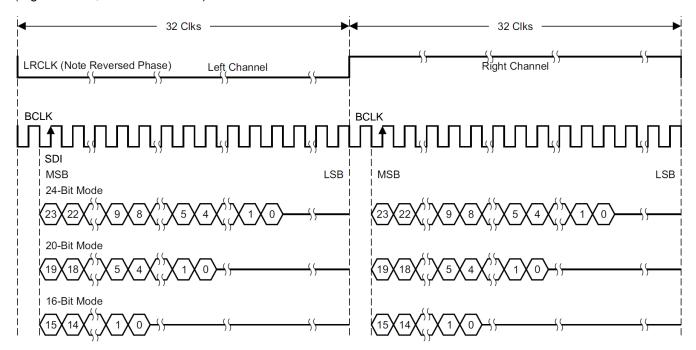

# 7.3.3.1 Stereo PS Format Timing

illustrates the timing of the stereo I<sup>2</sup>S format with 64 BCLK per LRCLK. Two's complement data is transmitted MSB to LSB with the left channel word beginning one BCLK after the falling edge of LRCLK and the right channel beginning one BCLK after the rising edge of LRCLK. Since data is MSB aligned to the beginning of word transmission, data precision does not need to be configured. Set the SAIF\_FORMAT[2:0] register bits to I<sup>2</sup>S (register 0x02, bits 2:0 = 3'b100).

A. Data presented in two's-complement form with most significant bit (MSB) first.

図 33. I²S 64-f<sub>S</sub> Format

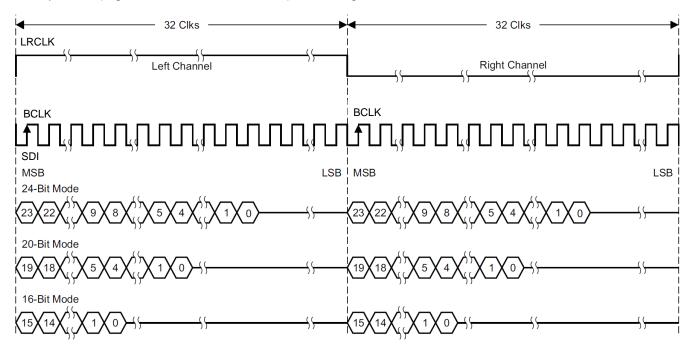

### 7.3.3.2 Stereo Left-Justified Format Timing

The stereo left justified format is very similar to the  $I^2S$  format timing, except the data word begins transmission at the same cycle that LRCLK toggles (when it is shifted by one bit from  $I^2S$ ). The phase of LRCLK is also opposite of  $I^2S$ . The left channel begins transmission when LRCLK transitions from low to high and the right channel begins transmission when LRCLK transitions from high-to-low. Set the SAIF\_FORMAT[2:0] register bits to left-justified (register 0x02, bits 2:0 = 3'b101). The timing is illustrated in .

A. Data presented in two's-complement form with most significant bit (MSB) first.

図 34. Left-Justified 64-f<sub>s</sub> Format

### 7.3.3.3 Stereo Right-Justified Format Timing

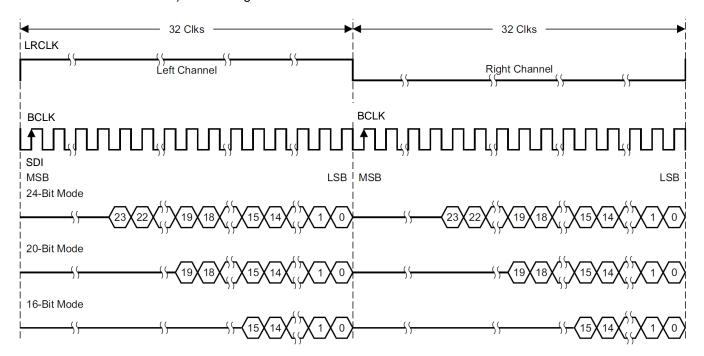

The stereo right justified format aligns the LSB of left channel data to the high to low transition of LRCLK and the LSB of the right channel data to the low to high transition of LRCLK. To insure data is received correctly, the SAIF must be configured for the proper data precision. The TAS5722L supports 16, 18, 20 and 24-bit data precision in right justified format. Set the SAIF\_FORMAT[2:0] register bits (register 0x02, bits 2:0) to the appropriate right-justified setting based on bit precision (value = 3'b000 for 24-bit, 3'b001 for 20-bit, 3'b010 for 18-bit and 3'b011 for 16-bit). The timing is illustrated in .

図 35. Right-Justified 64-f<sub>S</sub> Format

### 7.3.3.4 TDM Format Timing

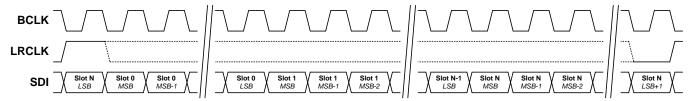

A TDM frame begins with the low to high transition of LRCLK. As long as LRCLK is high for at least one BCLK period and low for one BCLK period, duty cycle is irrelevant. The SAIF automatically detects the number of time slots as long as valid BCLK to LRCLK ratios are utilized (see SAIF introduction above).

For  $I^2S$  aligned TDM operation (when time slot 0 begins, one clock cycle after the low to high transition of LRCLK), set SAIF\_FORMAT[2:0] register bits to  $I^2S$  (register 0x02, bits 2:0 = 3'b100). Data is MSB aligned within the 32-bit time slots, so data precision does not need to be configured. The TDM format timing is illustrated in .

図 36. TDM I<sup>2</sup>S Format

For left-justified TDM operation (when time slot 0 begins the cycle LRCLK transitions from low to high), set SAIF\_FORMAT[2:0] register bits to left-justified(register 0x02, bits 2:0 = 3'b101). As with  $I^2S$ , data is MSB aligned. The timing is illustrated in .

図 37. TDM Left- and Right-Justified Format

For right-justified TDM operation (when time slot 0 begins the cycle LRCLK transitions from low to high), data is LSB aligned to the 32-bit time slot. As with stereo right-justified formats, the TAS5722L must have the data precision configured. Set the SAIF\_FORMAT[2:0] register bits (register 0x02, bits 2:0) to the appropriate right-justified setting based on bit precision (value = 3'b000 for 24-bit, 3'b001 for 20-bit, 3'b010 for 18-bit and 3'b011 for 16-bit). The timing shown in is the same as left-justified TDM, with the data LSB aligned.

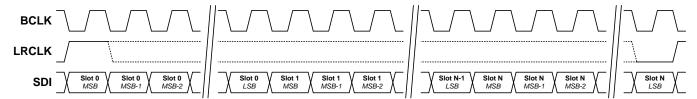

### 7.3.4 Audio Signal Path

illustrates the audio signal flow from the TDM SAIF to the speaker.

(1) See 表 3 for frequency options.

図 38. Audio Signal Path

### 7.3.4.1 High-Pass Filter (HPF)

Excessive DC in audio content can damage loudspeakers, so the amplifier employs a DC detect circuit that shuts down the power stage and issues a latching fault if this condition occurs. A high-pass filter is provided in the TAS5722L device to remove DC from incoming audio data to prevent this from occurring. 表 3 shows the high-pass, -3 dB corner frequencies for each sample rate. The filter can be bypassed by writing a 1 into bit 7 of register 0x02. The high pass corner frequency can be adjusted by setting the HPF\_CORNER bits in the Digital Control 3 register (B[5:7], register 0x13).

表 3. High-Pass Filter -3 dB Corner Frequencies by Sample Rate

| SAMPLE RATE | -3dB CORNER FREQUENCY (Hz) vs. HPF_CORNER [2:0] |      |      |      |       |       |       |       |

|-------------|-------------------------------------------------|------|------|------|-------|-------|-------|-------|

| (kHz)       | 000                                             | 001  | 010  | 011  | 100   | 101   | 110   | 111   |

| 44.1        | 3.675                                           | 7.35 | 14.7 | 29.4 | 58.8  | 117.6 | 235.2 | 470.4 |

| 48          | 4                                               | 8    | 16   | 32   | 64    | 128   | 256   | 512   |

| 88.2        | 7.35                                            | 14.7 | 29.4 | 58.8 | 117.6 | 235.2 | 470.4 | 940.8 |

| 96          | 8                                               | 16   | 32   | 64   | 128   | 256   | 512   | 1024  |

### 7.3.4.2 Amplifier Analog Gain and Digital Volume Control

The gain from TDM SAIF to speaker is controlled by setting the amplifier's analog gain and digital volume control. Amplifier analog gain settings are presented as the output level in dBV (dB relative to 1 Vrms) with a full scale serial audio input (0 dBFS) and the digital volume control set to 0 dB. It should be noted that these levels may not be achievable because of analog clipping in the amplifier, so they should be used to convey gain only.

表 4 outlines each gain setting expressed in dBV and  $V_{PK}$ .

表 4. Amplifier Gain Settings

| ANALOG_GAIN [1:0] | FULL SCALE OUTPUT |                       |  |  |  |

|-------------------|-------------------|-----------------------|--|--|--|

| SETTING           | dBV               | V <sub>PEAK</sub> (V) |  |  |  |

| 00                | 19.2              | 12.9                  |  |  |  |

| 01                | 20.7              | 15.3                  |  |  |  |

| 10                | 23.5              | 21.2                  |  |  |  |

| 11                | 26.3              | 29.2                  |  |  |  |

式 1 calculates the amplifiers output voltage.

$$V_{AMP} = Input + A_{dvc} + A_{AMP} dBV$$

where

- V<sub>AMP</sub> is the amplifier output voltage in dBV

- Input is the digital input amplitude in dB with respect to 0 dBFS

- A<sub>dvc</sub> is the digital volume control setting, -100 dB to 24dB in 0.25-dB steps

- A<sub>AMP</sub> is the amplifier analog gain setting (19.2, 20.7, 23.5, or 26.3) in dBV

(1)

Clipping in the digital domain occurs if the input level (in dB relative to 0 dBFS) plus the digital volume control setting (in dB) are greater than 0 dB. The signal path has approximately 0.5 dB of headroom, but TI does not recommend utilizing it.

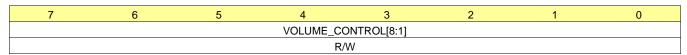

The digital volume control (DVC) can be adjusted from −100 dB to 24 dB in 0.25-dB steps. 式 2 illustrates how to set the 9-bit volume control bits. The top 8 MSBs of the DVCvalue are stored in Volume Control register (register 0x04) and the LSB is stored in the Digital Control 3 register (register 0x13, bit 0).

$$DVC_{value} = 0x19E + \frac{A_{dvc}}{0.25}$$

(2)

For example, digital volume settings of 0 dB, 24 dB and -100 dB map to 0x19E, 0x1FE and 0x0E respectively. Values below 0x0E are equivalent to mute (the amplifier continues to switch with no audio). When a change in digital volume control occurs, the device ramps the volume to the new setting in 0.25 dB steps either every LRCLK or every 8 LRCLK depending on the value of the VOL\_RAMP\_RATE bit (bit 6, reg 0x03).

The Class-D amplifier uses a closed-loop architecture, so the gain does not depend on the supply input ( $V_{PVDD}$ ). The approximate threshold for the onset of analog clipping is calculated in  $\pm 3$ .

$$V_{PK\left(max,preclip\right)} = V_{PVDD} \times \left(\frac{R_L}{2 \times R_{DS\left(on\right)} + R_{int\,erconnect} + R_L}\right) V$$

#### where

- $\bullet \quad V_{PK(max,preclip)}$  is the maximum peak unclipped output voltage in V

- V<sub>PVDD</sub> is the power supply voltage

- $R_1$  is the speaker load in  $\Omega$

- $R_{interconnect}$  is the additional resistance in the PCB (such as cabling and filters) in  $\Omega$

- $R_{DS(on)}$  is the power stage total on resistance (FET+bonding+packaging) in  $\Omega$

The effective on-resistance for the device (including FETs, bonding and packaging leads) is approximately 150 m $\Omega$  at room temperature and increases by approximately 1.6 times over +100°C rise in temperature.  $\frac{1}{2}$ 5 shows approximate maximum unclipped peak output voltages at room temperature (excluding interconnect resistances).

表 5. Approximate Maximum Unclipped Peak Output Voltage at Room Temperature

| SUPPLY VOLTAGE V <sub>PVDD</sub> (V) | MAXIMUM UNCLIPPED<br>PEAK VOLTAGE<br>V <sub>PK</sub> (V) |                  |  |  |

|--------------------------------------|----------------------------------------------------------|------------------|--|--|

|                                      | $R_L = 4 \Omega$                                         | $R_L = 8 \Omega$ |  |  |

| 12                                   | 11.16                                                    | 11.57            |  |  |

| 17                                   | 15.81                                                    | 16.39            |  |  |

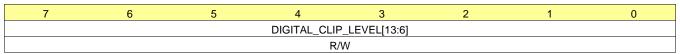

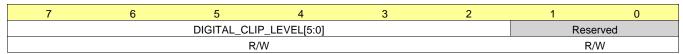

#### 7.3.4.3 Digital Clipper

The digital clipper hard limits the maximum DAC sample value, which provides a simple hardware mechanism to control the largest signal applied to the speaker. Because the block resides in the digital domain, the actual maximum output voltage also depends on the amplifier gain setting and the supply voltage (V<sub>PVDD</sub>) limited amplifier voltage swing (For example, analog clipping may occur before digital clipping).

The maximum amplifier output voltage (excluding limitation due to swing) is calculated in 式 4.

$$V_{AMP\left(max,dc\right)} = 20 \times log_{10} \left( \frac{DC_{level}}{0xFFFF} \right) + 0.5 + A_{AMP}$$

#### where

- V<sub>AMP(max,dc)</sub> is the amplifier maximum output voltage in dBV

- DC<sub>level</sub> is the digital clipper level

- A<sub>AMP</sub> is the amplifier analog gain setting (19.2, 20.7, 23.5, or 26.3) in dBV

Configure the digital clipper by writing the 20-bit  $DC_{level}$  to registers 0x01, 0x10 and 0x11. Set the  $DC_{level}$  to 0xFFFFF effectively bypasses the digital clipper.

(4)

(3)

### 7.3.4.4 Class-D Amplifier Settings

The PWM switching rate of the Class-D amplifier is a phase locked multiple of the input audio sample rate. 表 6 lists the PWM switching rate settings as programmed in bit 4 through bit 6 in register 0x06. The double-speed sample rates (for example 88.2 kHz, 96 kHz) have the same PWM switching frequencies as their equivalent single-speed sample rates.

表 6. PWM Switching Rates

| PWM_RATE [2:0] | SINGLE-SPEED<br>PWM RATE (× f <sub>LRCLK</sub> ) | DOUBLE-SPEED<br>PWM RATE × f <sub>LRCLK</sub> ) | 44.1 kHz, 88.2 kHz<br>f <sub>PWM</sub> (kHz) | 48 kHz, 96 kHz<br>f <sub>PWM</sub> (kHz) |

|----------------|--------------------------------------------------|-------------------------------------------------|----------------------------------------------|------------------------------------------|

| 000            | 6                                                | 3                                               | 264.6                                        | 288                                      |

| 001            | 8                                                | 4                                               | 352.8                                        | 384                                      |

| 010            | 10                                               | 5                                               | 441                                          | 480                                      |

| 011            | 12                                               | 6                                               | 529.2                                        | 576                                      |

| 100            | 14                                               | 7                                               | 617.4                                        | 672                                      |

| 101            | 16                                               | 8                                               | 705.6                                        | 768                                      |

| 110            | 20                                               | 10                                              | 882                                          | 960                                      |

| 111            | 24                                               | 12                                              | 1058.4                                       | 1152                                     |

The Class-D power stage overcurrent detector issues a latching fault if the load current exceeds the safe limit for the device. This threshold can be proportionately adjusted if desired by programming bits 4-5 of register 0x08. 表 7 shows the relative setting for each overcurrent setting.

表 7. Overcurrent Threshold Settings

| OC_THRESH<br>[1:0] | OVERCURRENT<br>THRESHOLD (%) |

|--------------------|------------------------------|

| 00                 | 100                          |

| 01                 | 75                           |

| 10                 | 50                           |

| 11                 | 25                           |

#### 7.4 Device Functional Modes

This section describes the modes of operation for the TAS5722L device.

表 8. Typical Current Consumption<sup>(1)</sup>

| INPUT<br>VOLTAGE<br>V <sub>PVDD</sub> (V) | MODE          | PWM<br>FREQUENCY<br>f <sub>PWM</sub> (kHz) | I <sub>PVDD</sub> +I <sub>AVDD</sub><br>(mA) | INPUT<br>CURRENT<br>I <sub>DVDD</sub> (mA) |

|-------------------------------------------|---------------|--------------------------------------------|----------------------------------------------|--------------------------------------------|

|                                           |               | 384                                        | 11.45                                        |                                            |

|                                           |               | 480                                        | 12.21                                        |                                            |

|                                           | Idle and Mute | 576                                        | 12.94                                        | 1.30                                       |

| 5                                         |               | 672                                        | 13.70                                        |                                            |

|                                           |               | 768                                        | 14.41                                        |                                            |

|                                           | Sleep         | _                                          | 8.48                                         | 0.32                                       |

|                                           | Shutdown      | _                                          | 0.021                                        | 0.046                                      |

|                                           |               | 384                                        | 13.06                                        |                                            |

|                                           | Idle and Mute | 480                                        | 14.46                                        |                                            |

|                                           |               | 576                                        | 15.79                                        | 1.30                                       |

| 12.5                                      |               | 672                                        | 17.18                                        |                                            |

|                                           |               | 768                                        | 18.49                                        |                                            |

|                                           | Sleep         | _                                          | 7.49                                         | 0.32                                       |

|                                           | Shutdown      | _                                          | 0.042                                        | 0.046                                      |

|                                           |               | 384                                        | 14.00                                        |                                            |

|                                           |               | 480                                        | 15.60                                        |                                            |

|                                           | Idle and Mute | 576                                        | 17.10                                        | 1.30                                       |

| 16.5                                      |               | 672                                        | 18.66                                        |                                            |

|                                           |               | 768                                        | 20.15                                        |                                            |

|                                           | Sleep         | _                                          | 7.61                                         | 0.32                                       |

|                                           | Shutdown      | _                                          | 0.045                                        | 0.046                                      |

<sup>(1)</sup> T<sub>A</sub> = 25°C, PVDD pin tied to AVDD pin, V<sub>DVDD</sub> = 1.8 V, R<sub>LOAD</sub> =  $4\Omega$  + 33  $\mu$ H, f<sub>IN</sub> = Idle, f<sub>S</sub> = 48 kHz, Gain = 20.7 dBV, PWR\_TUNE bit = 1

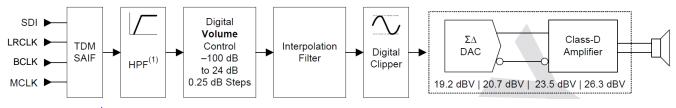

#### 7.4.1 Shutdown Mode (SDZ)

The device enters shutdown mode if either the SDZ pin is asserted low or the I<sup>2</sup>C SDZ register bit is set low (bit 0, reg 0x01). In shutdown mode, the device consumes the minimum quiescent current with most analog and digital blocks powered down. The Class-D amplifier power stage powers down and the output pins are in a Hi-Z state. I<sup>2</sup>C communication remains possible in shutdown mode and register bits states are retained.

If a latching fault condition has occurred (Over Temperature, Over Current or DC detect), the SDZ pin or I<sup>2</sup>C bit must toggle low before the fault register can be cleared. For more information on faults and recovery, see the *Faults and Status* section.

When the device exits shutdown mode (either by releasing the SDZ pin high or setting the  $I^2C$  SDZ register bit high), the device powers up the internal analog and digital blocks required for operation. If the  $I^2C$  SLEEP bit is set low (bit 1, reg 0x01), the device powers up the Class-D amplifier and begins the switching of the power stage. If the  $I^2C$  MUTE bit is set low (bit 4, reg 0x03), the device ramps up the volume to the current setting and begins playing audio.

If shutdown mode is asserted while audio is playing, the device ramps down the volume on the audio, stops the Class-D switching, puts the Class-D power stage output pins in a Hi-Z state and powers down the analog and digital blocks.

# 7.4.2 Sleep Mode

Sleep mode is similar to shutdown mode, except analog and digital blocks required to begin playing audio quickly remain powered up. Sleep mode operates as a *hard mute* where the Class-D amplifier stops switching, but the device does not power down completely. Entering sleep mode does not clear latching faults.

### 7.4.3 Mode Timing

When SDZ is deasserted (and the device is not in sleep mode), the amplifier begins to switch after a period of  $t_{ACTIVE}$ . At this point, the volume ramps from -100 dB to the programmed digital volume control (DVC) setting in a length of time  $t_{VRMP}$ .  $t_{VRMP}$  is determined by the DVC setting, sample rate and volume ramp rate bit, VOL\_RAMP\_RATE (bit 6 of register 0x03). Ramping the volume prevents audible artifacts that can occur if discontinuous volume changes are applied while audio is being played back. This period,  $t_{VRMP}$ , depends on the DVC setting and sample rate. Typical values for  $t_{VRMP}$  for a DVC of 0 dB are shown in Timing Requirements. 24 illustrates mode timing.

The time to enter or exit sleep or mute and the time to enter shudown are dominated by  $t_{VRMP}$ . 表 9 lists the timing parameters based on  $t_{VRMP}$ .

| - ·        | ,                                                          |                   |  |  |  |  |  |

|------------|------------------------------------------------------------|-------------------|--|--|--|--|--|

| SAMPLE     | RAMP TIMES (t <sub>VRAMP</sub> ) FROM -100 dB to 0 dB (ms) |                   |  |  |  |  |  |

| RATE (kHz) | VOL_RAMP_RATE = 0                                          | VOL_RAMP_RATE = 1 |  |  |  |  |  |

| 44.1       | 72.6                                                       | 9.1               |  |  |  |  |  |

| 48         | 66.7                                                       | 8.3               |  |  |  |  |  |

| 88.2       | 36.3                                                       | 4.5               |  |  |  |  |  |

| 96         | 33.3                                                       | 4.2               |  |  |  |  |  |

表 9. Typical DVC Ramp Times

### 7.4.4 Auto Sleep Mode

Auto sleep mode is an optional feature that automatically moves the amplifier from active mode to sleep mode when the device presents an idle audio input (i.e. zero value) to the SAIF for a prescribed number of samples. The device automatically returns to active mode when the device presents a non-idle audio input sample to the SAIF. Auto sleep mode takes advantage of the TAS5722L device's ability to rapidly enter and exit sleep mode from active mode. Because the device applies idle audio samples to the SAIF before entering sleep mode, a volume ramp can be avoided. When exiting sleep mode, the amplifier can resume switching before input sample has propagated through the signal path, which avoids any audible artifacts when resuming playback. AUTO\_SLEEP[1:0] (bits 4:3 in register 0x13) configures the number of idle samples required to enter auto sleep.

#### 7.4.5 Active Mode

If shutdown mode and sleep mode are not asserted, the device is in active mode. During active mode, audio playback is enabled.

#### 7.4.6 Mute Mode

When the  $I^2C_MUTE$  bit is set high (bit 4, reg 0x03) and the device is in active mode, the volume is ramped down and the Class-D amplifier continues to operate with an idle audio input.

#### 7.4.7 Faults and Status