TCA9509 JAJSLQ7D - AUGUST 2011 - REVISED APRIL 2021

# TCA9509 レベル変換 I<sup>2</sup>C および SMBUS バス・リピーター

# 1 特長

- 2 チャネルの双方向バッファ

- I<sup>2</sup>C バスおよび SMBus 互換

- B 側の動作電源電圧範囲:2.7V~5.5V

- A 側の動作電源電圧範囲:0.9V~5.5V

- 0.9V~5.5V と 2.7V~5.5V の電圧レベル変換

- アクティブ HIGH のリピーター・イネーブル入力

- 低電圧ポートAに外付けプルアップ抵抗は不要

- オープン・ドレインの I<sup>2</sup>C I/O

- 5.5V 許容の I<sup>2</sup>C およびイネーブル入力で、混在モー ドの信号動作に対応

- ロックアップの発生しない動作

- 標準モードおよびファースト・モード I<sup>2</sup>C デバイスおよ び複数のマスタに対応

- リピーター越しの調停およびクロック・ストレッチングを サポート

- 電源オフ時に高インピーダンスになる I<sup>2</sup>C バス・ピン

- 400kHz 高速 I<sup>2</sup>C バスの動作速度をサポート

- 利用可能なバージョン:

- 1.6mm×1.6mm、高さ0.4mm、0.5mm ピッチの QFN パッケージ

- 3mm × 3mm の業界標準 MSOP パッケージ

- JESD 78、Class II 準拠で 100mA 超のラッチアップ

- JESD 22 を超える ESD 保護

- 2000V、人体モデル (A114-A)

- 1000V、デバイス帯電モデル (C101)

# 2 アプリケーション

- サーバー

- ルーター (テレコム・スイッチング機器)

- 多くの I<sup>2</sup>C ターゲットや長い PCB 配線を持つ製品

# 3 概要

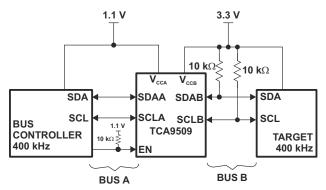

この TCA9509 IC は、I<sup>2</sup>C/SMBus システム用の I<sup>2</sup>C バ ス/SMBus リピーターです。混在モード・アプリケーション で、低電圧 (最低 0.9V) と、より高い電圧 (2.7V~5.5V) と の間の双方向電圧レベル変換 (昇圧変換/降圧変換)も 行うことができます。このデバイスにより、I<sup>2</sup>C および同様の バス・システムを拡張でき、レベル・シフト時にも性能劣化 を防ぐことができます。

TCA9509 は、I<sup>2</sup>C バス上のシリアル・データ (SDA) 信号 とシリアル・クロック (SCL) 信号の両方をバッファリングする ことで、400pF の B 側バス容量を可能にします。このデバ イスを使ってバスを2つに分割し、電圧や容量を分離する こともできます。

TCA9509 には、A 側ドライバと B 側ドライバの 2 種類の ドライバがあります。 すべての入力と B 側 I/O は、5.5V の 過電圧耐性を備えています。A側 I/Oは、デバイスの電 源がオフ (VCCB および / または VCCA = 0V) の場合 5.5V の過電圧耐性を備えています。

## 製品情報(1)

|    | 部品番号   | パッケージ     | 本体サイズ (公称)      |

|----|--------|-----------|-----------------|

| Т  | CA9509 | VSSOP (8) | 3.00mm × 3.00mm |

| '` |        | X2QFN (8) | 1.60mm × 1.60mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

概略回路図

# **Table of Contents**

| 1 特長                                                                                                                                                 | 1 9.2 Functional Block                    | Diagram10                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|

| 2 アプリケーション                                                                                                                                           |                                           | on11                                         |

| 3 概要                                                                                                                                                 |                                           | I Modes11                                    |

| 4 Revision History                                                                                                                                   |                                           | plementation12                               |

| 5 Description (continued)                                                                                                                            |                                           | mation                                       |

| 6 Pin Configuration and Functions                                                                                                                    | 4 10.2 Typical Applicati                  | on 12                                        |

| 7 Specifications                                                                                                                                     | 5 11 Power Supply Reco                    | ommendations15                               |

| 7.1 Absolute Maximum Ratings                                                                                                                         |                                           | 16                                           |

| 7.2 ESD Ratings                                                                                                                                      |                                           | es16                                         |

| 7.3 Recommended Operating Conditions                                                                                                                 |                                           | 16                                           |

| 7.4 Thermal Information                                                                                                                              | 13 Device and Docum                       | entation Support17                           |

| 7.5 Electrical Characteristics                                                                                                                       |                                           | cation of Documentation Updates 17           |

| 7.6 Timing Requirements                                                                                                                              |                                           | 17                                           |

| 7.7 I <sup>2</sup> C Interface Timing Requirements                                                                                                   |                                           | 17                                           |

| 8 Parameter Measurement Information                                                                                                                  |                                           | する注意事項17                                     |

| 9 Detailed Description                                                                                                                               | 10 13.5 用語集                               | 17                                           |

| 9.1 Overview                                                                                                                                         |                                           |                                              |

| 4 Revision History<br>資料番号末尾の英字は改訂を表しています。その<br>Changes from Povision C (December 2017                                                               |                                           |                                              |

| Changes from Revision C (December 2017                                                                                                               |                                           | Page                                         |

| <ul> <li>データシート全体で用語「マスタ、スレーブ」を</li> <li>Changed I<sub>CC</sub> Quiescent supply current for 0.9 mA to 0.5 mA in the Electrical Character</li> </ul> | $V_{\rm CCB}$ MIN value from 0.5 mA to 0. | 20 mA and the TYP value from                 |

| Changed text From: "Multiple B-sides of To                                                                                                           |                                           |                                              |

| Changes from Revision B (January 2012) to                                                                                                            | Revision C (December 2017)                | Page                                         |

| <ul><li>「ESD 定格」表、「機能説明」セクション、「ディー」</li></ul>                                                                                                        |                                           | ・<br>『リケー・ション <i>ト宝奘</i>   セクシノョン 「 <i>雷</i> |

| 源に関する推奨事項」セクション、「レイアウト」<br>ル、パッケージ、および注文情報」セクションを                                                                                                    | セクション、「 <i>デバイスおよび</i> ドキュメ               | ントのサポート」セクション、「メカニカ                          |

| <ul> <li>Added junction temperature to the Absolut</li> </ul>                                                                                        |                                           |                                              |

| Changed thermal information for RVH and                                                                                                              |                                           |                                              |

| <ul> <li>Changed V<sub>ILC</sub>, added Test Conditions with</li> </ul>                                                                              | new MIN and TVP values in the F           | Electrical Characteristics table 6           |

|                                                                                                                                                      |                                           |                                              |

| <ul> <li>Updated Bus A (0.9-V to 5.5-V Bus) Wavet</li> </ul>                                                                                         |                                           |                                              |

| <ul> <li>Updated Bus B (2.7-V to 5.5-V Bus) Wave</li> </ul>                                                                                          | orm                                       | /                                            |

| Changes from Revision A (October 2011) to                                                                                                            | Revision B (January 2012)                 | Page                                         |

| • DGK パッケージとパッケージ情報をデータシ                                                                                                                             | ートに追加                                     | 1                                            |

| Changes from Revision * (August 2011) to                                                                                                             | Revision A (October 2011)                 | Page                                         |

| <ul><li>ドキュメント内の複数の事例で、V<sub>CCA</sub>の動作</li></ul>                                                                                                  | ፪圧の下限を 0.9√ に訂正                           | <u></u> 1                                    |

| <ul><li>「特長」のB側の動作電源電圧範囲の値の誤</li></ul>                                                                                                               |                                           |                                              |

| 1 * * * * * * * * * * * * * * * * * * *                                                                                                              | 記を変更。  B 側:0.9V~5.5V を  L                 | 3 側:2.7Ⅴ~5.5Ⅴ」に変更。 1                         |

| • 「特長」の A 側の動作電源電圧範囲の値の誤                                                                                                                             |                                           |                                              |

Submit Document Feedback

に変更。......1

## 5 Description (continued)

The bus port B drivers are compliant with SMBus I/O levels, while the A-side uses a current sensing mechanism to detect the input or output LOW signal which prevents bus lock-up. The A-side uses a 1 mA current source for pull-up and a 200  $\Omega$  pull-down driver. This results in a LOW on the A-side accommodating smaller voltage swings. The output pull-down on the A-side internal buffer LOW is set for approximately 0.2 V, while the input threshold of the internal buffer is set about 50 mV lower than that of the output voltage LOW. When the A-side I/O is driven LOW internally, the LOW is not recognized as a LOW by the input. This prevents a lock-up condition from occurring. The output pull-down on the B-side drives a hard LOW and the input level is set at 0.3 of SMBus or I<sup>2</sup>C-bus voltage level which enables B side to connect to any other I<sup>2</sup>C-bus devices or buffer.

The TCA9509 drivers are not enabled unless  $V_{\text{CCA}}$  is above 0.8 V and  $V_{\text{CCB}}$  is above 2.5 V. The enable (EN) pin can also be used to turn the drivers on and off under system control. Caution should be observed to only change the state of the EN pin when the bus is idle.

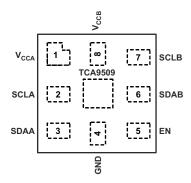

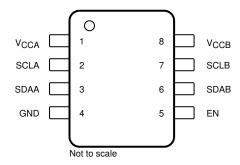

# **6 Pin Configuration and Functions**

図 6-1. RVH Package, 8-Pin X2QFN, Top View

図 6-2. DGK Package, 8-Pin VSSOP, Top View

PIN I/O **DESCRIPTION** NAME NO. 1 A-side supply voltage (0.9 V to 5.5 V)  $V_{CCA}$ Supply **SCLA** 2 I/O Serial clock bus, A side. SDAA 3 I/O Serial data bus. A side. GND 4 Supply Supply ground ΕN 5 Active-high repeater enable input Input SDAB 6 I/O Serial data bus, B side. Connect to V<sub>CCB</sub> through a pull-up resistor. **SCLB** 7 I/O Serial clock bus, B side. Connect to  $V_{\text{CCB}}$  through a pull-up resistor. 8 B-side and device supply voltage (2.7 V to 5.5 V) Supply  $V_{CCB}$ Thermal Thermal Attach Pad is not electrically connected and it is recommended to be attached to GND for best thermal performance. This is for the RVH package only. Attach Pad

表 6-1. Pin Functions

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                             |                    | MIN  | MAX | UNIT |

|------------------|---------------------------------------------|--------------------|------|-----|------|

| V <sub>CCB</sub> | Supply voltage                              |                    | -0.5 | 6   | V    |

| $V_{CCA}$        | Supply voltage                              |                    | -0.5 | 6   | V    |

| VI               | Enable input voltage <sup>(2)</sup>         | -0.5               | 6    | V   |      |

| V <sub>I/O</sub> | I <sup>2</sup> C bus voltage <sup>(2)</sup> | -0.5               | 6    | V   |      |

| I <sub>IK</sub>  | Input clamp current                         | V <sub>I</sub> < 0 |      | -20 | A    |

| I <sub>OK</sub>  | Output clamp current                        | V <sub>O</sub> < 0 |      | -20 | - mA |

| $P_d$            | Max power dissipation                       |                    |      | 100 | mW   |

| TJ               | Junction temperature                        |                    |      | 125 | °C   |

| T <sub>stg</sub> | Storage temperature                         |                    | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| V.===:             | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

|                  |                                |            | MIN                    | MAX                    | UNIT |

|------------------|--------------------------------|------------|------------------------|------------------------|------|

| V <sub>CCA</sub> | Supply voltage, A-side bus     |            | 0.9 <sup>(1)</sup>     | 5.5                    | V    |

| V <sub>CCB</sub> | Supply voltage, B-side bus     |            | 2.7                    | 5.5                    | V    |

| V <sub>IH</sub>  |                                | SDAA, SCLA | 0.7 × V <sub>CCA</sub> | V <sub>CCA</sub>       |      |

|                  | High-level input voltage       | SDAB, SCLB | 0.7 × V <sub>CCB</sub> | 5.5                    | V    |

|                  |                                | EN         | 0.7 × V <sub>CCA</sub> | 5.5                    |      |

|                  |                                | SDAA, SCLA | -0.5                   | 0.3                    |      |

| V <sub>IL</sub>  | Low-level input voltage        | SDAB, SCLB | -0.5                   | 0.3 × V <sub>CCB</sub> | V    |

|                  |                                | EN         | -0.5                   | 0.3 × V <sub>CCA</sub> |      |

|                  | Low level output ourrent       | SDAA, SCLA |                        | 10                     | μΑ   |

| I <sub>OL</sub>  | Low-level output current       | SDAB, SCLB |                        | 6                      | mA   |

| T <sub>A</sub>   | Operating free-air temperature | ·          | -40                    | 85                     | °C   |

Low-level supply voltage

<sup>(2)</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information

|                        |                                                       | TCA9509     |             |      |  |

|------------------------|-------------------------------------------------------|-------------|-------------|------|--|

|                        | THERMAL METRIC <sup>(1)</sup>                         | RVH (X2QFN) | DGK (VSSOP) | UNIT |  |

|                        |                                                       | 8 PINS      | 8 PINS      |      |  |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance <sup>(2)</sup> | 160.3       | 222.9       | °C/W |  |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance             | 66.4        | 109.5       | °C/W |  |

| $R_{\theta JB}$        | Junction-to-board thermal resistance                  | 115.9       | 144.5       | °C/W |  |

| ΨЈТ                    | Junction-to-top characterization parameter            | 0.8         | 34.5        | °C/W |  |

| ΨЈВ                    | Junction-to-board characterization parameter          | 116.2       | 142.7       | °C/W |  |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance          | 80.5        | n/a         | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

$V_{CCB}$  = 2.7 V to 5.5 V,  $V_{CCA}$  = 0.9 V to ( $V_{CCB}$ -1),  $T_A$  = -40°C to 85°C (unless otherwise noted)

|                                    | PARAMETER                                              |            | TEST CONDITIONS                                                                      | MIN  | TYP  | MAX  | UNIT     |  |

|------------------------------------|--------------------------------------------------------|------------|--------------------------------------------------------------------------------------|------|------|------|----------|--|

| V <sub>IK</sub>                    | Input clamp voltage                                    |            | I <sub>I</sub> = -18 mA                                                              | -1.5 |      | -0.5 | V        |  |

| V                                  | Low-level output voltage                               | SDAA, SCLA | $I_{OL} = 10 \ \mu A,$ $V_{ILA} = V_{ILB} = 0 \ V,$ $V_{CCA} = 0.9 \ to \ 1.2 \ V$   |      | 0.18 | 0.25 | V        |  |

| V <sub>OL</sub>                    | Low-level output voltage                               | SDAA, SCLA | $I_{OL} = 20 \mu A,$ $V_{ILA} = V_{ILB} = 0 V,$ $1.2V < V_{CCA} \le (V_{CCB} - 1 V)$ |      | 0.2  | 0.3  | V        |  |

| V <sub>OL</sub> – V <sub>ILc</sub> | Low-level input voltage below low-level output voltage | SDAA, SCLA |                                                                                      |      | 50   |      | mV       |  |

| V <sub>ILc</sub>                   | SDA and SCL low-level input                            | SDAA, SCLA | V <sub>CCA</sub> ≥ 1.5 V and V <sub>CCB</sub> ≥ 3.15 V                               | 110  | 150  |      | mV       |  |

|                                    | voltage contention                                     | SDAA, SCLA | V <sub>CCA</sub> < 1.5 V or V <sub>CCB</sub> < 3.15 V                                | 50   | 100  |      | IIIV     |  |

| V <sub>OLB</sub>                   | Low-level output voltage                               | SDAB, SCLB | I <sub>OL</sub> = 6 mA                                                               |      | 0.1  | 0.2  | V        |  |

|                                    | Quiescent aupply ourrent for V                         |            | All port A Static high                                                               | 0.25 | 0.45 | 0.9  | mA       |  |

| I <sub>CC</sub>                    | Quiescent supply current for V <sub>0</sub>            | CCA        | All port A Static low                                                                | 1.25 |      |      | IIIA     |  |

| I <sub>CC</sub>                    | Quiescent supply current for Vo                        | CCB        | All port B Static high                                                               | 0.2  | 0.5  | 1.1  | mA       |  |

|                                    |                                                        | SDAB, SCLB | V <sub>I</sub> = V <sub>CCB</sub>                                                    |      |      | ±1   | 10<br>±1 |  |

|                                    |                                                        | SDAB, SCLB | V <sub>I</sub> = 0.2 V                                                               |      |      | 10   |          |  |

| I.                                 | Input leakage current                                  | SDAA, SCLA | V <sub>I</sub> = V <sub>CCA</sub>                                                    |      |      | ±1   |          |  |

| l <sub>l</sub>                     | input leakage current                                  | ODAA, OOLA | V <sub>I</sub> = 0.2 V                                                               |      |      | 10   | μA       |  |

|                                    |                                                        | EN         | V <sub>I</sub> = V <sub>CCB</sub>                                                    |      |      | ±1   |          |  |

|                                    |                                                        | LIV        | V <sub>I</sub> = 0.2 V                                                               |      |      | -10  |          |  |

| l                                  | High-level output leakage                              | SDAB, SCLB | V <sub>O</sub> = 3.6 V                                                               |      |      | 10   | μA       |  |

| I <sub>OH</sub>                    | current                                                | SDAA, SCLA | VO - 0.0 V                                                                           |      |      | 10   | μΛ       |  |

| C <sub>IOA</sub>                   | I/O capacitance of A-side                              | SCLA, SDAA | V <sub>I</sub> = 0 V                                                                 |      | 6.5  | 7    | pF       |  |

| C <sub>IOB</sub>                   | I/O capacitance of B-side                              | SCLB, SDAB | V <sub>I</sub> = 0 V                                                                 | 5.5  |      | 6.2  | pF       |  |

Product Folder Links: TCA9509

<sup>(2)</sup> The package thermal impedance is calculated in accordance with JESD 51-7.

# 7.6 Timing Requirements

over recommended operating free-air temperature range (unless otherwise noted)

|                 |                                                           | MIN I | MAX | UNIT |

|-----------------|-----------------------------------------------------------|-------|-----|------|

| t <sub>su</sub> | Setup time, EN high before Start condition <sup>(1)</sup> | 100   |     | ns   |

| t <sub>h</sub>  | Hold time, EN high after Stop condition <sup>(1)</sup>    | 100   |     | ns   |

<sup>(1)</sup> EN should change state only when the global bus and the repeater port are in an idle state.

# 7.7 I<sup>2</sup>C Interface Timing Requirements

$T_A = -40$ °C to 85°C (unless otherwise noted)

|                   | PARAMETE                                                                   | :R               | V <sub>CCA</sub><br>(INPUT) | V <sub>CCB</sub><br>(OUTPUT) | TEST CONDITIONS | MIN   | TYP <sup>(1)</sup> | MAX   | UNIT |

|-------------------|----------------------------------------------------------------------------|------------------|-----------------------------|------------------------------|-----------------|-------|--------------------|-------|------|

| t <sub>PHL</sub>  | Propagation delay                                                          | port A to port B | 1.9 V                       | 5 V                          | EN High         | 123.1 | 127.2              | 132.8 |      |

|                   |                                                                            | port B to port A | 1.9 V                       | 5 V                          | EN HIGH         | 88.1  | 88.8               | 89.8  | ns   |

| t <sub>PLH</sub>  | Dranagation dalay                                                          | port A to port B | 101/                        | E.V.                         | TN Himb         | 122.6 | 125.7              | 131.7 |      |

|                   | Propagation delay                                                          | port B to port A | 1.9 V                       | 1.9 V 5 V EN High            |                 | 123   | 124.1              | 126.9 | ns   |

|                   | Transition time                                                            | port A           | 1.9 V                       | 5 V                          | EN High         | 40.1  | 40.9               | 41.9  |      |

| t <sub>rise</sub> | rransition time                                                            | port B           | 1.9 V                       |                              |                 | 57.3  | 57.5               | 58.4  | ns   |

|                   | Transition time                                                            | port A           | 1.9 V                       | 5.V                          | EN High         | 14.5  | 16.4               | 17.9  |      |

| t <sub>fall</sub> |                                                                            | port B           | 1.9 V                       | 5 V                          | EN HIGH         | 18.7  | 19.4               | 20.2  | ns   |

| t <sub>PLH2</sub> | Propagation delay<br>50% of initial low on<br>Port A to 1.5 V on<br>Port B | port A to port B | 1.9 V                       | 5 V                          |                 | 176   | 177.3              | 178   | ns   |

| f <sub>MAX</sub>  | Maximum switching frequency                                                |                  |                             |                              |                 | 400   |                    |       | KHz  |

(1) Typical values were measured with  $V_{CCA} = V_{CCB} = 2.7 \text{ V}$  at  $T_A = 25 ^{\circ}\text{C}$ , unless otherwise noted.

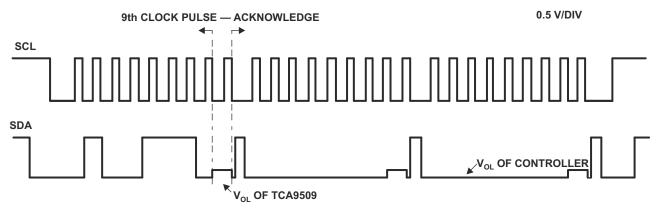

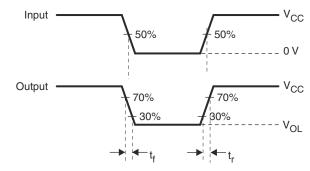

図 7-1. Bus A (0.9-V to 5.5-V Bus) Waveform

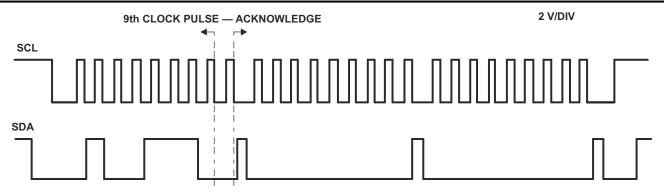

図 7-2. Bus B (2.7-V to 5.5-V Bus) Waveform

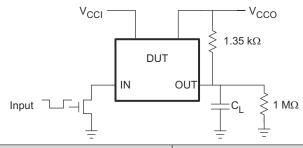

# **8 Parameter Measurement Information**

| PIN                 | CL    |  |  |  |

|---------------------|-------|--|--|--|

| SCLA, SDAA (A-side) | 50 pF |  |  |  |

| SDAB, SCLB (B-side) | 50 pF |  |  |  |

- A.  $R_T$  termination resistance should be equal to  $Z_{OUT}$  of pulse generators.

- B.  $C_L$  includes probe and jig capacitance.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O$  = 50  $\Omega$ , slew rate  $\geq$  1 V/ns.

- D. The outputs are measured one at a time, with one transition per measurement.

- E.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

図 8-1. Test Circuit and Voltage Waveforms

# 9 Detailed Description

#### 9.1 Overview

This TCA9509 integrated circuit is an  $I^2C$  bus/SMBus Repeater for use in  $I^2C$ /SMBus systems. It can also provide bidirectional voltage-level translation (up-translation/down-translation) between low voltages (down to 0.9 V) and higher voltages (2.7 V to 5.5 V) in mixed-mode applications. This device enables  $I^2C$  and similar bus systems to be extended, without degradation of performance even during level shifting.

The TCA9509 buffers both the serial data (SDA) and the serial clock (SCL) signals on the I<sup>2</sup>C bus, thus allowing 400-pF bus capacitance on the B-side. This device can also be used to isolate two halves of a bus for voltage and capacitance.

The TCA9509 has two types of drivers – A-side drivers and B-side drivers. All inputs and B-side I/O's are overvoltage tolerant to 5.5V. The A-side I/O's are overvoltage tolerant to 5.5 V when the device is unpowered  $(V_{CCB} \text{ and/or } V_{CCA} = 0V)$ .

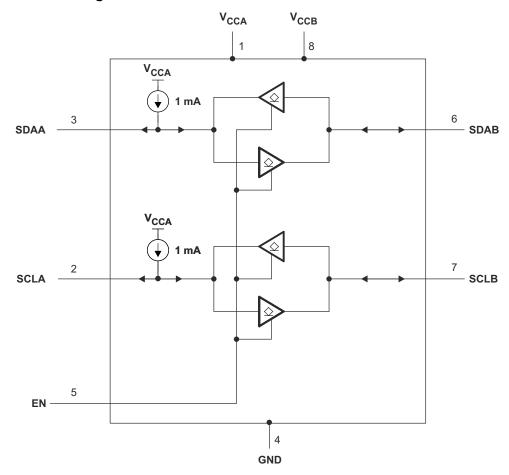

#### 9.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

## 9.3 Feature Description

# 9.3.1 Two-Channel Bidirectional Buffer

The TCA9509 is a two-channel bidirectional buffer with level-shifting capabilities, featuring an integrated current source on the A-side.

#### 9.3.2 Integrated A-Side Current Source

The A-side ports of the TCA9509 feature an integrated 1 mA current source, eliminating the need for external pull-up resistors on SDAA and SCLA.

## 9.3.3 Standard Mode and Fast Mode Support

The TCA9509 supports standard mode as well as fast mode  $I^2C$ . The maximum system operating frequency will depend on system design and delays added by the repeater.

#### 9.4 Device Functional Modes

表 9-1 lists the functional modes for the TCA9509.

表 9-1. Function Table

| INPUT<br>EN | FUNCTION                   |

|-------------|----------------------------|

| L           | Outputs disabled           |

| Н           | SDAA = SDAB<br>SCLA = SCLB |

# 10 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 10.1 Application Information

The TCA9509 is 5-V tolerant, so it does not require any additional circuitry to translate between 0.9-V to 5.5-V bus voltages and 2.7-V to 5.5-V bus voltages.

When the B-side of the TCA9509 is pulled low by a driver on the  $I^2C$  bus and the falling edge goes below 0.3  $V_{CCB}$ , it causes the internal driver on the A-side to turn on, causing the A-side to pull down to about 0.2  $V_{CCB}$ . When the A-side of the TCA9509 falls, a comparator detects the falling edge and causes the internal driver on the B-side to turn on and pull the B-side pin down to ground. In order to illustrate what would be seen in a typical application, refer to  $\mathbb{Z}$  7-1. If the bus controller in  $\mathbb{Z}$  10-1 were to write to the target through the TCA9509, waveforms shown in  $\mathbb{Z}$  7-2 would be observed on the B bus. This looks like a normal  $I^2C$  bus transmission, except that the high level may be as low as 0.9 V, and the turn on and turn off of the acknowledge signals are slightly delayed.

On the A-side bus of the TCA9509, the clock and data lines would have a positive offset from ground equal to the  $V_{OL}$  of the TCA9509. After the eighth clock pulse, the data line is pulled to the  $V_{OL}$  of the controller device, which is close to ground in this example. At the end of the acknowledge, the level rises only to the low level set by the driver in the TCA9509 for a short delay, while the B-bus side rises above 0.3  $V_{CCB}$  and then continues high. It is important to note that any arbitration or clock stretching events require that the low level on the A-bus side at the input of the TCA9509 ( $V_{IL}$ ) be at or below  $V_{ILC}$  to be recognized by the TCA9509 and then transmitted to the B-bus side.

#### 10.2 Typical Application

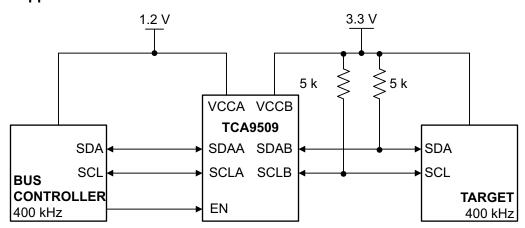

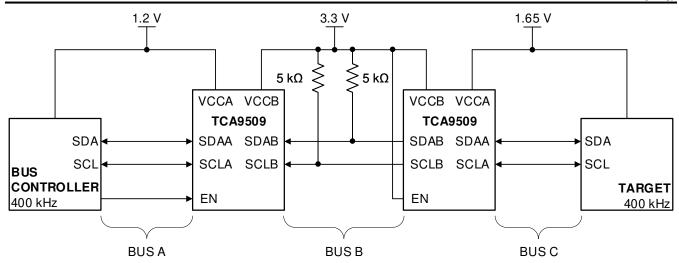

図 10-1. Typical Application, A-side Connected to controller

#### 10.2.1 Design Requirements

A typical application is shown in  $\boxtimes$  10-1. In this example, the system controller is running on a 1.2-V I<sup>2</sup>C bus, and the target is connected to a 3.3-V bus. Both buses run at 400 kHz. Controller devices can be placed on either bus. For the level translating application, the following should be true:  $V_{CCA} \le (V_{CCB} - 1 \text{ V})$

- V<sub>CCA</sub> = 0.9 V to 5.5 V

- V<sub>CCB</sub> = 2.7 to 5.5 V

- A-side ports must not be connected together

- Pullup resistors should not be placed on the A-side ports

Submit Document Feedback

## 10.2.2 Detailed Design Procedure

#### 10.2.2.1 Clock Stretching Support

The TCA9509 can support clock stretching, but care needs to be taken to minimize the overshoot voltage presented during the hand-off between the target and controller. This is best done by increasing the pull-up resistor value on B-side ports.

#### 10.2.2.2 V<sub>ILC</sub> and Pulldown Strength Requirements

For the TCA9509 to function correctly, all devices on the A-side must be able to pull the A-side below the voltage input low contention level ( $V_{ILC}$ ). This means that the  $V_{OL}$  of any device on the A-side must be below  $V_{ILC}$  min.

The  $V_{OL}$  can be adjusted by changing the  $I_{OL}$ through the device which is set by the pull-up resistance value. The pull-up resistance on the A-side must be carefully selected to ensure that the logic levels will be transferred correctly to the B-side.

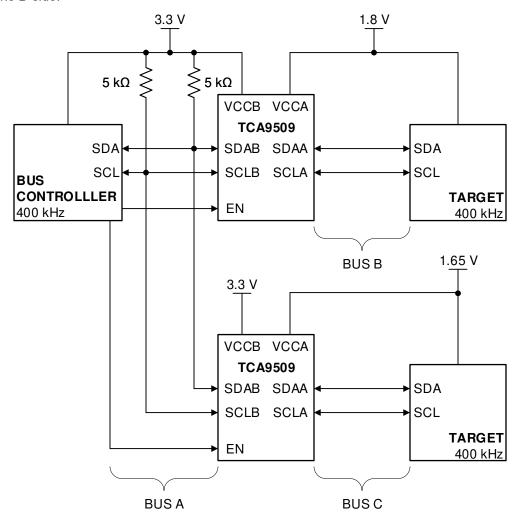

図 10-2. Typical Star Application

Multiple B-sides of TCA9509 can be connected in a star configuration, allowing all nodes to communicate with each other. The A-sides should not be connected together when used in a star/parallel configuration.

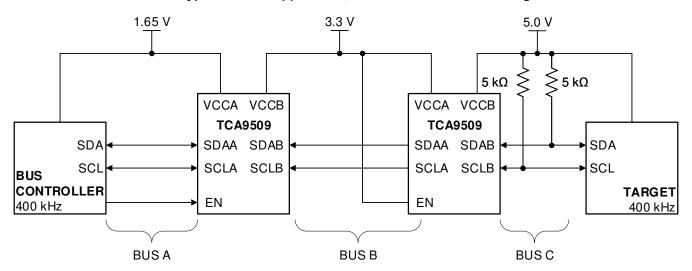

図 10-3. Typical Series Application, Two B-Sides Connected Together

図 10-4. Typical Series Application, A-side Connected to B-Side

To further extend the  $I^2C$  bus for long traces/cables, multiple TCA9509 devices can be connected in series as long as the A-side is connected to the B-side and  $V_{CCA} \le (V_{CCB} - 1 \text{ V})$  must also be met. Series connections can also be made by connecting both B-sides together while following power supply rule  $V_{CCA} \le (V_{CCB} - 1 \text{ V})$ .  $I^2C$  bus target devices can be connected to any of the bus segments. The number of devices that can be connected in series is limited by repeater delay/time-of-flight considerations on the maximum bus speed requirements.

# 11 Power Supply Recommendations

$V_{CCB}$  and  $V_{CCA}$  can be applied in any sequence at power up. The TCA9509 includes a power-up circuit that keeps the output drivers turned off until  $V_{CCB}$  is above 2.5 V and the  $V_{CCA}$  is above 0.8 V. After power up and with the EN high, a low level on the B-side (below  $0.3 \times V_{CCB}$ ) turns the corresponding A-side driver (either SDA or SCL) on and drives the A-side down to approximately 0.2 V. When the B-side rises above  $0.3 \times V_{CCB}$ , the A-side pull-down driver is turned off and the external pull-up resistor pulls the pin high. When the A-side falls first and goes below  $0.3 \times V_{CCA}$ , the B-side driver is turned on and the B-side pulls down to 0 V. The A-side pull-down is not enabled unless the A-side voltage goes below 0.4 V. If the A-side low voltage does not go below 0.5 V, the B-side driver turns off when the A-side voltage is above  $0.7 \times V_{CCA}$ . If the A-side low voltage goes below 0.4 V, the A-side pull-down driver is enabled, and the A-side is able to rise to only 0.5 V until the B-side rises above  $0.3 \times V_{CCB}$ .

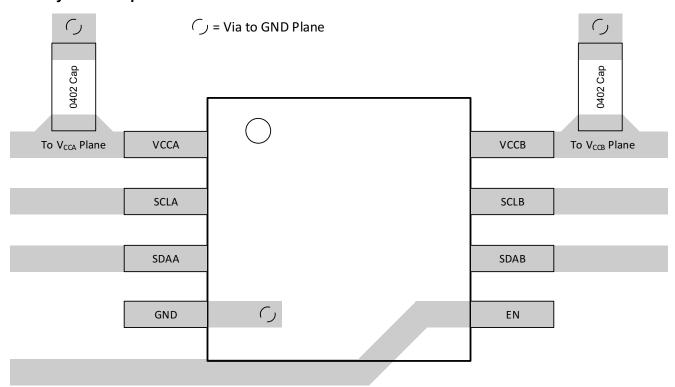

A 100 nF a decoupling capacitor should be placed as close to the  $V_{CCA}$  and  $V_{CCB}$  pins in order to provide proper filtering of supply noise.

# 12 Layout

# 12.1 Layout Guidelines

There are no special layout procedures required for the TCA9509.

It is recommended that the decoupling capacitors be placed as close to the VCC pins as possible.

## 12.2 Layout Example

図 12-1. Example Layout

# 13 Device and Documentation Support

# 13.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 13.2 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 13.3 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

## 13.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 13.5 用語集

TI 用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 1-Nov-2022

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                      |         |

| TCA9509DGKR      | ACTIVE | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | NIPDAUAG   SN                 | Level-1-260C-UNLIM | -40 to 85    | (7KO, 7KQ)           | Samples |

| TCA9509MRVHR     | ACTIVE | X2QFN        | RVH                | 8    | 5000           | RoHS & Green | NIPDAUAG                      | Level-1-260C-UNLIM | -40 to 85    | 7K                   | Samples |

| TCA9509RVHR      | ACTIVE | X2QFN        | RVH                | 8    | 5000           | RoHS & Green | NIPDAU   NIPDAUAG             | Level-1-260C-UNLIM | -40 to 85    | 7K                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 1-Nov-2022

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 13-Apr-2024

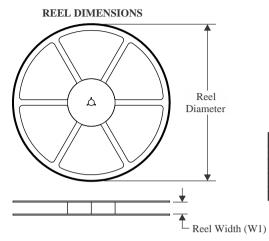

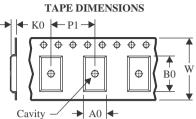

## TAPE AND REEL INFORMATION

|    | •                                                         |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

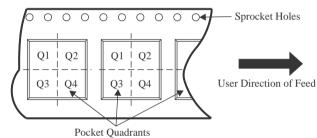

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TCA9509MRVHR | X2QFN           | RVH                | 8 | 5000 | 180.0                    | 8.4                      | 1.8        | 1.8        | 0.5        | 4.0        | 8.0       | Q1               |

| TCA9509RVHR  | X2QFN           | RVH                | 8 | 5000 | 180.0                    | 8.4                      | 1.8        | 1.8        | 0.5        | 4.0        | 8.0       | Q3               |

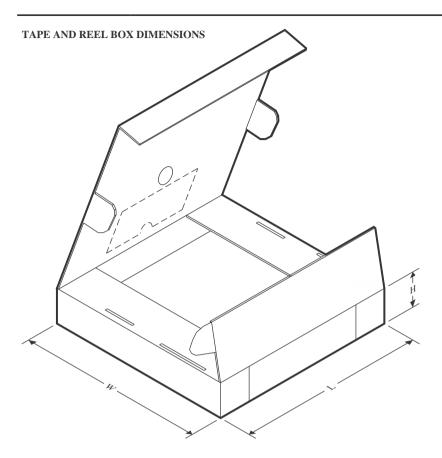

www.ti.com 13-Apr-2024

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TCA9509MRVHR | X2QFN        | RVH             | 8    | 5000 | 183.0       | 183.0      | 20.0        |

| TCA9509RVHR  | X2QFN        | RVH             | 8    | 5000 | 202.0       | 201.0      | 28.0        |

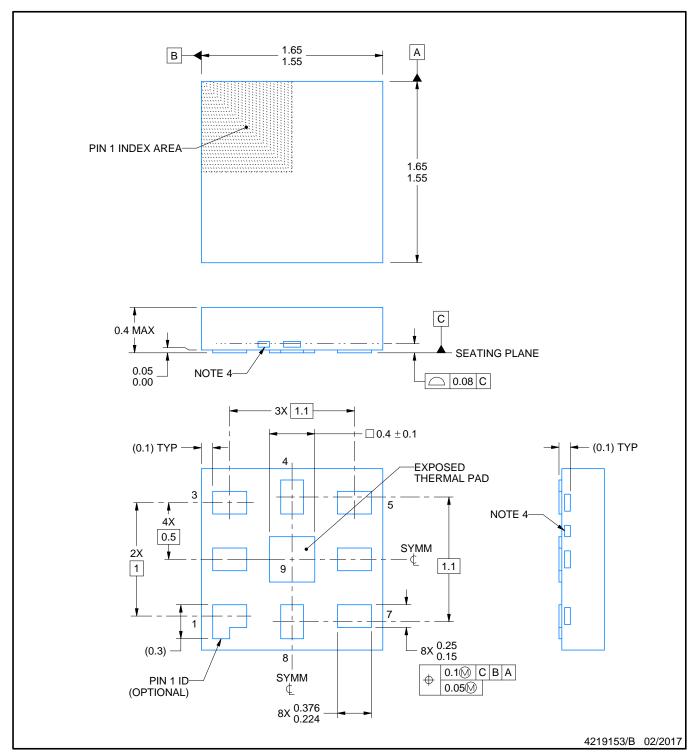

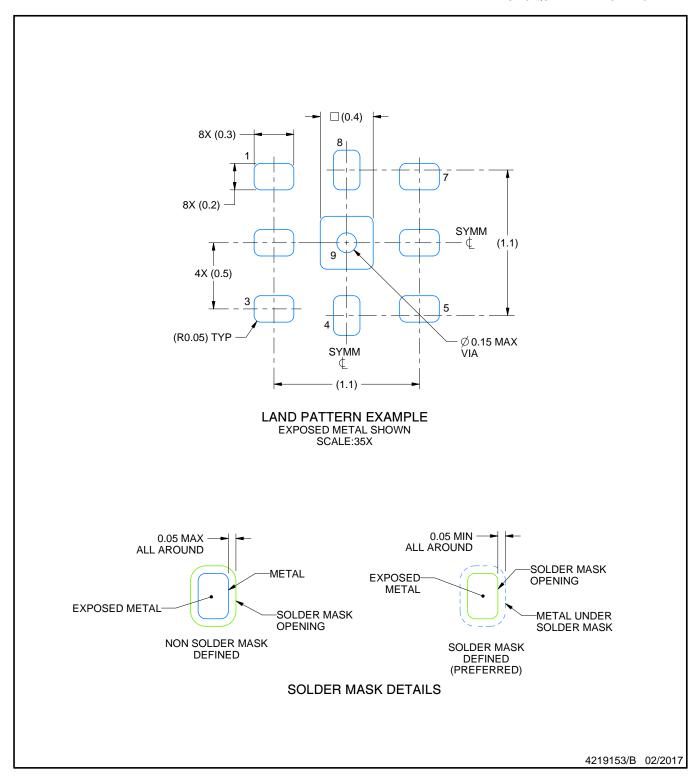

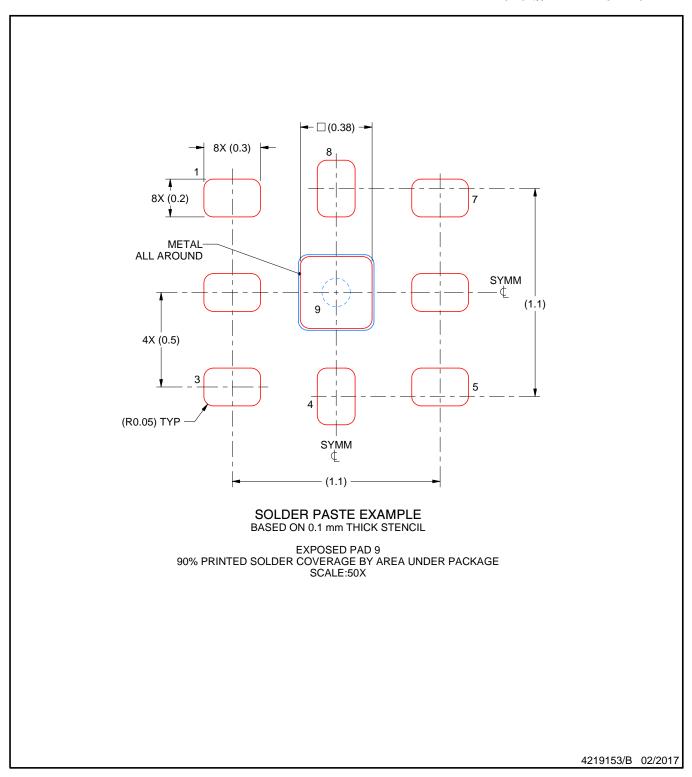

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

- 4. Exposed tie bars may vary in size and location.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 5. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 6. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

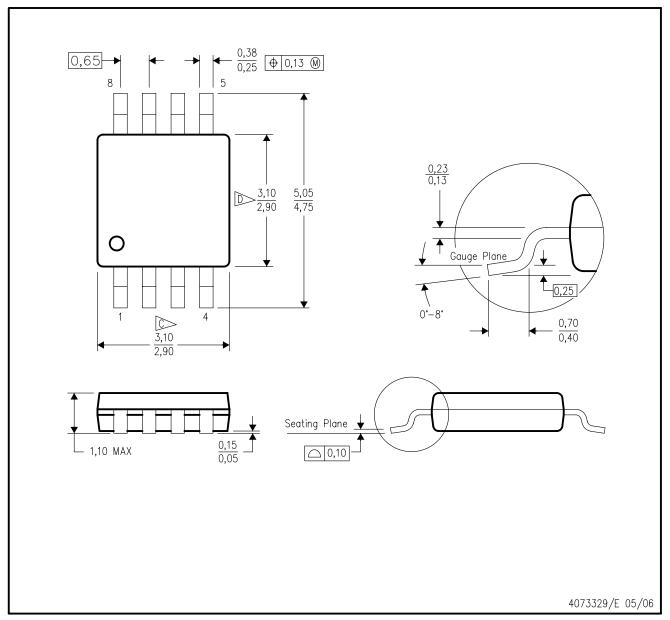

# DGK (S-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

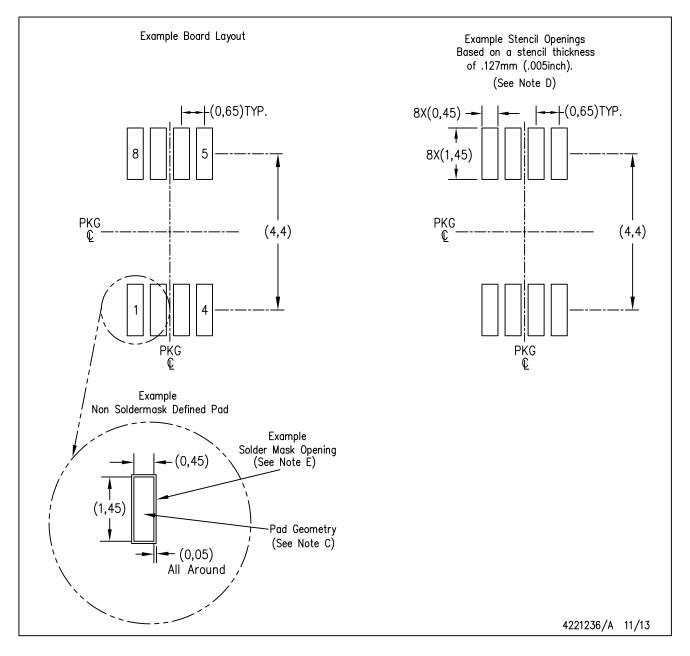

# DGK (S-PDSO-G8)

# PLASTIC SMALL OUTLINE PACKAGE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated