www.tij.co.jp JAJSBX3

## 超低消費電力、レール・ツー・レール出力、完全差動アンプ

## 特長

● 1超低消費電力:

- 電圧: 2.5V~5.5V

ー 電流 : 250μA

- パワーダウン・モード: 0.5μA (標準)

● 完全差動アーキテクチャ

● 帯域幅:36MHz

スルー・レート: 200V/µs

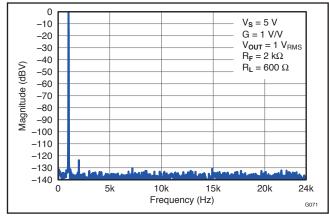

• THD: 1kHz $\tilde{C}$ -120dBc ( $1V_{RMS}$ ,  $R_L = 2k\Omega$ )

● 入力電圧ノイズ: 10nV/√Hz (f = 1kHz)

● 高いDC精度:

$-VOS:\pm100\mu V$

- VOSFリフト:  $\pm 3\mu$ V/°C (-40°C∼+125°C)

- AOL: 114dB

● レール・ツー・レール出力(RRO)

● 負レール入力 (NRI)

● 出力同相モード制御

## アプリケーション

- 低消費電力SAR、Δ∑ ADCドライバ

- 低消費電力、高性能:

- 差動-差動アンプ

- ー シングルエンド 差動アンプ

- 低消費電力、広帯域差動ドライバ

- 低消費電力、広帯域差動信号調整

- 多チャネルおよび高電力密度のシステム

## 概要

THS4531Aは、低消費電力の完全差動オペアンプであり、負レールを下回る入力同相モード範囲およびレール・ツー・レール出力を特長としています。このデバイスは、消費電力が重要な要件となる低消費電力データ・アクイジション・システムや高密度アプリケーション向けに設計されています。

高精度の出力同相モード制御により、DC結合でA/Dコンバータ (ADC) を駆動できます。この制御に加え、レール・ツー・レール出力、および負レールを下回る入力同相モード範囲により、2.5V~5Vの単一電源のみを使用して、シングルエンドのグランド基準信号源から逐次比較型 (SAR) およびデルタ・シグマ (AΣ) A/Dコンバータへのインターフェイスを容易に実現できます。THS4531Aは、汎用の低消費電力差動信号調整アプリケーションに対しても貴重なツールとなります。

THS4531Aは、-40°C~+125°Cの拡張工業用温度範囲全体にわたって仕様が規定されています。以下のパッケージ・オプションが用意されています。

- 8ピンSOIC (MSOP) およびVSSOP (DおよびDGK)

- 10ピンWQFN (RUN)

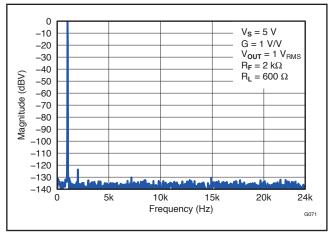

図 1. オーディオ・アナライザでの1kHz FFTプロット

表 1. 関連製品

| デバイス    | 帯域幅(MHz) | I <sub>Q</sub> (mA) | 100kHzでの<br>THD(dBc) | $V_N$ (nV/ $\sqrt{Hz}$ ) | レール・ツー・レール |

|---------|----------|---------------------|----------------------|--------------------------|------------|

| THS4521 | 145      | 1.14                | -120                 | 4.6                      | Out        |

| THS4520 | 570      | 15.3                | -114                 | 2                        | Out        |

| THS4121 | 100      | 16                  | <b>–</b> 79          | 5.4                      | In/Out     |

| THS4131 | 150      | 16                  | -107                 | 1.3                      | No         |

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的 参考資料としてご使用下さい。

参考員れていてこまれいでい。 製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確 認下さい

Tlおよび日本Tlは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLOS823A 翻訳版

# 静電気放電対策

ESDはこの集積回路にダメージを与えることがあります。テキサス・インスツルメンツ社は、全ての集積回路に適切なESD対策が行われることを推奨します。この適切な取扱いや取付け手順が守られない場合には、素子にダメージを与えることがあります。

ESDが与えるダメージには、素子へ微妙な性能劣化から完全な素子故障まで様々な症状に及びます。非常に些細なパラメータの変化でもその素子の仕様を満足しなくなることがあり、高詳細な集積回路はさらにESDによる影響を受けやすい場合があります。

## パッケージ/注文情報(1)

| 製品名      | チャネル数 | パッケージ-<br>リード | パッケージ・<br>コード     | 規定温度範囲        | パッケージ捺印     | 発注型番          | 出荷形態、数量      |     |     |     |     |     |     |               |      |               |              |

|----------|-------|---------------|-------------------|---------------|-------------|---------------|--------------|-----|-----|-----|-----|-----|-----|---------------|------|---------------|--------------|

|          | 1     | SOIC-8        | D                 | -40°C ∼+125°C | T4531A      | THS4531AID    | レール、75       |     |     |     |     |     |     |               |      |               |              |

|          | 1     | 3010-6        | D =40 C 13 +125 C | T4531A        | THS4531AIDR | テープ・リール、2500  |              |     |     |     |     |     |     |               |      |               |              |

| TUCAFOLA | 1     | Vecop o       | DOK               | 4000 .40500   | 531A        | THS4531AIDGK  | レール、80       |     |     |     |     |     |     |               |      |               |              |

| THS4531A | 1     | VSSOP-8       | DGK               | DGK           | DGK         | DGK           | DGK          | DGK | DGK | DGK | DGK | DGK | DGK | –40°C ∼+125°C | 531A | THS4531AIDGKR | テープ・リール、2500 |

|          | 1     | WOEN 10       | DUN               | 40°C 10E°C    | 531A        | THS4531AIRUNT | テープ・リール、250  |     |     |     |     |     |     |               |      |               |              |

|          | 1     | WQFN-10       | RUN               | –40°C ∼+125°C | 531A        | THS4531AIRUNR | テープ・リール、3000 |     |     |     |     |     |     |               |      |               |              |

<sup>(1)</sup> 最新のパッケージおよびご発注情報については、このデータシートの巻末にある「付録:パッケージ・オプション」を参照するか、TIのWebサイト(www.ti.comまたはwww.tij.co.jp)をご覧ください。

## 絶対最大定格

|                                |                                                                         | VALUE                                | UNITS |

|--------------------------------|-------------------------------------------------------------------------|--------------------------------------|-------|

| Supply voltage, V <sub>S</sub> | _ to V <sub>S+</sub>                                                    | 5.5                                  |       |

| Input/output voltag            | e, $V_{\text{IN}\pm}$ , $V_{\text{OUT}\pm}$ , and $V_{\text{OCM}}$ pins | $(V_{S-}) - 0.7 \sim (V_{S+}) + 0.7$ | V     |

| Differential input vo          | oltage, V <sub>ID</sub>                                                 | 1                                    | V     |

| Continuous output              | current, I <sub>O</sub>                                                 | 50                                   | mA    |

| Continuous input of            | urrent, I <sub>i</sub>                                                  | 0.75                                 |       |

| Continuous power               | dissipation                                                             | See Thermal Information              |       |

| Maximum junction               | temperature, T <sub>J</sub>                                             | 150                                  | °C    |

| Operating free-air             | temperature range, T <sub>A</sub>                                       | −40 ~ +125                           | °C    |

| Storage temperatu              | Storage temperature range, $T_{stq}$ = -65 $\sim$ +150                  |                                      | °C    |

| Electrostatic                  | Human body model (HBM)                                                  | 3                                    | kV    |

| discharge (ESD) ratings:       | Charge device model (CDM)                                               | 500                                  | V     |

## 熱特性について

|                               |                                              | THS4531A    | THS4531A                 | THS4531A      |        |

|-------------------------------|----------------------------------------------|-------------|--------------------------|---------------|--------|

| THERMAL METRIC <sup>(1)</sup> |                                              | SOIC<br>(P) | VSSOP<br>(MSOP)<br>(DGK) | WQFN<br>(RUN) | UNITS  |

|                               |                                              | 8 PINS      | 8 PINS                   | 10 PINS       |        |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance       | 133         | 198                      | 163           |        |

| $\theta_{JCtop}$              | Junction-to-case (top) thermal resistance    | 78          | 84                       | 66            |        |

| $\theta_{JB}$                 | Junction-to-board thermal resistance         | 73          | 120                      | 113           | °C/W   |

| ΨЈТ                           | Junction-to-top characterization parameter   | 26          | 19                       | 17            | · C/VV |

| ΨЈВ                           | Junction-to-board characterization parameter | 73          | 118                      | 113           |        |

| $\theta_{JCbot}$              | Junction-to-case (bottom) thermal resistance | N/A         | N/A                      | N/A           |        |

<sup>(1)</sup> 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート 『IC Package Thermal Metrics』(SPRA953)を参照してください。

## 電気的特性: Vs = 2.7V

測定条件: $T_A=25^{\circ}C$ 、 $V_{S+}=2.7V$ 、 $V_{S-}=0V$ 、 $V_{OCM}=オープン$ 、 $V_{OUT}=2V_{PP}$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準(特に記述のない限り)

| PARAMETER                            | CONDITIONS                                       | MIN TYP MA | X UNITS            | TEST<br>LEVEL |

|--------------------------------------|--------------------------------------------------|------------|--------------------|---------------|

| AC PERFORMANCE                       |                                                  |            |                    |               |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 1  | 34         |                    |               |

| Cmall signal bandwidth               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 2  | 16         | MHz                |               |

| Small-signal bandwidth               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 5  | 6          | IVITZ              |               |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 2.7        |                    |               |

| Gain-bandwidth product               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 27         | MHz                |               |

| Large-signal bandwidth               | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 34         | MHz                |               |

| Bandwidth for 0.1-dB flatness        | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 12         | MHz                |               |

| Slew rate, rise/fall, 25% to 75%     |                                                  | 190/320    | V/μs               |               |

| Rise/fall time, 10% to 90%           |                                                  | 5.2/6.1    | ns                 |               |

| Settling time to 1%, rise/fall       | V <sub>OUT</sub> = 2-V step                      | 25/20      |                    |               |

| Settling time to 0.1%, rise/fall     |                                                  | 60/60      | ns                 |               |

| Settling time to 0.01%, rise/fall    |                                                  | 150/110    | ns                 |               |

| Overshoot/undershoot, rise/fall      |                                                  | 1/1        | %                  |               |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -122       |                    | 0             |

| 2nd-order harmonic distortion        | f = 10 kHz                                       | -127       | dBc                | С             |

|                                      | f = 1 MHz                                        | -59        |                    |               |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -130       |                    |               |

| 3rd-order harmonic distortion        | f = 10 kHz                                       | -135       | dBc                |               |

|                                      | f = 1 MHz                                        | -70        |                    |               |

| 2nd-order intermodulation distortion | f = 1 MHz, 200-kHz tone spacing,                 | -83        | dD-                |               |

| 3rd-order intermodulation distortion | V <sub>OUT</sub> envelope = 2 V <sub>PP</sub>    | -81        | dBc                |               |

| Input voltage noise                  | f = 1 kHz                                        | 10         | nV/√ <del>Hz</del> |               |

| Voltage noise 1/f corner frequency   |                                                  | 45         | Hz                 |               |

| Input current noise                  | f = 100 kHz                                      | 0.25       | pA/√ <del>Hz</del> |               |

| Current noise 1/f corner frequency   |                                                  | 6.5        | kHz                |               |

| Overdrive recovery time              | Overdrive = 0.5 V                                | 65         | ns                 |               |

| Output balance error                 | V <sub>OUT</sub> = 100 mV, f = 1 MHz             | -65        | dB                 |               |

| Closed-loop output impedance         | f = 1 MHz (differential)                         | 2.5        | Ω                  |               |

## 電気的特性: Vs = 2.7V

測定条件: $T_A=25^\circ\text{C}$ 、 $V_{S^+}=2.7V$ 、 $V_{S^-}=0V$ 、 $V_{OCM}=オープン$ 、 $V_{OUT}=2V_{PP}$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準(特に記述のない限り)

| PARAMETER                                 | CONDITIONS                                             | MIN                   | TYP                    | MAX                   | UNITS    | TEST<br>LEVEL |

|-------------------------------------------|--------------------------------------------------------|-----------------------|------------------------|-----------------------|----------|---------------|

| DC PERFORMANCE                            |                                                        |                       |                        |                       |          |               |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                        | 100                   | 113                    |                       | dB       | Α             |

|                                           | T <sub>A</sub> = +25°C                                 |                       | ±100                   | ±400                  |          | Α             |

|                                           | $T_A = 0$ °C $\sim$ +70°C                              |                       |                        | ±715                  |          |               |

| Input-referred offset voltage             | $T_A = -40$ °C $\sim +85$ °C                           |                       |                        | ±855                  | μV       | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                       |                        | ±1300                 |          |               |

|                                           | $T_A = 0$ °C $\sim$ +70°C                              |                       | ±2                     | ±7                    |          |               |

| Input offset voltage drift <sup>(1)</sup> | $T_A = -40$ °C $\sim +85$ °C                           |                       | ±2                     | ±7                    | μV/°C    | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                       | ±3                     | ±9                    |          |               |

|                                           | T <sub>A</sub> = +25°C                                 |                       | 200                    | 250                   |          | Α             |

| Investigation accounts                    | $T_A = 0$ °C $\sim +70$ °C                             |                       |                        | 275                   | 4        |               |

| Input bias current                        | $T_A = -40^{\circ}C \sim +85^{\circ}C$                 |                       |                        | 286                   | nA       | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                       |                        | 305                   |          |               |

|                                           | T <sub>A</sub> = 0°C ~+70°C                            |                       | 0.45                   | 0.55                  |          |               |

| Input bias current drift <sup>(1)</sup>   | $T_A = -40^{\circ}C \sim +85^{\circ}C$                 |                       | 0.45                   | 0.55                  | nA/°C    | В             |

| •                                         | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                       | 0.45                   | 0.55                  |          |               |

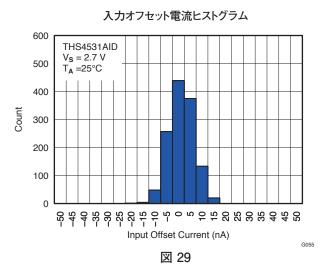

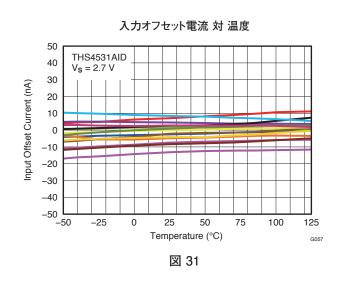

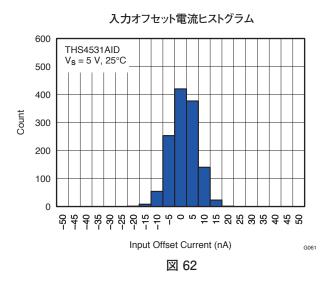

|                                           | T <sub>A</sub> = +25°C                                 |                       | ±5                     | ±50                   |          | Α             |

|                                           | $T_A = 0$ °C $\sim +70$ °C                             |                       |                        | ±55                   |          |               |

| Input offset current                      | $T_A = -40^{\circ}C \sim +85^{\circ}C$                 |                       |                        | ±57                   | nA       | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                       |                        | ±60                   |          |               |

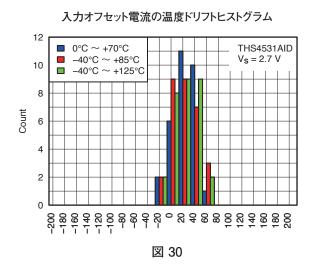

|                                           | $T_A = 0$ °C $\sim +70$ °C                             |                       | ±0.03                  | ±0.1                  | nA/°C    |               |

| Input offset current drift <sup>(1)</sup> | $T_A = -40^{\circ}C \sim +85^{\circ}C$                 |                       | ±0.03                  | ±0.1                  |          | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                       | ±0.03                  | ±0.1                  |          |               |

| INPUT                                     |                                                        | <u>'</u>              |                        |                       | 1        |               |

|                                           | T <sub>A</sub> = +25°C, CMRR > 87 dB                   |                       | V <sub>S-</sub> - 0.2  | V <sub>S-</sub>       | .,       | Α             |

| Common-mode input low                     | $T_A = -40^{\circ}C \sim +125^{\circ}C$ , CMRR > 87 dB |                       | V <sub>S-</sub> - 0.2  | V <sub>S</sub> _      | V        | В             |

|                                           | T <sub>A</sub> = +25°C, CMRR > 87 dB                   | V <sub>S+</sub> - 1.2 | V <sub>S+</sub> – 1.1  |                       | .,       | Α             |

| Common-mode input high                    | $T_A = -40^{\circ}C \sim +125^{\circ}C$ , CMRR > 87 dB | V <sub>S+</sub> - 1.2 |                        |                       | V        | В             |

| Common-mode rejection ratio               |                                                        | 90                    | 116                    |                       | dB       | Α             |

| Input impedance common-mode               |                                                        |                       | 200 II 1.2             |                       |          | С             |

| Input impedance differential mode         |                                                        |                       | 200    1               |                       | kΩ II pF | С             |

| OUTPUT                                    |                                                        |                       |                        |                       | I .      |               |

|                                           | T <sub>A</sub> = +25°C                                 |                       | V <sub>S-</sub> + 0.06 | V <sub>S-</sub> + 0.2 | .,       | Α             |

| Single-ended output voltage: low          | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                       | V <sub>S-</sub> + 0.06 | V <sub>S-</sub> + 0.2 | V        | В             |

| Cinale anded output vallence high         | T <sub>A</sub> = +25°C                                 | V <sub>S+</sub> - 0.2 | V <sub>S+</sub> - 0.11 |                       |          | Α             |

| Single-ended output voltage: high         | $T_A = -40^{\circ}C \sim +125^{\circ}C$                | V <sub>S+</sub> - 0.2 | V <sub>S+</sub> - 0.11 |                       | V        | В             |

| Output saturation voltage: high/low       |                                                        |                       | 110/60                 |                       | mV       | С             |

|                                           | T <sub>A</sub> = +25°C                                 | ±15                   | ±22                    |                       | _        | Α             |

| Linear output current drive               | $T_A = -40^{\circ}C \sim +125^{\circ}C$                | ±15                   |                        |                       | mA       | В             |

<sup>(1)</sup> 入力オフセット電圧ドリフト、入力バイアス電流ドリフト、および入力オフセット電流ドリフトは、端点での測定データから計算された平均値であり、それらの差を求めてから温度範囲で割ったものです。

## 電気的特性: Vs = 2.7V

測定条件: $T_A=25^\circ\text{C}$ 、 $V_{S^+}=2.7V$ 、 $V_{S^-}=0V$ 、 $V_{OCM}=オープン$ 、 $V_{OUT}=2V_{PP}$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準(特に記述のない限り)

| PARAMETER                                                          | CONDITIONS                                                                                 | MIN  | TYP            | MAX  | UNITS    | TEST<br>LEVEL |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|----------------|------|----------|---------------|

| POWER SUPPLY                                                       |                                                                                            |      |                |      |          |               |

| Specified operating voltage                                        |                                                                                            | 2.5  |                | 5.5  | V        | В             |

| Quiescent operating current/ch                                     | $T_A = +25$ °C, $\overline{PD} = V_{S+}$                                                   |      | 230            | 330  |          | Α             |

| Quiescent operating current/cri                                    | $T_A = -40$ °C $\sim +125$ °C, $\overline{PD} = V_{S+}$                                    |      | 270            | 370  | μΑ       | В             |

| Power-supply rejection (PSRR)                                      |                                                                                            | 87   | 108            |      | dB       | Α             |

| POWER DOWN                                                         |                                                                                            |      |                |      |          |               |

| Enable voltage threshold                                           | Specified on above 2.1 V                                                                   |      |                | 2.1  | V        | Α             |

| Disable voltage threshold                                          | Specified off below 0.7 V                                                                  | 0.7  |                |      |          | Α             |

| Disable pin bias current                                           | $\overline{PD} = V_{S-} + 0.5 \text{ V}$                                                   |      | 50             | 500  | nA       | Α             |

| Power-down quiescent current                                       | $\overline{PD} = V_{S-} + 0.5 \text{ V}$                                                   |      | 0.5            | 2    | μΑ       | Α             |

| Turn-on time delay                                                 | Time from $\overline{PD}$ = high to $V_{OUT}$ = 90% of final value, $R_L$ = 200 $\Omega$   |      | 650            |      |          | 0             |

| Turn-off time delay                                                | Time from $\overline{PD}$ = low to $V_{OUT}$ = 10% of original value, $R_L$ = 200 $\Omega$ |      | 20             |      | ns       | С             |

| OUTPUT COMMON-MODE VOLT                                            | AGE CONTROL (V <sub>OCM</sub> )                                                            |      |                |      |          |               |

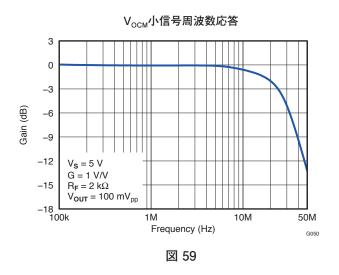

| Small-signal bandwidth                                             | V <sub>OCM</sub> input = 100 mV <sub>PP</sub>                                              |      | 23             |      | MHz      | С             |

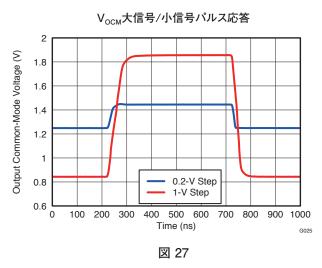

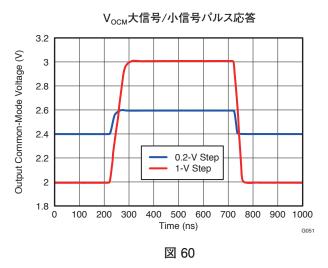

| Slew rate                                                          | V <sub>OCM</sub> input = 1 V <sub>STEP</sub>                                               |      | 14             |      | V/µs     | С             |

| Gain                                                               |                                                                                            | 0.99 | 0.996          | 1.01 | V/V      | Α             |

| Common-mode offset voltage                                         | Offset = output common-mode voltage – V <sub>OCM</sub> input voltage                       |      | ±1             | ±5   | mV       | Α             |

| V <sub>OCM</sub> input bias current                                | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                            |      | ±20            | ±100 | nA       | Α             |

| V <sub>OCM</sub> input voltage range                               |                                                                                            | 0.8  | 0.75 to<br>1.9 | 1.75 | V        | Α             |

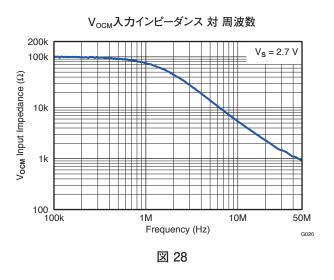

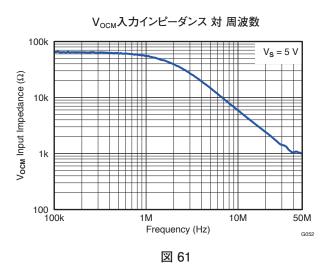

| V <sub>OCM</sub> input impedance                                   |                                                                                            |      | 100 II 1.6     |      | kΩ II pF | С             |

| Default voltage offset from (V <sub>S+</sub> – V <sub>S-</sub> )/2 | Offset = output common-mode voltage – (V <sub>S+</sub> – V <sub>S-</sub> )/2               |      | ±3             | ±10  | mV       | Α             |

## 電気的特性: Vs = 5V

測定条件:  $T_A=25^{\circ}C$ 、 $V_{S^+}=5V$ 、 $V_{S^-}=0V$ 、 $V_{OCM}=オープン$ 、 $V_{OUT}=2V_{PP}$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準(特に記述のない限り)

| PARAMETER                            | CONDITIONS                                       | MIN TYP | MAX UNITS | TEST<br>LEVEL |

|--------------------------------------|--------------------------------------------------|---------|-----------|---------------|

| AC PERFORMANCE                       |                                                  |         |           |               |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 1  | 36      |           |               |

| Cmall signal bandwidth               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 2  | 17      | MHz       |               |

| Small-signal bandwidth               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 5  | 6       | IVITZ     |               |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 2.7     |           |               |

| Gain-bandwidth product               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 27      | MHz       |               |

| Large-signal bandwidth               | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 36      | MHz       |               |

| Bandwidth for 0.1-dB flatness        | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 15      | MHz       |               |

| Slew rate, rise/fall, 25% to 75%     |                                                  | 220/390 | V/μs      |               |

| Rise/fall time, 10% to 90%           |                                                  | 4.6/5.6 | ns        |               |

| Settling time to 1%, rise/fall       | V 0 V                                            | 25/20   | ns        |               |

| Settling time to 0.1%, rise/fall     | V <sub>OUT</sub> = 2 V <sub>Step</sub>           | 60/60   | ns        |               |

| Settling time to 0.01%, rise/fall    |                                                  | 150/110 | ns        |               |

| Overshoot/undershoot, rise/fall      |                                                  | 1/1     | %         |               |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -122    |           |               |

| 2nd-order harmonic distortion        | f = 10 kHz                                       | -128    | dBc       | С             |

|                                      | f = 1 MHz                                        | -60     |           |               |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -130    |           |               |

| 3rd-order harmonic distortion        | f = 10 kHz                                       | -137    | dBc       |               |

|                                      | f = 1 MHz                                        | -71     |           |               |

| 2nd-order intermodulation distortion | f = 1 MHz, 200-kHz tone spacing,                 | -85     | dBc       |               |

| 3rd-order intermodulation distortion | V <sub>OUT</sub> envelope = 2 V <sub>PP</sub>    | -83     | UDC       |               |

| Input voltage noise                  | f = 1 kHz                                        | 10      | nV/√Hz    |               |

| Voltage noise 1/f corner frequency   |                                                  | 45      | Hz        |               |

| Input current noise                  | f = 100 kHz                                      | 0.25    | pA/√Hz    |               |

| Current noise 1/f corner frequency   |                                                  | 6.5     | kHz       |               |

| Overdrive recovery time              | Overdrive = 0.5 V                                | 65      | ns        |               |

| Output balance error                 | V <sub>OUT</sub> = 100 mV, f = 1 MHz             | -67     | dB        |               |

| Closed-loop output impedance         | f = 1 MHz (differential)                         | 2.5     | Ω         |               |

## 電気的特性: Vs = 5V

測定条件:  $T_A=25^{\circ}C$ 、 $V_{S^+}=5V$ 、 $V_{S^-}=0V$ 、 $V_{OCM}=オープン$ 、 $V_{OUT}=2V_{PP}$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準(特に記述のない限り)

| PARAMETER                                 | CONDITIONS                                             | MIN                    | TYP                    | MAX                   | UNITS       | TEST<br>LEVEL |

|-------------------------------------------|--------------------------------------------------------|------------------------|------------------------|-----------------------|-------------|---------------|

| DC PERFORMANCE                            |                                                        | ·                      |                        |                       |             |               |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                        | 100                    | 114                    |                       | dB          | Α             |

|                                           | $T_A = +25^{\circ}C$                                   |                        | ±100                   | ±400                  |             | Α             |

| Input referred effect voltage             | $T_A = 0$ °C $\sim +70$ °C                             |                        |                        | ±715                  | \/          |               |

| Input-referred offset voltage             | $T_A = -40$ °C $\sim +85$ °C                           |                        |                        | ±855                  | μV          | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                        |                        | ±1300                 |             |               |

|                                           | $T_A = 0$ °C $\sim +70$ °C                             |                        | ±2                     | ±7                    |             |               |

| Input offset voltage drift <sup>(1)</sup> | $T_A = -40$ °C $\sim +85$ °C                           |                        | ±2                     | ±7                    | μV/°C       | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                        | ±3                     | ±9                    |             |               |

|                                           | $T_A = +25^{\circ}C$                                   |                        | 200                    | 250                   |             | Α             |

| Input bigg gurrant                        | $T_A = 0$ °C $\sim +70$ °C                             |                        |                        | 279                   | <b>π</b> Λ  |               |

| Input bias current                        | $T_A = -40$ °C $\sim +85$ °C                           |                        |                        | 292                   | nA          | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                        |                        | 315                   |             |               |

|                                           | $T_A = 0$ °C $\sim +70$ °C                             |                        | 0.5                    | 0.65                  |             |               |

| Input bias current drift <sup>(1)</sup>   | $T_A = -40$ °C $\sim +85$ °C                           |                        | 0.5                    | 0.65                  | nA/°C       | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                        | 0.5                    | 0.65                  |             |               |

|                                           | T <sub>A</sub> = +25°C                                 |                        | ±5                     | ±50                   |             | Α             |

|                                           | $T_A = 0$ °C $\sim +70$ °C                             |                        |                        | ±55                   |             |               |

| Input offset current                      | $T_A = -40$ °C $\sim +85$ °C                           |                        |                        | ±57                   | nA          | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                        |                        | ±60                   |             |               |

|                                           | $T_A = 0$ °C $\sim +70$ °C                             |                        | ±0.03                  | ±0.1                  |             |               |

| Input offset current drift <sup>(1)</sup> | $T_A = -40^{\circ}C \sim +85^{\circ}C$                 |                        | ±0.03                  | ±0.1                  | nA/°C       | В             |

|                                           | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                        | ±0.03                  | ±0.1                  |             |               |

| INPUT                                     |                                                        | 1                      |                        |                       |             |               |

| O                                         | $T_A = +25^{\circ}C$ , CMRR > 87 dB                    |                        | V <sub>S-</sub> - 0.2  | V <sub>S-</sub>       |             | Α             |

| Common-mode input: low                    | $T_A = -40^{\circ}C \sim +125^{\circ}C$ , CMRR > 87 dB |                        | V <sub>S-</sub> - 0.2  | V <sub>S-</sub>       | V           | В             |

| O                                         | $T_A = +25^{\circ}C$ , CMRR > 87 dB                    | V <sub>S+</sub> - 1.2  | V <sub>S+</sub> -1.1   |                       |             | Α             |

| Common-mode input: high                   | $T_A = -40^{\circ}C \sim +125^{\circ}C$ , CMRR > 87 dB | V <sub>S+</sub> - 1.2  | V <sub>S+</sub> -1.1   |                       | V           | В             |

| Common-mode rejection ratio               |                                                        | 90                     | 116                    |                       | dB          | Α             |

| Input impedance common-mode               |                                                        |                        | 200 II 1.2             |                       | 1:0 II :- E | С             |

| Input impedance differential mode         |                                                        |                        | 200 II 1               |                       | kΩ II pF    | С             |

| OUTPUT                                    |                                                        | 1                      |                        |                       |             |               |

| Linear autority with the last             | T <sub>A</sub> = +25°C                                 |                        | V <sub>S-</sub> + 0.1  | V <sub>S-</sub> + 0.2 |             | Α             |

| Linear output voltage: low                | $T_A = -40^{\circ}C \sim +125^{\circ}C$                |                        | V <sub>S-</sub> + 0.1  | V <sub>S-</sub> + 0.2 |             | В             |

|                                           | T <sub>A</sub> = +25°C                                 | V <sub>S+</sub> - 0.25 | V <sub>S+</sub> - 0.12 |                       | V           | Α             |

| Linear output voltage: high               | $T_A = -40^{\circ}C \sim +125^{\circ}C$                | V <sub>S+</sub> - 0.25 | V <sub>S+</sub> - 0.12 |                       |             | В             |

| Output saturation voltage: high/low       |                                                        |                        | 120/100                |                       | mV          | С             |

| Lineau autorit autorita                   | T <sub>A</sub> = +25°C                                 | ±15                    | ±25                    |                       | A           | Α             |

| Linear output current drive               | $T_A = -40^{\circ}C \sim +125^{\circ}C$                | ±15                    |                        |                       | mA          | В             |

## 電気的特性: Vs = 5V

測定条件:  $T_A=25^{\circ}C$ 、 $V_{S^+}=5V$ 、 $V_{S^-}=0V$ 、 $V_{OCM}=オープン$ 、 $V_{OUT}=2V_{PP}$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準(特に記述のない限り)

| PARAMETER                                                          | CONDITIONS                                                                                 | MIN  | TYP             | MAX  | UNITS    | TEST<br>LEVEL |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-----------------|------|----------|---------------|

| POWER SUPPLY                                                       |                                                                                            |      |                 |      |          |               |

| Specified operating voltage                                        |                                                                                            | 2.5  |                 | 5.5  | V        | В             |

| Ouissant aparating surrent/sh                                      | $T_A = 25^{\circ}C, \overline{PD} = V_{S+}$                                                |      | 250             | 350  | ^        | Α             |

| Quiescent operating current/ch                                     | $T_A = -40$ °C to 125°C, $\overline{PD} = V_{S+}$                                          |      | 290             | 390  | μΑ       | В             |

| Power-supply rejection (PSRR)                                      |                                                                                            | 87   | 108             |      | dB       | Α             |

| POWER DOWN                                                         |                                                                                            |      |                 |      |          |               |

| Enable voltage threshold                                           | Specified on above 2.1 V                                                                   |      |                 | 2.1  | V        | Α             |

| Disable voltage threshold                                          | Specified off below 0.7 V                                                                  | 0.7  |                 |      | V        | Α             |

| Disable pin bias current                                           | $\overline{PD} = V_{S-} + 0.5 \text{ V}$                                                   |      | 50              | 500  | nA       | Α             |

| Power-down quiescent current                                       | $\overline{PD} = V_{S-} + 0.5 \text{ V}$                                                   |      | 0.5             | 2    | μΑ       | Α             |

| Turn-on time delay                                                 | Time from $\overline{PD}$ = high to $V_{OUT}$ = 90% of final value, $R_L$ = 200 $\Omega$   |      | 600             |      |          | С             |

| Turn-off time delay                                                | Time from $\overline{PD}$ = low to $V_{OUT}$ = 10% of original value, $R_L$ = 200 $\Omega$ |      | 15              |      | ns       |               |

| OUTPUT COMMON-MODE VOLT                                            | AGE CONTROL (V <sub>OCM</sub> )                                                            |      |                 |      |          |               |

| Small-signal bandwidth                                             | V <sub>OCM</sub> input = 100 mV <sub>PP</sub>                                              |      | 24              |      | MHz      | С             |

| Slew rate                                                          | V <sub>OCM</sub> input = 1 V <sub>STEP</sub>                                               |      | 15              |      | V/µs     | С             |

| Gain                                                               |                                                                                            | 0.99 | 0.996           | 1.01 | V/V      | Α             |

| Common-mode offset voltage                                         | Offset = output common-mode voltage – V <sub>OCM</sub> input voltage                       |      | ±1              | ±5   | mV       | Α             |

| V <sub>OCM</sub> input bias current                                | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                            |      | ±20             | ±120 | nA       | Α             |

| V <sub>OCM</sub> input voltage range                               |                                                                                            | 0.95 | 0.75 to<br>4.15 | 4.0  | V        | Α             |

| V <sub>OCM</sub> input impedance                                   |                                                                                            |      | 65 II 0.86      |      | kΩ II pF | С             |

| Default voltage offset from (V <sub>S+</sub> – V <sub>S-</sub> )/2 | Offset = output common-mode voltage – (V <sub>S+</sub> – V <sub>S-</sub> )/2               |      | ±3              | ±10  | mV       | Α             |

## デバイス情報

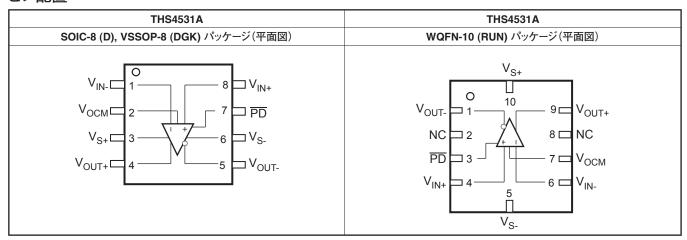

# ピン配置

## ピン機能

| 番号            | 名前                | 説明                                                                                                     |

|---------------|-------------------|--------------------------------------------------------------------------------------------------------|

| THS4531A D, I | OGKパッケー           | - <del></del>                                                                                          |

| 1             | V <sub>IN-</sub>  | 反転(負)出力帰還                                                                                              |

| 2             | V <sub>OCM</sub>  | 同相モード電圧入力                                                                                              |

| 3             | V <sub>S+</sub>   | アンプ正電源入力                                                                                               |

| 4             | V <sub>OUT+</sub> | 非反転アンプ出力                                                                                               |

| 5             | V <sub>OUT</sub>  | 反転アンプ出力                                                                                                |

| 6             | V <sub>S-</sub>   | アンプ負電源入力。注:マルチチャネル・デバイスでは各チャネルのV <sub>S</sub> -が互いに接続されます。                                             |

| 7             | PD                | パワーダウン、 $\overline{PD}$ = Low = 低消費電力モード、 $\overline{PD}$ = High = 通常動作(このピンは常にHighまたはLowに駆動する必要があります) |

| 8             | V <sub>IN+</sub>  | 非反転アンプ入力                                                                                               |

| THS4531A RU   | Nパッケージ            |                                                                                                        |

| 1             | V <sub>OUT</sub>  | 反転アンプ出力                                                                                                |

| 2, 8          | NC                | 内部接続なし                                                                                                 |

| 3             | PD                | パワーダウン、 $\overline{PD}$ = Low = 低消費電力モード、 $\overline{PD}$ = High = 通常動作(このピンは常にHighまたはLowに駆動する必要があります) |

| 4             | V <sub>IN+</sub>  | 非反転アンプ入力                                                                                               |

| 5             | V <sub>S-</sub>   | アンプ負電源入力。注:マルチチャネル・デバイスでは各チャネルのV <sub>S</sub> -が互いに接続されます。                                             |

| 6             | V <sub>IN</sub> _ | 反転アンプ入力                                                                                                |

| 7             | V <sub>OCM</sub>  | 同相モード電圧入力                                                                                              |

| 9             | V <sub>OUT+</sub> | 非反転アンプ出力                                                                                               |

| 10            | V <sub>S+</sub>   | アンプ正電源入力                                                                                               |

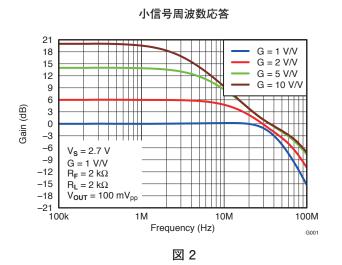

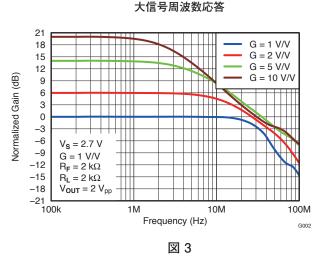

## グラフ一覧

| 説明                                      | $V_{S} = 2.7 V$ | V <sub>S</sub> = 5 V |

|-----------------------------------------|-----------------|----------------------|

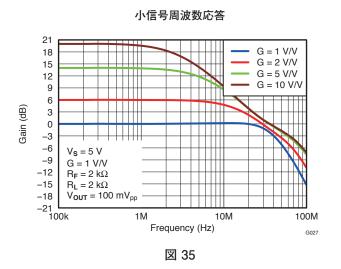

| 小信号周波数応答                                | 図2              | 図35                  |

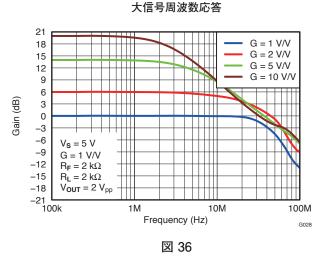

| 大信号周波数応答                                | 図3              | 図36                  |

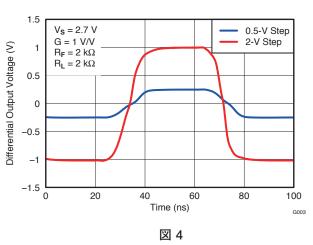

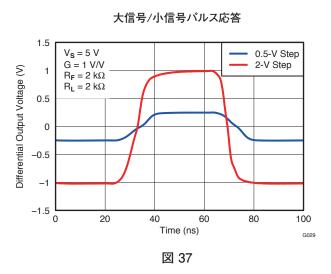

| 大信号/小信号パルス応答                            | 図 4             | 図37                  |

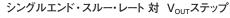

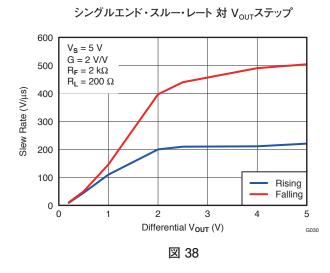

| シングルエンド・スルー・レート 対 V <sub>OUT</sub> ステップ | 図5              | 図38                  |

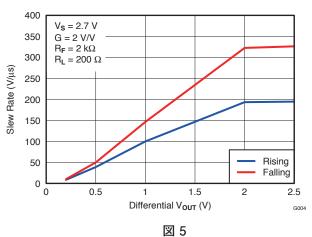

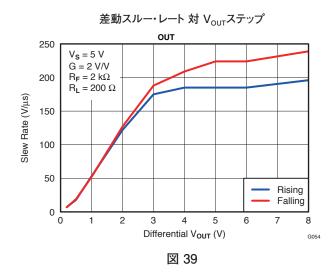

| 差動スルー・レート 対 V <sub>OUT</sub> ステップ       | 図6              | 図39                  |

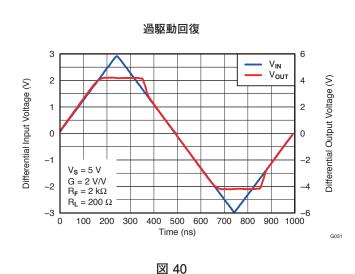

| 過駆動回復                                   | 図7              | 図40                  |

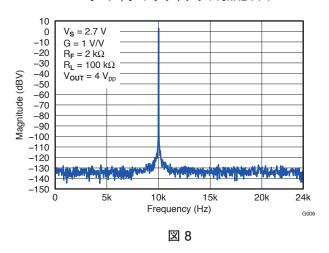

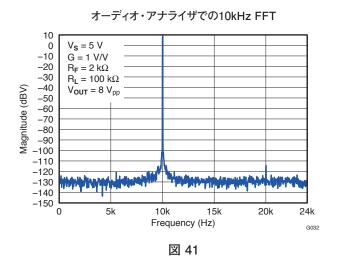

| オーディオ・アナライザでの10kHz FFT                  | 図8              | 図41                  |

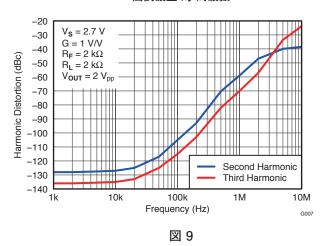

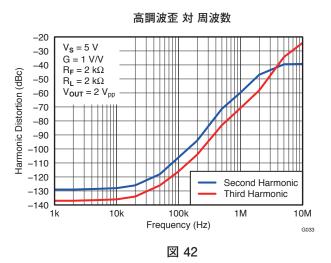

| 高調波歪 対 周波数                              | 図 9             | 図42                  |

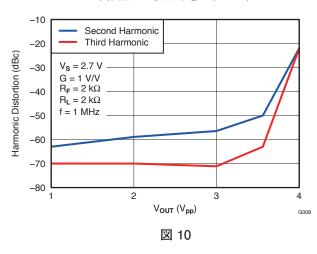

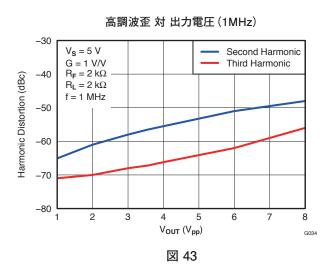

| 高調波歪 対 出力電圧(1MHz)                       | 図10             | 図43                  |

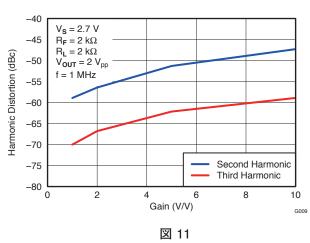

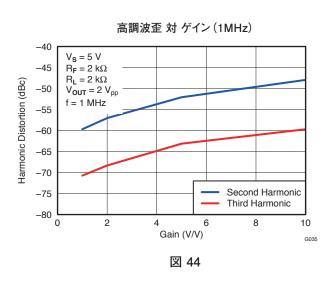

| 高調波歪 対 ゲイン(1MHz)                        | 図11             | 図 44                 |

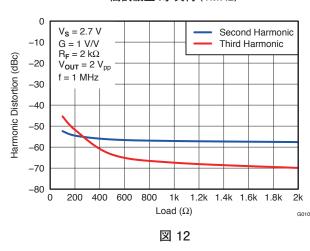

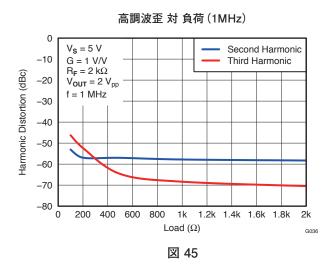

| 高調波歪 対 負荷 (1MHz)                        | 図12             | 図 45                 |

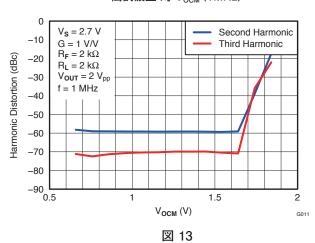

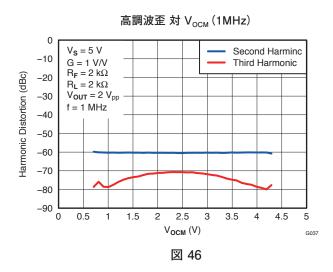

| 高調波歪 対 V <sub>OCM</sub> (1MHz)          | 図13             | 図 46                 |

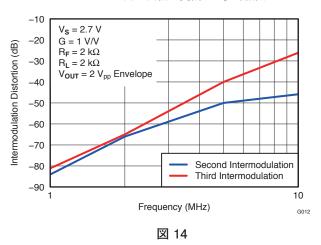

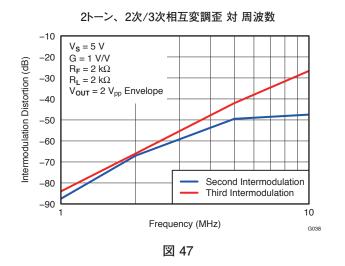

| 2トーン、2次/3次相互変調歪 対 周波数                   | 図14             | 図 47                 |

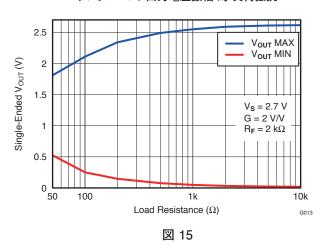

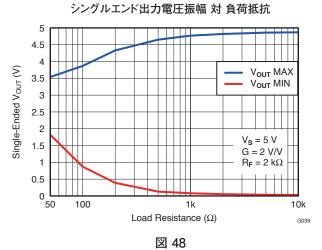

| シングルエンド出力電圧振幅 対 負荷抵抗                    | 図15             | 図 48                 |

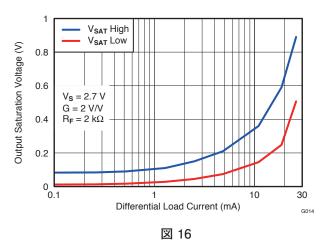

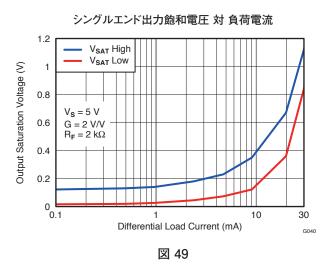

| シングルエンド出力飽和電圧 対 負荷電流                    | 図16             | 図 49                 |

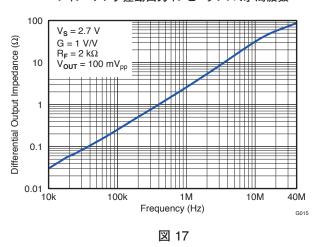

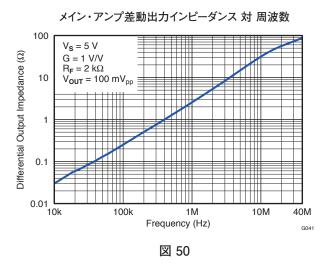

| メイン・アンプ差動出力インピーダンス 対 周波数                | 図17             | 図 50                 |

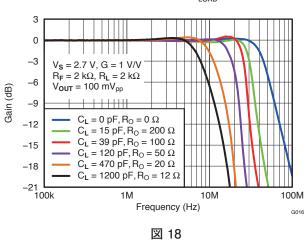

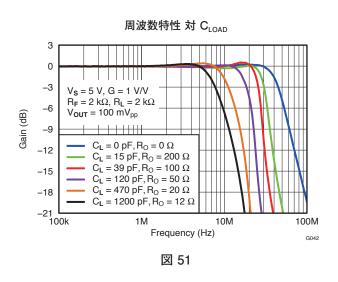

| 周波数応答 対 C <sub>LOAD</sub>               | 図 18            | 図51                  |

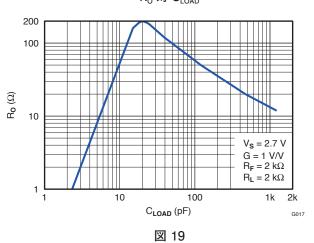

| Ro 対 CLOAD                              | 図 19            | 図52                  |

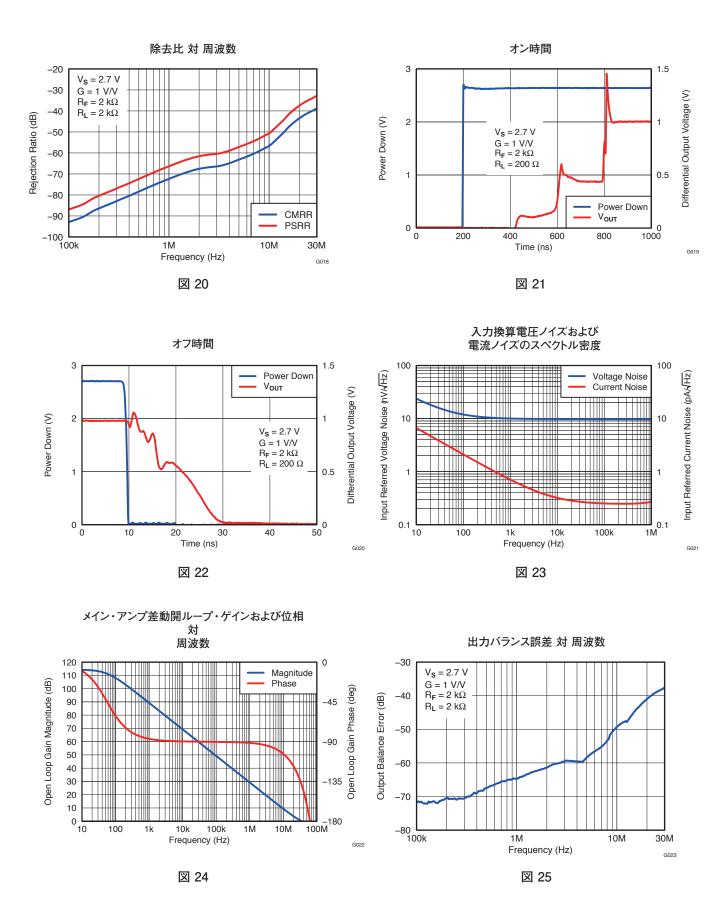

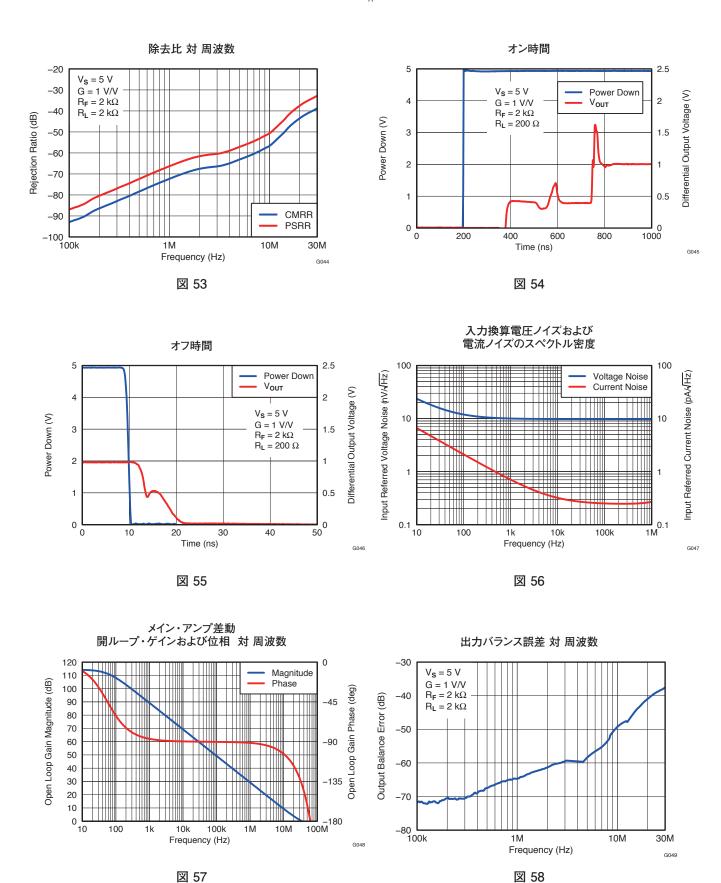

| 除去比 対 周波数                               | 図20             | 図53                  |

| オン時間                                    | 図21             | 図54                  |

| オフ時間                                    | 図22             | 図55                  |

| 入力基準電圧ノイズおよび電流ノイズのスペクトル密度               | 図23             | 図56                  |

| メイン・アンプ差動開ループ・ゲインおよび位相 対 周波数            | 図24             | 図57                  |

| 出力バランス誤差 対 周波数                          | 図25             | 図58                  |

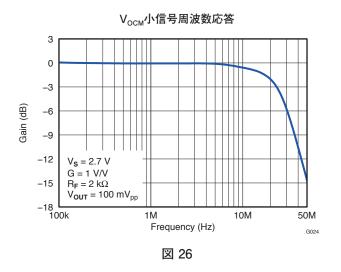

| V <sub>OCM</sub> 小信号周波数応答               | 図26             | 図59                  |

| V <sub>OCM</sub> 大信号/小信号パルス応答           | 図27             | 図 60                 |

| V <sub>OCM</sub> 入力インピーダンス 対 周波数        | 図28             | 図61                  |

| 回数 対 入力オフセット電流                          | 図29             | 図 62                 |

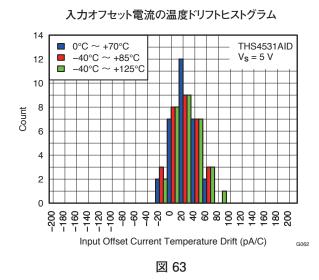

| 回数 対 入力オフセット電流の温度ドリフト                   | 図30             | 図 63                 |

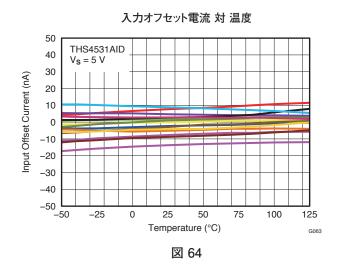

| 入力オフセット電流 対 温度                          | 図31             | 図 64                 |

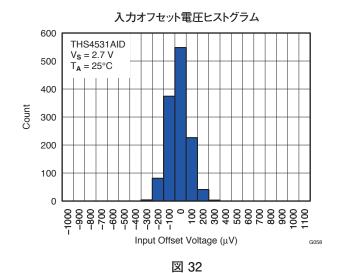

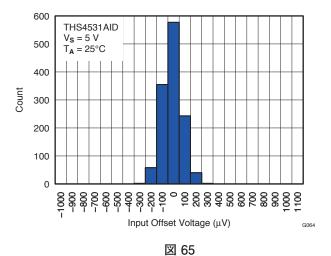

| 回数 対 入力オフセット電圧                          | 図32             | 図 65                 |

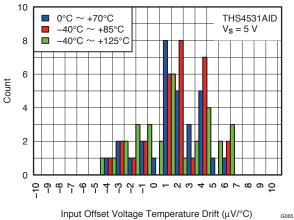

| 回数 対 入力オフセット電圧の温度ドリフト                   | 図33             | 図 66                 |

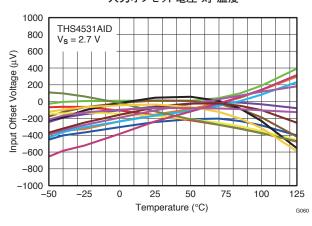

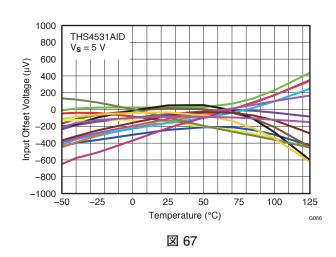

| 入力オフセット電圧 対 温度                          | 図34             | 図 67                 |

測定条件 (特に記述のない限り):  $V_{S+}=2.7V$ 、 $V_{S-}=0V$ 、CM=オープン、 $V_{OUT}=2Vpp$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準 (特に記述のない限り)

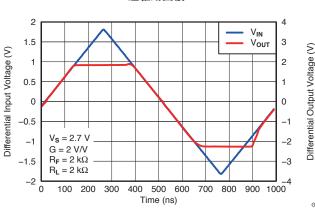

大信号/小信号パルス応答

差動スルー・レート 対 Voutステップ

図 7

G005

測定条件 (特に記述のない限り):  $V_{S+}=2.7V$ 、 $V_{S-}=0V$ 、CM=オープン、 $V_{OUT}=2Vpp$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準 (特に記述のない限り)

#### オーディオ・アナライザでの10kHz FFT

高調波歪 対 周波数

高調波歪 対 出力電圧(1MHz)

高調波歪 対 ゲイン (1MHz)

高調波歪 対 負荷 (1MHz)

高調波歪 対 V<sub>OCM</sub> (1MHz)

測定条件 (特に記述のない限り):  $V_{S+}=2.7V$ 、 $V_{S-}=0V$ 、CM=オープン、 $V_{OUT}=2Vpp$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準 (特に記述のない限り)

#### トーン、2次/3次相互変調歪 対 周波数

#### シングルエンド出力電圧振幅 対 負荷抵抗

#### シングルエンド出力飽和電圧 対 負荷電流

#### メイン・アンプ差動出力インピーダンス 対 周波数

周波数特性 対 CLOAD

R<sub>o</sub>対 C<sub>LOAD</sub>

測定条件 (特に記述のない限り):  $V_{S+}=2.7V$ 、 $V_{S-}=0V$ 、CM=オープン、 $V_{OUT}=2Vpp$ 、 $R_F=2k\Omega$ 、 $R_L=2k\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準 (特に記述のない限り)

##

Input Offset Voltage Temperature Drift (μV/°C)

図 33

#### 入力オフセット電圧 対 温度

図 34

測定条件 (特に記述のない限り):  $V_{S+}=5V$ 、 $V_{S-}=0V$ 、 $V_{OCM}=3$  オープン、 $V_{OUT}=2$ Vpp、 $R_F=2$ k $\Omega$ 、 $R_L=2$ k $\Omega$ 差動、G=1V/V、シングルエンド入力、差動出力、入力および出力は電源中点を基準、 $T_A=25$ °C (特に記述のない限り)

#### 入力オフセット電圧ヒストグラム

#### 入力オフセット電圧の温度ドリフトヒストグラム

図 66

入力オフセット電圧 対 温度

## アプリケーション情報

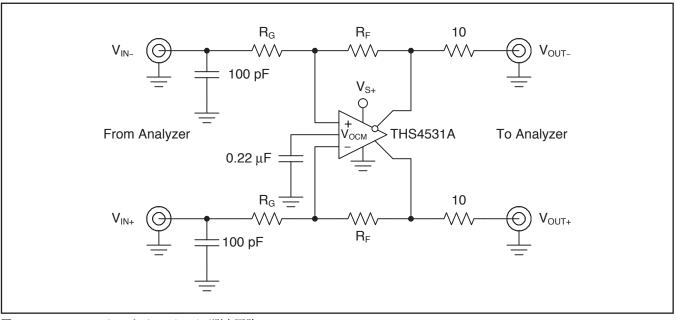

#### 代表的特性の測定用回路

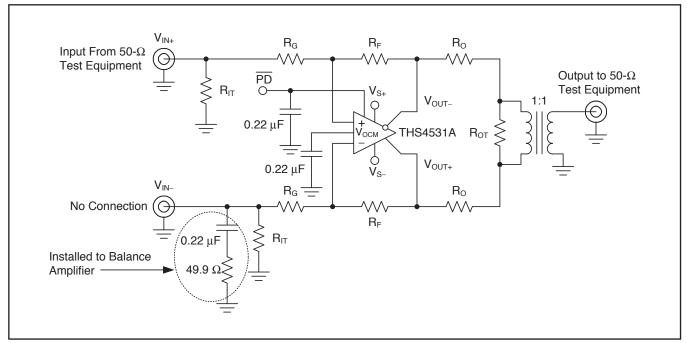

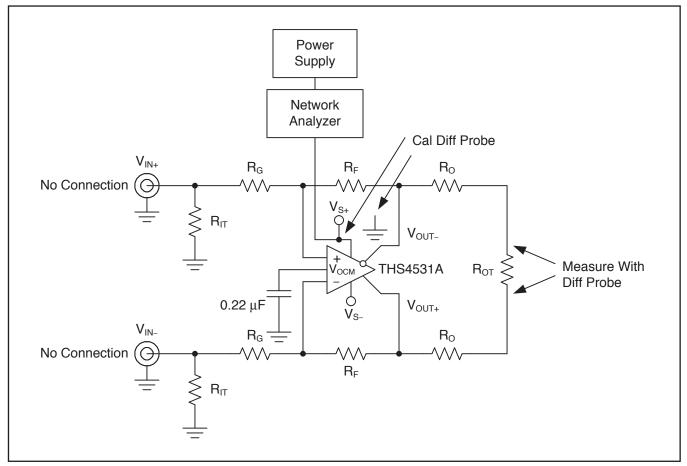

図68に、THS4531Aの特性を測定するために使用した、EVM 上の汎用測定回路を示します。説明を単純にするため、電源デカップリングについては示していません。推奨事項については、「アプリケーション情報」でレイアウトの項を参照してください。部品値は測定条件に応じて変わります。これは表2および表3に示され、また特に記述がある場合はそれに従います。使用した信号発生器の一部はAC結合の50 $\Omega$ ソースです。図に示されるように、回路のバランシングのために、非駆動側すなわち反転入力側で $R_{IT}$ と並列に0.22 $\mu$ Fのコンデンサと49.9 $\Omega$ の抵抗をグランドとの間

に挿入しています。一般的なラボ用試験機器へのインターフェイスを容易にするために両電源を使用していますが、適切なバイアスを加えれば、「アプリケーション情報」に示すようにアンプを単一電源で動作させても性能に影響はありません。ほとんどの試験では、デバイスはシングルエンド入力で、出力ではトランスを使って差動出力をシングルエンドに変換しています。これは、一般的なラボ用試験機器がシングルエンドの入力と出力を持つためです。差動入力および差動出力を使用した場合、性能は同等であるかまたは向上します。

図 68. 汎用測定回路

表 2. シングルエンド入力でのゲイン部品値 (1)

| ゲイン    | R <sub>F</sub> | R <sub>G</sub> | R <sub>IT</sub> |

|--------|----------------|----------------|-----------------|

| 1 V/V  | 2kΩ            | 2kΩ            | 51.1Ω           |

| 2 V/V  | 2kΩ            | 1kΩ            | 52.3Ω           |

| 5 V/V  | 2kΩ            | 392Ω           | $53.6\Omega$    |

| 10 V/V | 2kΩ            | 187kΩ          | 57.6Ω           |

<sup>(1)</sup> 各部品は、ゲインと50Ωの入力終端とを実現できるように選択されています。ここに示す抵抗値は最も近い標準値であるため、ゲインは近似値です。

表 3. 差動-シングルエンド1:1出力トランスを使用する場合の負荷部品値 (1)

| $R_L$       | R <sub>O</sub> | R <sub>OT</sub> | 減衰   |  |  |

|-------------|----------------|-----------------|------|--|--|

| 100Ω        | 25Ω            | open            | 6    |  |  |

| 200Ω        | 86.6Ω          | 69.8Ω           | 16.8 |  |  |

| $499\Omega$ | $237\Omega$    | 56.2Ω           | 25.5 |  |  |

| 1kΩ         | 487Ω           | 52.3Ω           | 31.8 |  |  |

| 2kΩ         | 976Ω           | 51.1Ω           | 37.9 |  |  |

<sup>(1)</sup> 負荷の合計には試験機器による50Ω終端も含まれます。部品は、1:1トランスを通して負荷と50Ωのライン終端とを実現できるように選択されています。ここに示す抵抗値は最も近い標準値であるため、負荷は近似値です。

出力では負荷部品値によって分圧回路が形成されるため、アンプの出力は減衰されます。表3の「減衰」列は、この分圧抵抗回路から予測される減衰を示しています。図68に示すように、出力にトランスを使用する場合には、トランスおよびラインでの損失によって信号の損失が多少大きくなるため、これらの値は近似値です。ほとんどの試験で使用される標準出力負荷は2kΩで、37.9dBの損失が伴います。

#### 周波数応答および出力インピーダンス

図68の回路は、アンプの周波数応答の測定に使用されます。

ネットワーク・アナライザを信号源および測定デバイスとして使用しています。ネットワーク・アナライザの出力インピーダンスは $50\Omega$ で、DC結合されています。 $R_{\rm IT}$ および $R_{\rm G}$ は、 $50\Omega$ に対するインピーダンス・マッチングと適切なゲインが維持されるように選択します。アンプをバランスさせるため、もう一方の入力で $R_{\rm IT}$ に並列に $49.9\Omega$ の抵抗をグランドに対して挿入します。

出力は、 $50\Omega$ の同軸ケーブルを介してネットワーク・アナライザの入力に接続されます。 $2k\Omega$ 負荷の場合、表3に示すように、アンプの出力の減衰分として測定値に37.9dBが付加されます。

出力インピーダンスについては、 $V_{\rm IN}$ がオープンの状態で $V_{\rm OUT}$ に信号を注入します。2個の $R_{\rm o}$ 抵抗での電圧降下を高インピーダンス差動プローブで測定し、アンプの出力におけるインピーダンスの計算に使用します。

#### 歪

1MHz以上では、図68に示す回路を使用して、高調波、相互 変調歪、およびアンプの出力インピーダンスを測定します。

信号発生器を信号源として使用し、スペクトル・アナライザで出力を測定します。信号発生器の出力インピーダンスは $50\Omega$ で、AC結合されています。 $R_{IT}$ および $R_{G}$ は、 $50\Omega$ に対するインピーダンス・マッチングと適切なゲインが維持されるように選択します。アンプをバランスさせるため、もう一方の入力で $R_{IT}$ に並列に $0.22\mu$ Fのコンデンサと $49.9\Omega$ の抵抗をグランドに対して挿入します。信号源で発生する高調波を低減するため、入力と直列にローパス・フィルタを挿入します。基本波のレベルを測定した後、出力にハイパス・フィルタを挿入して基本波を低減します。これは、基本波によってスペクトル・アナライザの入力に歪が生成されないようにするためです。

オーディオ帯域での歪は、オーディオ・アナライザを用いて測定します。詳細については、オーディオ測定の節を参照してください。

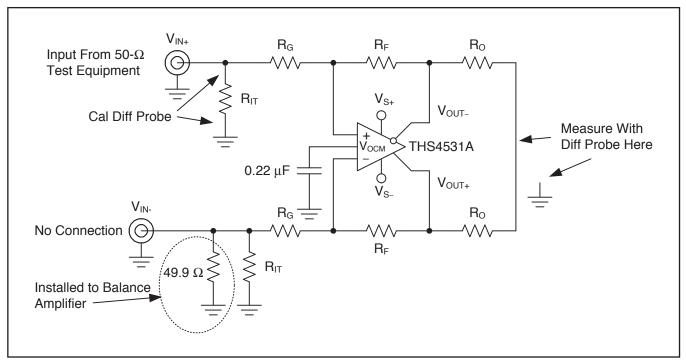

## スルー・レート、過渡応答、セトリング・タイム、過駆動、 出力電圧、オン/オフ時間

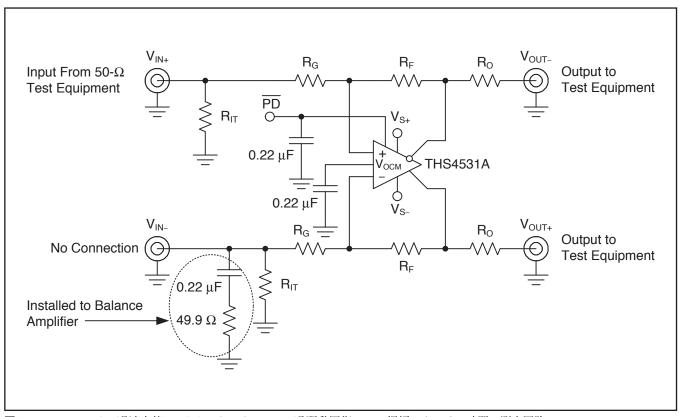

図69の回路は、スルー・レート、過渡応答、セトリング・タイム、過駆動回復、および出力電圧振幅の測定に使用されます。オン時間およびオフ時間は、 $\overline{PD}$ 入力で $50\Omega$ の入力終端によって測定します。この場合、 $0.22\mu$ Fのコンデンサを $49.9\Omega$ の抵抗で置き換えます。

図 69. スルー・レート、過渡応答、セトリング・タイム、 $Z_0$ 、過駆動回復、 $V_{OUT}$ 振幅、オン/オフ時間の測定回路

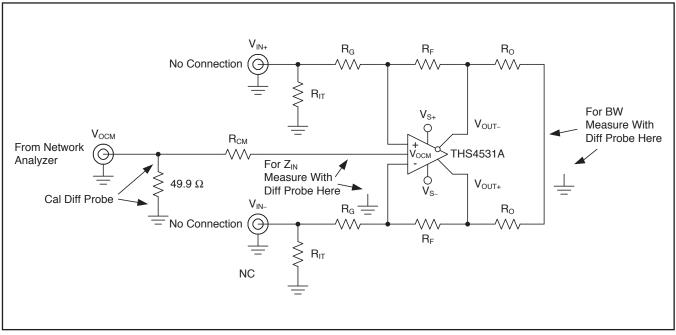

#### 同相モードおよび電源電圧変動除去

図70の回路は、CMRRの測定に使用されます。ネットワーク・アナライザからの信号を同相モードで入力に印加します。

図71は、 $V_{S}$ 、および $V_{S}$ のPSRRの測定に使用されます。電源をネットワーク・アナライザのDCオフセット入力に印加します。CMRR とPSRRの両方について、 $R_{OT}$ と並列に接続した高インピーダンス差動プローブを用いて出力を測定します。

図 70. CMRR測定回路

図 71. PSRR測定回路

## V<sub>OCM</sub>入力

図72の回路は、過渡応答、周波数応答、および $V_{OCM}$ 入力の入力インピーダンスの測定に使用されます。これらの測定では、 $49.9\Omega$ の $V_{OCM}$ 終端抵抗の両端が測定点となります。過渡応答と周波数応答は $R_{CM}=0\Omega$ で測定されます。2個の $R_0$ 抵抗の加算接合部に高インピーダンス差動プローブを使用して、グランド基準で測

定します。入力インピーダンスは、 $V_{\rm OCM}$ ピンで高インピーダンス差動プローブを使用して測定し、 $R_{\rm CM}$ での電圧降下を使用して、アンプの $V_{\rm OCM}$ 入力でのインピーダンスを計算します。

図 72. V<sub>OCM</sub>入力測定回路

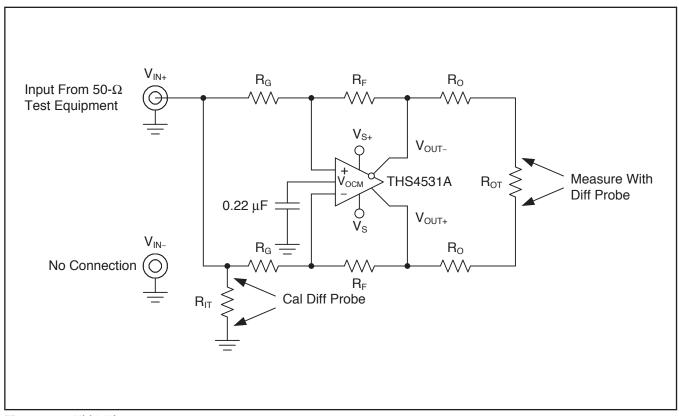

## バランス誤差

図73の回路は、メイン差動アンプのバランス誤差の測定に使用されます。ネットワーク・アナライザを信号源および測定デバイスとして使用しています。ネットワーク・アナライザの出力インピーダンスは50 $\Omega$ で、DC結合されています。 $R_{IT}$ および $R_{G}$ は、 $50\Omega$ に対するインピーダンス・マッチングと適切なゲインが維持されるように選択

します。アンプをバランスさせるため、もう一方の入力で $R_{\rm IT}$ に並列に49.9 $\Omega$ の抵抗をグランドに対して挿入します。出力は、2個の $R_0$ 抵抗の加算接合部に高インピーダンス差動プローブを使用して、グランド基準で測定します。

図 73. バランス誤差測定回路

#### アプリケーション回路

以下の回路は、THS4531Aのアプリケーション情報を示します。 説明を単純にするため、以降の図では電源デカップリング・コン デンサを示していません。推奨されるガイドラインについては、 「EVMおよびレイアウトに関する推奨事項」を参照してください。 完全差動オペアンプの使用方法および動作の詳細については、ア プリケーション・レポート『Fully-Differential Amplifiers』 (SLOA054D)を参照してください。

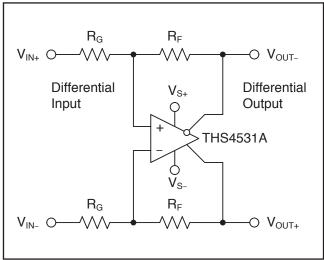

#### 差動入力ー差動出力アンプ

THS4531Aは完全差動オペアンプであり、差動入力信号を差動出力信号へと増幅するために使用できます。回路の基本的なブロック図を図74に示します( $V_{\rm OCM}$ および $\overline{\rm PD}$ 入力は示されていません)。回路のゲインは $R_{\rm F}$ を $R_{\rm G}$ で割った値によって設定されます。

図 74. 差動入力 - 差動出力アンプ

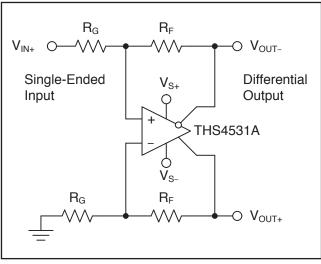

#### シングルエンド入力ー差動出力アンプ

THS4531Aは、シングルエンド入力信号を差動出力信号へと変換して増幅することもできます。回路の基本的なブロック図を図75に示します( $V_{\rm OCM}$ および $\overline{\rm PD}$ 入力は示されていません)。ここでも、回路のゲインは $R_{\rm F}$ を $R_{\rm G}$ で割った値によって設定されます。

図 75. シングルエンド入力-差動出力アンプ

#### 差動入力ーシングルエンド出力アンプ

THS4531Aのような完全差動オペアンプは、差動からシングルエンドへの変換には推奨されません。このアプリケーションは、計測アンプ、または古典的な差動アンプとして構成された標準オペアンプを使用すると、最適な性能が得られます。OPA835データシート(SLOS713)のアプリケーション情報を参照してください。

#### 入力同相モード電圧範囲

完全差動オペアンプの入力同相モード電圧は、デバイスの+お よび-入力ピンの電圧です。

オペアンプの入力同相モード電圧範囲 (V<sub>ICR</sub>)を超えないことが 重要です。オペアンプが線形動作していると仮定すると、入力 ピン間の電圧は最大でもわずか数ミリボルトです。したがって、一 方の入力ピンの電圧がわかれば、オペアンプの入力同相モード電 圧がわかります。

負入力を加算ノードとして扱うことにより、この電圧は次の式で 与えられます。

$$\left(V_{OUT+} \times \frac{R_G}{R_G + R_F}\right) + \left(V_{IN-} \times \frac{R_F}{R_G + R_F}\right) \tag{1}$$

オペアンプの $V_{\rm ICR}$ を求めるには、 $V_{\rm OUT+}$ の上限と下限で負入力の電圧を評価します。

オペアンプのゲインが増加すると、入力同相モード電圧は、ソースの入力同相モード電圧により近い値になります。

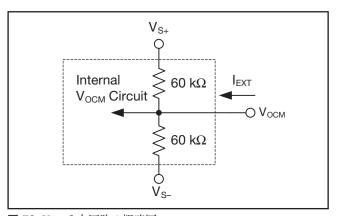

#### 出力同相モード電圧の設定

出力同相モード電圧は、 $V_{OCM}$ ピンの電圧によって設定され、内部回路によってこの電圧に可能な限り近い値に保持されます。未接続の場合、出力同相モードは内部回路によって電源中点に設定されますが、これは外部ソースによってオーバードライブできます。図76は、 $V_{OCM}$ 入力を示しています。内部の $V_{OCM}$ 回路は-3dB帯域幅が約24MHzであり、これは最高の性能を得るために必要な値ですが、このピンはDCバイアス入力ピンとしての使用を意図しています。ノイズを低減するため、このピンにはバイパス・コンデンサの使用を推奨します。内部の分圧抵抗回路をオーバードライブするために必要な外部電流は、次の式で近似されます。

$$I_{EXT} = \frac{2V_{OCM} - (V_{S+} - V_{S-})}{60k\Omega}$$

(2)

ここで、 $V_{\text{OCM}}$ は、 $V_{\text{OCM}}$ ピンに印加される電圧です。

図 76. V<sub>OCM</sub>入力回路の概略図

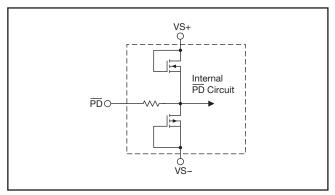

#### パワーダウン

パワーダウン・ピンは内部でCMOS段に接続されています。適切なHighロジックを確保するには、これを2.1V以上に駆動する必要があります。

図 77. パワーダウン内部回路の概略図

1.8Vロジックを使用してピンを駆動する場合は、デジタル・ロジックに最大 $100\mu$ Aの貫通電流が流れ、全体の静止電流が電気的特性に規定された最大ディスエーブル静止電流 $2\mu$ Aを超える場合があります。

消費電流の増加を最小限に抑えながら1.8Vロジックと適切にインターフェイスするには、SN74AVC1T45などのロジック・レベル変換器を使用できます。

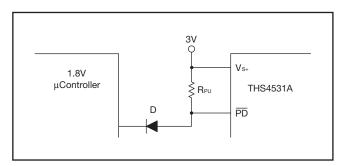

または、以下のようなダイオードとプルアップ抵抗を使用しても 同じ機能を実現できます。

図 78. 1.8Vロジックのマイコンに対するTHS4531Aのパワーダウン・ インターフェイス

パワーダウン・ピンの電圧は、電源電圧、入力ロジック・レベル、 およびダイオードの電圧降下の関数となります。ダイオードが順方 向バイアスであれば、パワーダウン電圧は次の式で決定されます。

$$V_{PD} = V_{L} + V_{f}$$

(3)

ここで、VLはロジック・レベル電圧、Vfはダイオードの順方向電 圧降下です。

これにより、1.8Vロジックに対して、パワーダウン・ロジック・レベルを2.1V以上および0.7V未満に保つには、ダイオードの順方向電圧が0.3Vより大きく、0.7V未満である必要があります。

たとえば、順方向電圧が約0.4Vのダイオードとして1N914を選択した場合、変換されたロジック電圧はディスエーブル動作に対して0.4V、イネーブル動作に対して2.2Vとなります。

追加の消費電流は次の式で求められます。

$$i_{PD} = \frac{V_{CC} - (V_L + V_f)}{R_{PU}}$$

(4)

この式は、RPUの値が大きいほど、追加電流が小さいことを示しています。RPUの適切な値としては $500k\Omega$ を使用でき、この場合、デバイス動作時の追加消費電流は $5.2\mu$ A、ディスエーブル時は $1.6\mu$ Aとなります。

#### 単一電源動作

一般的なラボ用機器による測定を容易にするため、THS4531A EVMは、両電源動作が可能となるよう作成されており、このデータシートに示すデータのほとんどは、両電源入力によって測定されています。ただし、このデバイスは単一電源動作用に設計され、性能に影響を与えることなく簡単に単一電源で使用できます。唯一の要件はデバイスを適切にバイアスすることであり、このデータシート内の仕様は単一電源動作に対して規定されています。

# 低消費電力アプリケーション、および帯域幅に対する抵抗値の影響

THS4531Aは、 $R_F$ の公称値が $2k\Omega$ となるよう設計されています。これにより、優れた歪特性、最大の帯域幅、最高の平坦度、および最適なパルス応答が得られます。この抵抗は、アンプの負荷ともなります。例えば、 $R_F=R_G=2k\Omega$ 、 $R_G$ をグランドに接続、 $V_{OUT+}=4V$ でゲインが1の場合、帰還パスを通ってグランドに1mAの電流が流れます。低消費電力アプリケーションでは、ゲイン設定抵抗の値を増やすことで、この電流を低減することが推奨されます。より大きな値のゲイン抵抗を使用することには、デバイスおよびPCBの寄生容量との相互作用によって、(消費電力の低減以外に)主に2つの副作用があります。

- 1. 帯域幅の低下

- 2. 位相マージンの低下

- (a) これにより周波数応答にピークが生じます。

- (b) また、パルス応答にオーバーシュートとリンギングが生じます。

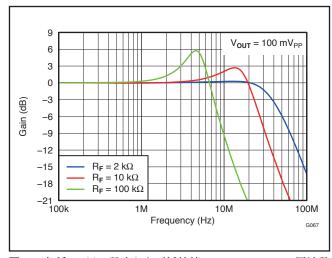

図79に、 $R_F = R_G = 2k\Omega$ 、 $10k\Omega$ 、 $100k\Omega$ でゲインが1のときの小信号周波数応答を示します。測定は $R_L = 2k\Omega$ で行われています。 $R_L$ の負荷効果により、値が小さいほどピークは小さくなりますが、値が大きくてもそれほど大きな影響はありません。

予想されるように、ゲイン抵抗が大きいと、帯域幅が小さくなり、応答にピークが生じます(周波数応答のピークは、パルス応答のオーバーシュートおよびリンギングと同じことです)。

図 79. 各種のゲイン設定および抵抗値でのTHS4531Aの周波数 応答

#### 容量性負荷の駆動

THS4531Aは、2pFの公称容量性負荷(差動)に対して設計されています。これを超える容量性負荷を駆動する場合は、出力と直列に小さな抵抗  $(R_o)$ をデバイスにできる限り近づけて配置することを推奨します。この $R_o$ を使用しないと、出力の容量がアンプの出力インピーダンスと相互作用して、アンプのループ・ゲインに位相シフトを発生させ、位相マージンが低下するため、次のような結果となります。

- 1. 周波数応答にピークが生じます。

- 2. パルスまたは方形波信号での時間ドメイン応答にオーバー シュート、アンダーシュート、およびリンギングが生じます。

- 3. 不安定な動作または発振に至る場合があります。

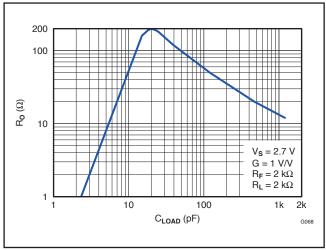

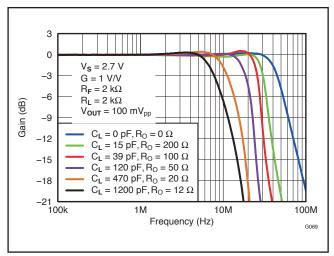

$R_0$ を挿入すると、位相シフトが補償され、位相マージンが回復されますが、帯域幅が制限されます。図69の回路は、 $2k\Omega$ の負荷抵抗とともに $V_{OUT+}$ および $V_{OUT-}$ 間に容量を差動配置した場合に、容量性負荷 $C_L$ に対して最適な $R_0$ を求める測定回路です。図80は、容量性負荷 $C_L$ に対する $R_0$ の最適な値を示し、図81は、さまざまな値での周波数応答を示しています。2.7Vと5Vのどちらの電源でも性能は同じです。

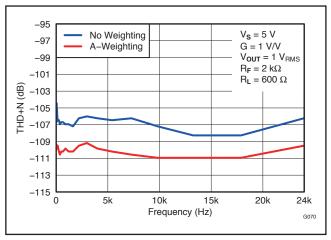

#### オーディオ性能

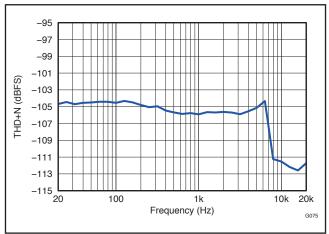

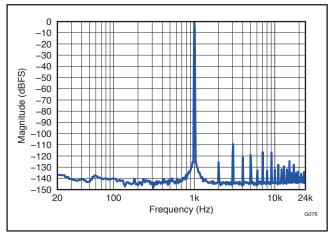

THS4531Aは、非常に低い静止電力で優れたオーディオ性能を発揮します。オーディオ帯域での性能を示すため、オーディオ・アナライザを使用してデバイスをテストしました。THD+NおよびFFT 試験を1Vrmsの出力電圧で実行しました。2.7Vと5Vのどちらの電源でも性能は同じです。使用した測定回路を図82に示し、アナライザの性能を図83および図84に示します。FFTプロットでは、高調波のスパーがアナライザの測定限界に位置しており、これはTHS4531Aが実際には直接測定可能な性能よりもずっと優れていることを意味します。THS4531Aの歪特性はオーディオ帯域で直接測定できないため、シミュレーションによって相関付けられた高雑音ゲイン構成での測定から推定されています。

図 80. 平坦な周波数応答を得るための推奨直列出力抵抗 対 容量性負荷

図 81. さまざまなRoおよびCt値での周波数応答

図 82. THS4531Aのオーディオ・アナライザ測定回路

図83. オーディオ・アナライザでのTHD+N、10Hz~24kHz

図 84. オーディオ・アナライザでの1kHz FFTプロット

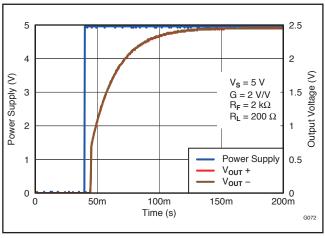

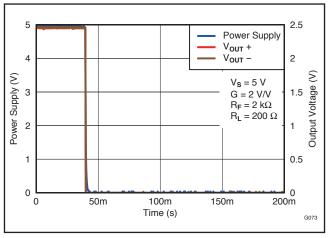

#### オーディオ・オン/オフ・ポップ性能

THS4531Aでは、差動出力間にスピーカーを接続して電源をオン/オフすることで、オン/オフ・ポップ性能を測定しています。また、THS4531Aのパワーダウン機能も使用しています。この測定はトーンありの場合とトーンなしの場合について実行しました。この測定中に、可聴のポップ音は発生しませんでした。

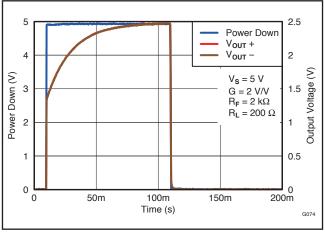

入力トーンがない場合について、図85はTHS4531Aの電源をオンにしたときの電圧波形を示し、図86は電源をオフにしたときの電圧波形を示しています。電源オン/オフ中の過渡電圧は、可聴ポップ音がないことを示しています。

図 85. 電源オン時のポップ性能

図 86. 電源オフ時のポップ性能

入力トーンがない場合について、図87はPDピンを使用してTHS4531Aをイネーブルおよびディスエーブルにしたときの電圧波形を示しています。電源オン/オフ中の過渡電圧は、可聴ポップ音がないことを示しています。

図 87. PDイネーブル時のポップ性能

# オーディオADCドライバ性能: THS4531AとPCM4204の組み合わせによる性能

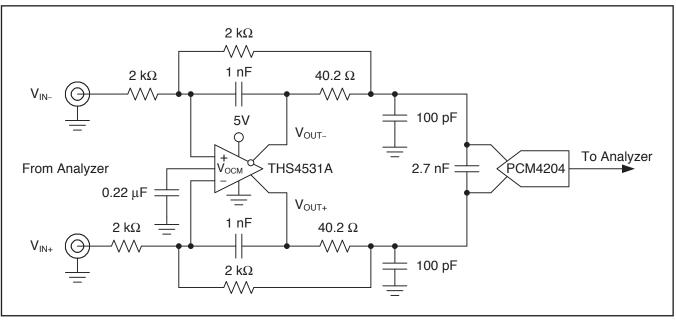

高性能オーディオADCの実現可能な性能を示すために、THS4531AをPCM4204の駆動アンプとしてテストしました。PCM4202は、プロ用、放送用のオーディオ・アプリケーション向けに設計された高性能4チャネルA/Dコンバータです。PCM4204のアーキテクチャでは、高度なディザリング機構を含む1チャネルあたり1ビットのデルタ・シグマ変調器を利用して、ダイナミック性能を向上しています。また、PCM出力データをサポートします。PCM4204は、柔軟なシリアル・ポート・インターフェイスおよび他の多くの高度な機能を備えています。詳細については、製品のデータシートを参照してください。

PCM4204 EVMを使用して、駆動アンプとしてのTHS4531Aのオーディオ性能をテストします。標準のPCM4204 EVMは、4個のOPA1632完全差動アンプを搭載し、これらはTHS4531Aと同じピン配置を使用しています。テストでは、このうち1つのアンプを同じパッケージ(MSOP)のTHS4531Aデバイスで置き換え、ゲインを1V/Vに変更し、電源を単一電源+5Vに変更しています。図88に回路を示します。単一電源+5Vを使用すると、THS4531Aの出力

同相モードは、デフォルトでPCM4204の入力に必要な+2.5Vとなります。そのため、THS4531Aの $V_{\rm OCM}$ 入力をPCM4204からの入力同相モード駆動に接続する抵抗は、必須ではなく、接続してもしなくても性能は変化しませんでした。EVMの電源接続は、正の電源入力 (+15V、+5VA、+5VD)を+5V外部電源 (EXT +3.3は不使用)に接続し、-15Vとすべてのグランド入力を外部電源のグランドに接続するよう変更しているため、1つの外部+5V電源だけでEVM上のすべてのデバイスに電源を供給できます。

オーディオ・アナライザを使用してEVMにアナログ・オーディオ入力を供給し、アナライザのデジタル入力によってPCM形式のデジタル出力を読み取ります。データは $f_s=96kHz$ で取得され、オーディオ出力はPCM形式を使用します。他のデータ・レートおよび形式でも、このデータシートに示される結果と同様の性能が示されることが予想されます。

図89は、重み付けなしでのTHD+N対周波数特性を示し、図90は1kHz入力トーンでのFFTを示しています。これらの測定におけるPCM4204への入力信号は、-0.5dBFSです。表4は、THS4531A+PCM4204を使用した測定結果を標準のデータシート性能と比較してまとめたものであり、このADCに対して優れた駆動アンプとなることを示しています。

#### SAR ADC性能

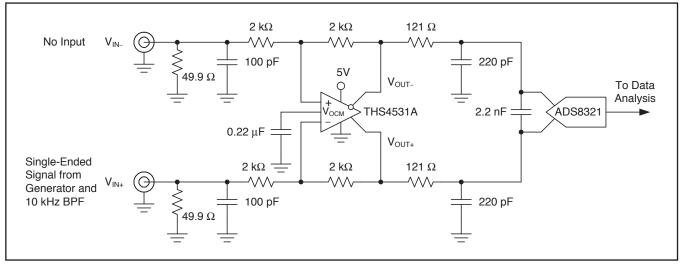

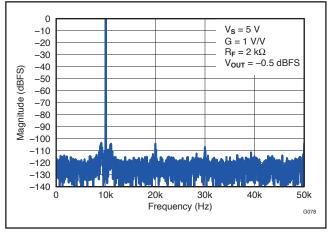

#### THS4531AとADS8321の組み合わせによる性能

高性能SAR ADCの実現可能な性能を示すために、THS4531A をADS8321の駆動アンプとしてテストしました。ADS8321は16ビットのSAR ADCであり、超低消費電力と小さなサイズによって優れたACおよびDC性能を実現します。図91の回路を使用して性能を

図 88. THS4531AおよびPCM4204のテスト回路

図 89. THS4531A+PCM4204のTHD+N 対 周波数 (重み付けなし)

図 90. THS4531A+PCM4204の1kHz FFT

表 4. AC分析: テスト回路とPCM4204データシート標準仕様の比較 (fs = 96kSPS)

| 構成                  | トーン  | THD + N |

|---------------------|------|---------|

| THS4531A + PCM4204  | 1kHz | -106 dB |

| PCM4204 データシート(標準値) | 1kHz | –103 dB |

測定しています。データは、ADS8321を100kSPSで使用し、入力 周波数10kHz、信号レベルはフルスケールより0.5dB下で取得しています。スペクトル性能のFFTプロットを図92に示します。表5は、FFT分析結果と、 $f_S=100$ kSPSでのADS8321の標準データシート性能をまとめたものです。詳細については、製品のデータシートを参照してください。

標準のADS8321 EVMおよびTHS4531A EVMに変更を加えて 図91の回路を実装し、駆動アンプとしてのTHS4531Aの性能を測定しました。単一+5V電源では、THS4531Aの出力同相モードが デフォルトで、ADS8321の入力に必要な+2.5Vとなるため、THS4531Aの $V_{OCM}$ 入力は $0.22\mu$ Fのコンデンサを使用してGNDへ と単純にバイパスします。表5に示されるFFT分析結果と標準データシート性能の一覧により、THS4531AがこのADCに対して優れた駆動アンプとなることがわかります。

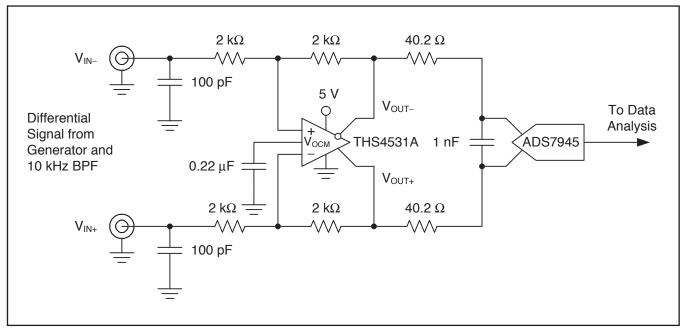

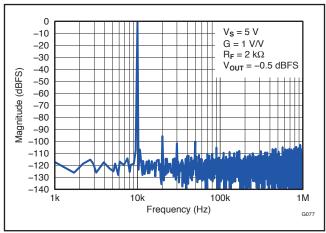

#### THS4531AとADS7945の組み合わせによる性能

高性能SAR ADCの実現可能な性能を示すために、THS4531A をADS7945の駆動アンプとしてテストしました。ADS7945は14 ビットのSAR ADCであり、低消費電力と小さなサイズによって優れたACおよびDC性能を実現します。図93の回路を使用して性能を測定しています。データは、ADS7945を2MSPSで使用し、入力周波数10kHz、信号レベルはフルスケールより0.5dB下で取得しています。スペクトル性能のFFTプロットを図94に示します。表6は、FFT分析結果と、 $f_S=2MSPS$ でのADS7945の標準データシート性能をまとめたものです。詳細については、製品のデータシートを参照してください。

図 91. THS4531AおよびADS8321のテスト回路

図 92. THS4531A + ADS8321の1kHz FFT

表 5. 10kHz FFT分析結果

| 構成                  | トーン   | SIGNAL   | SNR    | THD    | SINAD  | SFDR    |

|---------------------|-------|----------|--------|--------|--------|---------|

| THS4531A + ADS8321  | 10kHz | -0.5dBFS | 87 dBc | -96dBc | 87 dBc | 100 dBc |

| ADS8321 データシート(標準値) | 10kHz | -0.5dBFS | 87 dBc | -86dBc | 84 dBc | 86 dBc  |

標準のADS7945 EVMおよびTHS4531A EVMに変更を加えて 図93の回路を実装し、駆動アンプとしてのTHS4531Aの性能を 測定しました。単一+5V電源では、THS4531Aの出力同相モードがデフォルトで、ADS7945の入力に必要な+2.5Vとなるため、THS4531Aの $V_{\rm OCM}$ 入力は $0.22\mu {\rm F}$ のコンデンサを使用してGNDへと 単純にバイパスします。表6に示されるFFT分析結果と標準データ シート性能の一覧により、THS4531AがこのADCに対して優れた 駆動アンプとなることがわかります。

図 93. THS4531AおよびADS7945のテスト回路

図 94. THS4531AおよびADS7945のテスト回路

表 6. 10kHz FFT分析結果

| 構成                  | トーン   | SIGNAL    | SNR    | THD     | SFDR   |

|---------------------|-------|-----------|--------|---------|--------|

| THS4531A + ADS7945  | 10kHz | -0.5 dBFS | 83 dBc | -93 dBc | 96 dBc |

| ADS7945 データシート(標準値) | 10kHz | -0.5 dBFS | 84 dBc | -92 dBc | 94 dBc |

#### EVMおよびレイアウトに関する推奨事項

基板の設計時には、THS4531A EVM(SLOU356)を参考として使用してください。アンプ付近の外部部品のレイアウト、グランド・プレーンの構築、および電源配線については、EVMにできる限り合わせることを推奨します。一般的なガイドラインを以下に示します。

- 1. オペアンプへの入力および出力信号の配線は、直接配線とし、できる限り短くする必要があります。

- 2. 帰還パスは短い直接配線とし、ビアの使用はできる限り避けます。

- 3. グランドまたは電源プレーンは、アンプの入力および出力ピンの直下には配置しません。

- 4. 直列出力抵抗は、出力ピンにできる限り近づけて配置することを推奨します。設計で予想される容量性負荷に対して推奨される値については、図80「推奨直列出力抵抗対容量性負荷」を参照してください。

- 5. 2.2μFの電源デカップリング・コンデンサをデバイスから2イン チ以内の位置に配置し、他のオペアンプとも共用できるよう にします。両電源の場合は、両方の電源に対してコンデンサ が必要です。

- 6. 0.1µFの電源デカップリング・コンデンサを電源ピンのできる 限り近くに配置します。なるべく0.1インチ以内に配置してくだ さい。両電源の場合は、両方の電源に対してコンデンサが 必要です。

- 7.  $\overline{\text{PD}}$ ピンは、負電源電圧  $(V_s)$  を基準としたTTLロジック・レベルを使用します。このピンを使用しない場合は、正電源に接続してアンプをイネーブルにする必要があります。使用する場合は、アクティブにHighまたはLowに駆動する必要があり、不定の論理状態にしてはなりません。バイパス・コンデンサは必須ではありませんが、雑音の多い環境で堅牢性を向上させるために使用できます。

## パッケージ情報

#### 製品情報

| Orderable Device | Status | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp          | Op Temp (°C) | Top-Side<br>Markings (4) | Samples |

|------------------|--------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------|--------------|--------------------------|---------|

| THS4531AID       | ACTIVE | SOIC            | D                  | 8    | 75             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1<br>YEAR | -40 to 125   | T4531A                   | Samples |

| THS4531AIDGK     | ACTIVE | VSSOP           | DGK                | 8    | 80             | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAG      | Level-2-260C-1<br>YEAR | -40 to 125   | 531A                     | Samples |

| THS4531AIDGKR    | ACTIVE | VSSOP           | DGK                | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAG      | Level-2-260C-1<br>YEAR | -40 to 125   | 531A                     | Samples |

| THS4531AIDR      | ACTIVE | SOIC            | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1<br>YEAR | -40 to 125   | T4531A                   | Samples |

| THS4531AIRUNR    | ACTIVE | QFN             | RUN                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1<br>YEAR | -40 to 125   | 531A                     | Samples |

| THS4531AIRUNT    | ACTIVE | QFN             | RUN                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1<br>YEAR | -40 to 125   | 531A                     | Samples |

(1)マーケティング・ステータスは次のように定義されています。

ACTIVE: 製品デバイスが新規設計用に推奨されています。

LIFEBUY: TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND: 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していまい。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。 最新情報および製品 内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free" (鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。 高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田パンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。 それ以外は上記の様にPb-Free (RoHS) と考えられます。

Green (RoHS & no Sb/Br): TIにおける "Green"は、"Pb-Free"(RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

(4) ロゴ、ロット追跡コード情報、またはデバイスの環境カテゴリに関連した追加のマーキングが付与される場合があります。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって 提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続 けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破 壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報 が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金額を超える責任は負いかねます。

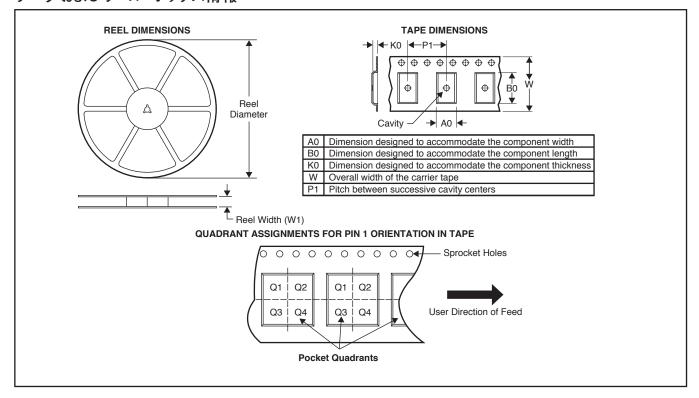

## パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| THS4531AIDGKR | VSSOP           | DGK                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| THS4531AIDR   | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| THS4531AIRUNR | QFN             | RUN                | 10 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| THS4531AIRUNT | QFN             | RUN                | 10 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

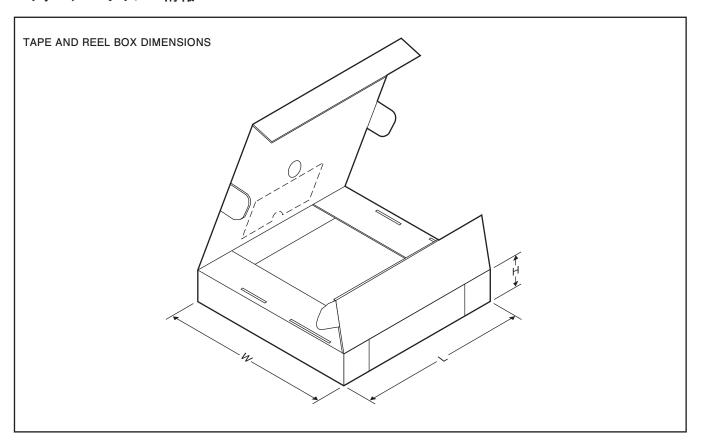

## パッケージ・マテリアル情報

## \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| THS4531AIDGKR | VSSOP        | DGK             | 8    | 2500 | 366.0       | 364.0      | 50.0        |

| THS4531AIDR   | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| THS4531AIRUNR | QFN          | RUN             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| THS4531AIRUNT | QFN          | RUN             | 10   | 250  | 210.0       | 185.0      | 35.0        |

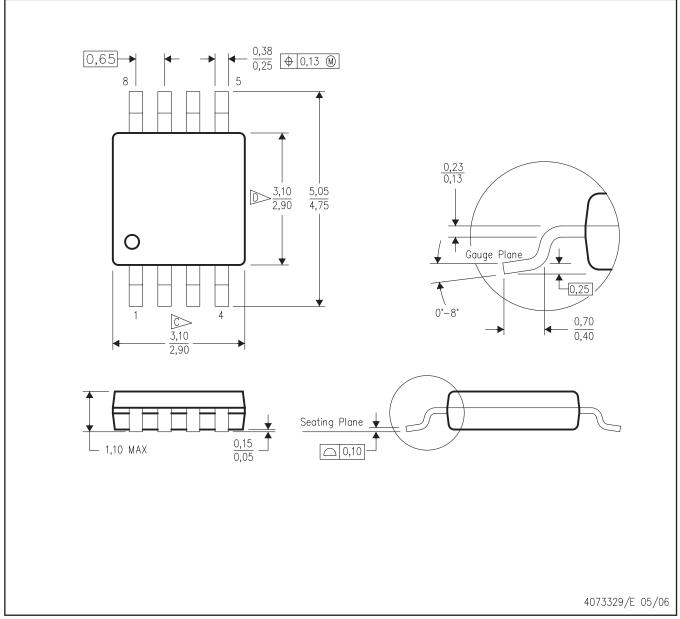

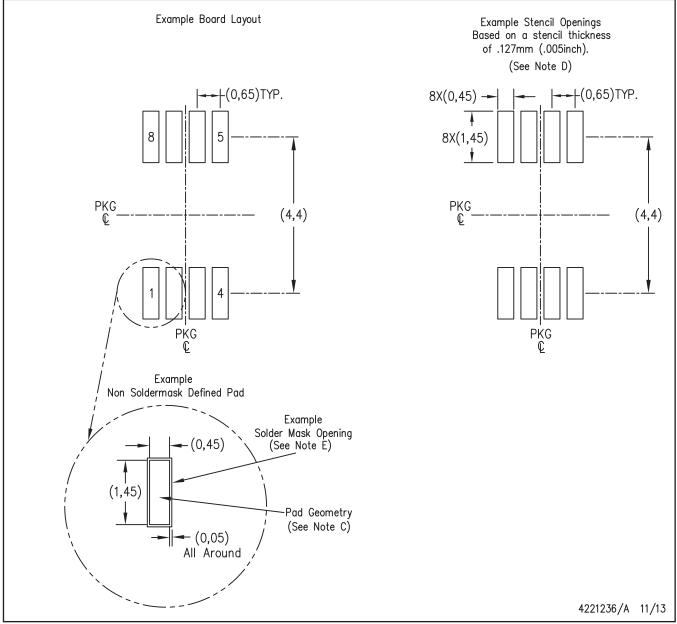

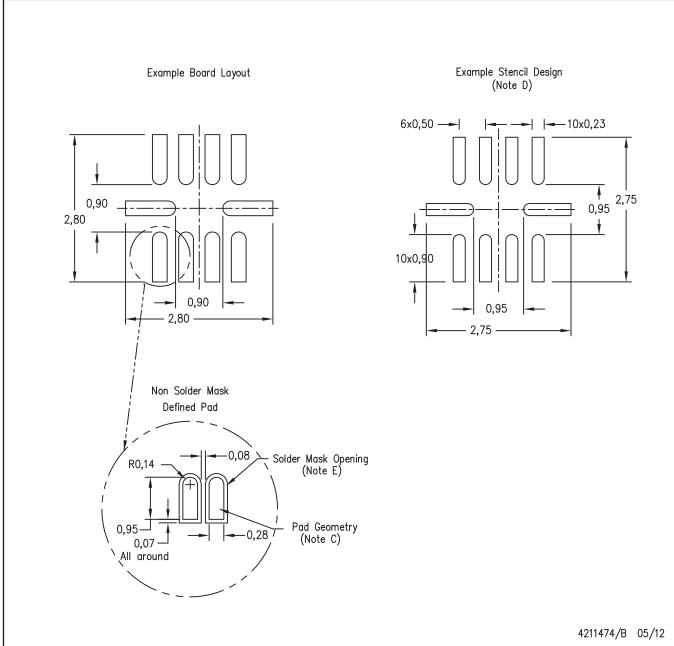

## DGK (S-PDSO-G8)

- 注: A. 全ての線寸法の単位はミリメートルです。

- E. JEDEC MO-187 variation AAに適合しています。

- 注: A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 代替設計については、資料IPC-7351を推奨します。

- D. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

- E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

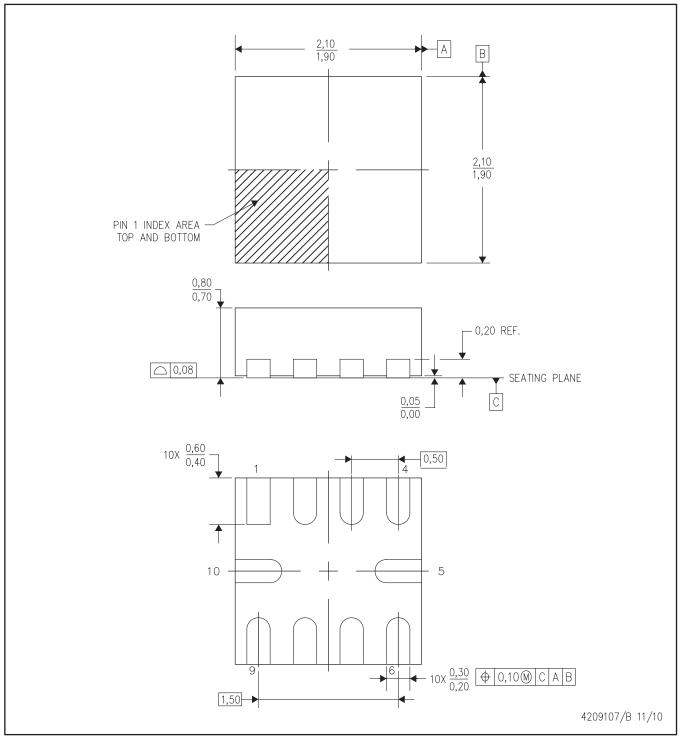

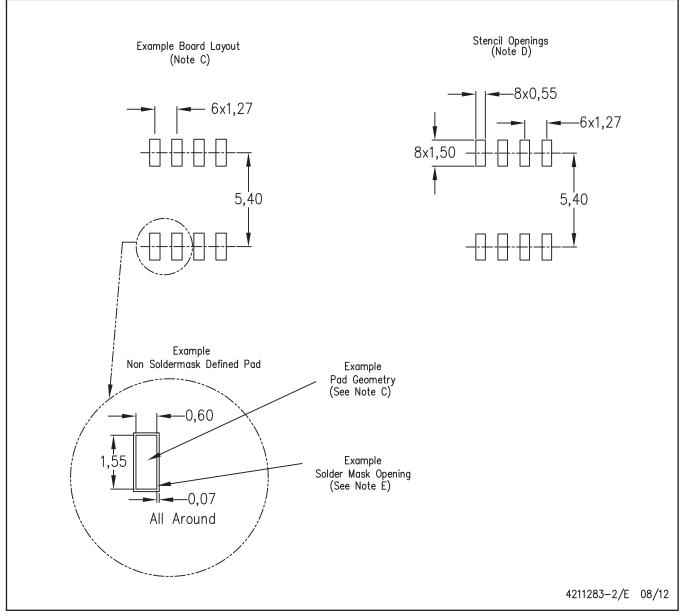

## RUN (S-PWQFN-N10)

- 注: A. 全ての線寸法の単位はミリメートルです。 寸法と許容差はASME Y14.5M- 1994に従っています。 B. 図は予告なく変更することがあります。

- C. QFN (クゥアド・フラットパック・ノーリード) パッケージ構造。

- 注: A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 代替設計については、資料IPC-7351を推奨します。

- D. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

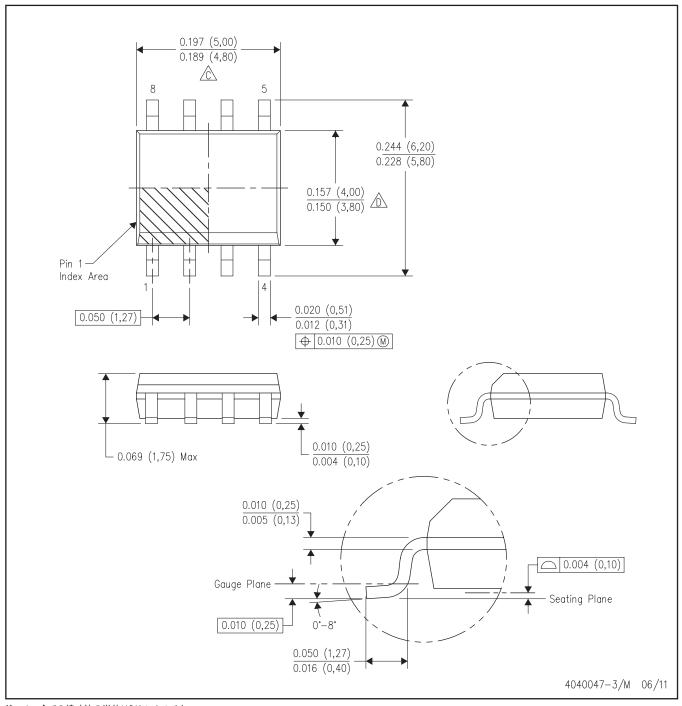

D (R-PDSO-G8) PLASTIC SMALL OUTLINE

- 注: A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

ボディー法には、 0.15mmを超えるモールド・フラッシュや突起は含まれません。

ボディー法には、 インターリード・フラッシュは含みません。 インターリード・フラッシュは、片側で0.50を超えることはありません。

- E. JEDEC MO-012 variation AAに適合しています。

- 注: A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 代替設計については、資料IPC-7351を推奨します。

- D. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

- E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

# ご注意

Texas Instruments Incorporated 及びその関連会社(以下総称してTIといいます)は、最新のJESD46に従いその半導体製品及びサービスを修正し、改善、改良、その他の変更をし、又は最新のJESD48に従い製品の製造中止またはサービスの提供を中止する権利を留保します。お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての半導体製品は、ご注文の受諾の際に提示されるTIの標準販売契約約款に従って販売されます。

TIは、その製品が、半導体製品に関するTIの標準販売契約約款に記載された保証条件に従い、販売時の仕様に対応した性能を有していることを保証します。検査及びその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、適用される法令によってそれ等の実行が義務づけられている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援又はお客様の製品の設計について責任を負うことはありません。TI 製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI 製部品を使用したお客様の製品及びアプリケーションに関連する危険を最小のものとするため、適切な設計上及び操作上の安全対策は、お客様にてお取り下さい。

TIは、TIの製品又はサービスが使用されている組み合せ、機械装置、又は方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品又はサービスを使用することについてライセンスを与えるとか、保証又は是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない、又はTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブック又はデータ・シートの中にある情報の重要な部分の複製は、その情報に一切の変更を加えること無く、且つその情報と関連する全ての保証、条件、制限及び通知と共になされる限りにおいてのみ許されるものとします。TIは、変更が加えられて文書化されたものについては一切責任を負いません。第三者の情報については、追加的な制約に服する可能性があります。

TIの製品又はサービスについて TI が提示したパラメーターと異なる、又は、それを超えてなされた説明で当該 TI 製品又はサービスを再販売することは、関連する TI 製品又はサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TI は、そのような説明については何の義務も責任も負いません。

TI からのアプリケーションに関する情報提供又は支援の一切に拘わらず、お客様は、ご自身の製品及びご自身のアプリケーションにおける TI 製品の使用に関する法的責任、規制、及び安全に関する要求事項の全てにつき、これをご自身で遵守する責任があることを認め、且つそのことに同意します。お客様は、想定される不具合がもたらす危険な結果に対する安全対策を立案し実行し、不具合及びその帰結を監視し、害を及ぼす可能性のある不具合の可能性を低減し、及び、適切な治癒措置を講じるために必要な専門的知識の一切を自ら有することを表明し、保証します。お客様は、TI 製品を安全でないことが致命的となるアプリケーションに使用したことから生じる損害の一切につき、TI 及びその代表者にその全額の補償をするものとします。

TI 製品につき、安全に関連するアプリケーションを促進するために特に宣伝される場合があります。そのような製品については、TIが目的とするところは、適用される機能上の安全標準及び要求事項を満たしたお客様の最終製品につき、お客様が設計及び製造ができるようお手伝いをすることにあります。それにも拘わらず、当該TI 製品については、前のパラグラフ記載の条件の適用を受けるものとします。

FDA クラスIII(又は同様に安全でないことが致命的となるような医療機器)へのTI 製品の使用は、TIとお客様双方の権限ある役員の間で、そのような使用を行う際について規定した特殊な契約書を締結した場合を除き、一切認められていません。

TIが軍需対応グレード品又は「強化プラスティック」製品として特に指定した製品のみが軍事用又は宇宙航空用アプリケーション、若しくは、軍事的環境又は航空宇宙環境にて使用されるように設計され、かつ使用されることを意図しています。お客様は、TIがそのように指定していない製品を軍事用又は航空宇宙用に使う場合は全てご自身の危険負担において行うこと、及び、そのような使用に関して必要とされるすべての法的要求事項及び規制上の要求事項につきご自身のみの責任により満足させることを認め、且つ同意します。

TIには、主に自動車用に使われることを目的として、ISO/TS 16949の要求事項を満たしていると特別に指定した製品があります。当該指定を受けていない製品については、自動車用に使われるようには設計されてもいませんし、使用されることを意図しておりません。従いまして、前記指定品以外のTI製品が当該要求事項を満たしていなかったことについては、TIはいかなる責任も負いません。

Copyright © 2014, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 静電気

- ●素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導電性マットにアースをとったもの等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、 静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを 行うこと。(但し、結露しないこと。) ● 直射日光があたる状態で保管・輸送しないこと。

#### 3. 防湿梱包

● 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

#### 4 機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を与えないこと。

#### 5. 熱衝撃

● はんだ付け時は、最低限 260℃以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が 一定以下に保証された無洗浄タイプのフラックスは除く。)

以上