📕 Order

Now

#### **TPS23523**

参考資料

JAJSF18A - DECEMBER 2017 - REVISED JANUARY 2019

Support &

Community

22

#### TPS23523: -48Vのホットスワップand Single OR-ingコントロ ーラ

#### 特長 1

- -10V~-80VのDC動作、絶対最大定格-200V

- ソフトスタート・コンデンサの切断機能

- デュアル・ホットスワップ・ゲート・ドライブ

- 400µAのゲート・ソーシング電流

- デュアル電流制限(VDSに基づく)

- 低V<sub>DS</sub>時に25mV ±4%

- 高V<sub>DS</sub>時に3mV ±25%

- UV (±1.5%)およびOV (±2%)をプログラム可能 - ヒステリシスをプログラム可能(±11%)

- 内蔵のORingコントローラ

- レギュレーション: 25mV ±15mV

- 高速なターンオフ: -6mV ±4mV

- タイムアウト後の再試行

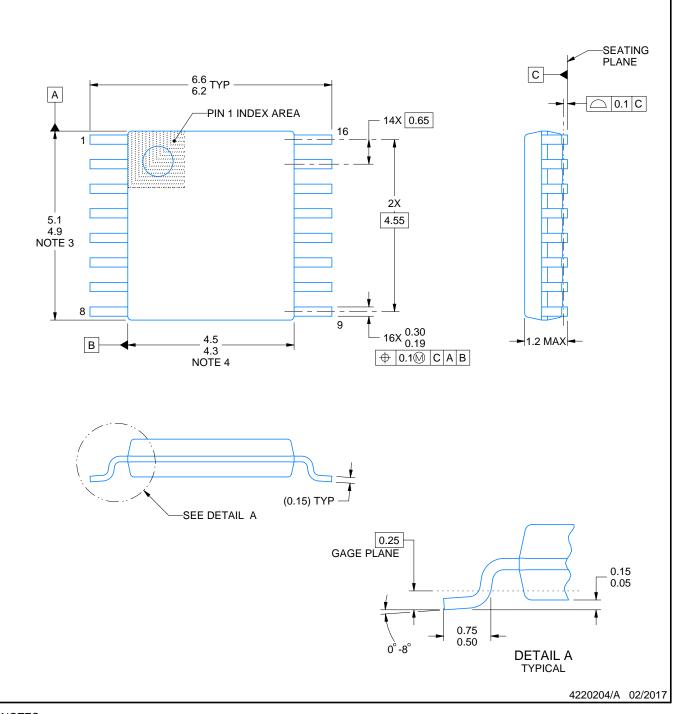

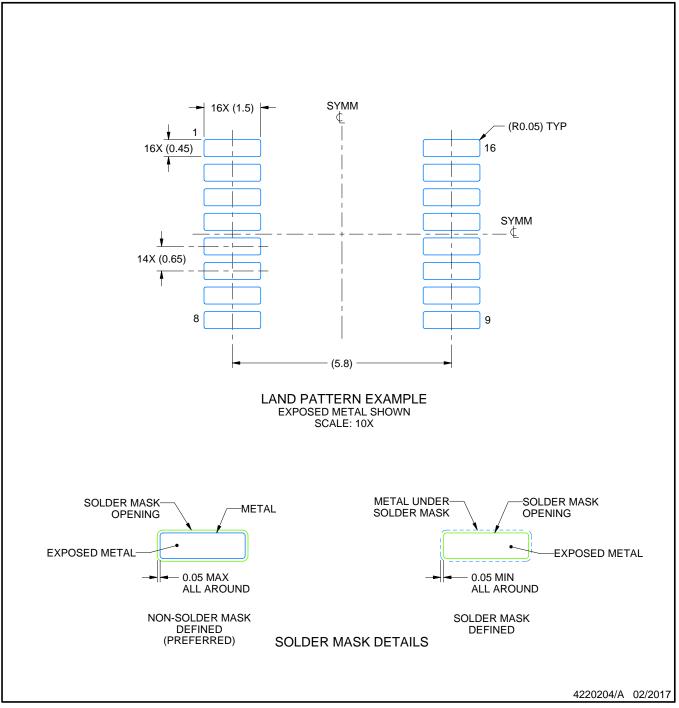

- 16ピンTSSOP

- 2 アプリケーション

- リモート無線ユニット

- ベースバンド・ユニット

- ルータおよびスイッチ

- スモールセル

- -48Vのテレコミュニケーション・インフラストラ クチャ

### 3 概要

TPS23523は、統合型ホットスワップおよびORingコント ローラで、大電力のテレコム・システムが厳格な過渡要件 に準拠するために使用できます。絶対最大定格が200V で、雷サージ・テストに簡単に耐えられます(IEC61000-4-5)。ソフトスタート・コンデンサの切断機能により、過渡応答 を損なうことなく突入電流が制限されるため、小さなホット スワップFETを使用できます。デュアル・ホットスワップ・ ゲート・ドライバにより、複数のホットスワップFETを必要と する大電力のアプリケーションで、スペースとBOMコストを 削減できます。400µAのソーシング電流により、高速な回 復が可能になり、雷サージ・テスト中にシステム・リセットを 避けるため役立ちます。デュアル電流制限により、ATIS 0600315.2013で要求されるようなブラウン・アウトおよび 入力ステップへの準拠が容易になります。最後に、正確な 低電圧および過電圧保護機能があり、スレッショルドとヒス テリシスをプログラム可能です。

TPS23523にはORingコントローラが内蔵されており、逆 フックアップ保護および逆電流保護を必要とする-48Vシス テムに理想的です。ORingコントローラは、入力の低下時 に出力を保護し、システム・リセットを回避します。

**刬品情報(1)**

| 型番       | パッケージ      | 本体サイズ(公称)     |

|----------|------------|---------------|

| TPS23523 | TSSOP (16) | 5.00mm×4.40mm |

|          |            |               |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

RTN  $\vdash$ R. UVEN PGb To Load R<sub>2</sub> Vref ov  $R_3 \ge$ 1kΩ Cs SS  $\sim$ -48 V\_OUT TPS23523 PW D Optional 100 0 Neg48  $\sim$ GATE BGATE Q, | GATE SNS TMF PROG VEE Стм C<sub>SS.VE</sub> Q<sub>2</sub> -48 V A Copyright © 2017, Texas Instruments Incorporated

概略回路図

🥭 Tools & Technical Software Documents

### 目次

| 1 | 特長   |                                                   |

|---|------|---------------------------------------------------|

| 2 | アプ   | リケーション1                                           |

| 3 | 概要   | · 1                                               |

| 4 | 改訂   | 「履歴2                                              |

| 5 | Pin  | Configuration and Functions 3                     |

| 6 | Spe  | cifications4                                      |

|   | 6.1  | Absolute Maximum Ratings 4                        |

|   | 6.2  | ESD Ratings 4                                     |

|   | 6.3  | Recommended Operating Conditions 4                |

|   | 6.4  | Thermal Information 5                             |

|   | 6.5  | Electrical Characteristics 5                      |

|   | 6.6  | Switching Characteristics 8                       |

|   | 6.7  | Typical Characteristics 9                         |

| 7 | Para | ameter Measurement Information 10                 |

|   | 7.1  | Relationship between Sense Voltage, Gate Current, |

|   |      | and Timer 10                                      |

| 8 | Deta | ailed Description 11                              |

|   | 8.1  | Overview 11                                       |

|   | 8.2  | Functional Block Diagram 11                       |

|    | 8.3  | Feature Description        | . 12 |

|----|------|----------------------------|------|

|    | 8.4  | Device Functional Modes    | . 17 |

| 9  | Appl | ication and Implementation | 19   |

|    | 9.1  | Application Information    | . 19 |

|    | 9.2  | Typical Application        | . 19 |

| 10 | Pow  | er Supply Recommendations  | 29   |

| 11 | Layo | out                        | 30   |

|    | 11.1 | Layout Guidelines          | . 30 |

|    | 11.2 | Layout Example             | . 30 |

| 12 |      | イスおよびドキュメントのサポート           |      |

|    | 12.1 | デバイス・サポート                  |      |

|    | 12.2 | ドキュメントのサポート                | . 31 |

|    | 12.3 | ドキュメントの更新通知を受け取る方法         | . 31 |

|    | 12.4 | コミュニティ・リソース                | . 31 |

|    | 12.5 | 商標                         | 31   |

|    | 12.6 | 静電気放電に関する注意事項              | . 31 |

|    | 12.7 | Glossary                   |      |

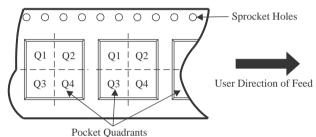

| 13 | メカニ  | ニカル、パッケージ、および注文情報          | 31   |

## 4 改訂履歴

| 20 | 017年12月発行のものから更新                                                            | Page |

|----|-----------------------------------------------------------------------------|------|

| •  | Added a row for V <sub>D</sub> in the <i>Absolute Maximum Ratings</i> table | 4    |

| •  | Added tablenote 2 to the Absolute Maximum Ratings table                     | 4    |

| •  | Updated Equation 12                                                         | 20   |

| •  | Updated Equation 22                                                         | 22   |

#### **TEXAS** NSTRUMENTS

www.ti.com

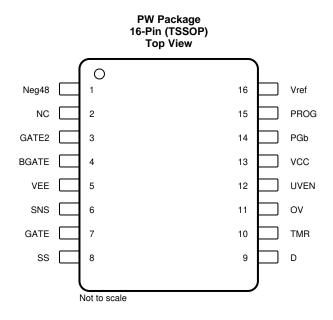

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN   |     | TYPE | DECODIDION                                                                                                                                                                                                                                        |

|-------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | ITPE | DESCRIPTION                                                                                                                                                                                                                                       |

| Neg48 | 1   | I    | Input to the OR-ing controller for the –48 feed. The TPS23523 will regulate the drop from VEE to Neg48 to 25 mV to mimic an ideal diode.                                                                                                          |

| NC    | 2   |      | No connect to space high voltage pins.                                                                                                                                                                                                            |

| GATE2 | 3   | 0    | Gate driver for the 2nd hot swap FET. NC if feature isn't used.                                                                                                                                                                                   |

| BGATE | 4   | 0    | Gate driver for the OR-ing FET.                                                                                                                                                                                                                   |

| VEE   | 5   | GND  | This pin corresponds to the IC GND. Kelvin sense to the bottom of $R_{SNS}$ to ensure accurate current limit.                                                                                                                                     |

| SNS   | 6   | I    | Sense pin, used to measure current and regulate it. Kelvin Sense to $R_{SNS}$ to ensure accurate current limits.                                                                                                                                  |

| GATE  | 7   | 0    | Gate drive for the main hot swap FET.                                                                                                                                                                                                             |

| SS    | 8   | 0    | Pin used for soft starting the output. Connect a capacitor ( $C_{SS}$ ) between the SS pin and -48V_OUT. The dv/dt rate on the -48V_OUT pin is proportional to the gate sourcing current divided by $C_{SS}$ .                                    |

| D     | 9   | I    | Pin used to sense the drain of the hot swap FET and to program the threshold where the hot swap switches from the CL1 and CL2. Connect a resistor from this pin to the drain of the hot swap FET (also called -48V_OUT) to program the threshold. |

| TMR   | 10  | 0    | Timer pin used to program the duration when the hot swap FET can be in current limit. Program this time by adding a capacitor between the TMR pin and VEE.                                                                                        |

| OV    | 11  | I    | Input overvoltage comparator. Tie a resistor divider to program the threshold where the device turns off due to overvoltage event.                                                                                                                |

| UVEN  | 12  | I    | Input undervoltage comparator. Tie a resistor divider to program the threshold where the device turns on.                                                                                                                                         |

| VCC   | 13  | S    | Clamped supply. Tie to RTN through resistor.                                                                                                                                                                                                      |

| PGb   | 14  | 0    | Power Good Bar, which is an open drain output that indicated when the power is good and the load can start drawing full power. PGb goes low when the hot swap is fully on and the DC/DC can draw full power.                                      |

| PROG  | 15  | I    | Adjust current limit and fast trip threshold by tying to VEE, floating, or tying to VEE through resistor.                                                                                                                                         |

| Vref  | 16  | 0    | 5V reference output. Connect to the base of a BJT to generate a rail that can be used to power current monitors and digital Isolators.                                                                                                            |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                        |                                                             | MIN  | MAX | UNIT |

|------------------------|-------------------------------------------------------------|------|-----|------|

| Supply voltage         | V <sub>VCC</sub> (current into V <sub>CC</sub> <10 mA)      | -0.3 | 20  | V    |

|                        | V <sub>SNS</sub> , V <sub>OV</sub>                          | -0.3 | 6.5 | V    |

| Input voltage          | V <sub>UVEN</sub> , , V <sub>SS</sub>                       | -0.3 | 30  | V    |

|                        | V <sub>D</sub> <sup>(2)</sup>                               | -0.3 | 40  | V    |

|                        | V <sub>Neg48</sub>                                          | -0.3 | 200 | V    |

| Input voltage          | $V_{Neg48}$ through 100- $\Omega$ resistor                  | -1   | 200 | V    |

|                        | $V_{Neg48}$ through 1-k $\Omega$ resistor                   | -2   | 200 | V    |

|                        | V <sub>GATE</sub> , V <sub>GATE2</sub> , V <sub>BGATE</sub> | -0.3 | VCC | V    |

| Output voltage         | V <sub>TMR</sub> , V <sub>PROG</sub> , V <sub>VREF</sub>    | -0.3 | 6.5 | V    |

| Output voltage         | V <sub>PGb</sub>                                            | -0.3 | 200 | V    |

| Operating junction ter | mperature, T <sub>J</sub>                                   | -40  | 125 | °C   |

| Storage temperature,   | T <sub>stg</sub>                                            | -55  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Current into the Pin D should be limited to < 1 mA through RD resistor

### 6.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | 1000  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | 500   | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                             |                                               | MIN  | NOM MAX | UNIT |

|-------------------------------------------------------------|-----------------------------------------------|------|---------|------|

| V <sub>VCC</sub>                                            | Supply voltage (current into $V_{CC}$ <10 mA) | 0    | 20      | V    |

| V <sub>SNS</sub> , V <sub>OV</sub>                          | Input voltage                                 | 0    | 5.5     | V    |

| V <sub>UVEN</sub> , V <sub>D</sub> , V <sub>SS</sub>        | Input voltage                                 | 0    | 18      | V    |

| V <sub>Neg48</sub>                                          | Input voltage, through 100- $\Omega$ resistor | -0.2 | 150     | V    |

| V <sub>GATE</sub> , V <sub>GATE2</sub> , V <sub>BGATE</sub> | Output voltage                                | 0    | VCC     | V    |

| V <sub>TMR</sub> , V <sub>PROG</sub> , V <sub>VREF</sub>    | Output voltage                                | 0    | 5.5     | V    |

| V <sub>PGb</sub>                                            | Output voltage                                | 0    | 80      | V    |

| C <sub>SS</sub>                                             | Capacitance                                   | 1    | 200     | nF   |

| R <sub>SS</sub>                                             | Resistance                                    | 1    | 10      | kΩ   |

| R <sub>D</sub>                                              | Resistance                                    | 120  | 2,000   | kΩ   |

| R <sub>NEG48V</sub>                                         | Resistance                                    | 100  | 1       | kΩ   |

### 6.4 Thermal Information

|                       |                                              | TPS23523   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                       |                                              | 16 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 98.4       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 31.3       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 44.3       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1.8        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 43.6       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$-40^{\circ}C \le T_{J} \le 125^{\circ}C, \ 1.1 \text{ mA} < I_{VCC} < 10 \text{ mA}, \ V_{(UVEN)} = 2 \text{ V}, \ V_{(OV)} = V_{(SNS)} = V_{(D)} = 0 \text{ V}, \ V_{(SS)} = GATEx = Hi-Z \text{ , } V_{(TMR)} = 0 \text{ V}, \ -1 \text{ V} < V_{NEG48Vx} < 150 \text{ V}, \ V_{Vref} = V_{PROG} = Hi-Z; \ All \ pin \ voltages \ are \ relative \ to \ VEE \ (unless \ otherwise \ noted)$

|                              | PARAMETER                                                                          | TEST CONDITIONS                                                                                                                                                                  | MIN   | TYP  | MAX   | UNIT |

|------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| VCC – Clamped                | Supply                                                                             |                                                                                                                                                                                  |       |      |       |      |

| V <sub>(UVLO_VCC)</sub>      | UVLO on VCC                                                                        | rising                                                                                                                                                                           | 9     | 9.5  | 10    | V    |

| V <sub>(UVLO_VCC,hyst)</sub> | UVLO hysteresis on VCC                                                             | hysteresis                                                                                                                                                                       |       | 1    |       | V    |

| V <sub>(VCC)</sub>           | VCC regulation                                                                     | $1.1 < I_{(VCC)} < 10$ mA (current into VCC)                                                                                                                                     | 12    | 14.5 | 18    | V    |

|                              |                                                                                    | $V_{VCC}$ = 10 V. Off                                                                                                                                                            |       |      | 1     | mA   |

| I <sub>Q</sub> Quiescen      | Quiescent Current                                                                  | V <sub>VCC</sub> = 10 V. On                                                                                                                                                      |       |      | 1     | mA   |

| 3                            |                                                                                    | V <sub>VCC</sub> = 10 V, Gateand BGATE in regulation                                                                                                                             |       |      | 1.1   | mA   |

| UVEN – Undervo               | Itage and Enable                                                                   |                                                                                                                                                                                  |       |      |       |      |

| V <sub>(UVEN_T)</sub>        | Threshold voltage for $V_{(UVEN)}$                                                 |                                                                                                                                                                                  | 0.985 | 1    | 1.015 | V    |

| I <sub>(UV_hyst)</sub>       | Hysteresis current, sourcing<br>from UV pin                                        | V <sub>UV</sub> = 1.5 V                                                                                                                                                          | 9     | 10   | 11.2  | μΑ   |

| OV – Overvoltage             | e                                                                                  |                                                                                                                                                                                  |       |      |       |      |

| V <sub>(OV_T)</sub>          | Threshold voltage for $\mathrm{V}_{\mathrm{OV}}$                                   |                                                                                                                                                                                  | 0.98  | 1    | 1.02  | V    |

| I <sub>(OV_hyst)</sub>       | Hysteresis current, sourcing<br>from OV pin                                        | V <sub>OV</sub> = 1.5 V                                                                                                                                                          | 9     | 10   | 11.2  | μΑ   |

| TMR – Timer                  |                                                                                    |                                                                                                                                                                                  |       |      |       |      |

| V <sub>TMR</sub>             | Voltage on timer when part times out.                                              | $V_D = 0 \text{ V}, \text{ TMR} \uparrow, \text{ measure } V_{TMR}$<br>when $V_{GATE} = 0$                                                                                       | 1.47  | 1.5  | 1.53  | V    |

| V <sub>TMR2</sub>            | Voltage on timer when part times out.                                              | $V_D = 1 \text{ V}, \text{ TMR} \uparrow, \text{ measure } V_{TMR}$<br>when $V_{GATE} = 0$                                                                                       | 0.735 | 0.75 | 0.765 | V    |

| 1                            | Timer Sourcing current when                                                        | $V_{SNS}$ = 0.1 V, $V_{D}$ = 0 V, $V_{TMR}$ = 0 V, measure I out from TMR                                                                                                        | 9     | 10   | 11    | μA   |

| I <sub>TMR,SRs</sub>         | in fault condition or when retrying.                                               | $V_{SNS}$ = 0.1 V, VD = 2 V, $V_{TMR}$ = 0 V, measure I out from TMR                                                                                                             | 45    | 50   | 55    | μA   |

| I <sub>TMR,SNC</sub>         | Timer sinking current when not in fault condition.                                 | $V_{SNS} = 0 \text{ V},  V_D = 0 \text{ V},  V_{TMR} = 2 \text{ V},$                                                                                                             | 1.5   | 2    | 2.5   | μA   |

| V <sub>TMR,RETRY</sub>       | Voltage on timer when the timer starts going back up in retry. Retry version only. | $ \begin{array}{l} V_{SNS} = 0 \ V, \ V_D = 0 \ V, \ TMR \ \uparrow = 2 \ V, \\ TMR \ \downarrow, \ measure \ V_{TMR} \ when \ I \ into \\ TMR \ change \ polarity \end{array} $ | 0.475 | 0.5  | 0.525 | V    |

| N <sub>RETRY</sub>           | Number of retry duty cycles.<br>Retry version only.                                |                                                                                                                                                                                  |       | 64   |       |      |

| D <sub>RETRY</sub>           | Retry duty cycle. Retry version only.                                              |                                                                                                                                                                                  |       | 0.4% |       |      |

| I <sub>GATE,TIMER</sub>      | Gate Sourcing Current<br>Threshold When timer starts<br>to run.                    | $V_G$ = 5 V, $V_D$ = 2 V, $V_{SNS}$ ↑, measure $I_{GATE}$ when TMR sources current                                                                                               | 5     | 10   | 15    | μA   |

Copyright © 2017–2019, Texas Instruments Incorporated

### **Electrical Characteristics (continued)**

$-40^{\circ}C \le T_{J} \le 125^{\circ}C, 1.1 \text{ mA} < I_{VCC} < 10 \text{ mA}, V_{(UVEN)} = 2 \text{ V}, V_{(OV)} = V_{(SNS)} = V_{(D)} = 0 \text{ V}, V_{(SS)} = GATEx = Hi-Z, V_{(TMR)} = 0 \text{ V}, -1 \text{ V} < V_{NEG48Vx} < 150 \text{ V}, V_{Vref} = V_{PROG} = Hi-Z; All pin voltages are relative to VEE (unless otherwise noted)$

| VSNS,TMR1<br>VSNS,TMR2<br>SNS – Sense Pin F<br>ISNS,LEAK<br>VSNS,CL1<br>VSNS,FST | Sense Voltage when Timer<br>starts to run.<br>Sense Voltage when Timer<br>starts to run.<br>For Current Limit<br>Leakage current on sense<br>pin<br>PROG = Float<br>PROG = Float<br>PROG = VEE<br>PROG = VEE<br>PROG = VEE<br>RPROG = 78.7kΩ<br>RPROG = 162 kΩ<br>Fold Back Current Limit | $\label{eq:VD} \begin{array}{l} V_{D} = 2 \; V, \; V_{TMR} = 0 \; V, \; V_{G} = 5 \; V; \\ V_{SNS} \uparrow, \; \text{measure } V_{SNS} \; \text{when TMR} \\ \text{sources current} \\ \\ \\ V_{D} = 0 \; V, \; V_{TMR} = 0 \; V, \; V_{G} = 5 \; V; \\ \\ V_{SNS} \uparrow, \; \text{measure } V_{SNS} \; \text{when TMR} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ | 1.5<br>23.25<br>-2<br>24<br>38<br>45<br>72<br>110 | 2.5<br>24.5<br>25<br>40<br>50<br>80<br>120 | 2<br>26<br>42<br>55<br>88 | mV<br>mV<br>μA<br>mV<br>mV<br>mV |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------|---------------------------|----------------------------------|

| VSNS,TMR2<br>SNS – Sense Pin F<br>I <sub>SNS,LEAK</sub><br>V <sub>SNS,CL1</sub>  | starts to run.<br>For Current Limit<br>Leakage current on sense<br>pin<br>PROG = Float<br>PROG = VEE<br>PROG = FLOAT<br>PROG = VEE<br>R <sub>PROG</sub> = 78.7kΩ<br>R <sub>PROG</sub> = 162 kΩ                                                                                            | $V_{SNS} \uparrow, measure V_{SNS} \text{ when TMR}$<br>sources current<br>$V_{TMR} = 0 \text{ V. } V_{GATE} = 5 \text{ V. } V_D = 0 \text{ V,}$<br>$V_{SNS} \uparrow, measure \text{ when } I_{GATE} = 0;$<br>$V_{TMR} = 0 \text{ V. } V_{GATE} = 5 \text{ V. } V_D = 0 \text{ V,}$<br>$V_{SNS} \uparrow, measure \text{ when } I_{GATE} > 100$                                      | -2<br>24<br>38<br>45<br>72<br>110                 | 25<br>40<br>50<br>80                       | 26<br>42<br>55<br>88      | μA<br>mV<br>mV<br>mV             |

| I <sub>SNS,LEAK</sub><br>V <sub>SNS,CL1</sub><br>                                | Leakage current on sense<br>pin<br>PROG = Float<br>PROG = VEE<br>PROG = FLOAT<br>PROG = VEE<br>$R_{PROG} = 78.7 k\Omega$<br>$R_{PROG} = 162 k\Omega$                                                                                                                                      | $V_{SNS} \uparrow$ , measure when $I_{GATE} = 0$ ;<br>$V_{TMR} = 0 V. V_{GATE} = 5 V. V_D = 0 V,$<br>$V_{SNS} \uparrow$ ,measure when $I_{GATE} > 100$                                                                                                                                                                                                                                | 24<br>38<br>45<br>72<br>110                       | 40<br>50<br>80                             | 26<br>42<br>55<br>88      | mV<br>mV<br>mV                   |

| ISNS,LEAK<br>VSNS,CL1<br>VSNS,FST                                                | pin<br>PROG = Float<br>PROG = VEE<br>PROG = FLOAT<br>PROG = VEE<br>$R_{PROG} = 78.7 k\Omega$<br>$R_{PROG} = 162 k\Omega$                                                                                                                                                                  | $V_{SNS} \uparrow$ , measure when $I_{GATE} = 0$ ;<br>$V_{TMR} = 0 V. V_{GATE} = 5 V. V_D = 0 V,$<br>$V_{SNS} \uparrow$ ,measure when $I_{GATE} > 100$                                                                                                                                                                                                                                | 24<br>38<br>45<br>72<br>110                       | 40<br>50<br>80                             | 26<br>42<br>55<br>88      | mV<br>mV<br>mV                   |

| V <sub>SNS,CL1</sub>                                                             | PROG = VEE<br>PROG = FLOAT<br>PROG = VEE<br>R <sub>PROG</sub> = 78.7kΩ<br>R <sub>PROG</sub> = 162 kΩ                                                                                                                                                                                      | $V_{SNS} \uparrow$ , measure when $I_{GATE} = 0$ ;<br>$V_{TMR} = 0 V. V_{GATE} = 5 V. V_D = 0 V,$<br>$V_{SNS} \uparrow$ ,measure when $I_{GATE} > 100$                                                                                                                                                                                                                                | 38<br>45<br>72<br>110                             | 40<br>50<br>80                             | 42<br>55<br>88            | mV<br>mV                         |

| V <sub>SNS,FST</sub>                                                             | PROG = FLOAT<br>PROG = VEE<br>$R_{PROG} = 78.7 k\Omega$<br>$R_{PROG} = 162 k\Omega$                                                                                                                                                                                                       | $V_{SNS} \uparrow$ , measure when $I_{GATE} = 0$ ;<br>$V_{TMR} = 0 V. V_{GATE} = 5 V. V_D = 0 V,$<br>$V_{SNS} \uparrow$ ,measure when $I_{GATE} > 100$                                                                                                                                                                                                                                | 45<br>72<br>110                                   | 50<br>80                                   | 55<br>88                  | mV                               |

| V <sub>SNS,FST</sub>                                                             | PROG = VEE<br>R <sub>PROG</sub> = 78.7kΩ<br>R <sub>PROG</sub> = 162 kΩ                                                                                                                                                                                                                    | $V_{SNS}$ $\uparrow$ ,measure when $I_{GATE}$ > 100                                                                                                                                                                                                                                                                                                                                   | 72<br>110                                         | 80                                         | 88                        |                                  |

| V <sub>SNS,FST</sub>                                                             | R <sub>PROG</sub> = 78.7kΩ<br>R <sub>PROG</sub> = 162 kΩ                                                                                                                                                                                                                                  | $V_{SNS}$ $\uparrow$ ,measure when $I_{GATE}$ > 100                                                                                                                                                                                                                                                                                                                                   | 110                                               |                                            |                           | m\/                              |

| -                                                                                | $R_{PROG} = 162 \text{ k}\Omega$                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       |                                                   | 120                                        |                           |                                  |

|                                                                                  |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                       | ~~                                                |                                            | 130                       | mV                               |

| N/                                                                               | Fold Back Current Limit                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                       | 68                                                | 75                                         | 82                        | mV                               |

| V <sub>SNS,CL2</sub>                                                             |                                                                                                                                                                                                                                                                                           | $V_{TMR} = 0 V$ , $V_{GATE} = 5 V$ , $V_D = 5 V$ ,<br>$V_{SNS} \uparrow$ , measure when $I_{GATE} = 0$ ;                                                                                                                                                                                                                                                                              | 2.25                                              | 3                                          | 3.75                      | mV                               |

| V <sub>SNS,FST2</sub>                                                            | Fast Trip during start-up                                                                                                                                                                                                                                                                 | $V_{TMR}$ = 0 V, $V_{GATE}$ = 5 V, $V_{D}$ = 5 V, $V_{SNS}$ ↑, Measure when $I_{GATE}$ > 100 mA                                                                                                                                                                                                                                                                                       | 6                                                 | 9                                          | 12                        | mV                               |

| PROG – Programir                                                                 | ng Pin to Set Current Limit (C                                                                                                                                                                                                                                                            | L) and Fast Trip                                                                                                                                                                                                                                                                                                                                                                      |                                                   |                                            |                           |                                  |

| _                                                                                | PROG pin current                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       | 7.9                                               | 10.1                                       | 12                        | μA                               |

|                                                                                  | Prog pin voltage                                                                                                                                                                                                                                                                          | Threshold on $V_{PROG}$ , where the fast trip setting changes from 80mV to 120mV.                                                                                                                                                                                                                                                                                                     |                                                   |                                            | 0.48                      | V                                |

| V <sub>PROG,MID</sub>                                                            | Prog pin voltage                                                                                                                                                                                                                                                                          | Threshold on $V_{PROG}$ , where the current limit setting changes from 25mV to 40mV.                                                                                                                                                                                                                                                                                                  | 0.94                                              | 1.23                                       | 1.51                      | V                                |

| $V_{PROG,High}$                                                                  | Prog pin voltage                                                                                                                                                                                                                                                                          | Threshold on $V_{PROG}$ , where the fast trip setting changes from 80mV to 120mV.                                                                                                                                                                                                                                                                                                     | 2.4                                               |                                            |                           | V                                |

| GATE – Gate Drive                                                                | e for Main Hot Swap FET                                                                                                                                                                                                                                                                   | · · · ·                                                                                                                                                                                                                                                                                                                                                                               |                                                   |                                            |                           |                                  |

| V <sub>(VCC-GATE)</sub>                                                          | Output gate voltage                                                                                                                                                                                                                                                                       | $V_{(SNS)} = 0 V$                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                            | 1                         | V                                |

| LOATE ODD NODW                                                                   | Sourcing Current during normal operation.                                                                                                                                                                                                                                                 | $V_{(TMR)} = 0 V. V_{(GATE)} = 8 V. V_D = 0$<br>V, $V_{(SNS)} = 0 V$                                                                                                                                                                                                                                                                                                                  | 250                                               | 400                                        |                           | μA                               |

|                                                                                  | Sourcing Current during star-<br>up                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                       | 15                                                | 20                                         | 25                        | μA                               |

| I(GATE,wkpd)                                                                     | Weak pull down current                                                                                                                                                                                                                                                                    | $V_{(SNS)} = 0 V. V_{UVEN} = 0 V$                                                                                                                                                                                                                                                                                                                                                     | 3                                                 | 5                                          | 7                         | mA                               |

| I <sub>(GATE,FST)</sub>                                                          | Fast Pull down current with<br>10mV overdrive                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                       | 0.4                                               | 1                                          | 1.5                       | А                                |

| GATE2 – Gate Driv                                                                | ve for Auxiliary Hot Swap FET                                                                                                                                                                                                                                                             | r                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                            |                           |                                  |

| V <sub>(VCC-GATE2)</sub>                                                         | Output gate voltage                                                                                                                                                                                                                                                                       | $V_{(SNS)} = 0 V$                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                            | 1                         | V                                |

|                                                                                  | weak pull down                                                                                                                                                                                                                                                                            | V <sub>GATE</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                               |                                                   | 5                                          |                           | mA                               |

|                                                                                  | Sourcing Current                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                       |                                                   | 50                                         |                           | μA                               |

|                                                                                  | Fast Pull down current with<br>10 mV overdrive                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                       | 0.4                                               | 1                                          | 1.5                       | A                                |

| V <sub>GATE,TH</sub>                                                             | Threshold on $V_{GATE}$ when $GATE2$ turns on                                                                                                                                                                                                                                             | Raise $V_{\text{GATE}},$ measure when $V_{\text{GATE2}}$ comes up.                                                                                                                                                                                                                                                                                                                    | 6.25                                              | 7.25                                       | 8                         | V                                |

|                                                                                  | Hysteresis of threshold on $V_{GATE}$ when GATE2 turns on                                                                                                                                                                                                                                 | hysteresis                                                                                                                                                                                                                                                                                                                                                                            |                                                   | 0.5                                        |                           | V                                |

### **Electrical Characteristics (continued)**

$-40^{\circ}C \leq T_{J} \leq 125^{\circ}C, 1.1 \text{ mA} < I_{VCC} < 10 \text{ mA}, V_{(UVEN)} = 2 \text{ V}, V_{(OV)} = V_{(SNS)} = V_{(D)} = 0 \text{ V}, V_{(SS)} = GATEx = Hi-Z, V_{(TMR)} = 0 \text{ V}, -1 \text{ V} < V_{NEG48Vx} < 150 \text{ V}, V_{Vref} = V_{PROG} = Hi-Z; All pin voltages are relative to VEE (unless otherwise noted)$

|                              | PARAMETER                                                                                  | TEST CONDITIONS                                                                                                                                           | MIN  | TYP  | MAX  | UNIT |

|------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| R <sub>(D,INT)</sub>         | Resistance from the drain pin to GND.                                                      |                                                                                                                                                           | 28.5 | 30   | 31.5 | kΩ   |

| V <sub>(D,CL_SW)</sub>       | Voltage on drain that<br>switches between two current<br>limits                            |                                                                                                                                                           | 1.46 | 1.5  | 1.54 | V    |

| V <sub>(D,TMR_SW)</sub>      | Voltage on drain that switches the $V_{\mbox{TMR}}$ threshold.                             | $ \begin{array}{l} V_{(TMR)} = 1 \ V, \ V_{(GATE)} = 5 \ V, \ V_{(SNS)} = \\ 20 \ mV, \ D\uparrow, \ measure \ V \ when \ I_{(GATE)} \\ = 0 \end{array} $ | 0.73 | 0.75 | 0.77 | V    |

| V <sub>(D,TMR_SW,hyst)</sub> | hysteresis for V <sub>(D,TMR,SW)</sub>                                                     | hysteresis                                                                                                                                                |      | 75   |      | mV   |

| SS (Soft Start)              |                                                                                            |                                                                                                                                                           |      |      |      |      |

| I <sub>(SS,PD)</sub>         | Pull down current when not in inrush                                                       | V <sub>SS</sub> = 5 V                                                                                                                                     | 100  |      |      | mA   |

| R <sub>(SS,GATE)</sub>       | Resistance between GATE and SS in the start-up phase                                       |                                                                                                                                                           |      | 80   |      | Ω    |

| Vref                         |                                                                                            |                                                                                                                                                           |      |      |      |      |

| V <sub>Vref</sub>            | Reference output                                                                           | 0 < I <sub>Vref</sub> < 800 µA                                                                                                                            | 4    | 4.9  | 5.5  | V    |

| I <sub>Vref</sub>            | V <sub>Vref</sub> SC current                                                               | Vref ON, V <sub>Vref</sub> (shorted)                                                                                                                      |      | 2    |      | mA   |

| Neg48                        |                                                                                            |                                                                                                                                                           |      |      |      |      |

|                              |                                                                                            | V <sub>Neg48</sub> = -50 mV, BGATE ON                                                                                                                     | -2   |      | 2    | μA   |

| (lkg,Neg48)                  | Leakage current                                                                            | V <sub>Neg48</sub> = -100 mV, BGATE ON                                                                                                                    | -7   |      | 7    | μA   |

|                              |                                                                                            | V <sub>Neg48</sub> = 150 V, BGATE off                                                                                                                     |      |      | 30   | μA   |

| V <sub>(FWD)</sub>           | Forward regulation voltage of<br>the OR-ing controller. $V_{FWD} = V_{EE} - V_{(NEG48Vx)}$ |                                                                                                                                                           | 10   | 25   | 40   | mV   |

| V <sub>(FWD,FST)</sub>       | Forward voltage where a fast pull up is activated.                                         | $V_{GATEx} = 5 V. V_{VEE} - V_{Neg48Vx} \uparrow$<br>measure when $I_{GATEx} = 100 \ \mu A$                                                               | 50   | 80   | 105  | mV   |

| V <sub>(RV)</sub>            | Fast reverse trip voltage.                                                                 |                                                                                                                                                           | 2    | 6    | 10   | mV   |

| BGATE                        |                                                                                            |                                                                                                                                                           |      |      |      |      |

| V <sub>VCC-BGATE</sub>       | Gate Output Voltage.                                                                       |                                                                                                                                                           |      | 0.65 | 1.1  | V    |

| (BGATE,SRS)                  | Gate sourcing current in regulation                                                        | $V_{VEE} - V_{Neg48Vx} = 50 \text{ mV}$                                                                                                                   |      | 5    |      | μA   |

| (BGATE,SINK)                 | Gate sinking current in regulation                                                         | $V_{VEE} - V_{Neg48Vx} = 0$                                                                                                                               |      | 5    |      | μΑ   |

| R <sub>GATE,SRC,FST</sub>    | Pull up resistance in fast sourcing mode.                                                  | $V_{VEE} - V_{Neg48Vx} = 100 \text{ mV}$ ; Measure current at $V_{GATEx} = 0 \text{ V}$ . R = $V_{VCC/I}$                                                 |      | 10   |      | kΩ   |

| (BGATE,FST)                  | Fast Gate pull down current                                                                | $V_{(VEE)} - V_{Neg48} = -15 \text{ mV}$                                                                                                                  | 0.4  | 1    | 1.5  | А    |

| PGb (Power Goo               | od Bar)                                                                                    |                                                                                                                                                           |      |      |      |      |

| V <sub>(GATE2,PGb)</sub>     | Threshold on GATE2 that triggers PGb to assert.                                            | Raise V <sub>GATE2</sub> until PGb asserts                                                                                                                | 6.5  | 7.25 | 8    | V    |

| V <sub>(PGb,PD)</sub>        | Pull down strength on PGb                                                                  | PGb sinking 1 mA                                                                                                                                          |      |      | 1.5  | V    |

| I(PGb,LEAK)                  | leakage current on PGb pin                                                                 |                                                                                                                                                           |      |      | 1    | μA   |

| OTSD (Over Ten               | nperature Shut Down)                                                                       |                                                                                                                                                           |      |      |      |      |

| T <sub>SD</sub>              | Shutdown temperature                                                                       | Temp Rising                                                                                                                                               | 135  | 155  | 175  | °C   |

| T <sub>SD,hyst</sub>         | Shutdown temperature<br>Hysteresis                                                         |                                                                                                                                                           |      | 8    |      | °C   |

JAJSF18A-DECEMBER 2017-REVISED JANUARY 2019

www.ti.com

Texas Instruments

### 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                                  | PARAMETER                                                  | TEST CONDITIONS                                                                                                             | MIN TYP | MAX | UNIT |

|----------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| VCC – Clar                       | nped Supply                                                |                                                                                                                             |         |     |      |

| t <sub>ID</sub>                  | Insertion Delay                                            | $V_{VCC}:$ 0 V $\rightarrow$ 10 V, measure delay before $V_{GATE}\uparrow$                                                  | 32      |     | ms   |

| UVEN                             |                                                            |                                                                                                                             |         |     |      |

| T <sub>UV,degl</sub>             | Deglitch on UVEN                                           |                                                                                                                             | 4       |     | μs   |

| ov                               |                                                            |                                                                                                                             |         |     |      |

| T <sub>OV,degl</sub>             | Deglitch on OV                                             |                                                                                                                             | 4       |     | μs   |

| SNS                              |                                                            |                                                                                                                             |         |     |      |

| T <sub>SNS,FST,R</sub><br>ESP    | Response time to large over current                        | $V_{SNS}$ steps from 0 mV to 60 mV. Measure time for GATE and GATE2 to come down.                                           | 300     |     | ns   |

| Neg48V                           |                                                            |                                                                                                                             |         |     |      |

| T <sub>Neg48V,FST</sub><br>,RESP | Response time to large reverse current                     | $V_{\rm NEG48V}$ steps from -40 mV to 15 mV. Measure time for BGATE to come down.                                           | 300     |     | ns   |

| PGb                              |                                                            |                                                                                                                             |         |     |      |

| t <sub>PGb,DEGL</sub>            | Deglitch of PGb. (GATE2 =<br>unloaded, raise GATE, measure | $\begin{array}{c} Power \ Good \uparrow (V_{(GATE)} \ 0 \ V \rightarrow 10 \ V) \\ Look \ for \ PGb \downarrow \end{array}$ | 1       |     | ms   |

|                                  | delay between GATE and PGb)                                | Power Good $\downarrow$ (V <sub>(GATE)</sub> 10 V $\rightarrow$ 0 V) Look for PGb $\uparrow$                                | 32      |     | ms   |

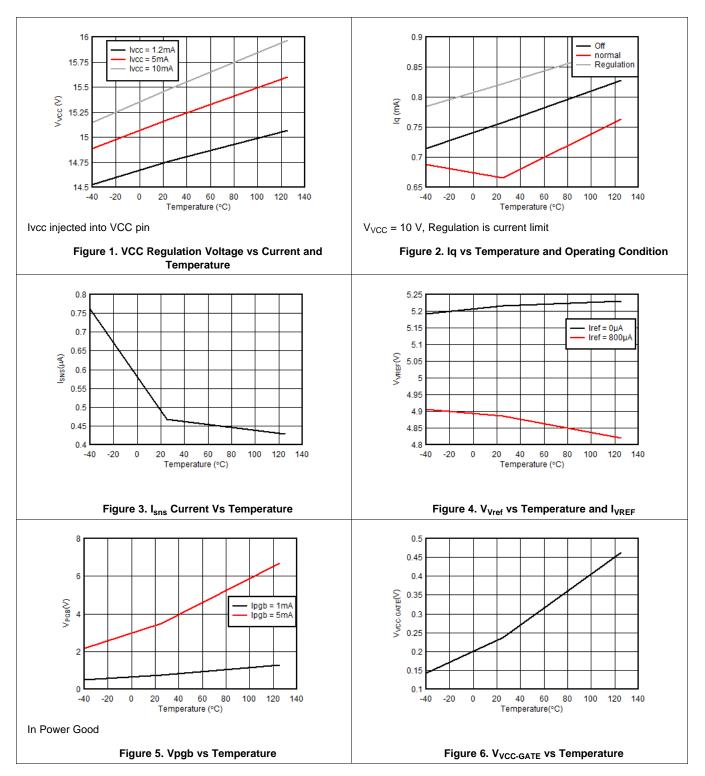

### 6.7 Typical Characteristics

**NSTRUMENTS**

EXAS

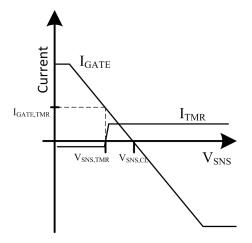

#### 7 Parameter Measurement Information

#### 7.1 Relationship between Sense Voltage, Gate Current, and Timer

The diagram below illustrates the relationship between the  $V_{SNS}$  (voltage across  $R_{SNS}$ ), Gate current, and the timer operation. The diagram is intended to help explain the various parameters in the electrical characteristic table and is not drawn to scale.

Note that  $I_{GATE}$  reduces as the sense voltage approaches the current limit threshold and it equals zero at the current limit regulation point. To ensure that the timer always runs when the IC is in regulation the timer starts at a slightly positive  $I_{GATE}$ .

Figure 7. Relationship Between Timer, Gate Current, and Sense Voltage (V<sub>GATE</sub> = 5 V)

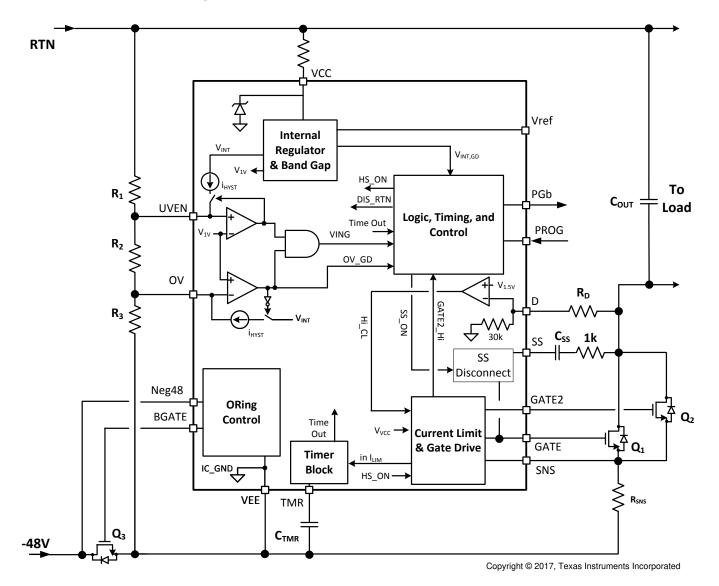

### 8 Detailed Description

### 8.1 Overview

The TPS23523 is an integrated hot swap and Single OR-ing controller that enables high power telecom systems to comply with stringent transient requirements. The soft start cap disconnect allows soft start at start-up and disconnects the soft start cap during normal operation. This allows for the use of smaller hot swap FETs without hurting the transient response. GATE2 is a second hot swap FET driver, which only turns ON when the main hot swap FET is fully on. Thus the FETs driven by GATE2 don't need to have strong SOA. This saves space and BOM cost in high power applications that require multiple hot swap FETs. The 400  $\mu$ A sourcing current allows fast recovery, which helps to avoid system resets during lightning surge tests. The dual current limit makes it easier to pass brown outs and input steps such as required by the ATIS 0600315.2013. Finally, the TPS23523 offers accurate undervoltage and overvoltage protection with programmable thresholds and hysteresis.

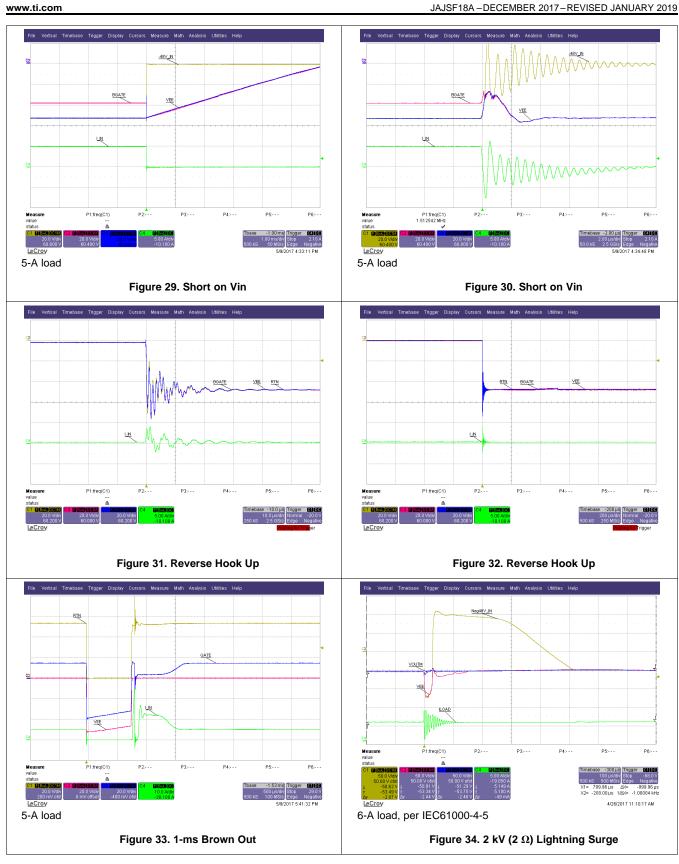

The TPS23523 integrates an OR-ing controller, making it ideal for -48 V systems that require reverse hook-up protection and reverse-current protection. The OR-ing controller protects the output when the input drops avoiding system resets. The OR-ing controller will turn off if any reverse current is detected.

### 8.2 Functional Block Diagram

# INSTRUMENTS

www.ti.com

#### 8.3 Feature Description

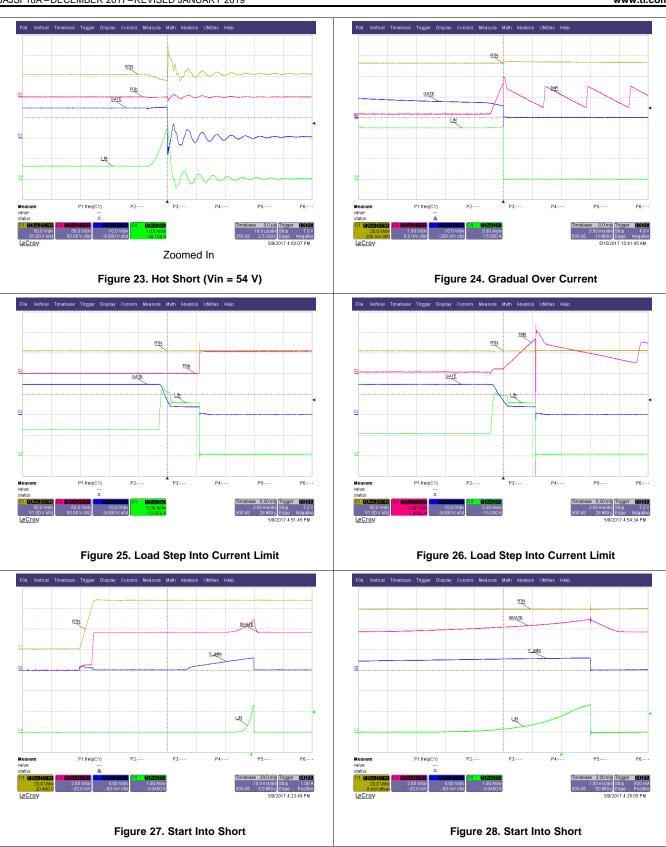

#### 8.3.1 Current Limit

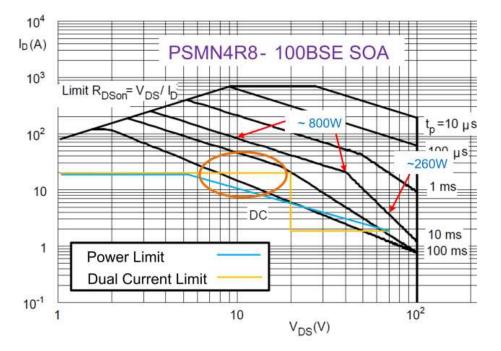

The TPS23523 utilizes two current limit thresholds:

- $I_{CL1}$  also referred to as high current limit threshold, which is used when the V<sub>DS</sub> of the hot swap FET is low.

- I<sub>CL2</sub> lower current limit threshold, which is used when the V<sub>DS</sub> of the hot swap FET is high.

This dual level protection scheme ensures that the part has a higher chance of riding out voltage steps and other transients due to the higher current limit at low  $V_{DS}$ , while protecting the MOSFET during start into short and hotshort events, by setting a lower current limit threshold for conditions with high  $V_{DS}$ . The transition threshold is programmed with a resistor that is connected from the drain of the hot swap FET to the D pin of the TPS23523. The figure below illustrates an example with a  $I_{CL1}$  set to 25 A and  $I_{CL2}$  set to 3 A. Note that compared to a traditional SOA protection scheme this approach allows better utilization of the SOA in the 10 V <  $V_{DS}$ . < 40-V range, which is critical in riding through transients and voltage steps.

Note that in both cases the TPS23523 regulated the gate voltage to enforce the current limit. However, this regulation is not very fast and doesn't offer the best protection against hot-shorts on the output. To protect in this scenario a fast comparator is used, which quickly pulls down the gate in case of severe over current events (2x bigger than  $V_{CL1}$ ).

Figure 8. Dual Current Limit vs FET Power Limit

#### 8.3.1.1 Programming the CL Switch-Over Threshold

The V<sub>DS</sub> threshold when the TPS23523 switches over from  $I_{CL1}$  to  $I_{CL2}$  (V<sub>D,SW</sub>) can be computed using Equation 1. For example, if a 15-V switch over is desired, R<sub>D</sub> should be set to 270 k $\Omega$ .

$$V_{\text{DS,SW}} = \frac{1.5 \text{ V} \times (30 \text{ k}\Omega + \text{R}_{\text{D}})}{30 \text{ k}\Omega}$$

(1)

#### 8.3.1.2 Setting Up the PROG Pin

The PROG pin can be tied to VEE, left floating, or tied to VEE through a resistor to adjust  $V_{SNS,CL1}$  and the ratio of fast trip to current limit. The options are set as follows:

•PROG = NC or Float: V<sub>SNS,CL1</sub> = 25 mV, V<sub>SNS,FST</sub> is 2x V<sub>SNS,CL1</sub>

•R<sub>PROG</sub> = 196 k $\Omega$  (1%): V<sub>SNS,CL1</sub> = 25 mV, V<sub>SNS,FST</sub> is 3x V<sub>SNS,CL1</sub>

#### Feature Description (continued)

• $R_{PROG}$  = 66.5 k $\Omega$  (1%):  $V_{SNS,CL1}$  = 40 mV,  $V_{SNS,FST}$  is 3x  $V_{SNS,CL1}$ •PROG = VEE:  $V_{SNS,CL1}$  = 40 mV,  $V_{SNS,FST}$  is 2x  $V_{SNS,CL1}$

#### 8.3.1.3 Programming CL1

The current limit at low  $V_{DS}$  (I<sub>CL1</sub>) of the TPS23523 can be computed using Equation 2.

$$I_{CL1} = \frac{V_{SNS,CL1}}{R_{SNS}}$$

(2)

To compute  $I_{CL1}$  for a 1-m $\Omega$  sense resistor use Equation 3 below.

$$I_{CL1} = \frac{V_{SNS,CL1}}{R_{SNS}} = \frac{25 \text{ mV}}{1 \text{ m}\Omega} = 25 \text{ A}$$

(3)

#### 8.3.1.4 Programming CL2

The current limit at high  $V_{DS}$  (I<sub>CL2</sub>) of the TPS23523 can be computed using Equation 4.

$$I_{CL2} = \frac{V_{SNS,CL2}}{R_{SNS}}$$

(4)

To compute  $I_{CL2}$  for a 1-m $\Omega$  sense resistor use Equation 5.

$$I_{CL2} = \frac{V_{SNS,CL2}}{R_{SNS}} = \frac{3 \text{ mV}}{1 \text{ m}\Omega} = 3 \text{ A}$$

(5)

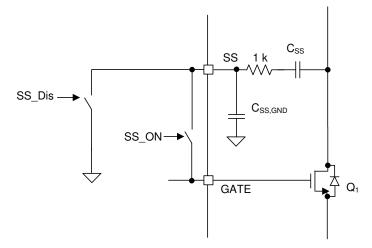

#### 8.3.2 Soft Start Disconnect

The inrush current into the output capacitor ( $C_{OUT}$ ) can be limited by placing a capacitor between the SS (Soft Start) pin and the drain of the hot swap MOSFET. In that case the inrush current can be computed using Equation 6.

$$I_{\rm INR} = \frac{C_{\rm OUT} \times I_{\rm GATE,SRS,START}}{C_{\rm SS}} = \frac{660 \,\mu\text{F} \times 20 \,\mu\text{A}}{33 \,\text{nF}} = 0.4 \,\text{A} \tag{6}$$

Note that with most hot swap the  $C_{SS}$  pin is tied simply to the gate pin, but this can interfere with performance during normal operation if transients or short circuits are encountered. In addition the  $C_{SS}$  capacitor tends to pull up the gate during hot plug and cause shoot through current if it is always tied to the gate. For that reason the TPS23523 has a disconnect switch between the gate pin and the SS pin as well as a discharge resistor. During the initial hot plug and during the insertion delay the switch between SS and GATE is open and SS is being discharged to GND through a resistor. Then during start-up SS and GATE are connected to limit the slew rate. Once in normal operation the SS pin is not tied to GATE and it is not shorted to GND, which prevents it from interfering with the operation during transients.

### Feature Description (continued)

Figure 9. Implementation of SS Disconnect

#### 8.3.3 Timer

Timer is a critical feature in the hot swap, which manages the stress level in the MOSFET. The timer will source and sink current into the timer capacitor as follows:

- Not in current limit: sink 2 µA

- If the part is in current limit and V<sub>GATE</sub> < V<sub>GATE,TH</sub>, the timer sources current as follows:

- V<sub>D</sub> < V<sub>D,CL SW</sub>: source 10 µA

- $V_D > V_{D,CL SW}$ : source 50 µA

The TPS23523 times out and shuts down the hot swap as follows.

- If  $V_D < V_{D,TMR SW}$  then the hot swap times out when  $V_{TMR}$  reaches 1.5 V.

- If  $V_D > V_{D,TMR,SW}$  then the hot swap times out when  $V_{TMR}$  reaches 0.75 V.

The above behavior maximizes the ability of the hot swap to ride out voltage steps, while ensuring that the FET remains safe even if the part can not ride out a voltage step.

A cool down period follows after the part times out. During this time the timer performs the following:

- Discharge C<sub>TMR</sub> with a 2-µA current source until 0.5 V

- Charge C<sub>TMR</sub> with a 10-µA current source until it is back to 1.5 V.

- Repeat the above 64 times

- Discharge timer to 0 V.

The part attempts to restart after finishing the above. If the UVEN signal is toggled while the 64 cycles are in progress the part restarts immediately after the 64 cycles are completed.

The timer operates as follows when recovering from POR:

- If V<sub>TMR</sub> < 0.5 V:</li>

- Proceed to regular startup

- Do not discharge  $V_{TMR}$

- If V<sub>TMR</sub> > 0.5 V:

- Go through 64 charge/discharge cycles

- Discharge V<sub>TMR</sub>

- Proceed to startup

The Time Out ( $T_{TO}$ ) can be computed using the equations below. Note that the time out depends on the V<sub>DS</sub> of the MOSFET.

(8)

#### Feature Description (continued)

$$T_{TO} = \frac{C_{TMR} \times V_{TMR}}{I_{TMR,SRS}}$$

(7)

$$T_{TO}(V_D < 0.75 V) = \frac{C_{TMR} \times 1.5 V}{10 \ \mu A}$$

$$T_{TO}(0.75 \text{ V} < V_D < 1.5 \text{ V}) = \frac{C_{TMR} \times 0.75 \text{ V}}{10 \ \mu \text{A}}$$

(9)

$$T_{TO}(V_D > 1.5 V) = \frac{C_{TMR} \times 0.75 V}{50 \ \mu A}$$

(10)

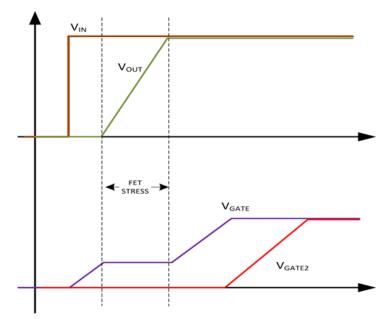

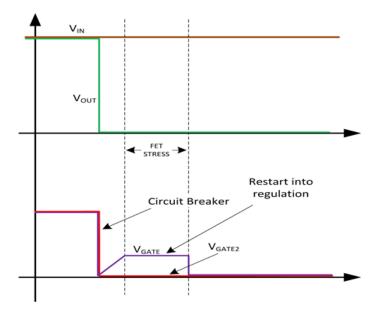

#### 8.3.4 Gate 2

The TPS23523 features a second hot swap Gate drive, which can be used to save BOM cost and size in applications that require multiple hot swap MOSFETs. The 2nd MOSFET is only turned ON when the main FET is enhanced. As a result the 2nd MOSFET doesn't operate with large current and large voltage across it, thus reducing the SOA requirements. In many cases a 5x6 QFN FET can replace a D<sup>2</sup>PACK FET. The following figures show the operation during start-up and Hot Short event. It can be seen that the second FET is OFF during stressful operation and turns on during normal operation to improve steady state efficiency and reduce power losses.

Figure 10. Gate 2 Operation During Start-Up

### Feature Description (continued)

Figure 11. Gate2 Operation During Hot Short

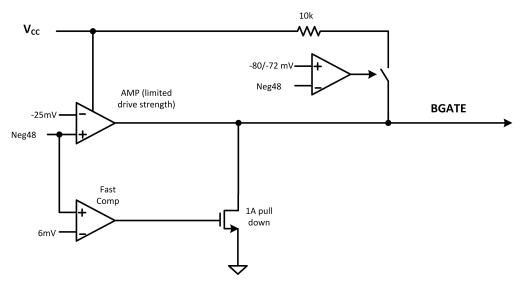

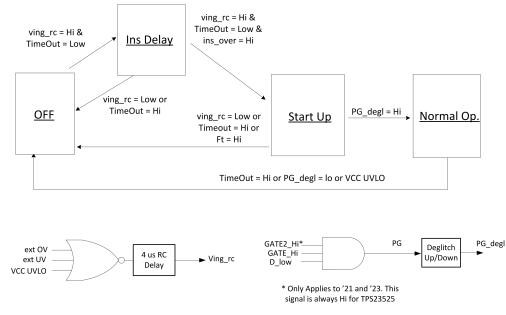

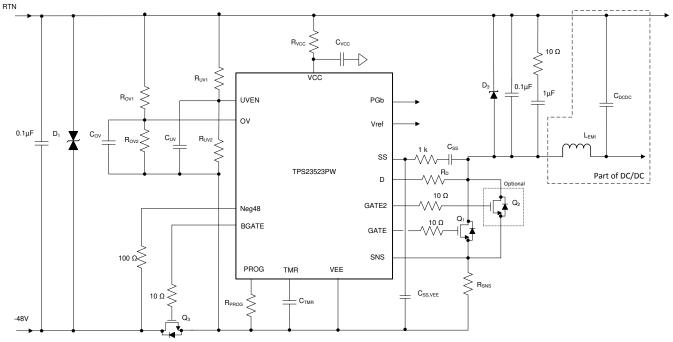

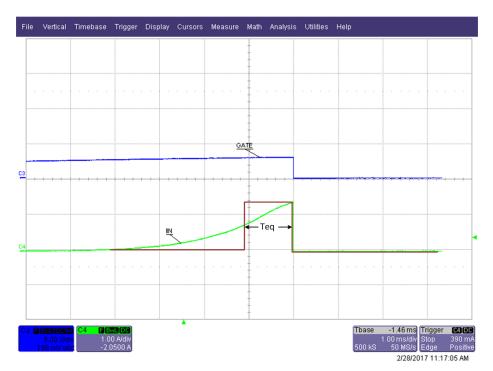

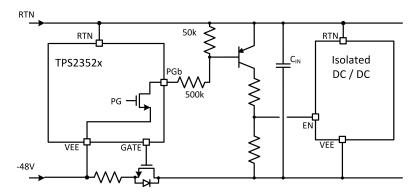

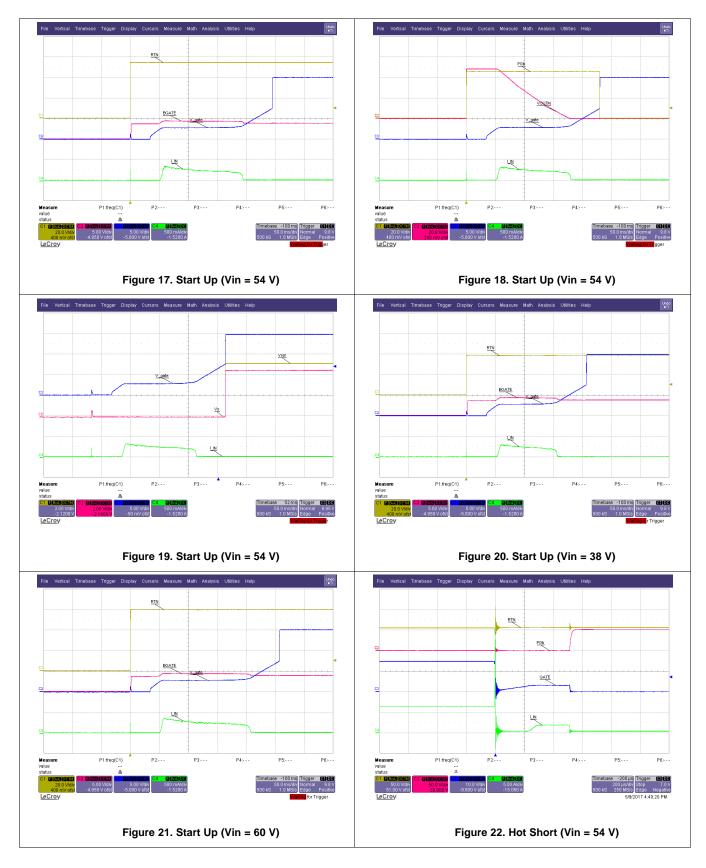

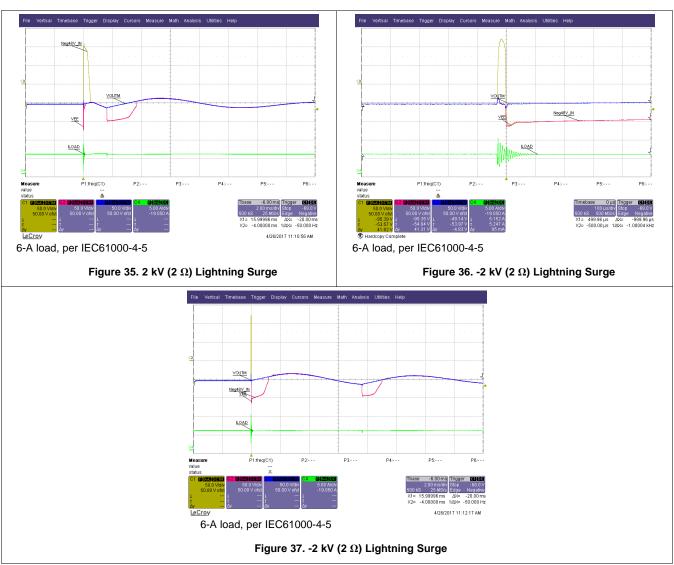

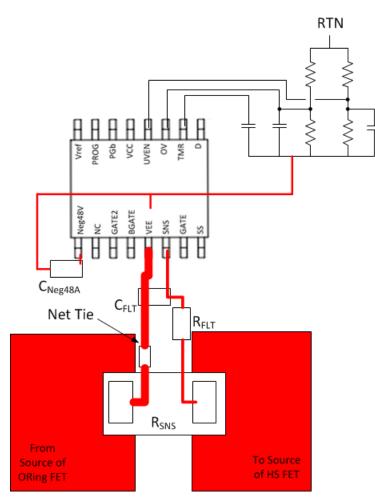

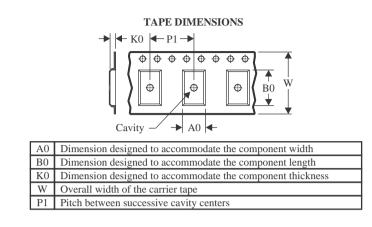

#### 8.3.5 OR-ing