TPS254900-Q1

JAJSCJ4A - SEPTEMBER 2016-REVISED OCTOBER 2016

# TPS254900-Q1 車載用USBホスト充電器、V<sub>BATT</sub>への短絡保護機能搭載

## 1 特長

- 下記内容でAEC-Q100認定済み

- デバイスHBM ESD分類レベルH2

- デバイスCDM ESD分類レベルC5

- 入力電圧範囲: 4.5V~6.5V

- 45mΩ(標準値)の ハイサイドMOSFETを内蔵

- 最大連続出力電流: 3A

- コネクタでV<sub>BUS</sub> ±5%のケーブル補償精度

- USB BC 1.2 CDPおよびSDPモードをサポート

- OUT、DP IN、DM INピンのバッテリ短絡保護

- DP\_INとDM\_INはIEC 61000-4-2規格に準拠

- ±8kV接触および±15kV空中放電

- 3mm×4mmの20ピンQFNパッケージ

### 2 アプリケーション

- 車載用USB充電ポート(ホストおよびハブ)

- 車載用USB保護

## 3 概要

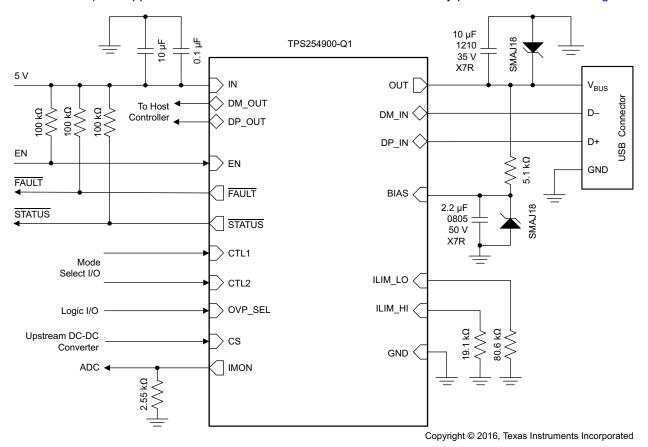

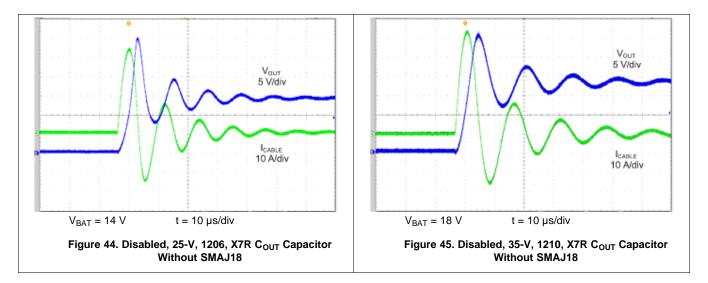

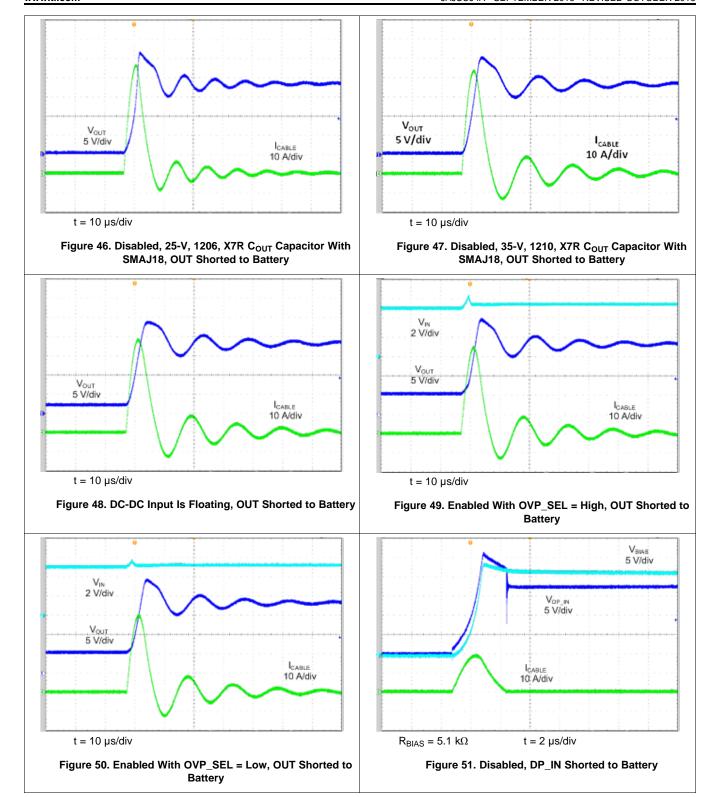

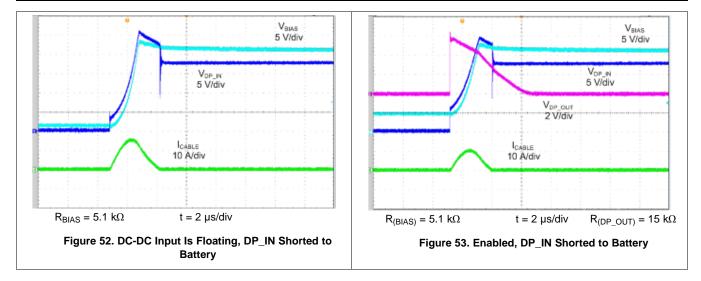

TPS254900-Q1デバイスはUSB充電ポート・コントローラ およびパワー・スイッチで、バッテリ短絡保護機能を備えています。この機能により、OUT、DM\_IN、DP\_INが保護されます。これら3本のピンは、18Vまでの電圧に耐えられます。バッテリへの短絡状況が発生すると、内部の

MOSFETが迅速にオフになります。この迅速なオフは、上流のDC/DCコンバータ、プロセッサ、ハブ・データ・ラインを保護するため非常に重要です。

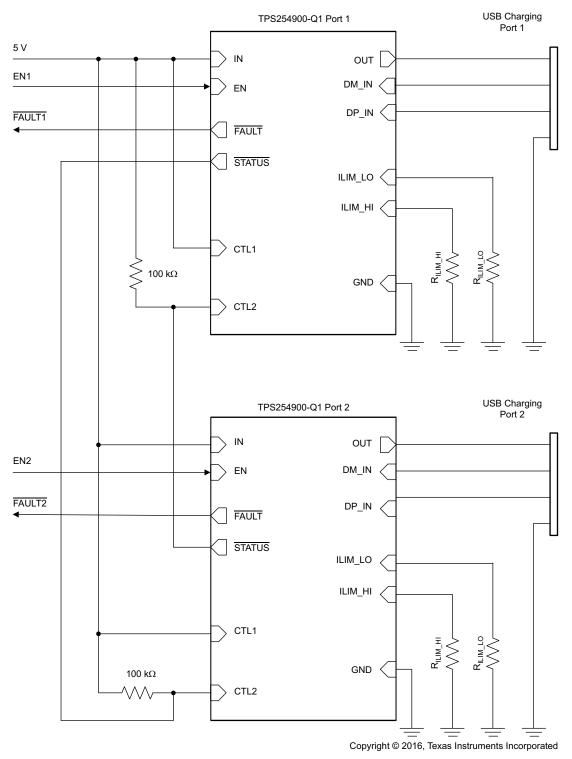

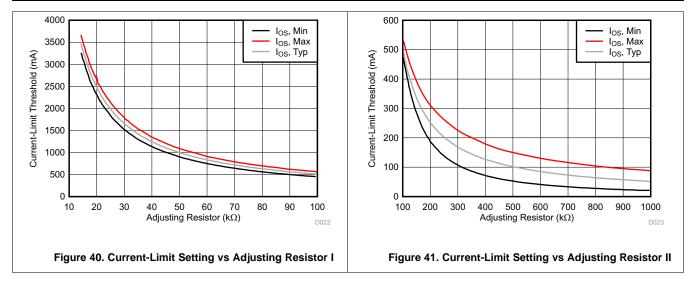

TPS254900-Q1 45mΩパワー・スイッチには2つの選択可能な可変の電流制限があり、隣接するポートに重い負荷が発生している場合に電流制限値を低く調整し、ポートの電力を管理できます。これは、複数のポートを持つシステムや、上流の電源の容量が限られている場合に重要です。

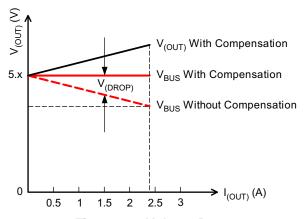

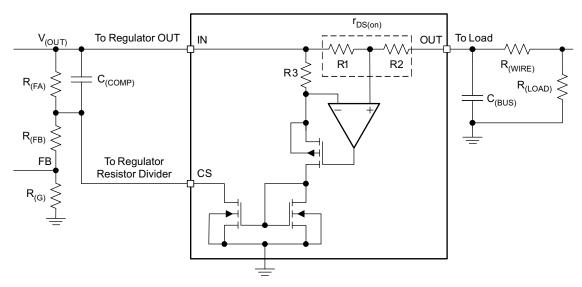

TPS254900-Q1には電流センス出力があり、上流の電源を制御して、大きな充電電流が供給されている場合でも、USBポートで5Vを維持できます。この機能は、USBケーブルが長く、高速充電を行う携帯機器によって大きな電圧低下が発生するようなシステムで重要です。

電流モニタにより、システムはIMON電圧を監視して、負荷電流をリアルタイムで監視できます。この電流モニタは非常に便利で、動的なポート電力管理にも使用できます。

また、TPS254900-Q1デバイスはDP\_INおよびDM\_IN について、IEC 61000-4-2、レベル4準拠のESD保護機 能を備えています。

## 製品情報<sup>(1)</sup>

| 型番           | パッケージ     | 本体サイズ(公称)     |

|--------------|-----------|---------------|

| TPS254900-Q1 | WQFN (20) | 3.00mm×4.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

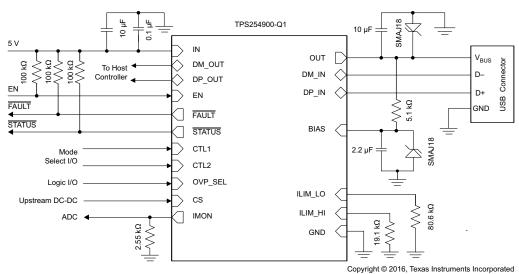

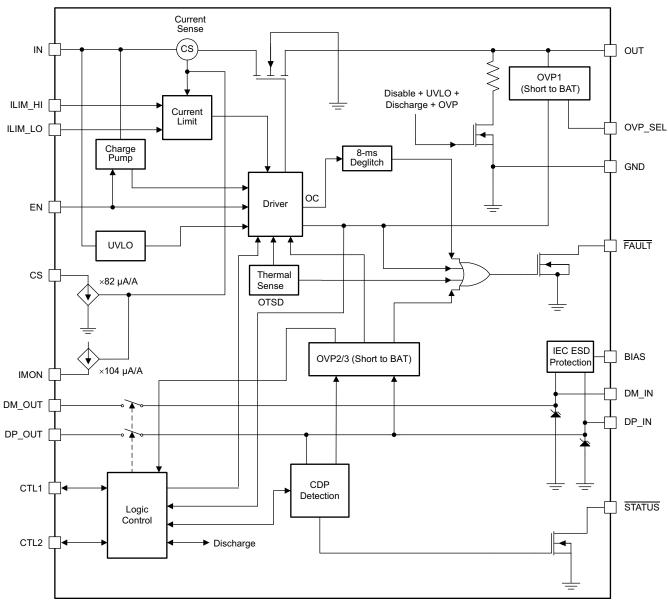

#### 回路図

# 目次

| 1<br>2<br>3<br>4<br>5<br>6 | 特長                                                                                                                                                                                                    | 11 | 8.4 Device Functional Modes |                |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------|----------------|

| 7<br>8                     | Parameter Measurement Information       15         Detailed Description       16         8.1 Overview       16         8.2 Functional Block Diagram       17         8.3 Feature Description       17 | 13 | <ul><li>12.5 商標</li></ul>   | 33<br>33<br>33 |

# 4 改訂履歴

| 2016年9月発行のものから更新                           | Page |

|--------------------------------------------|------|

| <ul><li>データシートを制品プレビューから書産データへ恋雨</li></ul> | 1    |

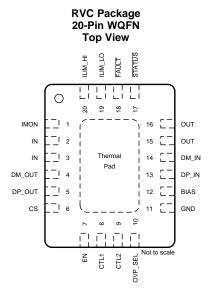

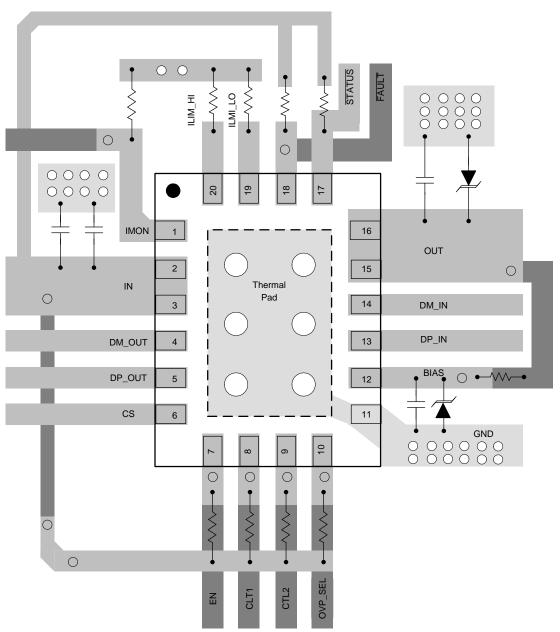

## 5 Pin Configuration and Functions

## **Pin Functions**

| PIN TYPE(1) |       |                     | DECORPORTION                                                                                                                                                                           |  |

|-------------|-------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                            |  |

| BIAS        | 12    | PWR                 | Used for IEC protection. Typically, connect a 2.2- $\mu$ F capacitor and a transient-voltage suppressor (TVS) to ground and 5.1 k $\Omega$ to OUT.                                     |  |

| CS          | 6     | 0                   | Linear cable compensation current. Connect to divider resistor of front-end dc-dc converter.                                                                                           |  |

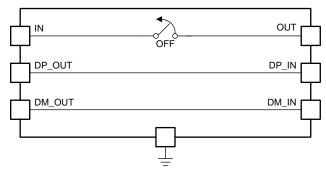

| CTL1        | 8     | 1                   | Logic-level control input for controlling the charging mode and the signal switches; see the Device Truth Table (TT).                                                                  |  |

| CTL2        | 9     | I                   | ogic-level control input for controlling the charging mode and the signal switches; see the evice Truth Table (TT).                                                                    |  |

| DM_IN       | 14    | I/O                 | D– data line to downstream connector                                                                                                                                                   |  |

| DM_OUT      | 4     | I/O                 | D– data line to upstream USB host controller                                                                                                                                           |  |

| DP_IN       | 13    | I/O                 | D+ data line to downstream connector                                                                                                                                                   |  |

| DP_OUT      | 5     | I/O                 | D+ data line to upstream USB host controller                                                                                                                                           |  |

| EN          | 7     | 1                   | Logic-level control input for turning the power and signal switches on or off. When EN is low, the device is disabled, and the signal and power switches are OFF.                      |  |

| FAULT       | 18    | 0                   | Active-low, open-drain output, asserted during overtemperature, overcurrent, and overvoltage conditions.                                                                               |  |

| GND         | 11    | _                   | Ground connection; should be connected externally to the thermal pad.                                                                                                                  |  |

| ILIM_HI     | 20    | I                   | External resistor used to set the high current-limit threshold.                                                                                                                        |  |

| ILIM_LO     | 19    | 1                   | External resistor used to set the low current-limit threshold and the load-detection current threshold.                                                                                |  |

| IMON        | 1     | 0                   | This pin sources a scaled-down ratio of current through the internal FET. A resistor from this pin to GND converts current to proportional voltage; used as an analog current monitor. |  |

| IN          | 2,3   | PWR                 | Input supply voltage; connect a 0.1-µF or greater ceramic capacitor from IN to GND as close to the IC as possible.                                                                     |  |

| OUT         | 15,16 | PWR                 | Power-switch output                                                                                                                                                                    |  |

| OVP_SEL     | 10    | I                   | Logic-level control input for choosing the OUT overvoltage threshold. When OVP_SEL is low, $V_{(OV\_OUT\_LOW)}$ is active. When OVP_SEL is high, $V_{(OV\_OUT\_HIGH)}$ is active.      |  |

| STATUS      | 17    | 0                   | Active-low open-drain output, asserted in load-detect conditions                                                                                                                       |  |

| Thermal pad |       | _                   | Thermal pad on the bottom of the package                                                                                                                                               |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input and output, PWR = Power

## 6 Specifications

## 6.1 Absolute Maximum Ratings

Voltages are with respect to GND unless otherwise noted (1)

|                  |                                  |                                                                        | MIN                | MAX                | UNIT |

|------------------|----------------------------------|------------------------------------------------------------------------|--------------------|--------------------|------|

|                  |                                  | CS, CTL1, CTL2, EN, FAULT, ILIM_HI, ILIM_LO, IN, IMON, OVP_SEL, STATUS | -0.3               | 7                  |      |

|                  | Voltage range                    | DM_OUT, DP_OUT                                                         | -0.3               | 5.7                | V    |

|                  |                                  | BIAS, DM_IN, DP_IN, OUT                                                | -0.3               | 18                 |      |

|                  | Continuous current               | DM_IN to DM_OUT or DP_IN to DP_OUT                                     | -100               | 100                | A    |

|                  | Continuous current               | OUT                                                                    | Internally limited |                    | mA   |

| I <sub>SRC</sub> | Continuous output source current | ILIM_HI, ILIM_LO, IMON                                                 | Inter              | nally limited      | Α    |

|                  | Continuous output sink surrent   | FAULT, STATUS                                                          |                    | 25                 | mA   |

| I <sub>SNK</sub> | Continuous output sink current   | CS                                                                     | Inter              | nally limited      | Α    |

| $T_{J}$          | Operating junction temperature   |                                                                        | -40                | Internally limited | °C   |

| T <sub>stg</sub> | Storage temperature              |                                                                        | -65                | 150                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                                                         |                                                                 | VALUE   | UNIT |

|--------------------|---------------------------------------------------------|-----------------------------------------------------------------|---------|------|

| V Electrostatic    | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2 000 <sup>(2)</sup>                                           |         |      |

|                    | Charged-device model (CDM), per AEC Q100-011            | ±750 <sup>(3)</sup>                                             | \/      |      |

| V <sub>(ESD)</sub> | discharge                                               | IEC 61000-4-2 contact discharge, DP_IN and DM_IN <sup>(4)</sup> | ±8 000  | V    |

|                    |                                                         | IEC 61000-4-2 air discharge, DP_IN and DM_IN <sup>(4)</sup>     | ±15 000 |      |

- (1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

- (2) The passing level per AEC-Q100 Classification H2.

- (3) The passing level per AEC-Q100 Classification C5

- (4) Surges per IEC 61000-4-2, level 4, 1999 applied from DP\_IN and DM\_IN to output ground of the TPS254900Q1EVM-817 (SLUUBIO) evaluation module.

#### 6.3 Recommended Operating Conditions

Voltages are with respect to GND unless otherwise noted.

|                  |                                |                                       | MIN  | NOM MAX | UNIT |

|------------------|--------------------------------|---------------------------------------|------|---------|------|

| $V_{(IN)}$       | Supply voltage                 | IN                                    | 4.5  | 6.5     | V    |

|                  | Input voltage                  | CTL1, CTL2, EN, OVP_SEL               | 0    | 6.5     | V    |

|                  | Input voltage                  | DM_IN, DM_OUT, DP_IN, DP_OUT          | 0    | 3.6     | V    |

|                  | Output continuous current      | OUT ( $-40$ °C $\leq T_A \leq 85$ °C) |      | 3       | Α    |

| I(OUT)           | Output continuous current      | DM_IN to DM_OUT or DP_IN to DP_OUT    | -30  | 30      | mA   |

|                  | Continuous output sink current | FAULT, STATUS                         |      | 10      | mA   |

| $R_{(ILIM\_xx)}$ | Current-limit-set resistors    |                                       | 14.3 | 1000    | kΩ   |

| TJ               | Operating junction temperature |                                       | -40  | 125     | °C   |

#### 6.4 Thermal Information

|                        |                                              | TPS254900-Q1 |      |

|------------------------|----------------------------------------------|--------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RVC (WQFN)   | UNIT |

|                        |                                              | 16 PINS      |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 37.9         | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 39.9         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 11.9         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.5          | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 11.8         | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 3.2          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

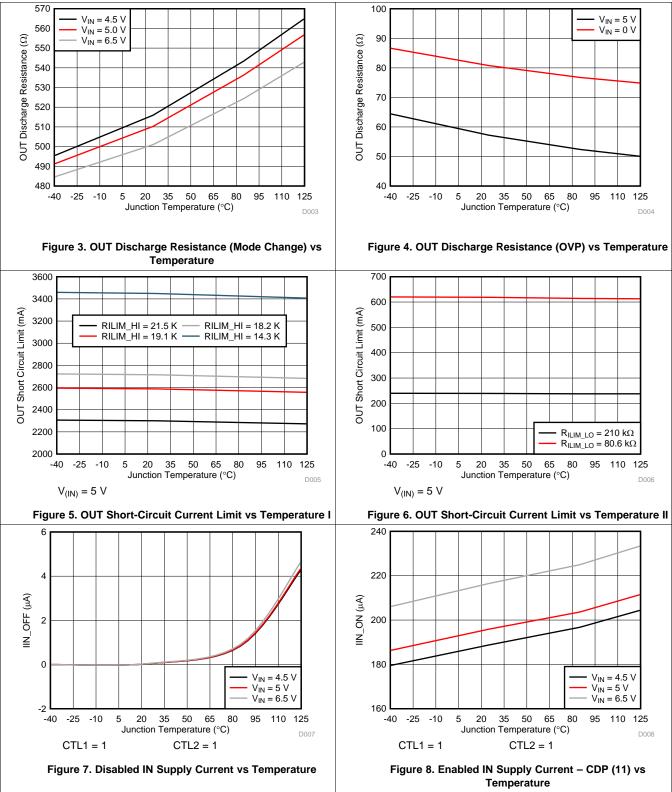

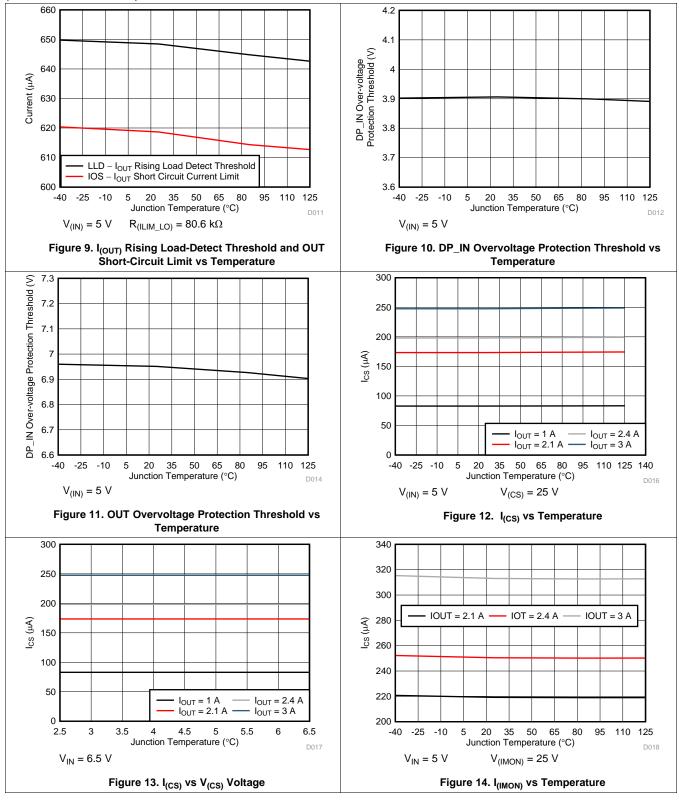

## 6.5 Electrical Characteristics

Unless otherwise noted,  $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 125^{\circ}\text{C}$  and  $4.5 \text{ V} \leq \text{V}_{(\text{IN})} \leq 6.5 \text{ V}, \text{V}_{(\text{EN})} = \text{V}_{(\text{CTL1})} = \text{V}_{(\text{CTL2})} = \text{V}_{(\text{IN})}, \text{R}_{(\text{FAULT})} = \text{R}_{(\text{STATUS})} = 10 \text{ k}\Omega, \text{R}_{(\text{ILIM}\_\text{HI})} = 19.1 \text{ k}\Omega, \text{R}_{(\text{ILIM}\_\text{LO})} = 80.6 \text{ k}\Omega.$  Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                       | PARAMETER                                 | TEST CONDITIONS                                                                                                                        | MIN  | TYP  | MAX  | UNIT |

|-----------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OUT – POW             | ER SWITCH                                 |                                                                                                                                        |      |      | '    |      |

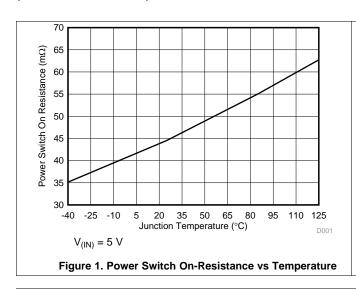

|                       |                                           | T <sub>J</sub> = 25°C                                                                                                                  |      | 45   | 55   |      |

| r <sub>DS(on)</sub>   | On-resistance <sup>(1)</sup>              | -40°C ≤ T <sub>J</sub> ≤ 85°C                                                                                                          |      | 45   | 69   | mΩ   |

|                       |                                           | –40°C ≤T <sub>J</sub> ≤ 125°C                                                                                                          |      | 45   | 77   |      |

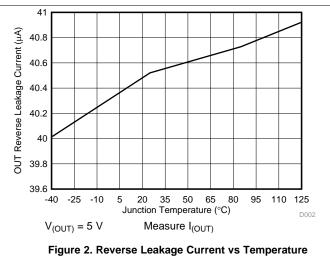

| I <sub>lkg</sub>      | Reverse leakage current                   | $V_{OUT} = 6.5 \text{ V}, V_{IN} = V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C},$ measure $I_{(IN)}$     |      | 0.01 | 2    | μΑ   |

| OUT - DISC            | HARGE                                     |                                                                                                                                        |      |      |      |      |

| R <sub>(DCHG)</sub>   | Discharge resistance (mode change)        |                                                                                                                                        | 400  | 500  | 630  | Ω    |

| CTL1, CTL2,           | , EN, OVP_SEL INPUTS                      |                                                                                                                                        |      |      | *    |      |

|                       | Input pin rising logic threshold voltage  |                                                                                                                                        | 1    | 1.35 | 2    | V    |

|                       | Input pin falling logic threshold voltage |                                                                                                                                        | 0.85 | 1.15 | 1.65 | V    |

|                       | Hysteresis (2)                            |                                                                                                                                        |      | 200  |      | mV   |

|                       | Input current                             | Pin voltage = 0 V or 6.5 V                                                                                                             | -1   |      | 1    | μΑ   |

| CURRENT L             | IMIT                                      |                                                                                                                                        |      |      |      |      |

|                       |                                           | $R_{(ILIM\_LO)} = 210 \text{ k}\Omega$                                                                                                 | 190  | 240  | 290  |      |

|                       |                                           | $R_{(ILIM\_LO)} = 80.6 \text{ k}\Omega$                                                                                                | 555  | 620  | 680  |      |

|                       |                                           | $R_{(ILIM\_LO)} = 21.5 \text{ k}\Omega$                                                                                                | 2145 | 2300 | 2460 |      |

| los                   | OUT short-circuit current<br>limit        | $R_{(ILIM\_LO)} = 19.1 \text{ k}\Omega$                                                                                                | 2420 | 2590 | 2760 | mA   |

|                       |                                           | $R_{(ILIM\_HI)} = 18.2 \text{ k}\Omega$                                                                                                | 2545 | 2720 | 2895 |      |

|                       |                                           | $R_{(ILIM\_HI)} = 14.3 \text{ k}\Omega$                                                                                                | 3240 | 3455 | 3670 |      |

|                       |                                           | R <sub>(ILIM_HI)</sub> shorted to GND                                                                                                  | 5000 | 6500 | 8000 |      |

| SUPPLY CU             | RRENT                                     |                                                                                                                                        |      |      |      |      |

| I <sub>(IN_OFF)</sub> | Disabled IN supply current                | $V_{(EN)} = 0$ V, $V_{(OUT)} = 0$ V, $-40^{\circ}C \le T_{J} \le 85^{\circ}C$ , no 5.1-k $\Omega$ resistor (open) between BIAS and OUT |      | 0.1  | 5    | μΑ   |

|                       |                                           | SDP mode (CTL1, CTL2 = 0, 1)                                                                                                           |      | 170  | 250  |      |

| I <sub>(IN_ON)</sub>  | Enabled IN supply current                 | CDP mode (CTL1, CTL2 = 1, 1)                                                                                                           |      | 200  | 280  | μΑ   |

|                       |                                           | Client mode (CTL1, CTL2 = 0, 0)                                                                                                        |      | 120  | 210  |      |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature. Thermal effects must be taken into account separately.

<sup>(2)</sup> This parameter is provided for reference only and does not constitute part of TI's published device specifications for purposes of TI's product warranty.

## **Electrical Characteristics (continued)**

Unless otherwise noted,  $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 125^{\circ}\text{C}$  and  $4.5 \text{ V} \leq \text{V}_{(\text{IN})} \leq 6.5 \text{ V}, \text{V}_{(\text{EN})} = \text{V}_{(\text{CTL1})} = \text{V}_{(\text{CTL2})} = \text{V}_{(\text{IN})}, \text{R}_{(\text{FAULT})} = \text{R}_{(\text{STATUS})} = 10 \text{ k}\Omega, \text{R}_{(\text{ILIM}\_\text{H})} = 19.1 \text{ k}\Omega, \text{R}_{(\text{ILIM}\_\text{LO})} = 80.6 \text{ k}\Omega.$  Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                            | with respect to GND.  PARAMETER              | TEST CONDITIONS                                                   | MIN          | TYP  | MAX  | UNIT  |

|----------------------------|----------------------------------------------|-------------------------------------------------------------------|--------------|------|------|-------|

|                            | SE LOCKOUT, IN                               |                                                                   |              |      |      |       |

| V <sub>(UVLO)</sub>        | UVLO threshold voltage                       | IN rising                                                         | 3.9          | 4.15 | 4.3  | V     |

| (0120)                     | Hysteresis (3)                               | T <sub>J</sub> = 25°C                                             |              | 100  |      | mV    |

| FAULT                      | ,                                            | 0                                                                 |              |      |      |       |

|                            | Output low voltage                           | $I_{(FAULT)} = 1 \text{ mA}$                                      |              |      | 100  | mV    |

|                            | Off-state leakage                            | V <sub>(FAULT)</sub> = 6.5 V                                      |              |      | 2    | μA    |

| STATUS                     | on state tourlage                            | (FAULT)                                                           |              |      |      | Pr. 1 |

|                            | Output low voltage                           | I <sub>(STATUS)</sub> = 1 mA                                      |              |      | 100  | mV    |

|                            | Off-state leakage                            | $V_{(STATUS)} = 6.5 \text{ V}$                                    |              |      | 2    | μA    |

| THERMAL SHUT               |                                              | (STATUS) 515 T                                                    |              |      |      | μ.,   |

| T <sub>(OTSD2)</sub>       | Thermal shutdown threshold                   |                                                                   | 155          |      |      | °C    |

| T <sub>(OTSD1)</sub>       | Thermal shutdown threshold in current-limit  |                                                                   | 135          |      |      | °C    |

|                            | Hysteresis (3)                               |                                                                   |              | 20   |      | °C    |

| LOAD DETECT (              | $(V_{CTL1} = V_{CTL2} = V_{IN})$             | 1                                                                 | II           |      |      |       |

| I <sub>(LD)</sub>          | I <sub>OUT</sub> load detection<br>threshold | $R_{(ILIM\_LO)} = 80.6 \text{ k}\Omega$ , rising load current     | 585          | 650  | 715  | mA    |

|                            | Hysteresis (3)                               |                                                                   |              | 50   |      | mA    |

| DM_IN AND DP_              | IN OVERVOLTAGE PROTE                         | CTION                                                             | <b>"</b>     |      |      |       |

| V <sub>(OV_Data)</sub>     | Protection trip threshold                    | DP_IN and DM_IN rising                                            | 3.7          | 3.9  | 4.15 | V     |

| (= :_= = ::::)             | Hysteresis (3)                               | -                                                                 |              | 100  |      | mV    |

|                            | · · ·                                        | DP_IN = DM_IN = 18 V, IN = 5 V or 0 V                             |              | 200  |      |       |

| R <sub>(DCHG_Data)</sub>   | Discharge resistor after OVP(2)              | DP_IN = DM_IN = 5 V, IN = 5 V                                     |              | 370  |      | kΩ    |

| (= = : : = = = : : : ;     |                                              | DP_IN = DM_IN = 5 V, IN = 0                                       |              | 390  |      |       |

| OUT OVERVOLT               | TAGE PROTECTION                              |                                                                   | <b>"</b>     |      |      |       |

| V <sub>(OV_OUT_LOW)</sub>  | Protection trip threshold                    | OUT rising                                                        | 5.65         | 6    | 6.35 | V     |

| (= ======                  | Hysteresis (3)                               |                                                                   |              | 90   |      | mV    |

| V <sub>(OV_OUT_HIGH)</sub> | Protection trip threshold                    | OUT rising                                                        | 6.6          | 6.95 | 7.3  | V     |

| ( = = = - /                | Hysteresis (3)                               |                                                                   |              | 130  |      | mV    |

| _                          | 5                                            | OUT = 18 V, IN = 5 V                                              |              | 55   | 85   |       |

| R <sub>(DCHG_OUT)</sub>    | Discharge resistor                           | OUT = 18 V, IN = 0                                                |              | 80   | 120  | kΩ    |

| CABLE COMPE                | NSATION                                      |                                                                   | <del>-</del> |      |      |       |

|                            |                                              | Load = 3 A, $2.5 \text{ V} \le \text{V}_{(CS)} \le 6.5 \text{ V}$ | 234          | 246  | 258  |       |

|                            |                                              | Load = 2.4 A, 2.5 V $\leq$ V <sub>(CS)</sub> $\leq$ 6.5 V         | 187          | 197  | 207  | _     |

| I <sub>(CS)</sub>          | Sink current                                 | Load = 2.1 A, 2.5 V $\leq$ V <sub>(CS)</sub> $\leq$ 6.5 V         | 163          | 172  | 181  | μA    |

|                            |                                              | Load = 1 A, 2.5 V $\leq$ V <sub>(CS)</sub> $\leq$ 6.5 V           | 77           | 82   | 87   |       |

| CURRENT MON                | ITOR OUTPUT (IMON)                           | , (66)                                                            |              |      |      |       |

|                            | \ - /                                        | Load = 3 A, $0 \le V_{(IMON)} \le 2.5 \text{ V}$                  | 287          | 312  | 337  |       |

|                            |                                              | Load = 2.4 A, $0 \le V_{(IMON)} \le 2.5 \text{ V}$                | 230          | 250  | 270  |       |

| I <sub>(IMON)</sub>        | Source current                               | Load = 2.1 A, $0 \le V_{(IMON)} \le 2.5 \text{ V}$                | 201          | 218  | 235  | μΑ    |

| (IIVIOIN)                  |                                              | Load = 1 A, $0 \le V_{(IMON)} \le 2.5 \text{ V}$                  | 94           | 104  | 114  |       |

|                            |                                              | Load = 0.5 A, $0 \le V_{(IMON)} \le 2.5 \text{ V}$                | 44           | 52   | 60   |       |

<sup>(3)</sup> This parameter is provided for reference only and does not constitute part of TI's published device specifications for purposes of TI's product warranty.

## **Electrical Characteristics (continued)**

Unless otherwise noted,  $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 125^{\circ}\text{C}$  and  $4.5 \text{ V} \leq \text{V}_{\text{(IN)}} \leq 6.5 \text{ V}, \text{V}_{\text{(EN)}} = \text{V}_{\text{(CTL1)}} = \text{V}_{\text{(CTL2)}} = \text{V}_{\text{(IN)}}, \text{R}_{\text{(FAULT)}} = \text{R}_{\text{(STATUS)}} = 10 \text{ k}\Omega, \text{R}_{\text{(ILIM\_LO)}} = 19.1 \text{ k}\Omega, \text{R}_{\text{(ILIM\_LO)}} = 80.6 \text{ k}\Omega.$  Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

| R(HS_ON)   Pand DM switch on-resistance   30 mA   V(DP_OUT) = V(DM_OUT) = 2.4 V, I(DP_IN) = I(DM_IN) =   3.8   7.4   1.5 mA   V(DP_OUT) = V(DM_OUT) = 0 V, I(DP_IN) = I(DM_IN) =   0.05   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.15   0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            | PARAMETER                        | TEST CONDITIONS                                                                               | MIN  | TYP  | MAX  | UNIT |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| R(HS_ON)   DP and DM switch onesistance   30 mA   V <sub>(DP_OUT)</sub> = V <sub>(DM_OUT)</sub> = 2.4 V, I <sub>(DP_IN)</sub> = I <sub>(DM_IN)</sub> = 3.8 7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HIGH-BANDWID               | TH ANALOG SWITCH                 |                                                                                               |      |      |      |      |

| AR(HS_ON)    Switch resistance mismatch between DP and DM channels   V(DP_OUT) = V(DM_OUT) = 0 V, I(DP_IN) = I(DM_IN) =   0.05   0.15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D                          | DP and DM switch on-             |                                                                                               |      | 3.2  | 6.5  | 0    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | K(HS_ON)                   | resistance                       | $V_{(DP\_OUT)} = V_{(DM\_OUT)} = 2.4 \text{ V}, I_{(DP\_IN)} = I_{(DM\_IN)} = -15 \text{ mA}$ |      | 3.8  | 7.6  | Ω    |

| $ \begin{array}{c} \text{C}_{\text{(IO\_OFF)}} & \text{channels} & \bigvee_{\text{(DP\_OUT)}} = V_{\text{(DM\_OUT)}} = 2.4 \text{ V, } I_{\text{(DP\_IN)}} = I_{\text{(DM\_IN)}} = \\ -15  \text{mA} & \\ \text{C}_{\text{(IO\_OFF)}} & \text{DP and DM switch off-state} \\ \text{capacitance}^{(4)} & V_{\text{EN}} = 0 \text{ V, } V_{\text{(DP\_IN)}} = V_{\text{(DM\_IN)}} = 0.3 \text{ V, } Vac = 0.03 \\ V_{\text{PP}} \text{ , } f = 1 \text{ MHz} \\ \end{array} $ $ \begin{array}{c} \text{DP and DM switch on-state} \\ \text{capacitance}^{(4)} & V_{\text{(DP\_IN)}} = V_{\text{(DM\_IN)}} = 0.3 \text{ V, } Vac = 0.03 \text{ V}_{\text{PP}} \text{ , } f = 1 \\ \text{MHz} & \\ \text{DP and DM switch on-state} \\ \text{capacitance}^{(4)} & V_{\text{(DP\_IN)}} = V_{\text{(DM\_IN)}} = 0.3 \text{ V, } Vac = 0.03 \text{ V}_{\text{PP}} \text{ , } f = 1 \\ \text{MHz} & \\ \text{DP and DM switch on-state} \\ \text{C}_{\text{(IO\_ON)}} & V_{\text{(DP\_IN)}} = V_{\text{(DM\_IN)}} = 0.3 \text{ V, } Vac = 0.03 \text{ V}_{\text{PP}} \text{ , } f = 1 \\ \text{MHz} & \\ \text{DO_{-state isolation}} & \\ \text{DO_{-state cross-channel}} & f = 250  \text{MHz} & \\ \text{SO}_{\text{DM}} & \text{SO}_{\text{DM}} & \text{SO}_{\text{DM}} & \\ \text{DO_{-state cross-channel}} & f = 250  \text{MHz} & \\ \text{DO_{-state isolation}} & V_{\text{EN}} = 0 \text{ V, } V_{\text{(DP\_IN)}} = V_{\text{(DM\_IN)}} = 3.6 \text{ V, } V_{\text{(DP\_OUT)}} \\ \text{DV}_{\text{IOM_OUT)}} & \text{DV, measure I}_{\text{(DP\_OUT)}} & \text{DV, } \text{DO}_{\text{DO}} & \\ \text{DO_{-IN}} & \text{DO_{-IN}} & \text{DO_{-IN}} & \\ \text{DO_{-IN}} & \text{DO_{-IN}} & \text{DO_{-IN}} & \text{DO_{-IN}} & \\ \text{DO_{-IN}} & \text{DO_{-IN}} & \text{DO_{-IN}} & \text{DO_{-IN}} & \\ \text{DO_{-IN}}$ | IAD I                      |                                  |                                                                                               |      | 0.05 | 0.15 | Ω    |

| $ \begin{array}{c} C(IO\_OFF) & capacitance^{(4)} & V_PP ,  f = 1 MHz^T \\ C_{(IO_ON)} & DP and DM switch on\text{-state} \\ capacitance^{(4)} & V_{(DP_IN)} = V_{(DM_IN)} = 0.3 V ,  Vac = 0.03 V_PP ,  f = 1 \\ MHz & Id_DM Id_DM \\ DO^F state isolation^{(3)} & V_{(EN)} = 0 V ,   V_DM_IN \\ DO^T state cross-channel \\ isolation^{(4)} & f = 250 MHz \\ Id_IN DM^T DM^DM DM^T DM^T DM^T DM^T DM^T DM^T DM^T DM^T DM^DM DM^T DM$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $ \Delta R_{(HS\_ON)} $    |                                  |                                                                                               |      | 0.05 | 0.15 | 12   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C <sub>(IO_OFF)</sub>      |                                  |                                                                                               |      | 8.8  |      | pF   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C <sub>(IO_ON)</sub>       |                                  |                                                                                               |      | 10.9 |      | pF   |

| $I_{lkg(OFF)}  \text{Off-state leakage current}  \begin{array}{c} I_{lkg(OFF)} \\ I_{lkg(OFF)} \\ \end{array}  \begin{array}{c} V_{EN} = 0 \text{ V, V}_{(DP\_IN)} = V_{(DM\_IN)} = 3.6 \text{ V, V}_{(DP\_OUT)} \\ = V_{(DM\_OUT)} = 0 \text{ V, measure I}_{(DP\_OUT)} \text{ and} \\ I_{(DM\_OUT)} = 0 \text{ V, measure I}_{(DP\_OUT)} \\ \end{array}  \begin{array}{c} 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.1 \\$                                                                                                                                                                                                                                                         |                            | Off-state isolation(3)           | V <sub>(EN)</sub> = 0 V, f = 250 MHz                                                          |      | 8    |      | dB   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                  | f = 250 MHz                                                                                   |      | 30   |      | dB   |

| CHARGING DOWNSTREAM PORT DETECT $V_{(DM\_SRC)}$ DM_IN CDP output voltage $V_{(DP\_IN)} = 0.6 \text{ V}, -250 \text{ μA} < I_{(DM\_IN)} < 0 \text{ μA}$ 0.5       0.6       0.7 $V_{(DAT\_REF)}$ DP_IN rising lower window threshold for $V_{(DM\_SRC)}$ activation       0.36       0.36       0.36 $V_{(LGC\_SRC)}$ DP_IN rising upper window threshold for VDM_SRC de-activation       0.8       0.8 $V_{(LGC\_SRC\_HYS)}$ Hysteresis (4)       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $I_{lkg(OFF)}$             | Off-state leakage current        | $= V_{(DM\_OUT)} = 0 V$ , measure $I_{(DP\_OUT)}$ and                                         |      | 0.1  | 1.5  | μΑ   |

| $V_{(DM\_SRC)}$ DM_IN CDP output voltage $V_{(DP\_IN)} = 0.6 \text{ V}, -250 \text{ μA} < I_{(DM\_IN)} < 0 \text{ μA}$ 0.5 0.6 0.7 $V_{(DAT\_REF)}$ DP_IN rising lower window threshold for $V_{(DM\_SRC)}$ activation 0.36 0.4 $V_{(DM\_SRC)}$ 0.5 0.6 0.5 $V_{(LGC\_SRC)}$ 0.8 0.8 $V_{(LGC\_SRC)}$ DP_IN rising upper window threshold for VDM_SRC de-activation 0.8 0.8 0.8 $V_{(LGC\_SRC\_HYS)}$ Hysteresis (4) 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BW                         | Bandwidth (-3 dB) <sup>(4)</sup> | $R_{(L)} = 50 \Omega$                                                                         |      | 940  |      | MHz  |

| $\begin{array}{c} V_{(DAT\_REF)} & \begin{array}{c} DP\_IN \ rising \ lower \ window \\ threshold \ for \ V_{(DM\_SRC)} \\ activation \\ & \\ \\ V_{(LGC\_SRC)} \end{array} & \begin{array}{c} 0.36 \\ \\ 50 \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CHARGING DO                | WNSTREAM PORT DETECT             |                                                                                               |      |      |      |      |

| $\begin{array}{c cccc} V_{(DAT\_REF)} & & threshold for \ V_{(DM\_SRC)} \\ & & & & & & & & & & & & & & & & & & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{(DM\_SRC)}$            | DM_IN CDP output voltage         | $V_{(DP_{-}IN)} = 0.6 \text{ V}, -250  \mu\text{A} < I_{(DM_{-}IN)} < 0  \mu\text{A}$         | 0.5  | 0.6  | 0.7  | V    |

| V(LGC_SRC)     DP_IN rising upper window threshold for VDM_SRC de-activation     0.8       V(LGC_SRC_HYS)     Hysteresis <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{(DAT\_REF)}$           | threshold for $V_{(DM\_SRC)}$    |                                                                                               | 0.36 |      | 0.4  | V    |

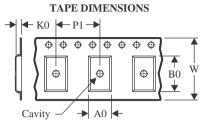

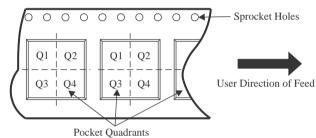

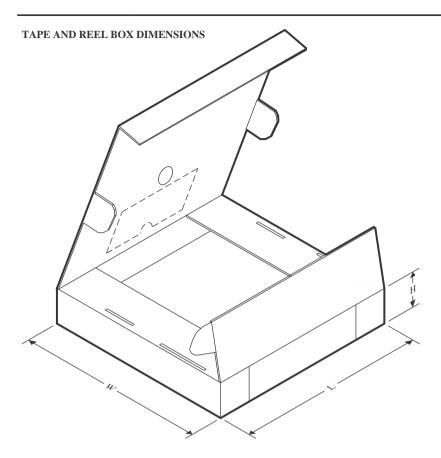

| V(LGC_SRC)     threshold for VDM_SRC de-activation     0.8     0.8       V(LGC_SRC_HYS)     Hysteresis <sup>(4)</sup> 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            | Hysteresis (4)                   |                                                                                               |      | 50   |      | mV   |