**TPS54360**

Community

JAJSBY0G -AUGUST 2012-REVISED JUNE 2018

# TPS54360 60V入力、3.5A、Eco-Mode™搭載の降圧型DC/DCコンバータ

## 特長

- 4.5V~60V (絶対最大定格65V)の入力範囲

- 連続電流3.5A、最小ピーク・インダクタ電流制限 4.5A

- 電流モード制御のDC/DCコンバータ

- 92mΩのハイサイドMOSFET

- 軽負荷で高い効率を実現するパルス・スキップ Eco-mode™

- 内蔵のブート再充電FETにより軽負荷時のドロッ プアウトを低減

- 動作時静止電流: 146µA

- シャットダウン時電流2uA

- 100kHz~2.5MHzの固定スイッチング周波数

- 外部クロックに同期

- 調整可能なUVLO電圧およびヒステリシス

- 内部ソフトスタート

- 高精度のサイクル単位電流制限

- 熱、過電圧、周波数フォールドバック保護

- 内部基準電圧: 0.8V、1%

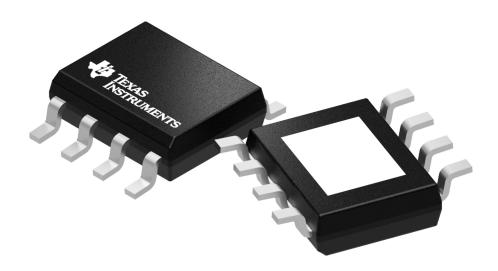

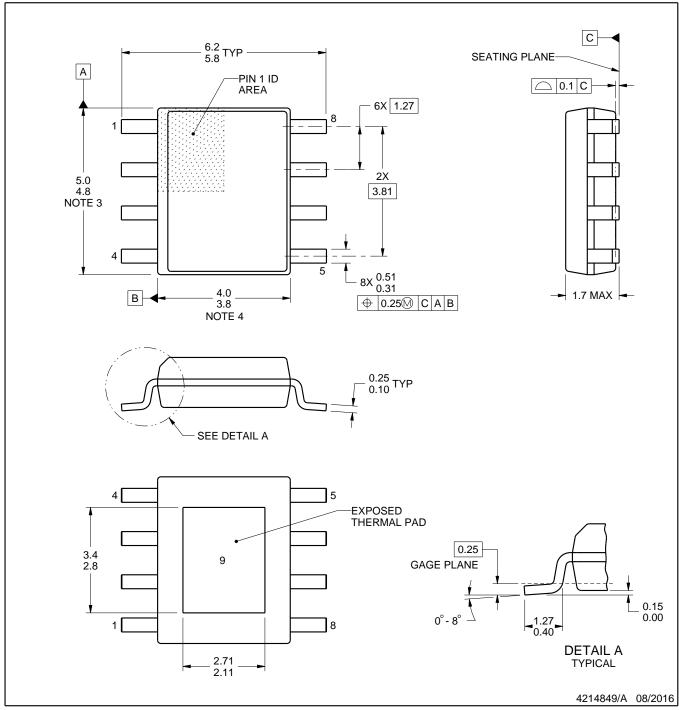

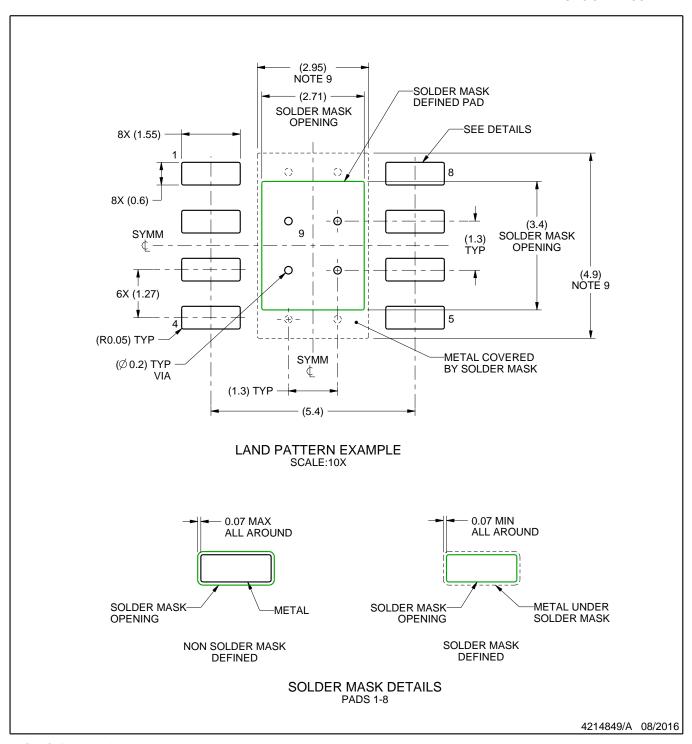

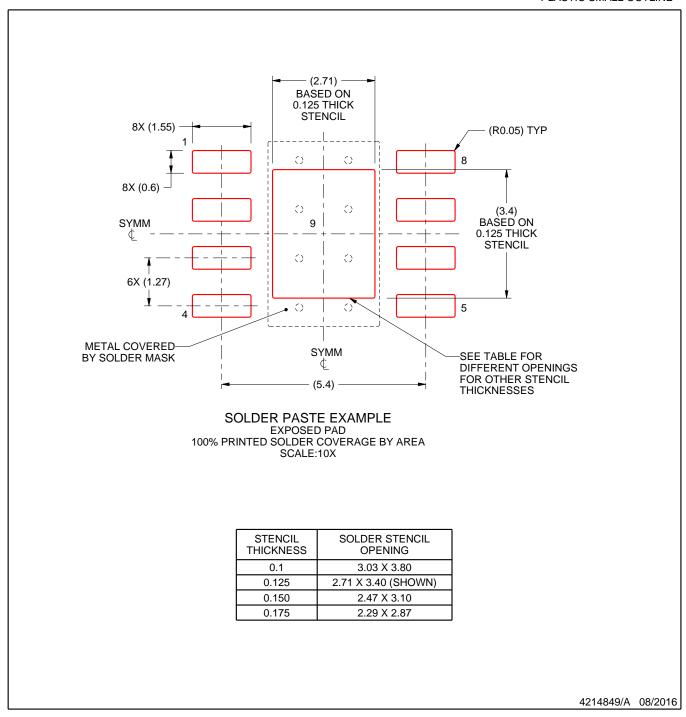

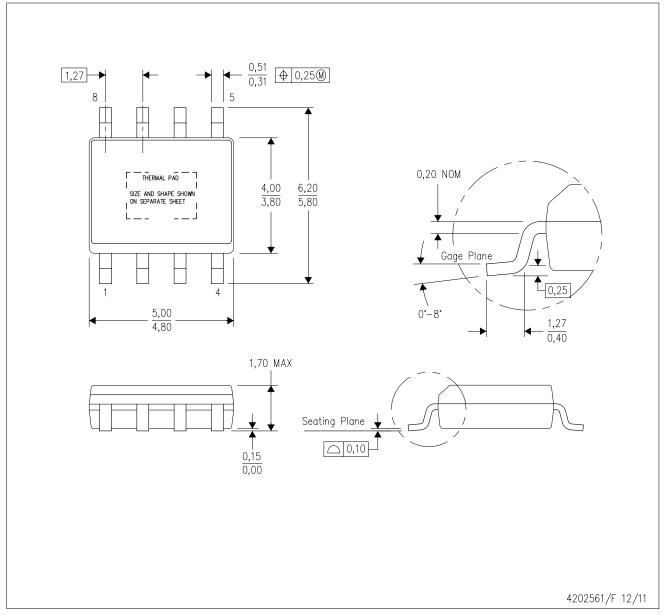

- 8端子のHSOIC付き PowerPAD™パッケージ

- 動作温度範囲T₁= -40℃~150℃

- WEBENCH® Power Designerにより、TPS54360 を使用するカスタム設計を作成

## 2 アプリケーション

12V、24V、48Vの産業用、車載用、通信用電源シス テム

## 3 概要

TPS54360は、ハイサイドMOSFETを内蔵した、60V、 3.5Aの降圧型レギュレータです。ISO 7637に準拠し、最 大65Vの負荷ダンプ・パルスに耐えることができます。 電流 モード制御により外部補償が単純化され、柔軟な部品選 択が可能になります。低リップルのパルス・スキップ・モード を使用すると、無負荷時の消費電流を146uAまで低減で きます。イネーブル・ピンをLowにすると、シャットダウン時 消費電流が2µAまで減少します。

低電圧誤動作防止は内部で4.3Vに設定されていますが、 イネーブル・ピンを使用してさらに高い電圧に設定すること ができます。起動時の出力電圧の上昇を内部で制御する ことにより、スタートアップを制御し、オーバーシュートを防 ぎます。

スイッチング周波数の範囲が広いため、効率または外部 部品のサイズを最適化できます。周波数フォールドバック と過熱シャットダウン機能によって、過負荷状態時に内部 部品および外部部品を保護します。

TPS54360は、8端子の熱的に強化されたHSOIC PowerPAD™パッケージで供給されます。

#### 製品情報

| 発注型番     | パッケージ     | 本体サイズ         |

|----------|-----------|---------------|

| TPS54360 | HSOIC (8) | 4.89mm×3.90mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

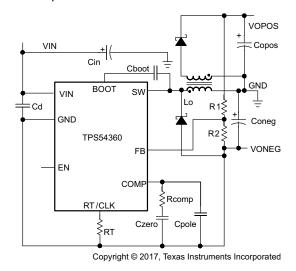

# 概略回路図

Copyright © 2017, Texas Instruments Incorporated

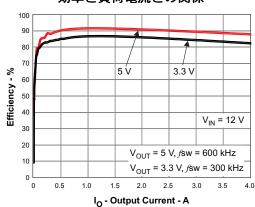

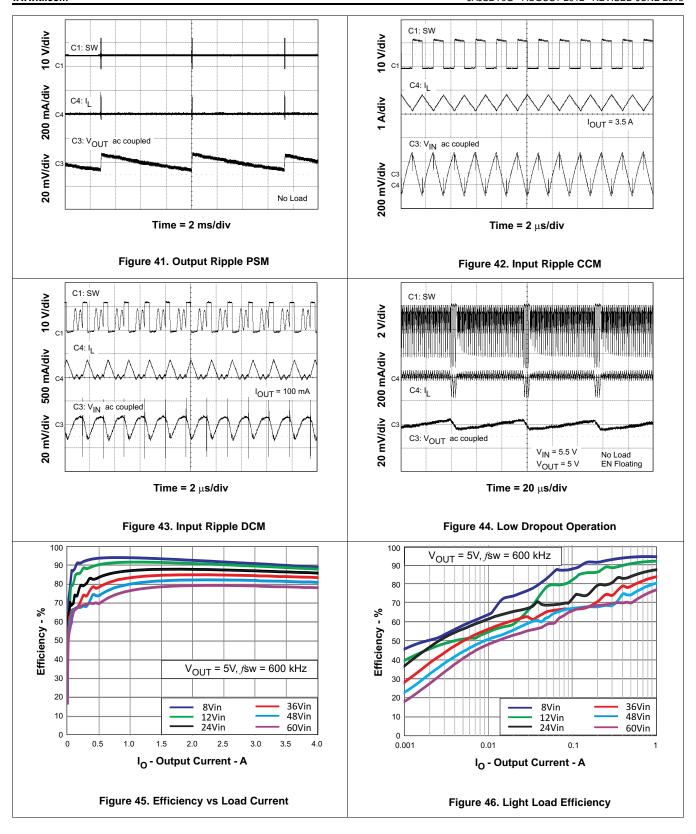

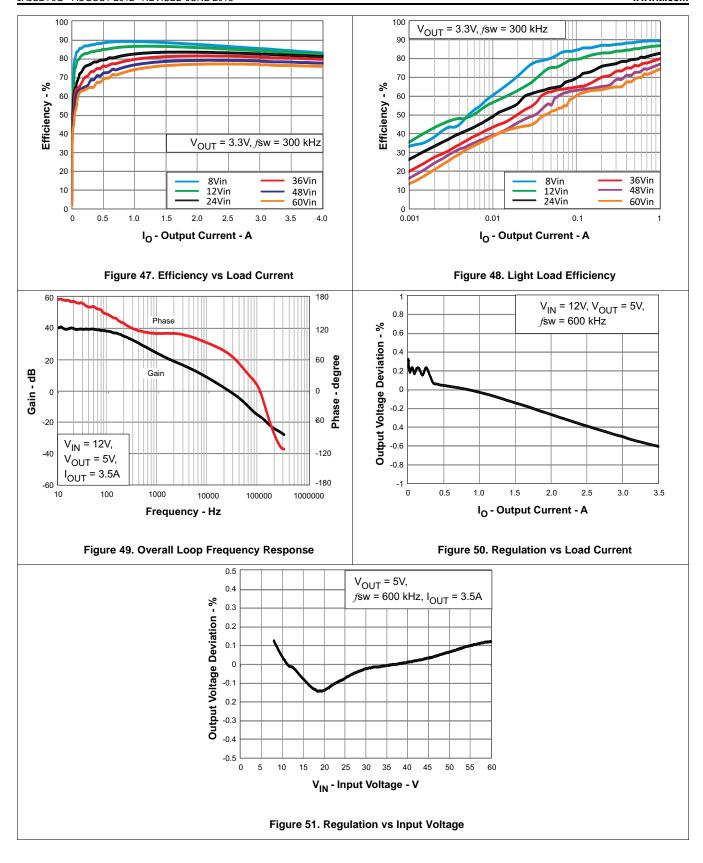

# 効率と負荷電流との関係

|   | ٠.            |

|---|---------------|

| _ |               |

| е | $\mathcal{I}$ |

| 1 | 特長1                                    |    | 7.3 Feature Description        | 19 |

|---|----------------------------------------|----|--------------------------------|----|

| 2 | アプリケーション                               |    | 7.4 Device Functional Modes    |    |

| 3 | 概要1                                    | 8  | Application and Implementation | 25 |

| 4 | 改訂履歴                                   |    | 8.1 Application Information    | 25 |

| 5 | Pin Configuration and Functions 4      |    | 8.2 Typical Application        | 25 |

| 6 | Specifications5                        | 9  | Power Supply Recommendations   | 37 |

|   | 6.1 Absolute Maximum Ratings 5         | 10 | Layout                         | 38 |

|   | 6.2 ESD Ratings                        |    | 10.1 Layout Guidelines         | 38 |

|   | 6.3 Recommended Operating Conditions 5 |    | 10.2 Layout Example            |    |

|   | 6.4 Thermal Information 5              | 11 | デバイスおよびドキュメントのサポート             |    |

|   | 6.5 Electrical Characteristics7        |    | 11.1 ドキュメントのサポート               |    |

|   | 6.6 Timing Requirements 8              |    | 11.2 ドキュメントの更新通知を受け取る方法        |    |

|   | 6.7 Typical Characteristics 8          |    | 11.3 コミュニティ・リソース               |    |

| 7 | Detailed Description 12                |    | 11.4 商標                        |    |

|   | 7.1 Overview 12                        |    | 11.5 静電気放電に関する注意事項             |    |

|   | 7.2 Functional Block Diagram 13        | 12 | メカニカル、パッケージ、および注文情報            | 39 |

|   |                                        |    |                                |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| R        | evision F (March 2017) から Revision G に変更                                                                                                                             | Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | 上端にTIリファレンス・デザイン用のナビゲーション・アイコンを 追加                                                                                                                                   | 1    |

| <u>•</u> | Added VBOOT clamping stipulation to Equation 2                                                                                                                       | 15   |

| Re       | evision E (March 2014) から Revision F に変更                                                                                                                             | Page |

| •        | 「特長」、「詳細な設計手順」、「デバイスのサポート」の各セクションにWEBENCHの情報を追記                                                                                                                      | 1    |

| •        | Changed the Handling Ratings table to the ESD Ratings table                                                                                                          | 5    |

| •        | Moved the Storage temperature to the Absolute Maximum Ratings table                                                                                                  | 5    |

| •        | Changed V <sub>IN</sub> MIN Value From: 4.5 V To: V <sub>O</sub> + V <sub>DO</sub> , and added Note 1 in the <i>Recommended Operating Conditions</i>                 | 5    |

| •        | Updated text and added Equation 1 and Equation 2 in Low Dropout Operation and Bootstrap Voltage (BOOT)                                                               | 14   |

| •        | Deleted text: "The start and stop voltage for a typical 5 V" and Figure: "5V Start/Stop Voltage" from the Low Dropout Operation and Bootstrap Voltage (BOOT) section | 14   |

| •        | Changed Equation 7 and Equation 8                                                                                                                                    | 16   |

| •        | Changed Equation 27                                                                                                                                                  | 26   |

| •        | Added new section: Minimum V <sub>IN</sub>                                                                                                                           | 31   |

| •        | Deleted 2 graphs named "Low Dropout Operation" from the Application Curves section                                                                                   | 34   |

| Re       | evision D (February 2013) から Revision E に変更                                                                                                                          | Page |

| •        | データシートを新しい <b>TI</b> レイアウトに変更し、「製品情報」表を追加                                                                                                                            | 1    |

| •        | Added the Handling Ratings table and Recommended Operating Conditions table                                                                                          | 5    |

| •        | Changed the Operating: nonswitching supply current TEST CONDITIONS From: FB = 0.83 V To: FB = 0.9 V                                                                  | 7    |

| •        | Changed RT/CLK high threshold MAX value From: 1.7 V To: 2 V                                                                                                          | 7    |

| •        | Changed Figure 6 title From: HIGH FREQUENCY RANGE To: LOW FREQUENCY RANGE                                                                                            | 8    |

| •        | Changed Figure 7 title From: LOW FREQUENCY RANGE To: HIGH FREQUENCY RANGE                                                                                            | 8    |

| Revision C (October 2012) から Revision D に変更                                           | Page |

|---------------------------------------------------------------------------------------|------|

| • Changed Figure 11 and Figure 12 From: I <sub>EN</sub> (μV) To: I <sub>EN</sub> (μA) | 9    |

| Revision B (September 2012) から Revision C に変更                                         | Page |

| Changed From: 20 mV/div To: 200 mV/div in Figure 42                                   | 34   |

| Revision A (September 2012) から Revision B に変更                                         | Page |

| <ul><li>「特長」の「シャットダウン時電流1μA」を「シャットダウン時電流2μA」に変更</li></ul>                             | 1    |

| 2012年8月発行のものから更新                                                                      | Page |

| <ul><li>デバイスの状態を製品プレビューから量産データに変更</li></ul>                                           | 1    |

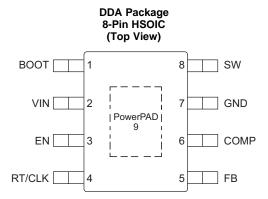

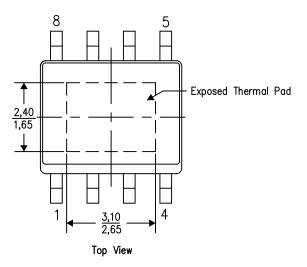

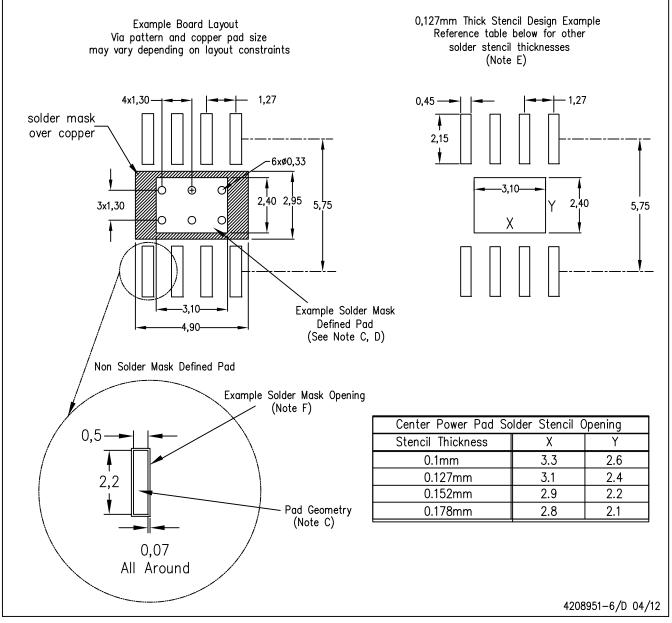

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN         |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| воот        | 1   | 0   | A bootstrap capacitor is required between BOOT and SW. If the voltage on this capacitor is below the minimum required to operate the high side MOSFET, the output is switched off until the capacitor is refreshed.                                                                                                                                                                                                                                                                                                                         |  |

| VIN         | 2   | I   | Input supply voltage with 4.5 V to 60 V operating range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| EN          | 3   | ı   | Enable terminal, with internal pull-up current source. Pull below 1.2 V to disable. Float to enable. Adjust the input undervoltage lockout with two resistors. See the <i>Enable and Adjusting Undervoltage Lockout</i> section.                                                                                                                                                                                                                                                                                                            |  |

| RT/CLK      | 4   | 1   | Resistor Timing and External Clock. An internal amplifier holds this terminal at a fixed voltage when using external resistor to ground to set the switching frequency. If the terminal is pulled above the PLL upper threshold, a mode change occurs and the terminal becomes a synchronization input. The internal amplifie disabled and the terminal is a high impedance clock input to the internal PLL. If clocking edges stop, the internal amplifier is re-enabled and the operating mode returns to resistor frequency programming. |  |

| FB          | 5   | I   | Inverting input of the transconductance (gm) error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| СОМР        | 6   | 0   | Error amplifier output and input to the output switch current (PWM) comparator. Connect frequency compensation components to this terminal.                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| GND         | 7   | -   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SW          | 8   | I   | The source of the internal high-side power MOSFET and switching node of the converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Thermal Pad | 9   | _   | GND terminal must be electrically connected to the exposed pad on the printed circuit board for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                       |                     | MIN  | MAX | UNIT |  |

|---------------------------------------|---------------------|------|-----|------|--|

|                                       | VIN                 | -0.3 | 65  |      |  |

|                                       | EN                  | -0.3 | 8.4 |      |  |

| Innut voltoge                         | BOOT                |      | 73  | V    |  |

| Input voltage                         | FB                  | -0.3 | 3   | V    |  |

|                                       | COMP                | -0.3 | 3   |      |  |

|                                       | RT/CLK              | -0.3 | 3.6 |      |  |

|                                       | BOOT-SW             |      | 8   |      |  |

| Output voltage                        | SW                  | -0.6 | 65  | V    |  |

|                                       | SW, 10-ns transient | -2   | 65  |      |  |

| Operating junction temperature        |                     | -40  | 150 | °C   |  |

| Storage temperature, T <sub>STG</sub> |                     | -65  | 150 | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                      |                                                   | MAX   | UNIT |

|----------------------|---------------------------------------------------|-------|------|

|                      | Human Body Model (HBM) ESD Stress Voltage (2)     | ±2000 | V    |

| V <sub>ESD</sub> (') | Charged Device Model (HBM) ESD Stress Voltage (3) | ±500  | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                     | MIN            | MAX  | UNIT |

|-----------------|-------------------------------------|----------------|------|------|

| V <sub>IN</sub> | Supply input voltage <sup>(1)</sup> | $V_O + V_{DO}$ | 60   | V    |

| Vo              | Output voltage                      | 0.8            | 58.8 | V    |

| Io              | Output current                      | 0              | 3.5  | Α    |

| $T_{J}$         | Junction temperature                | -40            | 150  | °C   |

<sup>(1)</sup> See Equation 1

## 6.4 Thermal Information

|                  |                                                         | TPS54360    |      |

|------------------|---------------------------------------------------------|-------------|------|

|                  | THERMAL METRIC <sup>(1)(2)</sup>                        | DDA (HSOIC) | UNIT |

|                  |                                                         | 8 PINS      |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (standard board) | 42.0        | °C/W |

| ΤιΨ              | Junction-to-top characterization parameter              | 5.9         | °C/W |

| ΨЈВ              | Junction-to-board characterization parameter            | 23.4        | °C/W |

| $\theta_{JCtop}$ | Junction-to-case(top) thermal resistance                | 45.8        | °C/W |

| $\theta_{JCbot}$ | Junction-to-case(bottom) thermal resistance             | 3.6         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Level listed above is the passing level per ANSI/ESDA/JEDEC JS-001. JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process. terminals listed as 1000 V may actually have higher performance.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process, terminals listed as 250 V may actually have higher performance.

<sup>(2)</sup> Power rating at a specific ambient temperature T<sub>A</sub> should be determined with a junction temperature of 150°C. This is the point where distortion starts to substantially increase. See power dissipation estimate in application section of this data sheet for more information.

# **Thermal Information (continued)**

|                                                    | TPS54360    |      |  |

|----------------------------------------------------|-------------|------|--|

| THERMAL METRIC <sup>(1)(2)</sup>                   | DDA (HSOIC) | UNIT |  |

|                                                    | 8 PINS      |      |  |

| $\theta_{JB}$ Junction-to-board thermal resistance | 23.4        | °C/W |  |

## 6.5 Electrical Characteristics

$T_J = -40$ °C to 150°C,  $V_{IN} = 4.5$  to 60V (unless otherwise noted)

| PARAMETER                                                  | TEST CONDITIONS                                                 | MIN   | TYP    | MAX   | UNIT  |

|------------------------------------------------------------|-----------------------------------------------------------------|-------|--------|-------|-------|

| SUPPLY VOLTAGE (VIN TERMINALS)                             |                                                                 |       |        |       |       |

| Operating input voltage                                    |                                                                 | 4.5   |        | 60    | V     |

| Internal undervoltage lockout threshold                    | Rising                                                          | 4.1   | 4.3    | 4.48  | V     |

| Internal undervoltage lockout threshold hysteresis         |                                                                 |       | 325    |       | mV    |

| Shutdown supply current                                    | EN = 0 V, 25°C, 4.5 V ≤ VIN ≤ 60 V                              |       | 2.25   | 4.5   |       |

| Operating: nonswitching supply current                     | FB = 0.9 V, T <sub>A</sub> = 25°C                               |       | 146    | 175   | μΑ    |

| ENABLE AND UVLO (EN TERMINALS)                             |                                                                 |       |        |       |       |

| Enable threshold voltage                                   | No voltage hysteresis, rising and falling                       | 1.1   | 1.2    | 1.3   | V     |

|                                                            | Enable threshold +50 mV                                         |       | -4.6   |       |       |

| Input current                                              | Enable threshold –50 mV                                         | -0.58 | -1.2   | -1.8  | μΑ    |

| Hysteresis current                                         |                                                                 | -2.2  | -3.4   | -4.5  | μΑ    |

| VOLTAGE REFERENCE                                          |                                                                 |       |        |       |       |

| Voltage reference                                          |                                                                 | 0.792 | 0.8    | 0.808 | V     |

| HIGH-SIDE MOSFET                                           |                                                                 |       |        |       |       |

| On-resistance                                              | V <sub>IN</sub> = 12 V, BOOT-SW = 6 V                           |       | 92     | 190   | mΩ    |

| ERROR AMPLIFIER                                            |                                                                 |       |        |       |       |

| Input current                                              |                                                                 |       | 50     |       | nA    |

| Error amplifier transconductance (g <sub>M</sub> )         | -2 μA < I <sub>COMP</sub> < 2 μA, V <sub>COMP</sub> = 1 V       |       | 350    |       | μMhos |

| Error amplifier transconductance $(g_M)$ during soft-start | $-2 \mu A < I_{COMP} < 2 \mu A, V_{COMP} = 1 V, V_{FB} = 0.4 V$ |       | 77     |       | μMhos |

| Error amplifier dc gain                                    | V <sub>FB</sub> = 0.8 V                                         |       | 10,000 |       | V/V   |

| Min unity gain bandwidth                                   |                                                                 |       | 2500   |       | kHz   |

| Error amplifier source/sink                                | V <sub>(COMP)</sub> = 1 V, 100 mV overdrive                     |       | ±30    |       | μА    |

| COMP to SW current transconductance                        |                                                                 |       | 12     |       | A/V   |

| CURRENT LIMIT                                              |                                                                 |       |        |       |       |

|                                                            | All VIN and temperatures, Open Loop (1)                         | 4.5   | 5.5    | 6.8   | i     |

| Current limit threshold                                    | All temperatures, VIN = 12 V, Open Loop <sup>(1)</sup>          | 4.5   | 5.5    | 6.25  | Α     |

|                                                            | VIN = 12 V, T <sub>A</sub> = 25°C, Open Loop <sup>(1)</sup>     | 5.2   | 5.5    | 5.85  | Ī     |

| Current limit threshold delay                              |                                                                 |       | 60     |       | ns    |

| THERMAL SHUTDOWN                                           |                                                                 |       |        |       |       |

| Thermal shutdown                                           |                                                                 |       | 176    |       | °C    |

| Thermal shutdown hysteresis                                |                                                                 |       | 12     |       | °C    |

| TIMING RESISTOR AND EXTERNAL CLOCK (RT/CLK                 | FERMINALS)                                                      | *     |        |       |       |

| Switching frequency range using RT mode                    |                                                                 | 100   |        | 2500  | kHz   |

| f <sub>SW</sub> Switching frequency                        | $R_T = 200 \text{ k}\Omega$                                     | 450   | 500    | 550   | kHz   |

| Switching frequency range using CLK mode                   |                                                                 | 160   |        | 2300  | kHz   |

| RT/CLK high threshold                                      |                                                                 |       | 1.55   | 2     | V     |

| RT/CLK low threshold                                       |                                                                 | 0.5   | 1.2    |       | V     |

<sup>(1)</sup> Open Loop current limit measured directly at the SW terminal and is independent of the inductor value and slope compensation.

## 6.6 Timing Requirements

| PARAMETER                                   | TEST CONDITIONS                                | MIN TYP | MAX | UNIT |

|---------------------------------------------|------------------------------------------------|---------|-----|------|

| INTERNAL SOFT-START TIME                    | ·                                              |         |     |      |

| Soft-start time                             | f <sub>SW</sub> = 500 kHz, 10% to 90%          | 2.1     |     | ms   |

| Soft-start time                             | f <sub>SW</sub> = 2.5 MHz, 10% to 90%          | 0.42    |     | ms   |

| HIGH-SIDE MOSFET                            |                                                |         |     |      |

| Minimum controllable on time                | V <sub>IN</sub> = 12 V, T <sub>A</sub> = 25°C  | 135     |     | ns   |

| TIMING RESISTOR AND EXTERNAL CLOCK (RT/CL   | K TERMINALS)                                   |         |     |      |

| Minimum CLK input pulse width               |                                                | 15      |     | ns   |

| RT/CLK falling edge to SW rising edge delay | Measured at 500 kHz with RT resistor in series | 55      |     | ns   |

| PLL lock in time                            | Measured at 500 kHz                            | 78      |     | μS   |

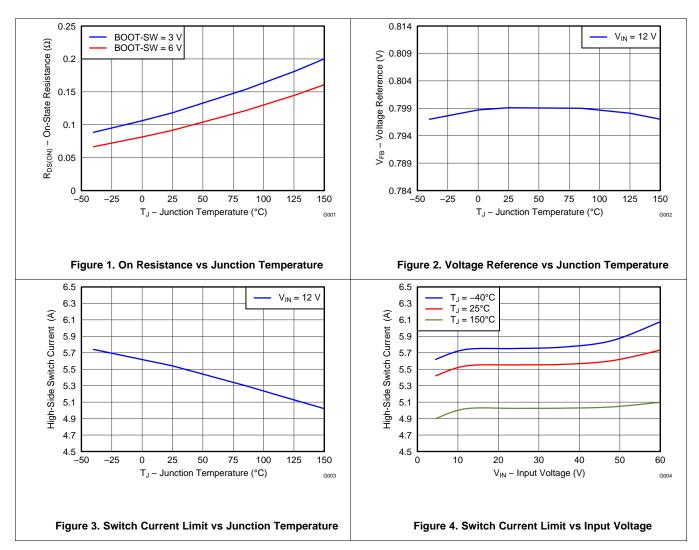

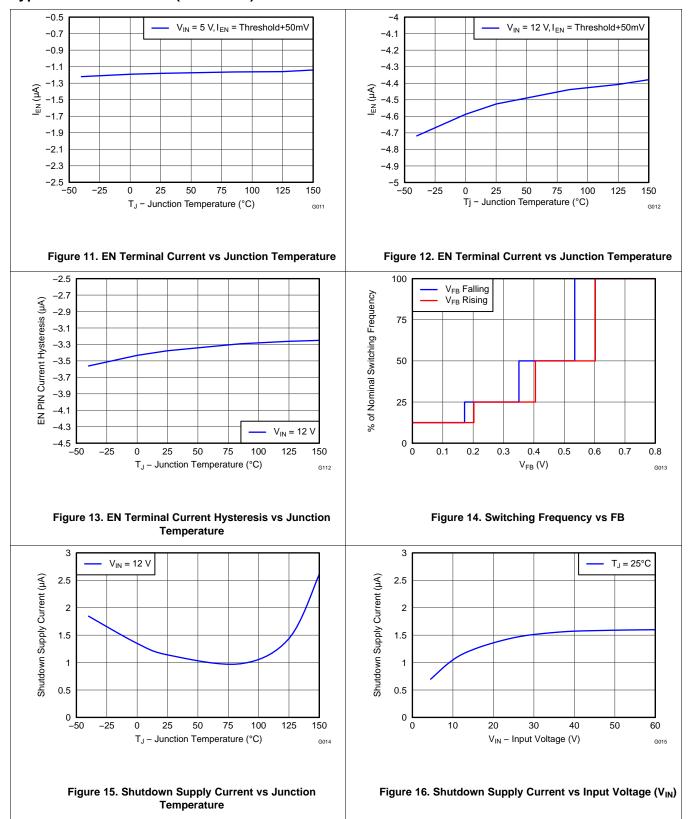

## 6.7 Typical Characteristics

## **Typical Characteristics (continued)**

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

The TPS54360 is a 60-V, 3.5-A, step-down (buck) regulator with an integrated high side n-channel MOSFET. The device implements constant frequency, current mode control which reduces output capacitance and simplifies external frequency compensation. The wide switching frequency range of 100 kHz to 2500 kHz allows either efficiency or size optimization when selecting the output filter components. The switching frequency is adjusted using a resistor to ground connected to the RT/CLK terminal. The device has an internal phase-locked loop (PLL) connected to the RT/CLK terminal that will synchronize the power switch turn on to a falling edge of an external clock signal.

The TPS54360 has a default input start-up voltage of approximately 4.3 V. The EN terminal can be used to adjust the input voltage undervoltage lockout (UVLO) threshold with two external resistors. An internal pull up current source enables operation when the EN terminal is floating. The operating current is 146  $\mu$ A under no load condition (not switching). When the device is disabled, the supply current is 2  $\mu$ A.

The integrated  $92m\Omega$  high side MOSFET supports high efficiency power supply designs capable of delivering 3.5 amperes of continuous current to a load. The gate drive bias voltage for the integrated high side MOSFET is supplied by a bootstrap capacitor connected from the BOOT to SW terminals. The TPS54360 reduces the external component count by integrating the bootstrap recharge diode. The BOOT terminal capacitor voltage is monitored by a UVLO circuit which turns off the high side MOSFET when the BOOT to SW voltage falls below a preset threshold. An automatic BOOT capacitor recharge circuit allows the TPS54360 to operate at high duty cycles approaching 100%. Therefore, the maximum output voltage is near the minimum input supply voltage of the application. The minimum output voltage is the internal 0.8 V feedback reference.

Output overvoltage transients are minimized by an overvoltage transient protection (OVP) comparator. When the OVP comparator is activated, the high side MOSFET is turned off and remains off until the output voltage is less than 106% of the desired output voltage.

The TPS54360 includes an internal soft-start circuit that slows the output rise time during start-up to reduce inrush current and output voltage overshoot. Output overload conditions reset the soft-start timer. When the overload condition is removed, the soft-start circuit controls the recovery from the fault output level to the nominal regulation voltage. A frequency foldback circuit reduces the switching frequency during start-up and overcurrent fault conditions to help maintain control of the inductor current.

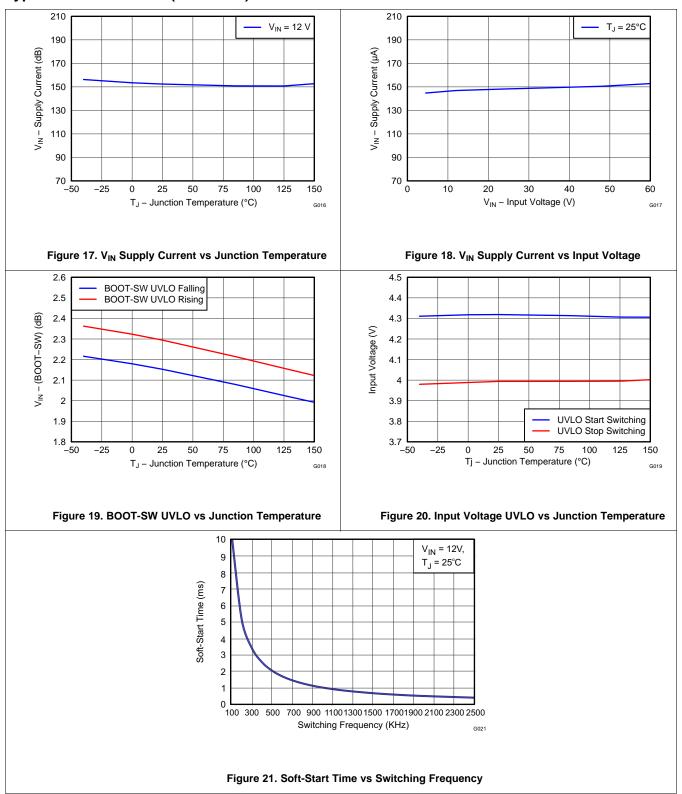

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

## 7.3 Feature Description

## 7.3.1 Fixed Frequency PWM Control

The TPS54360 uses fixed frequency, peak current mode control with adjustable switching frequency. The output voltage is compared through external resistors connected to the FB terminal to an internal voltage reference by an error amplifier. An internal oscillator initiates the turn on of the high side power switch. The error amplifier output at the COMP terminal controls the high side power switch current. When the high side MOSFET switch current reaches the threshold level set by the COMP voltage, the power switch is turned off. The COMP terminal voltage will increase and decrease as the output current increases and decreases. The device implements current limiting by clamping the COMP terminal voltage to a maximum level. The pulse skipping Eco-mode is implemented with a minimum voltage clamp on the COMP terminal.

## 7.3.2 Slope Compensation Output Current

The TPS54360 adds a compensating ramp to the MOSFET switch current sense signal. This slope compensation prevents sub-harmonic oscillations at duty cycles greater than 50%. The peak current limit of the high side switch is not affected by the slope compensation and remains constant over the full duty cycle range.

#### 7.3.3 Pulse Skip Eco-mode

The TPS54360 operates in a pulse skipping Eco-mode at light load currents to improve efficiency by reducing switching and gate drive losses. If the output voltage is within regulation and the peak switch current at the end of any switching cycle is below the pulse skipping current threshold, the device enters Eco-mode. The pulse skipping current threshold is the peak switch current level corresponding to a nominal COMP voltage of 600 mV.

When in Eco-mode, the COMP terminal voltage is clamped at 600 mV and the high side MOSFET is inhibited. Since the device is not switching, the output voltage begins to decay. The voltage control loop responds to the falling output voltage by increasing the COMP terminal voltage. The high side MOSFET is enabled and switching resumes when the error amplifier lifts COMP above the pulse skipping threshold. The output voltage recovers to the regulated value, and COMP eventually falls below the Eco-mode pulse skipping threshold at which time the device again enters Eco-mode. The internal PLL remains operational when in Eco-mode. When operating at light load currents in Eco-mode, the switching transitions occur synchronously with the external clock signal.

During Eco-mode operation, the TPS54360 senses and controls peak switch current, not the average load current. Therefore the load current at which the device enters Eco-mode is dependent on the output inductor value. The circuit in Figure 34 enters Eco-mode at about 24 mA output current. As the load current approaches zero, the device enters a pulse skip mode during which it draws only  $146 \,\mu\text{A}$  input quiescent current.

## 7.3.4 Low Dropout Operation and Bootstrap Voltage (BOOT)

The TPS54360 provides an integrated bootstrap voltage regulator. A small capacitor between the BOOT and SW terminals provides the gate drive voltage for the high side MOSFET. The BOOT capacitor is refreshed when the high side MOSFET is off and the external low side diode conducts. The recommended value of the BOOT capacitor is 0.1  $\mu$ F. A ceramic capacitor with an X7R or X5R grade dielectric with a voltage rating of 10 V or higher is recommended for stable performance over temperature and voltage.

When operating with a low voltage difference from input to output, the high side MOSFET of the TPS54360 will operate at 100% duty cycle as long as the BOOT to SW terminal voltage is greater than 2.1 V. When the voltage from BOOT to SW drops below 2.1 V, the high side MOSFET is turned off and an integrated low side MOSFET pulls SW low to recharge the BOOT capacitor. To reduce the losses of the small low side MOSFET at high output voltages, it is disabled at 24 V output and re-enabled when the output reaches 21.5 V.

Because the gate drive current sourced from the BOOT capacitor is small, the high side MOSFET can remain on for many switching cycles before the MOSFET is turned off to refresh the capacitor. Thus the effective duty cycle of the switching regulator can be high, approaching 100%. The effective duty cycle of the converter during dropout is mainly influenced by the voltage drops across the power MOSFET, the inductor resistance, the low side diode voltage and the printed circuit board resistance.

Equation 1 calculates the minimum input voltage required to regulate the output voltage and ensure normal operation of the device. This calculation must include tolerance of the component specifications and the variation of these specifications at their maximum operating temperature in the application.

$$V_{IN}(min) = \frac{V_{OUT} + V_F + R_{dc} \times I_{OUT}}{0.99} + R_{DS(on)} \times I_{OUT} - V_F$$

#### where

- V<sub>F</sub> = Schottky diode forward voltage

- R<sub>dc</sub> = DC resistance of inductor and PCB

•

$$R_{DS(on)} = High-side MOSFET R_{DS(on)}$$

(1)

At heavy loads, the minimum input voltage must be increased to ensure a monotonic start- up. Use Equation 2 to calculate the minimum input voltage for this condition.

$$V_{OUT(max)} = D_{(max)} \times (V_{IN(min)} - I_{OUT(max)} \times R_{DS(on)} + V_F) - V_F + I_{OUT(max)} \times R_{dc}$$

where

- $D_{(max)} \ge 0.9$

- IB2SW = 100 μA

- $t_{SW} = 1 / f_{SW}(MHz)$

- VB2SW = VBOOT + V<sub>F</sub>

- VBOOT =  $(1.41 \times V_{IN} 0.554 V_F / t_{SW} 1.847 \times 10^3 \times IB2SW) / (1.41 + 1 / t_{SW})^*$

- $R_{DS(on)} = 1 / (-0.3 \times VB2SW^2 + 3.577 \times VB2SW 4.246)$

\*VBOOT is clamped by the IC. If VBOOT calculates to greater than 6 V, set VBOOT = 6 V (2)

#### 7.3.5 Error Amplifier

The TPS54360 voltage regulation loop is controlled by a transconductance error amplifier. The error amplifier compares the FB terminal voltage to the lower of the internal soft-start voltage or the internal 0.8 V voltage reference. The transconductance (gm) of the error amplifier is 350  $\mu$ A/V during normal operation. During soft-start operation, the transconductance is reduced to 78  $\mu$ A/V and the error amplifier is referenced to the internal soft-start voltage.

The frequency compensation components (capacitor, series resistor and capacitor) are connected between the error amplifier output COMP terminal and GND terminal.

## 7.3.6 Adjusting the Output Voltage

The internal voltage reference produces a precise  $0.8 \text{ V} \pm 1\%$  voltage reference over the operating temperature and voltage range by scaling the output of a bandgap reference circuit. The output voltage is set by a resistor divider from the output node to the FB terminal. It is recommended to use 1% tolerance or better divider resistors. Select the low side resistor  $R_{LS}$  for the desired divider current and use Equation 3 to calculate  $R_{HS}$ . To improve efficiency at light loads consider using larger value resistors. However, if the values are too high, the regulator will be more susceptible to noise and voltage errors from the FB input current may become noticeable.

$$R_{HS} = R_{LS} \times \left( \frac{Vout - 0.8V}{0.8 V} \right)$$

(3)

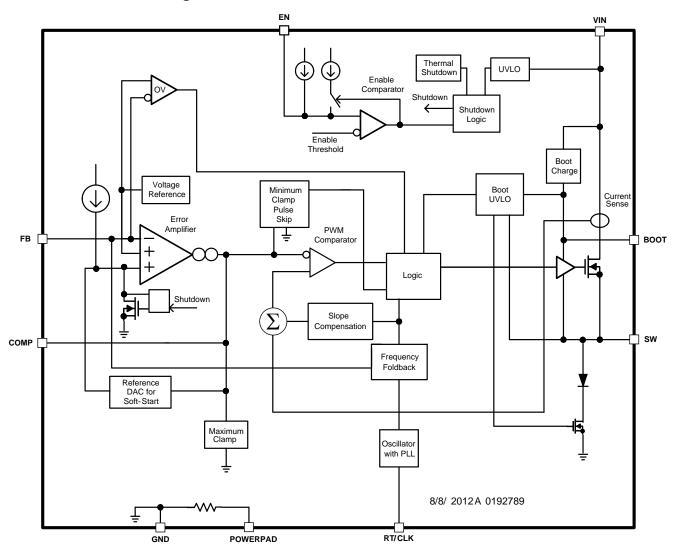

## 7.3.7 Enable and Adjusting Undervoltage Lockout

The TPS54360 is enabled when the VIN terminal voltage rises above 4.3 V and the EN terminal voltage exceeds the enable threshold of 1.2 V. The TPS54360 is disabled when the VIN terminal voltage falls below 4 V or when the EN terminal voltage is below 1.2 V. The EN terminal has an internal pull-up current source, I1, of 1.2  $\mu$ A that enables operation of the TPS54360 when the EN terminal floats.

If an application requires a higher undervoltage lockout (UVLO) threshold, use the circuit shown in Figure 22 to adjust the input voltage UVLO with two external resistors. When the EN terminal voltage exceeds 1.2 V, an additional 3.4  $\mu$ A of hysteresis current, lhys, is sourced out of the EN terminal. When the EN terminal is pulled below 1.2 V, the 3.4  $\mu$ A lhys current is removed. This additional current facilitates adjustable input voltage UVLO hysteresis. Use Equation 4 to calculate R<sub>UVLO1</sub> for the desired UVLO hysteresis voltage. Use Equation 5 to calculate R<sub>UVLO2</sub> for the desired VIN start voltage.

In applications designed to start at relatively low input voltages (e.g., from 4.5 V to 9 V) and withstand high input voltages (e.g., from 40 V to 60 V), the EN terminal may experience a voltage greater than the absolute maximum voltage of 8.4 V during the high input voltage condition. It is recommended to use a zener diode to clamp the terminal voltage below the absolute maximum rating.

Figure 22. Adjustable Undervoltage Lockout (UVLO)

$$R_{UVLO1} = \frac{V_{START} - V_{STOP}}{I_{HYS}}$$

$$R_{UVLO2} = \frac{V_{ENA}}{\frac{V_{START} - V_{ENA}}{R_{UVLO1}} + I_1}$$

(4)

#### 7.3.8 Internal Soft-Start

The TPS54360 has an internal digital soft-start that ramps the reference voltage from zero volts to its final value in 1024 switching cycles. The internal soft-start time (10% to 90%) is calculated using Equation 6.

$$t_{SS}(ms) = \frac{1024}{f_{SW}(kHz)}$$

(6)

If the EN terminal is pulled below the stop threshold of 1.2 V, switching stops and the internal soft-start resets. The soft-start also resets in thermal shutdown.

## 7.3.9 Constant Switching Frequency and Timing Resistor (RT/CLK) Terminal)

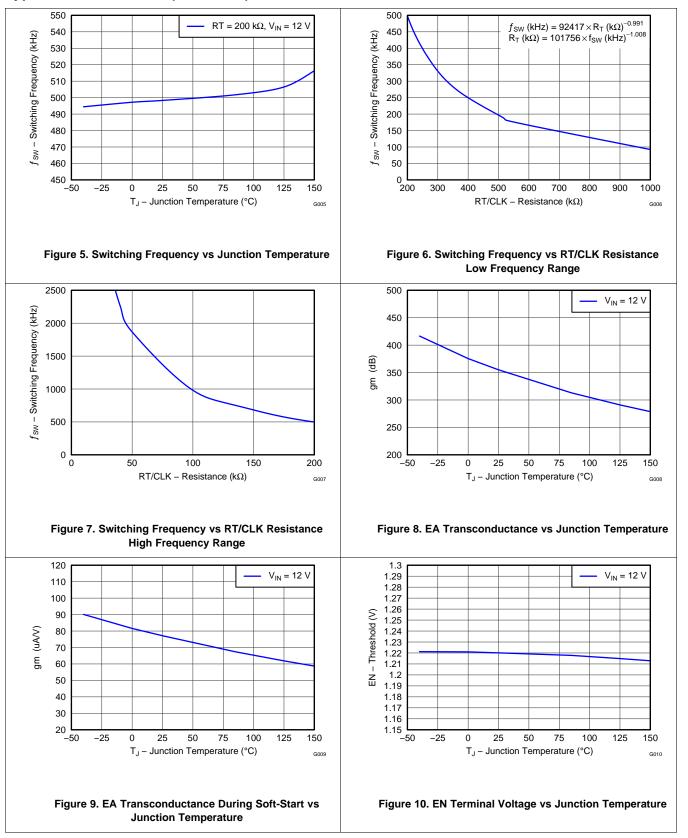

The switching frequency of the TPS54360 is adjustable over a wide range from 100 kHz to 2500 kHz by placing a resistor between the RT/CLK terminal and GND terminal. The RT/CLK terminal voltage is typically 0.5 V and must have a resistor to ground to set the switching frequency. To determine the timing resistance for a given switching frequency, use Equation 7 or Equation 8 or the curves in Figure 5 and Figure 6. To reduce the solution size one would typically set the switching frequency as high as possible, but tradeoffs of the conversion efficiency, maximum input voltage and minimum controllable on time should be considered. The minimum controllable on time is typically 135 ns which limits the maximum operating frequency in applications with high input to output step down ratios. The maximum switching frequency is also limited by the frequency foldback circuit. A more detailed discussion of the maximum switching frequency is provided in the next section.

$$R_{T} (k\Omega) = \frac{101756}{f \text{sw } (k\text{Hz})^{1.008}}$$

$$f \text{sw } (k\text{Hz}) = \frac{92417}{RT (k\Omega)^{0.991}}$$

(8)

## 7.3.10 Accurate Current Limit Operation and Maximum Switching Frequency

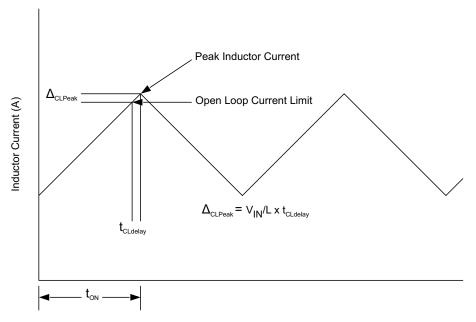

The TPS54360 implements peak current mode control in which the COMP terminal voltage controls the peak current of the high side MOSFET. A signal proportional to the high side switch current and the COMP terminal voltage are compared each cycle. When the peak switch current intersects the COMP control voltage, the high side switch is turned off. During overcurrent conditions that pull the output voltage low, the error amplifier increases switch current by driving the COMP terminal high. The error amplifier output is clamped internally at a level which sets the peak switch current limit. The TPS54360 provides an accurate current limit threshold with a typical current limit delay of 60 ns. With smaller inductor values, the delay will result in a higher peak inductor current. The relationship between the inductor value and the peak inductor current is shown in Figure 23.

Figure 23. Current Limit Delay

To protect the converter in overload conditions at higher switching frequencies and input voltages, the TPS54360 implements a frequency foldback. The oscillator frequency is divided by 1, 2, 4, and 8 as the FB terminal voltage falls from 0.8 V to 0 V. The TPS54360 uses a digital frequency foldback to enable synchronization to an external clock during normal start-up and fault conditions. During short-circuit events, the inductor current can exceed the peak current limit because of the high input voltage and the minimum controllable on time. When the output voltage is forced low by the shorted load, the inductor current decreases slowly during the switch off time. The frequency foldback effectively increases the off time by increasing the period of the switching cycle providing more time for the inductor current to ramp down.

With a maximum frequency foldback ratio of 8, there is a maximum frequency at which the inductor current can be controlled by frequency foldback protection. Equation 9 calculates the maximum switching frequency at which the inductor current will remain under control when  $V_{OUT}$  is forced to  $V_{OUT(SC)}$ . The selected operating frequency should not exceed the calculated value.

Equation 10 calculates the maximum switching frequency limitation set by the minimum controllable on time and the input to output step down ratio. Setting the switching frequency above this value will cause the regulator to skip switching pulses to achieve the low duty cycle required at maximum input voltage.

$$f_{SW(maxskip)} = \frac{1}{t_{ON}} \times \left( \frac{I_O \times R_{dc} + V_{OUT} + V_d}{V_{IN} - I_O \times R_{DS(on)} + V_d} \right)$$

$$f_{SW(shift)} = \frac{f_{DIV}}{t_{ON}} \times \left( \frac{I_{CL} \times R_{dc} + V_{OUT(sc)} + V_d}{V_{IN} - I_{CL} \times R_{DS(on)} + V_d} \right)$$

(10)

Where:

I<sub>O</sub> Output currentI<sub>CL</sub> Current limit

**Rdc** inductor resistance

V<sub>IN</sub> maximum input voltage

**V**<sub>OUT</sub> output voltage

**V**<sub>OUTSC</sub> output voltage during short

$\begin{array}{ll} \textbf{Vd} & \text{diode voltage drop} \\ \textbf{R}_{\textbf{DS(on)}} & \text{switch on resistance} \\ \textbf{t}_{\textbf{ON}} & \text{controllable on time} \end{array}$

$f_{DIV}$  frequency divide equals (1, 2, 4, or 8)

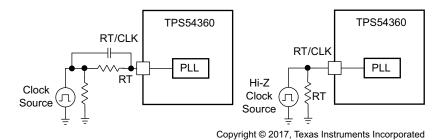

## 7.3.11 Synchronization to RT/CLK Terminal

The RT/CLK terminal can receive a frequency synchronization signal from an external system clock. To implement this synchronization feature connect a square wave to the RT/CLK terminal through either circuit network shown in Figure 24. The square wave applied to the RT/CLK terminal must switch lower than 0.5 V and higher than 1.7 V and have a pulsewidth greater than 15 ns. The synchronization frequency range is 160 kHz to 2300 kHz. The rising edge of the SW will be synchronized to the falling edge of RT/CLK terminal signal. The external synchronization circuit should be designed such that the default frequency set resistor is connected from the RT/CLK terminal to ground when the synchronization signal is off. When using a low impedance signal source, the frequency set resistor is connected in parallel with an ac coupling capacitor to a termination resistor (e.g., 50  $\Omega$ ) as shown in Figure 24. The two resistors in series provide the default frequency setting resistance when the signal source is turned off. The sum of the resistance should set the switching frequency close to the external CLK frequency. It is recommended to ac couple the synchronization signal through a 10 pF ceramic capacitor to RT/CLK terminal.

The first time the RT/CLK is pulled above the PLL threshold the TPS54360 switches from the RT resistor freerunning frequency mode to the PLL synchronized mode. The internal 0.5 V voltage source is removed and the RT/CLK terminal becomes high impedance as the PLL starts to lock onto the external signal. The switching frequency can be higher or lower than the frequency set with the RT/CLK resistor. The device transitions from the resistor mode to the PLL mode and locks onto the external clock frequency within 78 microseconds. During the transition from the PLL mode to the resistor programmed mode, the switching frequency will fall to 150 kHz and then increase or decrease to the resistor programmed frequency when the 0.5 V bias voltage is reapplied to the RT/CLK resistor.

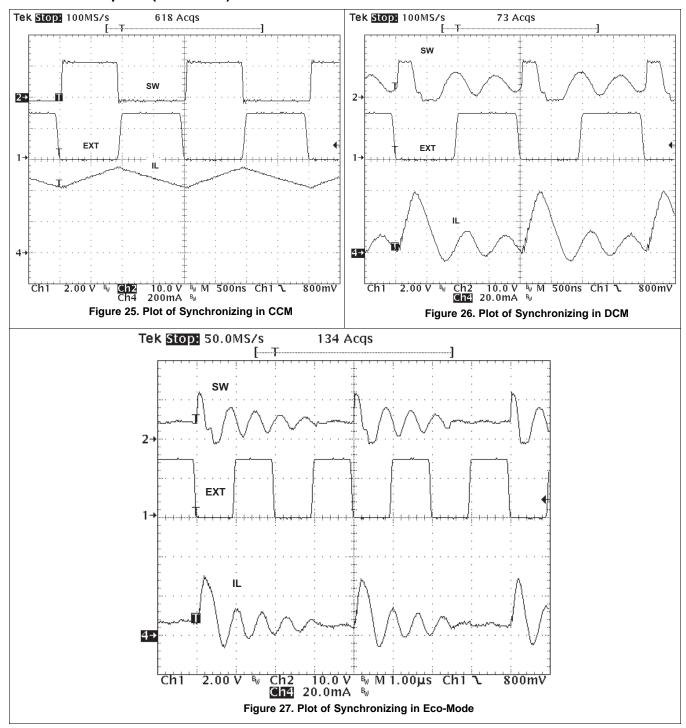

The switching frequency is divided by 8, 4, 2, and 1 as the FB terminal voltage ramps from 0 to 0.8 volts. The device implements a digital frequency foldback to enable synchronizing to an external clock during normal start-up and fault conditions. Figure 25, Figure 26 and Figure 27 show the device synchronized to an external system clock in continuous conduction mode (CCM), discontinuous conduction (DCM), and pulse skip mode (Eco-Mode).

Figure 24. Synchronizing to a System Clock

#### 7.3.12 Overvoltage Protection

The TPS54360 incorporates an output overvoltage protection (OVP) circuit to minimize voltage overshoot when recovering from output fault conditions or strong unload transients in designs with low output capacitance. For example, when the power supply output is overloaded the error amplifier compares the actual output voltage to the internal reference voltage. If the FB terminal voltage is lower than the internal reference voltage for a considerable time, the output of the error amplifier will increase to a maximum voltage corresponding to the peak current limit threshold. When the overload condition is removed, the regulator output rises and the error amplifier output transitions to the normal operating level. In some applications, the power supply output voltage can increase faster than the response of the error amplifier output resulting in an output overshoot.

The OVP feature minimizes output overshoot when using a low value output capacitor by comparing the FB terminal voltage to the rising OVP threshold which is nominally 109% of the internal voltage reference. If the FB terminal voltage is greater than the rising OVP threshold, the high side MOSFET is immediately disabled to minimize output overshoot. When the FB voltage drops below the falling OVP threshold which is nominally 106% of the internal voltage reference, the high side MOSFET resumes normal operation.

#### 7.3.13 Thermal Shutdown

The TPS54360 provides an internal thermal shutdown to protect the device when the junction temperature exceeds 176°C. The high side MOSFET stops switching when the junction temperature exceeds the thermal trip threshold. Once the die temperature falls below 164°C, the device reinitiates the power up sequence controlled by the internal soft-start circuitry.

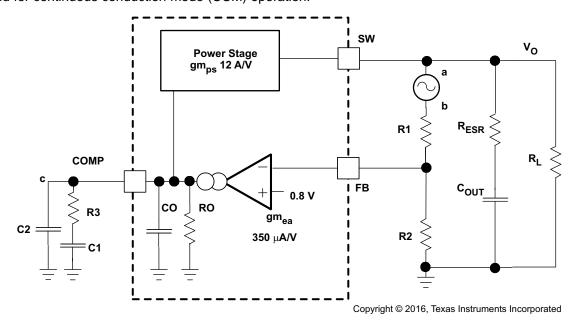

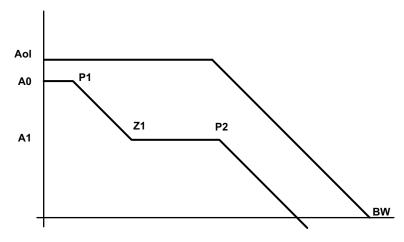

## 7.3.14 Small Signal Model for Loop Response

Figure 28 shows an equivalent model for the TPS54360 control loop which can be simulated to check the frequency response and dynamic load response. The error amplifier is a transconductance amplifier with a gm<sub>EA</sub> of 350  $\mu$ A/V. The error amplifier can be modeled using an ideal voltage controlled current source. The resistor R<sub>o</sub> and capacitor C<sub>o</sub> model the open loop gain and frequency response of the amplifier. The 1mV ac voltage source between the nodes a and b effectively breaks the control loop for the frequency response measurements. Plotting c/a provides the small signal response of the frequency compensation. Plotting a/b provides the small signal response of the overall loop. The dynamic loop response can be evaluated by replacing R<sub>L</sub> with a current source with the appropriate load step amplitude and step rate in a time domain analysis. This equivalent model is only valid for continuous conduction mode (CCM) operation.

Figure 28. Small Signal Model for Loop Response

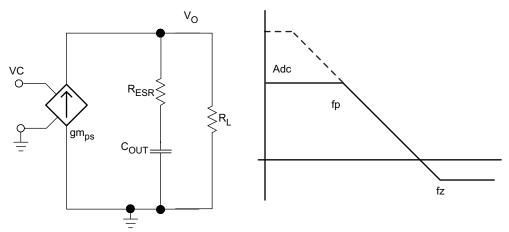

#### 7.3.15 Simple Small Signal Model for Peak Current Mode Control

Figure 29 describes a simple small signal model that can be used to design the frequency compensation. The TPS54360 power stage can be approximated by a voltage-controlled current source (duty cycle modulator) supplying current to the output capacitor and load resistor. The control to output transfer function is shown in Equation 11 and consists of a dc gain, one dominant pole, and one ESR zero. The quotient of the change in switch current and the change in COMP terminal voltage (node c in Figure 28) is the power stage transconductance, gm<sub>PS</sub>. The gm<sub>PS</sub> for the TPS54360 is 12 A/V. The low-frequency gain of the power stage is the product of the transconductance and the load resistance as shown in Equation 12.

As the load current increases and decreases, the low-frequency gain decreases and increases, respectively. This variation with the load may seem problematic at first glance, but fortunately the dominant pole moves with the load current (see Equation 13). The combined effect is highlighted by the dashed line in the right half of Figure 29. As the load current decreases, the gain increases and the pole frequency lowers, keeping the 0-dB crossover frequency the same with varying load conditions. The type of output capacitor chosen determines whether the ESR zero has a profound effect on the frequency compensation design. Using high ESR aluminum electrolytic capacitors may reduce the number frequency compensation components needed to stabilize the overall loop because the phase margin is increased by the ESR zero of the output capacitor (see Equation 14).

Copyright © 2017, Texas Instruments Incorporated

Figure 29. Simple Small Signal Model and Frequency Response for Peak Current Mode Control

$$\frac{V_{OUT}}{V_{C}} = Adc \times \frac{\left(1 + \frac{s}{2\pi \times f_{Z}}\right)}{\left(1 + \frac{s}{2\pi \times f_{P}}\right)}$$

(11)

$$Adc = gm_{ps} \times R_L$$

(12)

$$f_{P} = \frac{1}{C_{OUT} \times R_{L} \times 2\pi} \tag{13}$$

$$f_{Z} = \frac{1}{C_{OUT} \times R_{ESR} \times 2\pi}$$

(14)

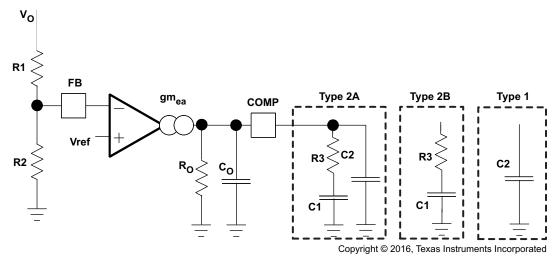

#### 7.3.16 Small Signal Model for Frequency Compensation

The TPS54360 uses a transconductance amplifier for the error amplifier and supports three of the commonly-used frequency compensation circuits. Compensation circuits Type 2A, Type 2B, and Type 1 are shown in Figure 30. Type 2 circuits are typically implemented in high bandwidth power-supply designs using low ESR output capacitors. The Type 1 circuit is used with power-supply designs with high-ESR aluminum electrolytic or tantalum capacitors. Equation 15 and Equation 16 relate the frequency response of the amplifier to the small signal model in Figure 30. The open-loop gain and bandwidth are modeled using the  $R_{\rm O}$  and  $R_{\rm O}$  shown in Figure 30. See the application section for a design example using a Type 2A network with a low ESR output capacitor.

Equation 15 through Equation 24 are provided as a reference. An alternative is to use WEBENCH software tools to create a design based on the power supply requirements.

Figure 30. Types of Frequency Compensation

Figure 31. Frequency Response of the Type 2A and Type 2B Frequency Compensation

$$Ro = \frac{Aol(V/V)}{gm_{ea}}$$

$$C_{O} = \frac{gm_{ea}}{2\pi \times BW (Hz)}$$

(15)

$$EA = A0 \times \frac{\left(1 + \frac{s}{2\pi \times f_{Z1}}\right)}{\left(1 + \frac{s}{2\pi \times f_{P1}}\right) \times \left(1 + \frac{s}{2\pi \times f_{P2}}\right)}$$

(17)

$$A0 = gm_{ea} \times Ro \times \frac{R2}{R1 + R2}$$

(18)

$$A1 = gm_{ea} \times Ro \mid R3 \times \frac{R2}{R1 + R2}$$

(19)

$$P1 = \frac{1}{2\pi \times Ro \times C1} \tag{20}$$

$$Z1 = \frac{1}{2\pi \times R3 \times C1} \tag{21}$$

P2 =

$$\frac{1}{2\pi \times R3 \mid \mid R_{O} \times (C2 + C_{O})}$$

type 2a (22)

$$P2 = \frac{1}{2\pi \times R3 \mid \mid R_O \times C_O} \text{ type 2b}$$

(23)

P2 =

$$\frac{1}{2\pi \times R_{O} \times (C2 + C_{O})}$$

type 1 (24)

## 7.4 Device Functional Modes

## 7.4.1 Operation with $V_{IN} = < 4.5 \text{ V (Minimum } V_{IN})$

The device is recommended to operate with input voltages above 4.5 V. The typical  $V_{IN}$  UVLO threshold is 4.3 V and the device may operate at input voltages down to the UVLO voltage. At input voltages below the actual UVLO voltage, the device will not switch. If EN is externally pulled up to  $V_{IN}$  or left floating, when  $V_{IN}$  passes the UVLO threshold the device will become active. Switching is enabled, and the soft start sequence is initiated. The TPS54360 will start at the soft start time determined by the internal soft start time.

## 7.4.2 Operation with EN Control

The enable threshold voltage is 1.2 V typical. With EN held below that voltage the device is disabled and switching is inhibited even if VIN is above its UVLO threshold. The IC quiescent current is reduced in this state. If the EN voltage is increased above the threshold while VIN is above its UVLO threshold, the device becomes active. Switching is enabled, and the soft start sequence is initiated. The TPS54360 starts at the soft-start time determined by the internal soft start time.

## **Device Functional Modes (continued)**

#### 7.4.3 Alternate Power Supply Topologies

## 7.4.3.1 Inverting Power

The TPS54360 can be used to convert a positive input voltage to a negative output voltage. Idea applications are amplifiers requiring a negative power supply. For a more detailed example see SLVA317.

Figure 32. TPS54360 Inverting Power Supply

## 7.4.3.2 Split-Rail Power Supply

The TPS54360 can be used to convert a positive input voltage to a split rail positive and negative output voltage by using a coupled inductor. Idea applications are amplifiers requiring a split rail positive and negative voltage power supply. For a more detailed example see SLVA369.

Figure 33. TPS54360 Split Rail Power Supply

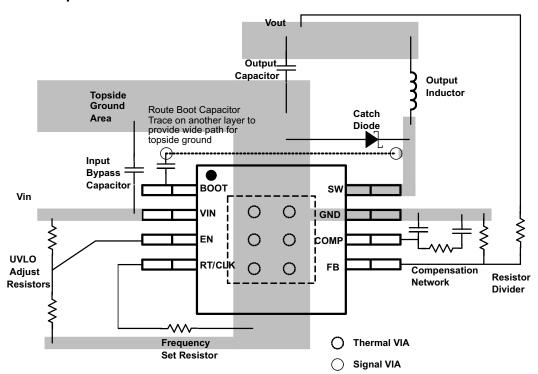

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The TPS54360 is a 60-V, 3.5-A, step-down regulator with an integrated high side MOSFET. Ideal applications are: 12 V, 24 V and 48 V industrial, automotive and communications power systems.

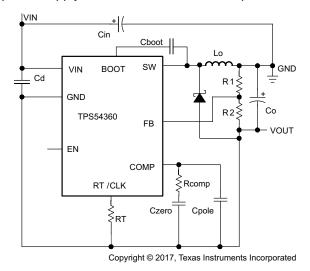

## 8.2 Typical Application

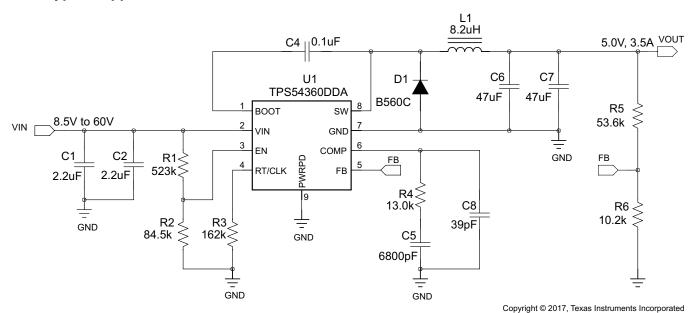

Figure 34. 5 V Output TPS54360 Design Example

## 8.2.1 Design Requirements

This guide illustrates the design of a high frequency switching regulator using ceramic output capacitors. A few parameters must be known in order to start the design process. These requirements are typically determined at the system level. For this example, start with the following known parameters:

**Table 1. Design Parameters**

| PARAMETER                                       | VALUE                    |  |  |  |  |

|-------------------------------------------------|--------------------------|--|--|--|--|

| Output Voltage                                  | 5 V                      |  |  |  |  |

| Transient Response 0.875 A to 2.625 A load step | $\Delta V_{OUT} = 4 \%$  |  |  |  |  |

| Maximum Output Current                          | 3.5 A                    |  |  |  |  |

| Input Voltage                                   | 12 V nom. 8.5 V to 60 V  |  |  |  |  |

| Output Voltage Ripple                           | 0.5% of V <sub>OUT</sub> |  |  |  |  |

| Start Input Voltage (rising VIN)                | 8 V                      |  |  |  |  |

| Stop Input Voltage (falling VIN)                | 6.25 V                   |  |  |  |  |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Custom Design with WEBENCH® Tools

Click here to create a custom design using the TPS54360 device with the WEBENCH® Power Designer.

- 1. Start by entering your  $V_{IN}$ ,  $V_{OUT}$ , and  $I_{OUT}$  requirements.

- 2. Optimize your design for key parameters like efficiency, footprint and cost using the optimizer dial and compare this design with other possible solutions from Texas Instruments.

- 3. The WEBENCH Power Designer provides you with a customized schematic along with a list of materials with real time pricing and component availability.

- 4. In most cases, you will also be able to:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand the thermal performance of your board

- Export your customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share your design with colleagues

- 5. Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 8.2.2.2 Selecting the Switching Frequency

The first step is to choose a switching frequency for the regulator. Typically, the designer uses the highest switching frequency possible since this produces the smallest solution size. High switching frequency allows for lower value inductors and smaller output capacitors compared to a power supply that switches at a lower frequency. The switching frequency that can be selected is limited by the minimum on-time of the internal power switch, the input voltage, the output voltage and the frequency foldback protection.

Equation 9 and Equation 10 should be used to calculate the upper limit of the switching frequency for the regulator. Choose the lower value result from the two equations. Switching frequencies higher than these values results in pulse skipping or the lack of overcurrent protection during a short circuit.

The typical minimum on time,  $t_{onmin}$ , is 135 ns for the TPS54360. For this example, the output voltage is 5 V and the maximum input voltage is 60 V, which allows for a maximum switch frequency up to 710 kHz to avoid pulse skipping from Equation 9. To ensure overcurrent runaway is not a concern during short circuits use Equation 10 to determine the maximum switching frequency for frequency foldback protection. With a maximum input voltage of 60 V, assuming a diode voltage of 0.7 V, inductor resistance of 25 m $\Omega$ , switch resistance of 92 m $\Omega$ , a current limit value of 4.7 A and short circuit output voltage of 0.1 V, the maximum switching frequency is 902 kHz.

For this design, a lower switching frequency of 600 kHz is chosen to operate comfortably below the calculated maximums. To determine the timing resistance for a given switching frequency, use Equation 7 or the curve in Figure 6. The switching frequency is set by resistor  $R_3$  shown in Figure 34. For 600 kHz operation, the closest standard value resistor is 162 k $\Omega$ .

$$f_{\text{SW(maxskip)}} = \frac{1}{135\text{ns}} \times \left( \frac{3.5 \text{ A x } 25 \text{ m}\Omega + 5 \text{ V} + 0.7 \text{ V}}{60 \text{ V} - 3.5 \text{ A x } 92 \text{ m}\Omega + 0.7 \text{ V}} \right) = 710 \text{ kHz}$$

(25)

$$f_{\text{SW(shift)}} = \frac{8}{135 \text{ ns}} \times \left( \frac{4.7 \text{ A x } 25 \text{ m}\Omega + 0.1 \text{ V} + 0.7 \text{ V}}{60 \text{ V} - 4.7 \text{ A x } 92 \text{ m}\Omega + 0.7 \text{ V}} \right) = 902 \text{ kHz}$$

(26)

RT

$$(k\Omega) = \frac{101756}{600 (kHz)^{1.008}} = 161 k\Omega$$

(27)

## 8.2.2.3 Output Inductor Selection (L<sub>O</sub>)

To calculate the minimum value of the output inductor, use Equation 28.

K<sub>IND</sub> is a ratio that represents the amount of inductor ripple current relative to the maximum output current. The inductor ripple current is filtered by the output capacitor. Therefore, choosing high inductor ripple currents impacts the selection of the output capacitor since the output capacitor must have a ripple current rating equal to or greater than the inductor ripple current. In general, the inductor ripple value is at the discretion of the designer, however, the following guidelines may be used.

For designs using low ESR output capacitors such as ceramics, a value as high as  $K_{IND} = 0.3$  may be desirable. When using higher ESR output capacitors,  $K_{IND} = 0.2$  yields better results. Since the inductor ripple current is part of the current mode PWM control system, the inductor ripple current should always be greater than 150 mA for stable PWM operation. In a wide input voltage regulator, it is best to choose relatively large inductor ripple current. This provides sufficienct ripple current with the input voltage at the minimum.

For this design example,  $K_{IND}$  = 0.3 and the minimum inductor value is calculated to be 7.3  $\mu$ H. The nearest standard value is 8.2  $\mu$ H. It is important that the RMS current and saturation current ratings of the inductor not be exceeded. The RMS and peak inductor current can be found from Equation 30 and Equation 31. For this design, the RMS inductor current is 3.5 A and the peak inductor current is 3.97 A. The chosen inductor is a WE 7447797820, which has a saturation current rating of 5.8 A and an RMS current rating of 5.05 A.

As the equation set demonstrates, lower ripple currents will reduce the output voltage ripple of the regulator but will require a larger value of inductance. Selecting higher ripple currents will increase the output voltage ripple of the regulator but allow for a lower inductance value.

The current flowing through the inductor is the inductor ripple current plus the output current. During power up, faults or transient load conditions, the inductor current can increase above the peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative design approach is to choose an inductor with a saturation current rating equal to or greater than the switch current limit of the TPS54360 which is nominally 5.5 A.

$$L_{O(min)} = \frac{V_{IN(max)} - V_{OUT}}{I_{OUT} \times K_{IND}} \times \frac{V_{OUT}}{V_{IN(max)} \times f_{SW}} = \frac{60 \text{ V} - 5 \text{ V}}{3.5 \text{ A} \times 0.3} \times \frac{5 \text{ V}}{60 \text{ V} \times 600 \text{ kHz}} = 7.3 \text{ }\mu\text{H}$$

(28)

$$I_{RIPPLE} = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times L_{O} \times f_{SW}} = \frac{5 \text{ V x } (60 \text{ V - 5 V})}{60 \text{ V x } 8.2 \text{ } \mu\text{H x } 600 \text{ kHz}} = 0.932 \text{ A}$$

(29)

$$I_{L(rms)} = \sqrt{\left(I_{OUT}\right)^{2} + \frac{1}{12} \times \left(\frac{V_{OUT} \times \left(V_{IN(max)} - V_{OUT}\right)}{V_{IN(max)} \times L_{O} \times f_{SW}}\right)^{2}} = \sqrt{\left(3.5 \text{ A}\right)^{2} + \frac{1}{12} \times \left(\frac{5 \text{ V} \times (60 \text{ V} - 5 \text{ V})}{60 \text{ V} \times 8.2 \text{ } \mu\text{H} \times 600 \text{ kHz}}\right)^{2}} = 3.5 \text{ A}}$$

(30)

$$I_{L(peak)} = I_{OUT} + \frac{I_{RIPPLE}}{2} = 3.5 \text{ A} + \frac{0.932 \text{ A}}{2} = 3.97 \text{ A}$$

(31)

### 8.2.2.4 Output Capacitor

There are three primary considerations for selecting the value of the output capacitor. The output capacitor determines the modulator pole, the output voltage ripple, and how the regulator responds to a large change in load current. The output capacitance needs to be selected based on the most stringent of these three criteria.

The desired response to a large change in the load current is the first criteria. The output capacitor needs to supply the increased load current until the regulator responds to the load step. The regulator does not respond immediately to a large, fast increase in the load current such as transitioning from no load to a full load. The regulator usually needs two or more clock cycles for the control loop to sense the change in output voltage and adjust the peak switch current in response to the higher load. The output capacitance must be large enough to

supply the difference in current for 2 clock cycles to maintain the output voltage within the specified range. Equation 32 shows the minimum output capacitance necessary, where  $\Delta I_{OUT}$  is the change in output current, fsw is the regulators switching frequency and  $\Delta V_{OUT}$  is the allowable change in the output voltage. For this example, the transient load response is specified as a 4% change in  $V_{OUT}$  for a load step from 0.875 A to 2.625 A. Therefore,  $\Delta I_{OUT}$  is 2.625 A - 0.875 A = 1.75 A and  $\Delta V_{OUT}$  = 0.04 × 5 = 0.2 V. Using these numbers gives a minimum capacitance of 29.2 µF. This value does not take the ESR of the output capacitor into account in the output voltage change. For ceramic capacitors, the ESR is usually small enough to be ignored. Aluminum electrolytic and tantalum capacitors have higher ESR that must be included in load step calculations.

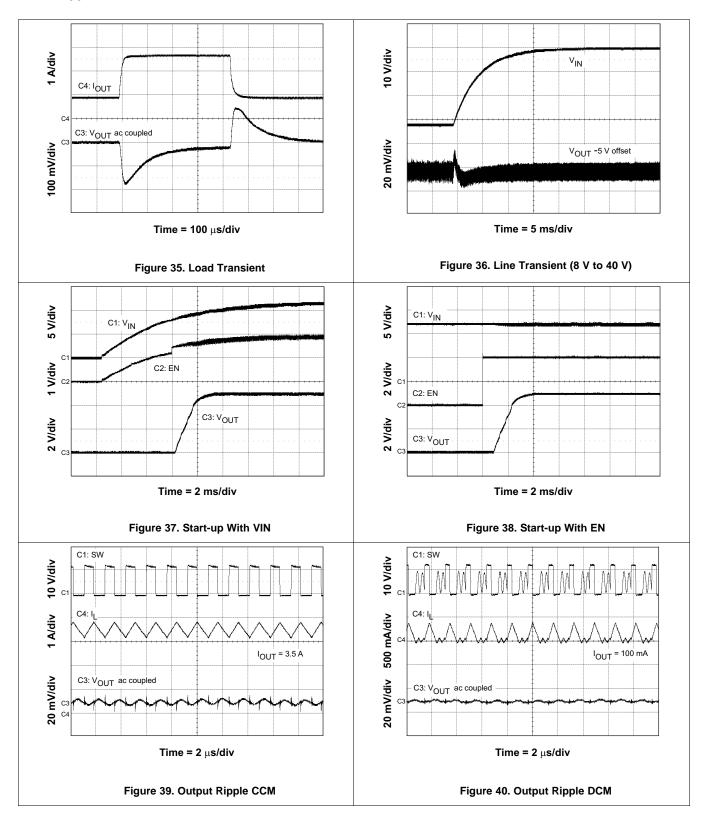

The output capacitor must also be sized to absorb energy stored in the inductor when transitioning from a high to low load current. The catch diode of the regulator can not sink current so energy stored in the inductor can produce an output voltage overshoot when the load current rapidly decreases. A typical load step response is shown in Figure 35. The excess energy absorbed in the output capacitor will increase the voltage on the capacitor. The capacitor must be sized to maintain the desired output voltage during these transient periods. Equation 33 calculates the minimum capacitance required to keep the output voltage overshoot to a desired value, where Lo is the value of the inductor, IoH is the output current under heavy load, IoL is the output under light load, V<sub>f</sub> is the peak output voltage, and Vi is the initial voltage. For this example, the worst case load step will be from 2.625 A to 0.875 A. The output voltage increases during this load transition and the stated maximum in our specification is 4 % of the output voltage. This makes  $V_f = 1.04 \times 5 = 5.2$ . Vi is the initial capacitor voltage which is the nominal output voltage of 5 V. Using these numbers in Equation 33 yields a minimum capacitance of 24.6 μF.

Equation 34 calculates the minimum output capacitance needed to meet the output voltage ripple specification. where fsw is the switching frequency,  $V_{ORIPPLE}$  is the maximum allowable output voltage ripple, and  $I_{RIPPLE}$  is the inductor ripple current. Equation 34 yields 7.8 μF.

Equation 35 calculates the maximum ESR an output capacitor can have to meet the output voltage ripple specification. Equation 35 indicates the ESR should be less than 27 m $\Omega$ .

The most stringent criteria for the output capacitor is 29.2 µF required to maintain the output voltage within regulation tolerance during a load transient.

Capacitance de-ratings for aging, temperature and dc bias increases this minimum value. For this example, 2 x 47 μF, 10 V ceramic capacitors with 5 mΩ of ESR will be used. The derated capacitance is 58.3 μF, well above the minimum required capacitance of 29.2 µF.

Capacitors are generally rated for a maximum ripple current that can be filtered without degrading capacitor reliability. Some capacitor data sheets specify the Root Mean Square (RMS) value of the maximum ripple current. Equation 36 can be used to calculate the RMS ripple current that the output capacitor must support. For this example, Equation 36 yields 269 mA.

$$C_{OUT} > \frac{2 \times \Delta I_{OUT}}{f_{SW} \times \Delta V_{OUT}} = \frac{2 \times 1.75 \text{ A}}{600 \text{ kHz x } 0.2 \text{ V}} = 29.2 \text{ }\mu\text{F}$$

(32)

$$C_{OUT} > L_{O} \times \frac{\left( \left( l_{OH} \right)^{2} - \left( l_{OL} \right)^{2} \right)}{\left( \left( V_{f} \right)^{2} - \left( V_{I} \right)^{2} \right)} = 8.2 \ \mu H \times \frac{\left( 2.625 \ A^{2} - 0.875 \ A^{2} \right)}{\left( 5.2 \ V^{2} - 5 \ V^{2} \right)} = 24.6 \ \mu F$$

(33)

$$C_{OUT} > \frac{1}{8 \times f_{SW}} \times \frac{1}{\left(\frac{V_{ORIPPLE}}{I_{RIPPLE}}\right)} = \frac{1}{8 \times 600 \text{ kHz}} \times \frac{1}{\left(\frac{25 \text{ mV}}{0.932 \text{ A}}\right)} = 7.8 \,\mu\text{F}$$

(34)

$$R_{ESR} < \frac{V_{ORIPPLE}}{I_{RIPPLE}} = \frac{25 \text{ mV}}{0.932 \text{ A}} = 27 \text{ m}\Omega$$

(35)

$$R_{ESR} < \frac{V_{ORIPPLE}}{I_{RIPPLE}} = \frac{25 \text{ mV}}{0.932 \text{ A}} = 27 \text{ m}\Omega$$

$$I_{COUT(rms)} = \frac{V_{OUT} \times \left(V_{IN(max)} - V_{OUT}\right)}{\sqrt{12} \times V_{IN(max)} \times L_{O} \times f_{SW}} = \frac{5 \text{ V} \times (60 \text{ V} - 5 \text{ V})}{\sqrt{12} \times 60 \text{ V} \times 8.2 \text{ } \mu\text{H} \times 600 \text{ kHz}} = 269 \text{ mA}$$

(36)

#### 8.2.2.5 Catch Diode

The TPS54360 requires an external catch diode between the SW terminal and GND. The selected diode must have a reverse voltage rating equal to or greater than  $V_{IN(max)}$ . The peak current rating of the diode must be greater than the maximum inductor current. Schottky diodes are typically a good choice for the catch diode due to their low forward voltage. The lower the forward voltage of the diode, the higher the efficiency of the regulator.

Typically, diodes with higher voltage and current ratings have higher forward voltages. A diode with a minimum of 60 V reverse voltage is preferred to allow input voltage transients up to the rated voltage of the TPS54360.

For the example design, the B560C-13-F Schottky diode is selected for its lower forward voltage and good thermal characteristics compared to smaller devices. The typical forward voltage of the B560C-13-F is 0.70 volts at 5 A.

The diode must also be selected with an appropriate power rating. The diode conducts the output current during the off-time of the internal power switch. The off-time of the internal switch is a function of the maximum input voltage, the output voltage, and the switching frequency. The output current during the off-time is multiplied by the forward voltage of the diode to calculate the instantaneous conduction losses of the diode. At higher switching frequencies, the ac losses of the diode need to be taken into account. The ac losses of the diode are due to the charging and discharging of the junction capacitance and reverse recovery charge. Equation 37 is used to calculate the total power dissipation, including conduction losses and ac losses of the diode.

The B560C-13-F diode has a junction capacitance of 300 pF. Using Equation 37, the total loss in the diode is 2.58 Watts.

If the power supply spends a significant amount of time at light load currents or in sleep mode, consider using a diode which has a low leakage current and slightly higher forward voltage drop.

$$P_{D} = \frac{\left(V_{IN(max)} - V_{OUT}\right) \times I_{OUT} \times Vfd}{V_{IN(max)}} + \frac{C_{j} \times f_{SW} \times \left(V_{IN} + Vfd\right)^{2}}{2} = \frac{\left(60 \text{ V} - 5 \text{ V}\right) \times 3.5 \text{ A} \times 0.7 \text{ V}}{60 \text{ V}} + \frac{300 \text{ pF} \times 600 \text{ kHz} \times (60 \text{ V} + 0.7 \text{ V})^{2}}{2} = 2.58 \text{ W}$$

(37)

#### 8.2.2.6 Input Capacitor

The TPS54360 requires a high quality ceramic type X5R or X7R input decoupling capacitor with at least 3  $\mu$ F of effective capacitance. Some applications will benefit from additional bulk capacitance. The effective capacitance includes any loss of capacitance due to dc bias effects. The voltage rating of the input capacitor must be greater than the maximum input voltage. The capacitor must also have a ripple current rating greater than the maximum input current ripple of the TPS54360. The input ripple current can be calculated using Equation 38.

The value of a ceramic capacitor varies significantly with temperature and the dc bias applied to the capacitor. The capacitance variations due to temperature can be minimized by selecting a dielectric material that is more stable over temperature. X5R and X7R ceramic dielectrics are usually selected for switching regulator capacitors because they have a high capacitance to volume ratio and are fairly stable over temperature. The input capacitor must also be selected with consideration for the dc bias. The effective value of a capacitor decreases as the dc bias across a capacitor increases.

For this example design, a ceramic capacitor with at least a 60 V voltage rating is required to support the maximum input voltage. Common standard ceramic capacitor voltage ratings include 4 V, 6.3 V, 10 V, 16 V, 25 V, 50 V or 100 V. For this example, two 2.2  $\mu$ F, 100 V capacitors in parallel are used. Table 2 shows several choices of high voltage capacitors.

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using Equation 39. Using the design example values,  $I_{OUT} = 3.5$  A,  $C_{IN} = 4.4$   $\mu$ F, fsw = 600 kHz, yields an input voltage ripple of 331 mV and a rms input ripple current of 1.72 A.

$$I_{CI(rms)} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN(min)}}} \times \frac{\left(V_{IN(min)} - V_{OUT}\right)}{V_{IN(min)}} = 3.5 \text{ A} \sqrt{\frac{5 \text{ V}}{8.5 \text{ V}}} \times \frac{\left(8.5 \text{ V} - 5 \text{ V}\right)}{8.5 \text{ V}} = 1.72 \text{ A}$$

(38)

$$\Delta V_{IN} = \frac{I_{OUT} \times 0.25}{C_{IN} \times f_{SW}} = \frac{3.5 \text{ A} \times 0.25}{4.4 \text{ } \mu\text{F} \times 600 \text{ kHz}} = 331 \text{ mV}$$

(39)

Table 2. Capacitor Types

| VALUE (μF) | EIA Size | VOLTAGE | DIALECTRIC | COMMENTS              |  |

|------------|----------|---------|------------|-----------------------|--|

| 1 to 2.2   | 1210     | 100 V   |            | GRM32 series          |  |

| 1 to 4.7   | 1210     | 50 V    |            | GRIVISZ SEITES        |  |

| 1          | 4000     | 100 V   |            | GRM31 series          |  |

| 1 to 2.2   | 1206     | 50 V    |            | GRIVIST Series        |  |

| 1 to 1.8   | 2220     | 50 V    |            |                       |  |

| 1 to 1.2   | 2220     | 100 V   |            | VI VZD aariaa         |  |

| 1 to 3.9   | 2005     | 50 V    |            | VJ X7R series         |  |

| 1 to 1.8   | 2225     | 100 V   | V7D        |                       |  |

| 1 to 2.2   | 4040     | 100 V   | X7R        | C C4500               |  |

| 1.5 to 6.8 | 1812     | 50 V    |            | C series C4532        |  |

| 1 to 2.2   | 1210     | 100 V   |            | C series C3225        |  |

| 1 to 3.3   | 1210     | 50 V    |            |                       |  |

| 1 to 4.7   | 4040     | 50 V    |            |                       |  |

| 1          | 1210     | 100 V   |            | VZD distantina anima  |  |

| 1 to 4.7   | 1010     | 50 V    |            | X7R dielectric series |  |

| 1 to 2.2   | 1812     | 100 V   |            |                       |  |

### 8.2.2.7 Bootstrap Capacitor Selection

A 0.1- $\mu F$  ceramic capacitor must be connected between the BOOT and SW terminals for proper operation. A ceramic capacitor with X5R or better grade dielectric is recommended. The capacitor should have a 10 V or higher voltage rating.

#### 8.2.2.8 Undervoltage Lockout Set Point