🕳 Order

Now

#### **TPS546C20A**

JAJSFL9C – JULY 2016 – REVISED JUNE 2018

# TPS546C20A 4.5V~18V、35A 2xスタック可能、 テレメトリをサポートするPMBus搭載の同期降圧コンバータ

### 1 特長

Texas

INSTRUMENTS

- PMBus<sup>™</sup>1.3準拠のコンバータ: 35A

- 2つのデバイスをスタックし、電流共有により最 大70Aを供給可能

- 入力電圧範囲: 4.5V~18V

- 出力電圧範囲: 0.35V~5.5V

- 3.2mΩおよび1.4mΩのスタックされた NexFET™ 電力段を内蔵

- 600mV以上での基準電圧精度0.5%

- 損失なしのローサイドMOSFET電流センシング

- 電圧モード制御、入力フィードフォワード付き

- 差動リモート・センシング

- プリバイアスされた出力への単調起動

- 出力電圧および出力電流の報告

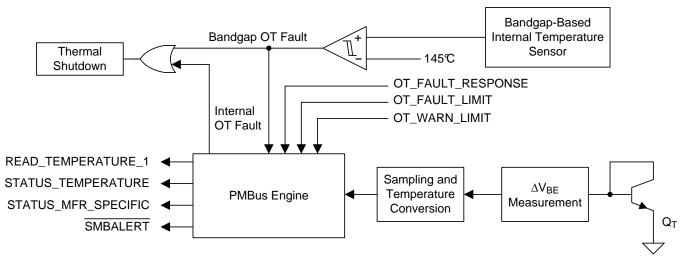

- 内部的なダイ温度の監視

- 2つのPMBusアドレス(マスタ36d/スレーブ37d)

- ピン・ストラッピングによりブートアップ時の Voutとソフトスタート値を選択可能

- PMBusインターフェイスにより次のものをプログ ラム可能

- OCP、UVLO、ソフトスタート、PG、OV、UV、OT レベル、フォルト応答

- 電源オンおよび電源オフの遅延

- ・ サーマル・シャットダウン

- ピン・ストラッピングによるスイッチング周波数: 200kHz~1MHz

- 外部クロックへの周波数同期、またはSYNC-OUT へのクロック出力

- WEBENCH<sup>®</sup> Power Designerにより、 TPS546C20Aを使用するカスタム設計を作成

- 2 アプリケーション

- テストおよび計測機器

- イーサネット・スイッチ、光スイッチ、ルータ、 基地局

- ・ サーバー

- エンタープライズ・ストレージSSD

## 3 概要

TPS546C20Aデバイスは、PMBus 1.3準拠の非絶縁 DC/DCコンバータで、FETが内蔵されており、高い周波数 での動作と、35Aの電流出力を、7mm×5mmのパッケージ で実現しています。2つのTPS546C20Aデバイスを並列 に接続して、最大70Aの負荷に対応できます。電流センシ ングは、電力段電流のごく一部をサンプリングして行わ れ、デバイスの温度に依存しません。内蔵のNexFET電力 段と最適化されたドライバにより、高い周波数と、損失のな いスイッチングが実現され、非常に電力密度の高いソ リューションが可能になります。PMBusインターフェイスに よって、VOUT\_COMMANDによるAVS機能、柔軟なコン バータの設定に加えて、出力電圧、電流、内部ダイの温 度など主要なパラメータの監視が可能です。システムの要 件に応じ、フォルト状況に対して再起動、ラッチオフ、また は無視の応答を設定できます。

製品情報<sup>(1)</sup>

| 型番         | パッケージ     | 本体サイズ         |

|------------|-----------|---------------|

| TPS546C20A | LQFN (40) | 7.00mm×5.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

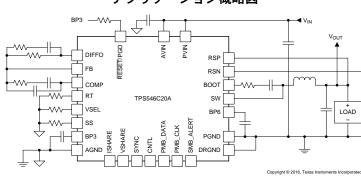

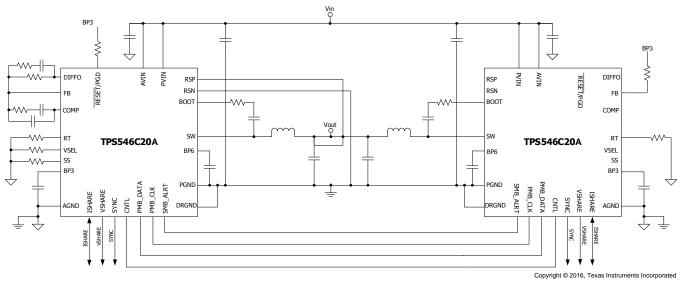

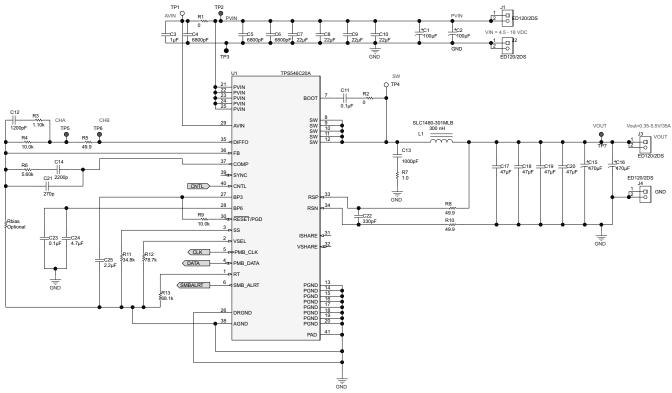

アプリケーション概略図

# 目次

| 1 | 特長   |                                    |

|---|------|------------------------------------|

| 2 | アプ   | リケーション1                            |

| 3 | 概要   | ·                                  |

| 4 | 改訂   | 履歴2                                |

| 5 | 改訂   | '履歴2                               |

| 6 | Pin  | Configuration and Functions 3      |

| 7 | Spe  | cifications5                       |

|   | 7.1  | Absolute Maximum Ratings 5         |

|   | 7.2  | ESD Ratings 5                      |

|   | 7.3  | Recommended Operating Conditions 5 |

|   | 7.4  | Thermal Information 6              |

|   | 7.5  | Electrical Characteristics 6       |

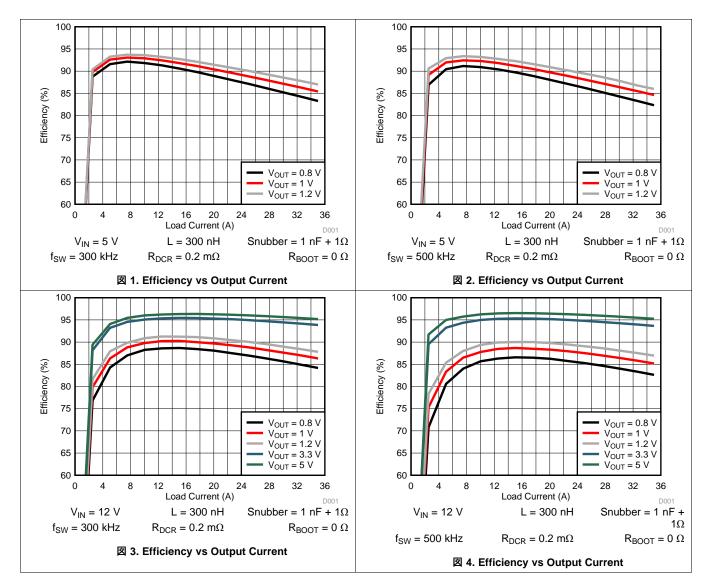

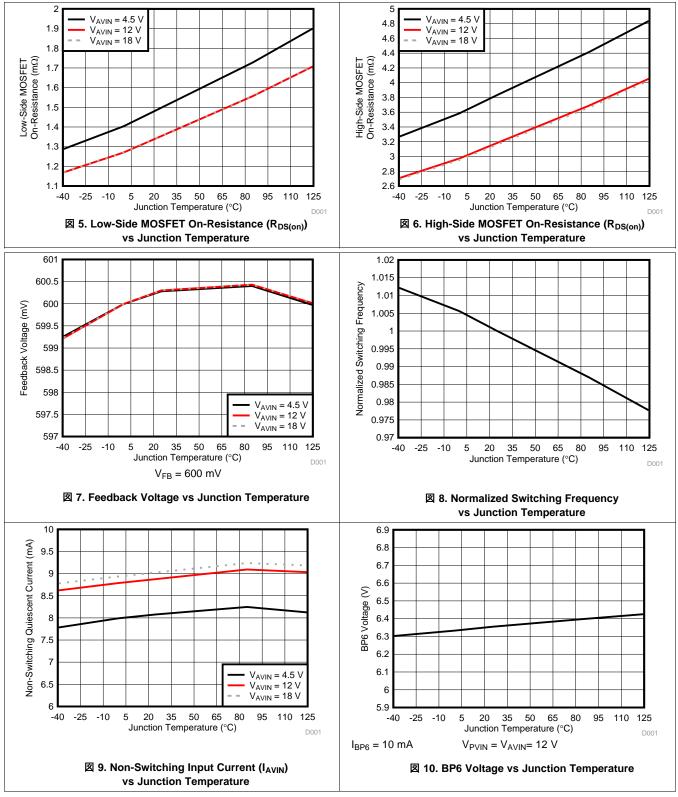

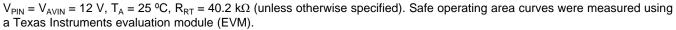

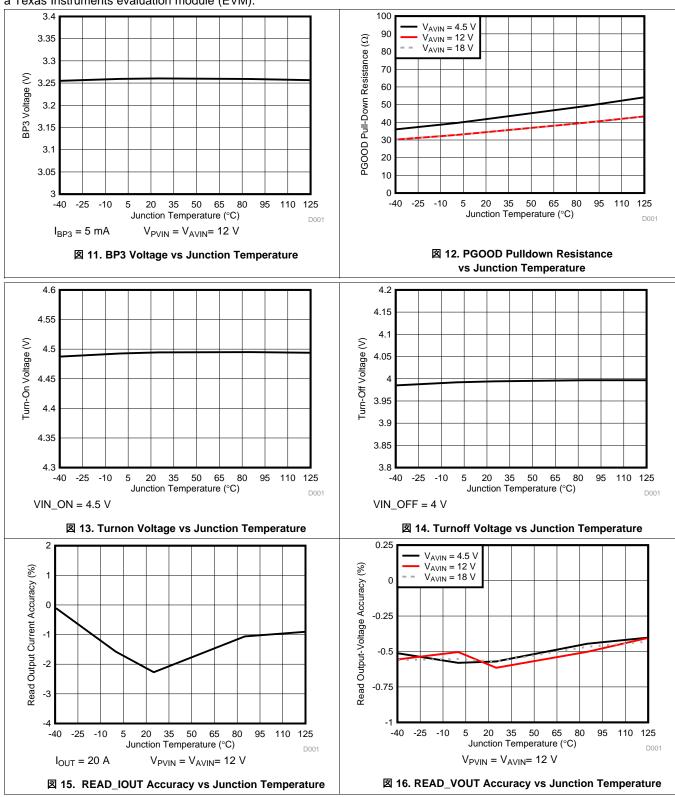

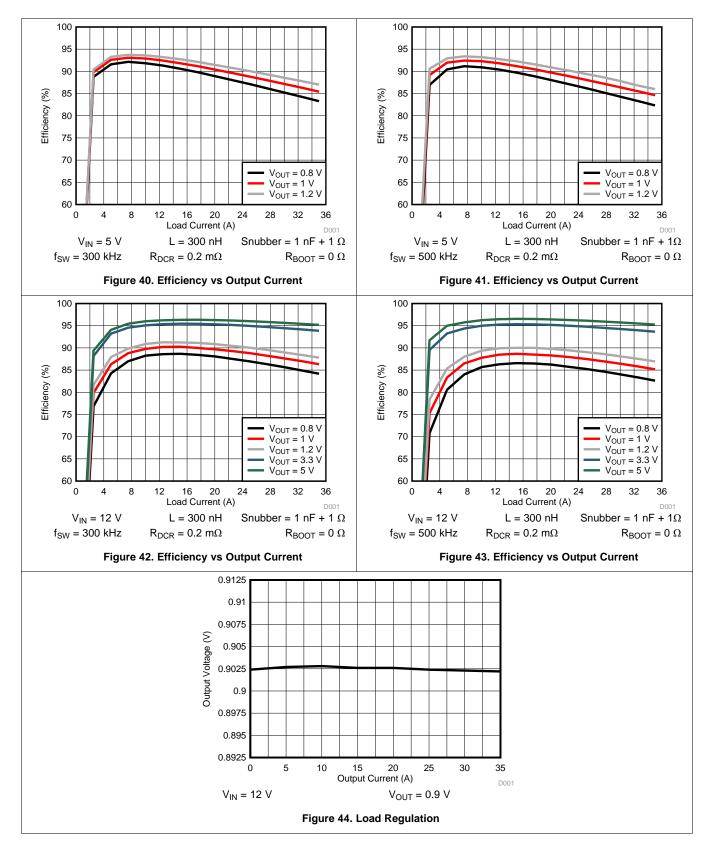

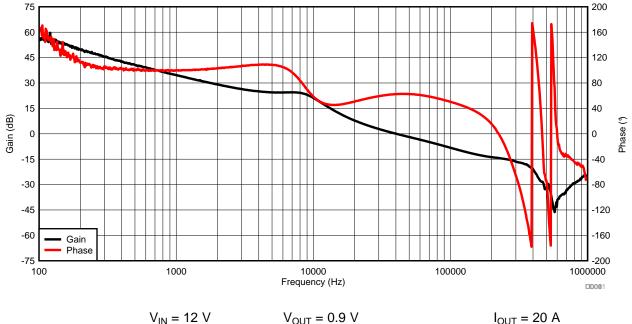

|   | 7.6  | Typical Characteristics 10         |

| 8 | Deta | ailed Description 14               |

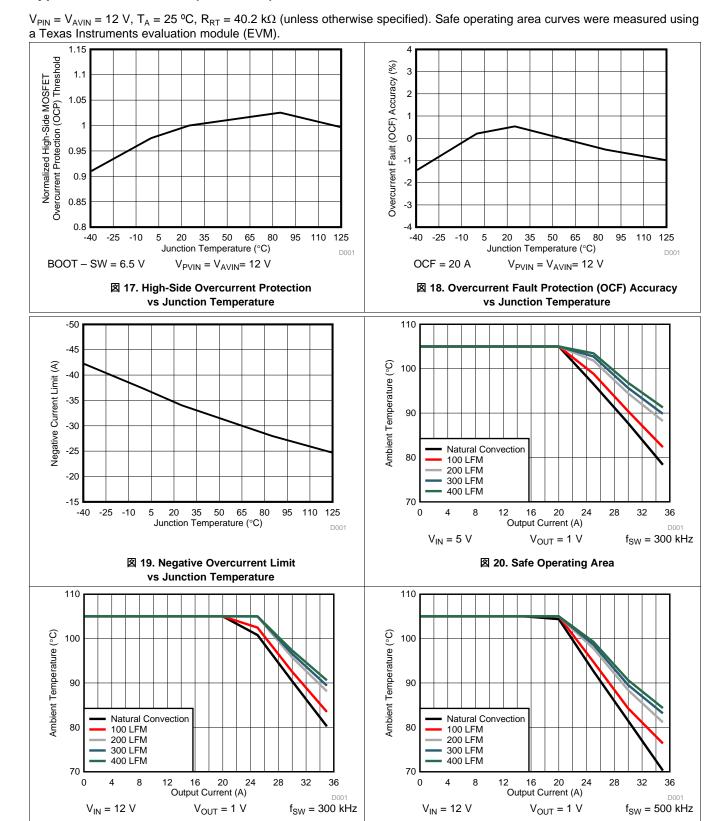

|   | 8.1  | Overview 14                        |

|   | 8.2  | Functional Block Diagram 14        |

|   | 8.3  | Feature Description 15             |

|   | 8.4  | Device Functional Modes 32         |

|    | 8.5  | Programming                                 | 32 |

|----|------|---------------------------------------------|----|

|    | 8.6  | Register Maps                               | 35 |

| 9  | Appl | ication and Implementation                  | 78 |

|    | 9.1  | Application Information                     | 78 |

|    | 9.2  | Typical Application                         | 78 |

| 10 | Pow  | er Supply Recommendations                   | 87 |

| 11 | Layo | out                                         | 87 |

|    | 11.1 | Layout Guidelines                           | 87 |

|    | 11.2 | Layout Example                              | 88 |

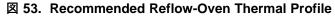

|    | 11.3 | Mounting and Thermal Profile Recommendation | 88 |

| 12 | デバ   | イスおよびドキュメントのサポート                            | 90 |

|    | 12.1 | 開発サポート                                      | 90 |

|    | 12.2 | ドキュメントの更新通知を受け取る方法                          |    |

|    | 12.3 | コミュニティ・リソース                                 | 90 |

|    | 12.4 | 商標                                          | 90 |

|    | 12.5 | 静電気放電に関する注意事項                               | 90 |

|    | 12.6 | Glossary                                    | 91 |

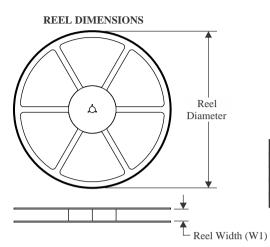

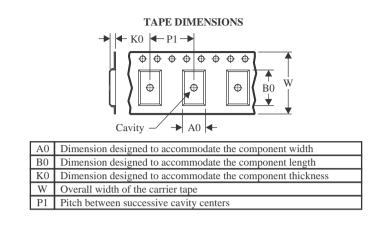

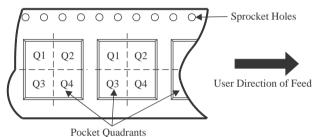

| 13 | メカニ  | ニカル、パッケージ、および注文情報                           | 91 |

|    |      |                                             |    |

### 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Revision B (November 2016) から Revision C に変更 |                                |    |  |  |

|----------------------------------------------|--------------------------------|----|--|--|

| •                                            | データシートのタイトルを更新、WEBENCHへのリンクを追加 | 1  |  |  |

| •                                            | Replace Equation 26            | 81 |  |  |

### Revision A (August) から Revision B に変更

| • | 「特長」の「2つのPMBusアドレス」および「ピン・ストラッピングによりブートアップ」を追加                                        | 1    |

|---|---------------------------------------------------------------------------------------|------|

| • | Added M <sub>IOUT(acc)</sub> spec for ambient temp                                    | 9    |

|   | 変更 図 23                                                                               |      |

| • | 追加 Soft-Start Resistors table                                                         | . 23 |

| • | 削除 "Read only " from the Default Behavior column of 表 5 for CMD Codes 78h through 80h | . 34 |

| • | Changed sentence in Soft-Start Time description for clarification                     | . 83 |

### 2016年7月発行のものから更新

| • 製品のステータスを「製品プレビュー」から「量産データ」へ変更1 |

|-----------------------------------|

|-----------------------------------|

### 5 改訂履歴

| Re | evision B (December 2016) から Revision C に変更 | Page |

|----|---------------------------------------------|------|

| •  | データシートのタイトルを更新、WEBENCHへのリンクを追加              | 1    |

| •  | Replace Equation 26                         | 81   |

Page

Page

www.ti.com

#### www.ti.com

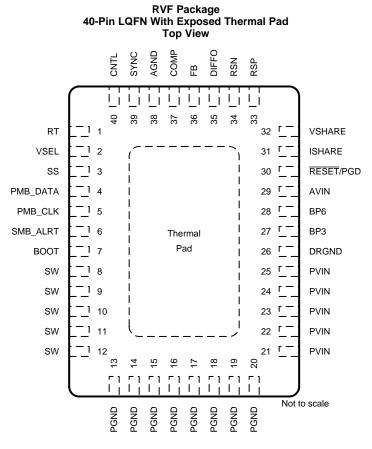

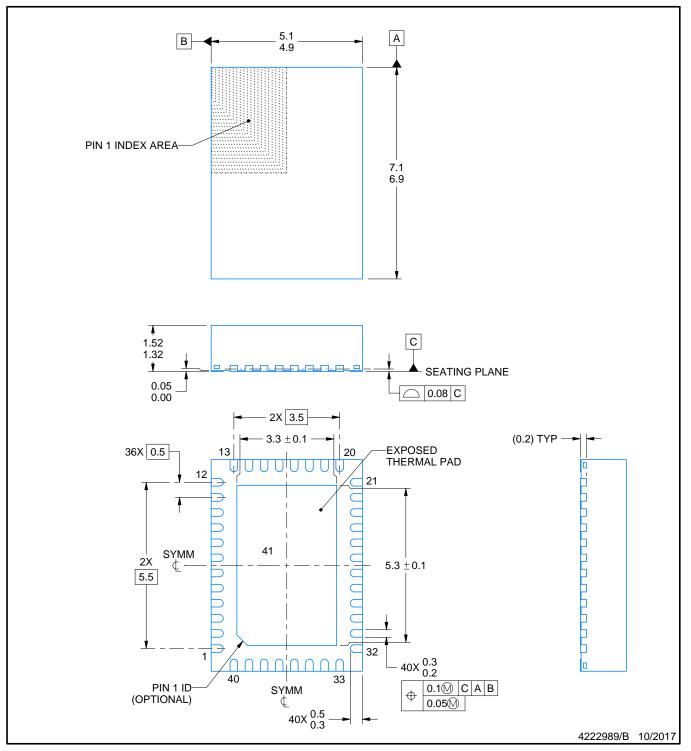

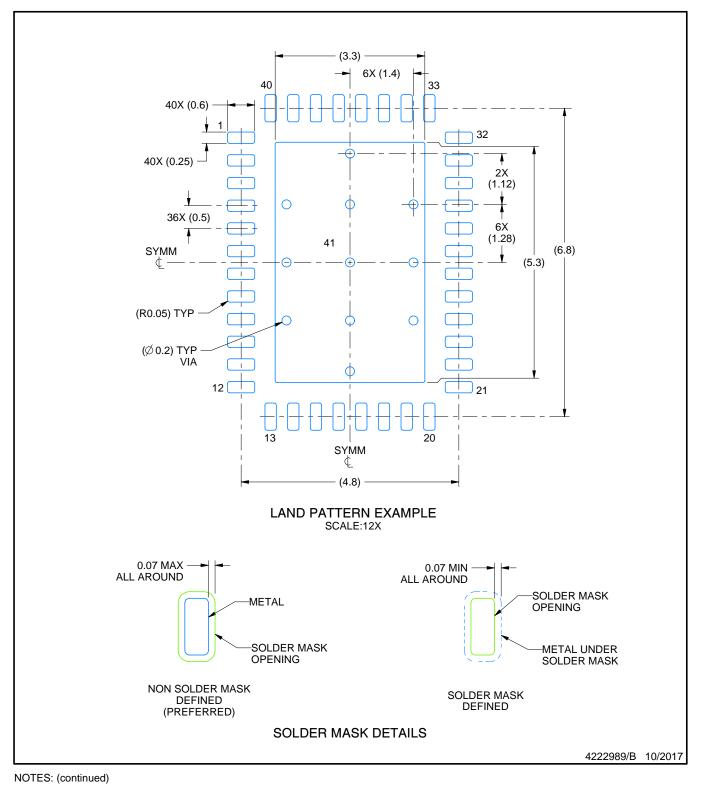

### 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN   |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |  |

|-------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME  | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |  |

| AGND  | 38  | _   | Analog ground return for controller device. Connect this pin to PGND and DRGND at the thermal pad.                                                                                                                                                                                                                                                                     |  |

| AVIN  | 29  | I   | put power to the controller. Connect a low-impedance bypass with a minimum of 1 $\mu$ F to PGND. The AVIN<br>bltage is also used for input feed-forward. PVIN and AVIN must be the same potential for accurate short<br>rcuit protection.                                                                                                                              |  |

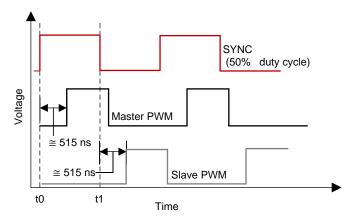

| BP3   | 27  | 0   | put of the 3.3-V onboard regulator. This regulator powers the controller and should be bypassed with a imum of 2.2 $\mu$ F to AGND. The BP3 pin is not designed to power external circuit.                                                                                                                                                                             |  |

| BP6   | 28  | 0   | ut of the 6.5-V onboard regulator. This regulator powers the driver stage of the controller and should be<br>ssed with a minimum of 2.2 $\mu$ F to the thermal pad (power-stage ground, essentially PGND). TI<br>mmends using an additional 100-nF (typical) bypass capacitor for reducing ripple on BP6. The low-<br>dance bypassing of this pin to PGND is critical. |  |

| BOOT  | 7   | I/O | Bootstrap pin for the internal flying high-side driver. Connect a 100-nF (typical) capacitor from this pin to the SW pin. To reduce the voltage spike at SW, a BOOT resistor with a value between 1 $\Omega$ to 15 $\Omega$ can be blaced in series with the BOOT capacitor to slow down turnon of the high-side FET.                                                  |  |

| CNTL  | 40  | I   | PMBus CNTL pin. See the <i>Supported PMBus Commands</i> section. The CNTL pin has an internal pullup and floats high when left floating.                                                                                                                                                                                                                               |  |

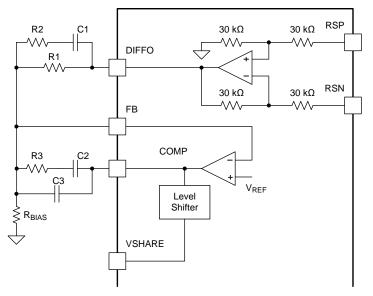

| COMP  | 37  | 0   | Output of the error amplifier. Connect compensator network from this pin to the FB pin.                                                                                                                                                                                                                                                                                |  |

| DIFFO | 35  | 0   | Output of the differential remote sense amplifier. This provides remote sensing for output voltage reporting and the voltage control loop. For the loop slave device in a 2-phase configuration, the DIFFO pin can be left floating.                                                                                                                                   |  |

| DRGND | 26  | _   | Power ground return for controller device. This pin should be directly connected to the thermal pad on the PCB board.                                                                                                                                                                                                                                                  |  |

| FB    | 36  | I   | Feedback pin for the control loop. Negative input of the error amplifier. In 2-phase configuration, the FB pin of the loop slave device should be tied to the BP3 pin.                                                                                                                                                                                                 |  |

TPS546C20A

JAJSFL9C-JULY 2016-REVISED JUNE 2018

www.ti.com

NSTRUMENTS

Texas

### Pin Functions (continued)

| PIN I/O DESCRIPTION |     |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|---------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | NO. | 1/0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

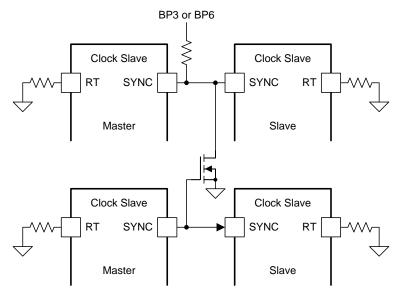

| ISHARE              | 31  | I/O | Current sharing signal for 2-phase operation. For a stand-alone device, the ISHARE pin can be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                     | 13  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 14  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 15  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PGND                | 16  | _   | Power stage ground return. These pins are internally connected to the thermal pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                     | 17  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 18  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 19                  |     | -   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 20  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PMB_CLK             | 5   | I   | PMBus CLK pin. See the Supported PMBus Commands section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| PMB_DATA            | 4   | I/O | PMBus DATA pin. See the Supported PMBus Commands section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                     | 21  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 22  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PVIN                | 23  | I   | Input power to the power stage. Low-impedance bypassing of these pins to PGND is critical.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                     | 24  | -   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 25  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

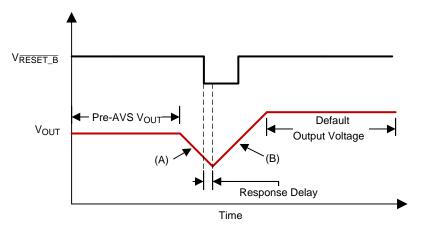

| RESET/PGD           | 30  | I/O | s for the output voltage reset or the power-good output. The function of this pin is determined by accessible bit, EN_RESET_B, in the MFR_SPECIFIC_21 (E4h) register. The default of this pin is wer-good indicator. For output voltage reset, this pin is a logic-low input. An internal pulldown of present so this pin requires a pullup resistor to enable the programming of VOUT. As the power-cator, this pin is an open-drain output which floats up to external pullup when the device is and in regulation. During any fault or warn conditions, this pin is pulled low. For details see 表 4. pin can be left floating when not used.                                                                                                                                                                                                                                                                                                                                  |  |

| RSP                 | 33  | I   | The positive input of the remote sense amplifier. For a stand-alone device or the loop master device in a 2-<br>phase configuration, connect the RSP pin to the output voltage at the load. For the loop slave device in a 2-<br>phase configuration, the remote sense amplifier is not required for output voltage sensing or regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| RSN                 | 34  | I   | The negative input of the remote sense amplifier. For a stand-alone device or the loop master device in a 2 phase configuration, connect the RSN pin to the ground at the load. For the loop slave device in a 2-phase configuration, the remote sense amplifier is not required for output-voltage sensing or regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

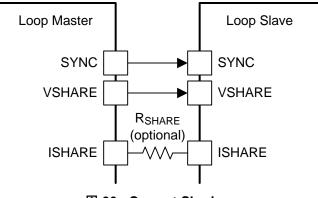

| RT                  | 1   | I   | Frequency-setting resistor. Connect a resistor from this pin to AGND to program the switching frequency. Do not leave this pin floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SMB_ALRT            | 6   | 0   | SMBus™ alert pin. See the Supported PMBus Commands section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                     | 8   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 9   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SW                  | 10  | I/O | Switched power output of the device. Connect the output averaging filter and bootstrap capacitor to this group of pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                     | 11  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                     | 12  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SS                  | 3   | I   | Configures default soft-start time. The SS pin sets default TON_RISE time by connecting a resistor from this pin to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

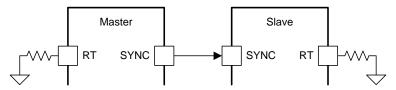

| SYNC                | 39  | I/O | frequency synchronization. For the stand-alone device or the loop master device in a 2-phase figuration, with external pullup to the BP6 pin, the SYNC pin will be configured as SYNC-IN pin, and will synchronized to the rising edge of the external clock applied to this pin. Otherwise, the SYNC pin will be figured as SYNC-IN pin. For the loop slave device in a 2-phase configuration, the SYNC pin will ays be SYNC-IN, and will be synchronized to the falling edge of the incoming clock on SYNC pin. Only 6 duty cycle external clock can be applied to the 2-phase stack to realize the interleaving of 2 phases. Joying an external clock to both the loop master and the loop slave device to synchronize the stack is onal. Without the external clock, the loop master device will output a 50% duty-cycle clock to the loop re device and the slave device will be synchronized to the falling edge of the clock. The SYNC pin can be floating when not used. |  |

| VSEL                | 2   | I   | Configures default output voltage setting. The VSEL pin sets default output voltage by connecting a resistor from this pin to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| VSHARE              | 32  | I/O | Voltage sharing signal for 2-phase operation. For stand-alone device, the VSHARE pin can be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

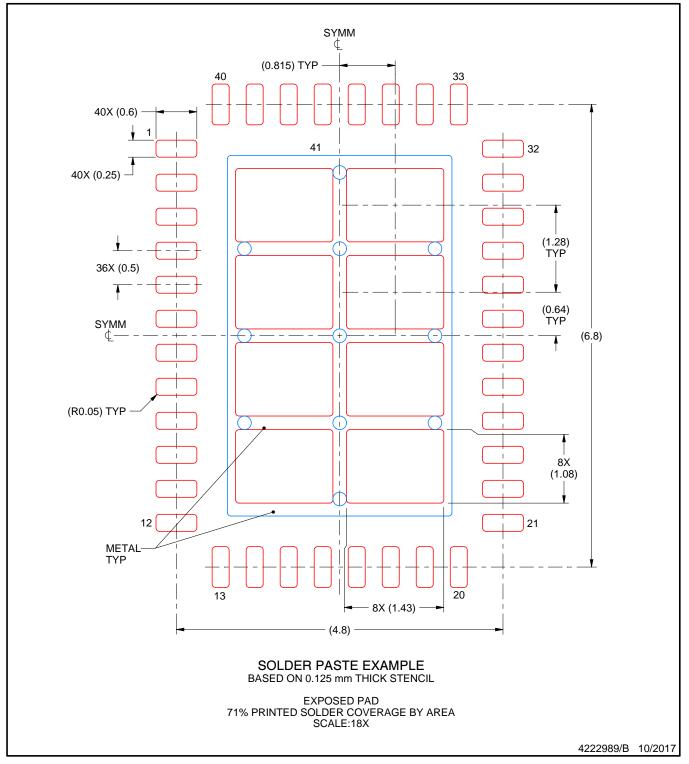

| Thermal pad         | 1   | _   | Package thermal pad, internally connected to PGND. The thermal pad must have adequate solder coverage for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                       |                                                                              | MIN                           | MAX | UNIT |  |

|---------------------------------------|------------------------------------------------------------------------------|-------------------------------|-----|------|--|

|                                       | PVIN, AVIN                                                                   | -0.3                          | 18  |      |  |

|                                       | PVIN, AVIN< 2 ms transient                                                   | -0.3                          | 19  |      |  |

|                                       | PVIN - SW (PVIN to SW differential)                                          | -0.3                          | 25  |      |  |

|                                       | PVIN - SW (PVIN to SW differential, < 10-ns transient because of SW ringing) | -5                            | 25  |      |  |

| Input voltage                         | BOOT                                                                         | -0.3                          | 37  | V    |  |

|                                       | BOOT – SW (BOOT to SW differential)                                          | -0.3                          | 7   |      |  |

|                                       | PMB_CLK, PMB_DATA                                                            |                               | 5.5 |      |  |

|                                       | VSEL, SS                                                                     | PMB_DATA -0.3 5.5<br>-0.3 3.6 |     |      |  |

|                                       | SYNC, RESET/PGD, CNTL, RSP, RSN, RT, ISHARE, FB                              | -0.3                          | 7   |      |  |

|                                       | SW                                                                           | -1                            | 25  |      |  |

|                                       | SW < 100 ns transient                                                        | -1 2                          | 25  |      |  |

| Output voltage                        | BP6, COMP, DIFFO, VSHARE                                                     | -0.3                          | 7   | V    |  |

|                                       | SMB_ALRT                                                                     | -0.3                          | 5.5 |      |  |

|                                       | BP3                                                                          | -0.3                          | 3.6 |      |  |

| Operating junction temperat           | ture, T <sub>J</sub>                                                         | -40                           | 150 | °C   |  |

| Storage temperature, T <sub>stg</sub> |                                                                              | -55                           | 150 | °C   |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

| V <sub>(ESD)</sub> Electrostatic discharge |                         |                                                                                | VALUE | UNIT |

|--------------------------------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                                          | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V(ESD)                                     | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                           | MIN | NOM | MAX | UNIT |

|-------------------|---------------------------|-----|-----|-----|------|

| V <sub>AVIN</sub> | Controller input voltage  | 4.5 | 12  | 18  | V    |

| V <sub>PVIN</sub> | Power stage input voltage | 4.5 | 12  | 18  | V    |

| TJ                | Junction temperature      | -40 |     | 125 | °C   |

#### TPS546C20A

JAJSFL9C – JULY 2016 – REVISED JUNE 2018

www.ti.com

**STRUMENTS**

**EXAS**

### 7.4 Thermal Information

|                       |                                              | TPS546C20A |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RVF (PQFN) | UNIT |

|                       |                                              | 40 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 28.5       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 3.8        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 3.8        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

### 7.5 Electrical Characteristics

$T_{J} = -40^{\circ}$ C to 125°C,  $V_{PVIN} = V_{AVIN} = 12$  V,  $R_{RT} = 40.2$  k $\Omega$ ; zero power dissipation (unless otherwise noted)

|                       | PARAMETER                             | TEST CONDITIONS                                                                         | MIN   | ТҮР                    | MAX  | UNIT |

|-----------------------|---------------------------------------|-----------------------------------------------------------------------------------------|-------|------------------------|------|------|

| INPUT SUPPI           | LY                                    |                                                                                         |       |                        |      |      |

| V <sub>AVIN</sub>     | Input supply voltage range            |                                                                                         | 4.5   |                        | 18   | V    |

| V <sub>PVIN</sub>     | Power stage voltage range             |                                                                                         | 4.5   |                        | 18   | v    |

| I <sub>AVIN</sub>     | Input Operating Current               | Not switching                                                                           |       | 7.7                    | 12   | mA   |

| UVLO                  |                                       |                                                                                         | ·     |                        |      |      |

|                       |                                       | Factory default setting                                                                 |       | 4.5                    |      | V    |

| VIN_ON                | Input turnon voltage                  | Programmable range, 15 different settings                                               | 4.25  |                        | 7.75 | v    |

|                       |                                       | Accuracy                                                                                | -5%   |                        | 5%   |      |

|                       |                                       | Factory default setting                                                                 |       | 4                      |      | V    |

| VIN_OFF               | Input turnoff voltage                 | Programmable range, 15 different settings                                               | 4     |                        | 7.5  | v    |

|                       |                                       | Accuracy                                                                                | -5%   |                        | 5%   |      |

| ERROR AMP             | LIFIER AND FEEDBACK VOLTAGE           |                                                                                         |       |                        |      |      |

| V <sub>FB</sub>       |                                       | Default setting                                                                         |       | 600                    |      | mV   |

|                       | Feedback pin voltage                  | Setpoint range <sup>(1)</sup>                                                           | 0.35  |                        | 1.65 | V    |

|                       |                                       | Setpoint resolution <sup>(1)</sup>                                                      |       | 2 <sup>-9</sup>        |      | V    |

|                       | Feedback pin voltage accuracy         | $V_{FB} = 600 \text{ mV}, 0^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}^{(2)}$     | -0.5% |                        | 0.5% |      |

|                       |                                       | $V_{FB} = 600 \text{ mV}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}^{(2)}$  | -1%   |                        | 1%   |      |

| V <sub>FB(ACC)</sub>  |                                       | $V_{FB} = 1650 \text{ mV}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}^{(2)}$ | -1%   |                        | 1%   | %    |

|                       |                                       | $V_{FB} = 350 \text{ mV}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}^{(2)}$  | -1.5% |                        | 1.5% |      |

| A <sub>OL</sub>       | Open-loop gain <sup>(1)</sup>         |                                                                                         | 80    |                        |      | dB   |

| G <sub>BWP</sub>      | Gain bandwidth product <sup>(1)</sup> |                                                                                         | 15    |                        |      | MHz  |

| I <sub>FB</sub>       | FB pin input bias current             | V <sub>FB</sub> = 0.6 V                                                                 | -75   |                        | 75   | nA   |

| 1                     | Sourcing                              | V <sub>FB</sub> = 0 V                                                                   | 1     |                        |      | mA   |

| ICOMP                 | Sinking                               | V <sub>FB</sub> = 1.2 V                                                                 | 1     |                        |      | mA   |

| OSCILLATOR            | 2                                     |                                                                                         |       |                        |      |      |

| f <sub>SW</sub>       | Adjustment range <sup>(2)</sup>       |                                                                                         | 200   |                        | 1000 | kHz  |

|                       | Switching frequency <sup>(2)</sup>    | $R_{RT} = 40.2 \text{ k}\Omega$                                                         | 450   | 500                    | 550  | kHz  |

| V <sub>RMP</sub>      | Ramp peak-to-peak <sup>(1)</sup>      |                                                                                         | V     | / <sub>AVIN</sub> /6.5 |      | V    |

| V <sub>VLY</sub>      | Valley voltage <sup>(1)</sup>         |                                                                                         |       | 1.23                   |      | V    |

| SYNCHRONIZ            | ZATION                                |                                                                                         |       |                        |      |      |

| V <sub>IH(sync)</sub> | High-level input voltage              |                                                                                         | 2.2   |                        |      | V    |

| VIL(sync)             | Low-level input voltage               |                                                                                         |       |                        | 0.80 | V    |

| T <sub>pw(sync)</sub> | Sync input iminimum pulse width       | Fsw = 160kHz to 1.2MHz                                                                  |       |                        | 200  | ns   |

(1) Specified by design. Not production tested.

(2) The parameter covers 4.5 V to 18 V of AVIN.

#### www.ti.com

### **Electrical Characteristics (continued)**

$T_{J} = -40^{\circ}$ C to 125°C,  $V_{PVIN} = V_{AVIN} = 12$  V,  $R_{RT} = 40.2$  k $\Omega$ ; zero power dissipation (unless otherwise noted)

|                            | PARAMETER                                                                                      | TEST CONDITIONS                                                        | MIN  | TYP  | MAX  | UNIT |

|----------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| T <sub>Mdelay(sync)</sub>  | Delay from the rising edge of SYNC<br>input to the SW rising edge of the loop<br>master device |                                                                        |      | 515  |      | ns   |

| T <sub>S delay(sync)</sub> | Delay from the falling edge of SYNC<br>input to the SW rising edge of the loop<br>slave device |                                                                        |      | 515  |      | ns   |

| f <sub>SYNC</sub>          | Synchronization frequency                                                                      |                                                                        | 160  |      | 1200 | kHz  |

| Δf <sub>SYNC</sub>         | SYNC pin frequency range from free running frequency <sup>(1)</sup>                            |                                                                        | -20% |      | 20%  |      |

| RESET                      |                                                                                                |                                                                        |      |      |      |      |

| V <sub>IH(reset)</sub>     | High-level input voltage <sup>(1)</sup>                                                        |                                                                        | 1.35 |      |      | V    |

| V <sub>IL(reset)</sub>     | Low-level input voltage                                                                        |                                                                        |      |      | 0.8  | v    |

| T <sub>pw(reset)</sub>     | Minimum RESET_B pulse width                                                                    |                                                                        | 200  |      |      | ns   |

| BP6 REGULATO               | R                                                                                              |                                                                        |      |      |      |      |

| V <sub>BP6</sub>           | Regulator output voltage                                                                       | I <sub>BP6</sub> = 10 mA                                               | 5.85 | 6.4  | 6.95 | V    |

| V <sub>BP6(do)</sub>       | Regulator dropout voltage                                                                      | $V_{AVIN}-V_{BP6}, \ V_{AVIN}=4.5 \ V, \ I_{BP6}=25 \ mA$              | 100  | 200  | 400  | mV   |

| I <sub>BP6SC</sub>         | Regulator short-circuit current <sup>(1)</sup>                                                 | V <sub>AVIN</sub> = 12 V                                               |      | 150  |      | mA   |

| V <sub>BP6UV</sub>         | Regulator UVLO voltage <sup>(1)</sup>                                                          |                                                                        |      | 3.73 |      | V    |

| V <sub>BP6UV(hyst)</sub>   | Regulator UVLO voltage hysteresis <sup>(1)</sup>                                               |                                                                        |      | 270  |      | mV   |

| BOOTSTRAP                  |                                                                                                |                                                                        |      |      |      |      |

| V <sub>BOOT(drop)</sub>    | Bootstrap voltage drop                                                                         | I <sub>BOOT</sub> = 5 mA                                               |      |      | 150  | mV   |

| BP3 REGULATO               | R                                                                                              |                                                                        |      |      |      |      |

| V <sub>BP3</sub>           | 3-V regulator output voltage                                                                   | $V_{AVIN} \ge 4.5 \text{ V}, \text{ I}_{BP3} = 5 \text{ mA}$           | 3    | 3.2  | 3.4  | V    |

| I <sub>BP3SC</sub>         | 3-V regulator short-circuit current <sup>(1)</sup>                                             |                                                                        | 18   | 35   |      | mA   |

| PWM                        |                                                                                                |                                                                        |      |      |      |      |

| T <sub>ON(min)</sub>       | Minimum controllable pulse width <sup>(1)</sup>                                                |                                                                        |      |      | 100  | ns   |

| T <sub>OFF(min)</sub>      | Minimum off-time <sup>(1)</sup>                                                                |                                                                        |      | 515  | 550  | ns   |

| SOFT START                 |                                                                                                |                                                                        |      |      |      |      |

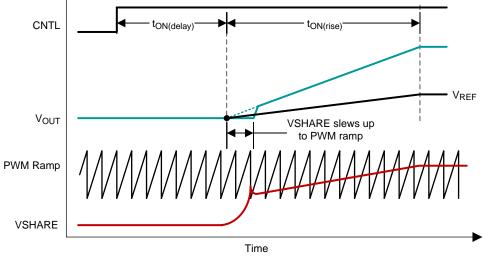

|                            |                                                                                                | Factory default setting                                                |      | 3    |      |      |

| TON_RISE                   | Soft-start time                                                                                | Programmable range, 16 discrete settings <sup>(1)</sup> (3)            | 0    |      | 100  | ms   |

| TON_NOL                    |                                                                                                | Accuracy, TON_RISE = 3 ms, VOUT_COMMAND = 0.95 V                       | -10% |      | 10%  |      |

|                            |                                                                                                | Factory default setting <sup>(4)</sup>                                 |      | 0    |      |      |

| TON_MAX_FAU<br>LT_LIMIT    | Upper limit on the time to power up the output                                                 | Programmable range, 16 discrete settings <sup>(1)</sup> <sup>(4)</sup> | 0    |      | 100  | ms   |

|                            | ouput                                                                                          | Accuracy <sup>(1)</sup>                                                | -10% |      | 10%  |      |

|                            |                                                                                                | Factory default setting                                                |      | 0    |      |      |

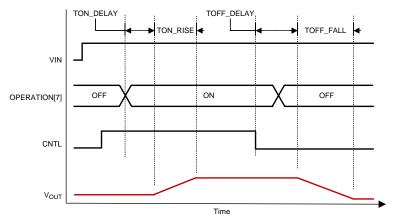

| TON_DELAY                  | Turn-on delay                                                                                  | Programmable range, 16 discrete settings <sup>(1)</sup>                | 0    |      | 100  | ms   |

|                            |                                                                                                | Accuracy <sup>(1)</sup>                                                | -10% |      | 10%  |      |

| SOFT STOP                  |                                                                                                |                                                                        |      |      |      |      |

|                            |                                                                                                | Factory default setting <sup>(5)</sup>                                 |      | 0    |      |      |

| TOFF_FALL                  | Soft-stop time                                                                                 | Programmable range, 16 discrete settings <sup>(1)</sup> <sup>(5)</sup> | 0    |      | 100  | ms   |

| TOFF_FALL                  | Soft-stop time                                                                                 | Accuracy, TOFF_FALL = 1 ms, VOUT_COMMAND = 0.95V                       | -10% |      | 10%  |      |

|                            |                                                                                                | Factory default setting                                                |      | 0    |      |      |

| TOFF_DELAY                 | Turn-off delay                                                                                 | Programmable range, 16 discrete settings <sup>(1)</sup>                | 0    |      | 100  | ms   |

| _                          | 2                                                                                              | Accuracy <sup>(1)</sup>                                                | -10% |      | 10%  |      |

| REMOTE SENSE               |                                                                                                |                                                                        |      |      |      |      |

<sup>(3)</sup> The setting of TON\_RISE of 0 ms means the unit to bring its output voltage to the programmed regulation value as quickly as possible, which results in an effective TON\_RISE time of 1 ms (fastest time supported). The setting of TON\_MAX\_FAULT\_LIMIT of 0 means disabling TON\_MAX\_FAULT response and reporting completely.

<sup>(4)</sup>

The setting of TOFF\_FALL of 0 ms means the unit to bring its output voltage down to 0 as quickly as possible, which results in an (5) effective TOFF\_FALL time of 1 ms (fastest time supported).

www.ti.com

## **Electrical Characteristics (continued)**

$T_J = -40^{\circ}$ C to 125°C,  $V_{PVIN} = V_{AVIN} = 12$  V,  $R_{RT} = 40.2$  k $\Omega$ ; zero power dissipation (unless otherwise noted)

|                           | PARAMETER                                                                                                                                       | TEST CONDITIONS                                                       | MIN  | TYP          | MAX                   | UNIT             |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|--------------|-----------------------|------------------|

|                           |                                                                                                                                                 | $(V_{RSP} - V_{RSN}) = 0.6 V$                                         | -4   |              | 4                     |                  |

| V <sub>DIFFO(ERROR)</sub> | Error Voltage from DIFFO to (RSP –<br>RSN)                                                                                                      | $(V_{RSP} - V_{RSN}) = 1.2 V$                                         | -5   |              | 5                     | mV               |

|                           | ·                                                                                                                                               | $(V_{RSP} - V_{RSN}) = 3 V$                                           | -15  |              | 15                    |                  |

| BW                        | Closed-loop bandwidth <sup>(1)</sup>                                                                                                            |                                                                       | 2    |              |                       | MHz              |

| V <sub>DIFFO(max)</sub>   | Maximum DIFFO output voltage                                                                                                                    |                                                                       |      |              | V <sub>BP6</sub> -0.2 | V                |

| I <sub>DIFFO</sub>        | DIFFO sourcing current                                                                                                                          |                                                                       | 1    |              |                       | mA               |

| DIFFO                     | DIFFO sinking current                                                                                                                           |                                                                       | 1    |              |                       | mA               |

| POWER STAGE               |                                                                                                                                                 |                                                                       |      |              |                       |                  |

| R <sub>HS</sub>           | High-side power device on-resistance                                                                                                            | $V_{BOOT}$ - $V_{SW}$ = 4.5 V, $T_{J}$ = 25°C                         |      | 3.5          |                       | mΩ               |

|                           |                                                                                                                                                 | $V_{BOOT}$ - $V_{SW}$ = 6.3V, $T_{J}$ = 25°C                          |      | 3.2          |                       | mΩ               |

| R <sub>LS</sub>           | Low-side power device on-resistance                                                                                                             | $V_{AVIN} = 4.5 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$        |      | 1.5          |                       | mΩ               |

| NLS                       |                                                                                                                                                 | $V_{AVIN} \ge 12 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$       |      | 1.4          |                       | mΩ               |

| T <sub>DEAD(LtoH)</sub>   | Power stage driver dead-time from<br>Low-side off to High-side on                                                                               | $V_{AVIN} \ge 12 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}^{(1)}$ |      | 15           |                       | ns               |

| T <sub>DEAD(HtoL)</sub>   | Power stage driver dead-time from<br>High-side off to Low-side on                                                                               | $V_{AVIN} \ge 12 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}^{(1)}$ |      | 15           |                       | ns               |

| CURRENT SHAI              | RING                                                                                                                                            | 1                                                                     | L.   |              |                       |                  |

|                           | Output current sharing accuracy of two<br>devices defined as the ratio of the<br>current difference between two devices<br>to the total current | I <sub>OUT</sub> ≥ 20 A per device                                    | -15% |              | 15%                   |                  |

| ISHARE(acc)               | Output current sharing accuracy of two<br>devices defined as the current<br>difference between each device and the<br>half of total current     | I <sub>OUT</sub> < 20 A per device                                    | -3   |              | 3                     | A                |

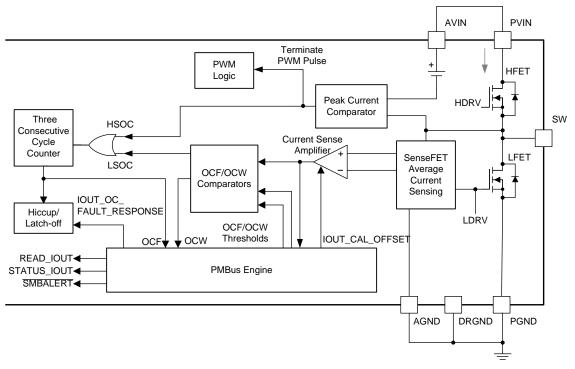

| LOW-SIDE CUR              | RENT LIMIT PROTECTION                                                                                                                           | L                                                                     |      |              |                       | 1                |

|                           |                                                                                                                                                 |                                                                       |      | 7 ×          |                       |                  |

| t <sub>OFF(OC)</sub>      | Off time between restart attempts <sup>(1)</sup>                                                                                                |                                                                       |      | TON_RI<br>SE |                       | ms               |

| IOUT_OC_FAUL              |                                                                                                                                                 | Factory default setting                                               |      | 42           |                       | A                |

| T_LIMIT                   | threshold                                                                                                                                       | Programmable range                                                    | 5    |              | 52                    | ~                |

| NEGOC                     | Negative output current overcurrent<br>protection threshold                                                                                     |                                                                       | -60  | -40          | -20                   | A                |

| IOUT_OC_WAR               | Output current overcurrent warning                                                                                                              | Factory default setting                                               |      | 37           |                       |                  |

| N_LIMIT                   | threshold                                                                                                                                       | Programmable range                                                    | 4    |              | 50                    | A                |

| I <sub>OC(acc)</sub>      | Output current overcurrent fault accuracy                                                                                                       | I <sub>OUT</sub> ≥ 20 A                                               | -15% |              | 15%                   |                  |

| HIGH-SIDE SHO             | RT CIRCUIT PROTECTION                                                                                                                           | I                                                                     |      |              |                       | I                |

| I <sub>HSOC</sub>         | High-side short-circuit protection fault threshold                                                                                              | $(V_{BOOT}-VSW) = 6.3V, T_J = 25^{\circ}C$                            |      | 65           |                       | А                |

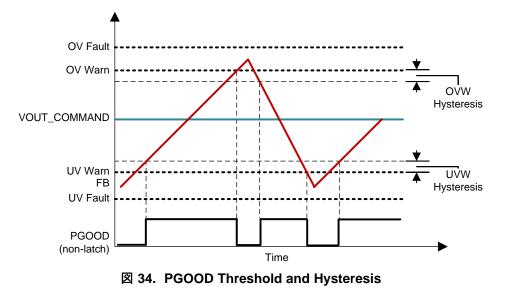

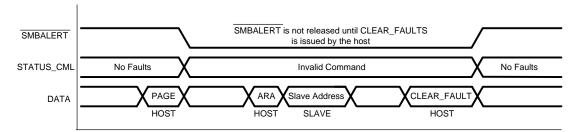

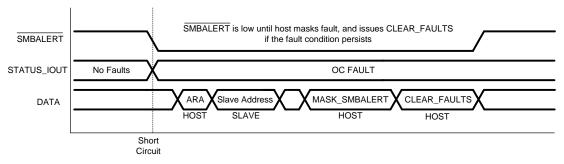

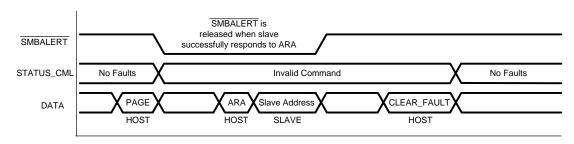

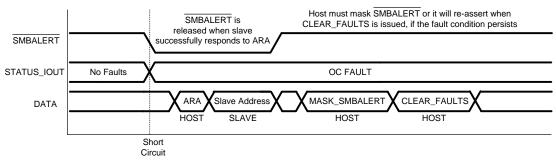

| POWER GOOD                | (PGOOD) AND OVERVOLTAGE/UNDERV                                                                                                                  |                                                                       |      |              |                       |                  |