# Power Stage Designer

#### **ABSTRACT**

Power Stage Designer™ software tool is a Java® based tool that helps engineers speed up their power supply designs by calculating voltages and currents for 21 topologies according to the user's inputs. Additionally, Power Stage Designer contains a Bode plotting tool and a helpful toolbox with various functions for power supply design. This document describes how the different features of Power Stage Designer can be used and also explains the calculations behind these functions.

#### **Table of Contents**

| 1 Topologies Window                                                                   | 2                |

|---------------------------------------------------------------------------------------|------------------|

| 2 FET Losses Calculator                                                               |                  |

| 3 Load Step Calculator                                                                | <mark>7</mark>   |

| 4 Capacitor Current Sharing Calculator                                                | 8                |

| 5 AC/DC Bulk Capacitor Calculator                                                     |                  |

| 6 RCD-Snubber Calculator for Flyback Converters                                       | 11               |

| 7 RC-Snubber Calculator                                                               | 13               |

| 8 Output Voltage Resistor Divider                                                     | 15               |

| 9 Dynamic Analog Output Voltage Scaling                                               | 17               |

| 10 Dynamic Digital Output Voltage Scaling                                             | 18               |

| 11 Unit Converter                                                                     | 19               |

| 12 Loop Calculator                                                                    | <mark>2</mark> 0 |

| 12.1 Inputs                                                                           | 21               |

| 12.2 Transfer Functions                                                               | 23               |

| 13 Filter Designer                                                                    | 35               |

| 13.1 Impedances                                                                       | 35               |

| 13.2 Transfer Functions                                                               | 35               |

| 13.3 Filter Output Impedance                                                          |                  |

| 13.4 Damping Factor                                                                   | 36               |

| 14 Additional Information                                                             |                  |

| 15 Revision History                                                                   | 37               |

|                                                                                       |                  |

| List of Figures                                                                       |                  |

| Figure 1-1. Main Window of Power Stage Designer Displaying Supported Topologies       | 2                |

| Figure 1-2. Topology Window for SEPIC                                                 |                  |

| Figure 1-3. Graph Window for FET Q1 of a SEPIC Operating in CCM                       |                  |

| Figure 2-1. FET Losses Calculator Window                                              | 5                |

| Figure 3-1. Load Step Calculator Window                                               |                  |

| Figure 4-1. Capacitor Current Sharing Calculator                                      | 8                |

| Figure 5-1. Bulk Capacitor Calculator for AC/DC Power Supplies Window                 |                  |

| Figure 6-1. RCD-Snubber Calculator for Flyback Converters Window                      |                  |

| Figure 7-1. RC-Snubber Calculator Window                                              |                  |

| Figure 8-1. Output Voltage Resistor Divider Calculator Window                         |                  |

| Figure 9-1. Dynamic Output Voltage Scaling Calculator Window                          | 17               |

| Figure 10-1. Dynamic Output Voltage Scaling Calculator Window                         |                  |

| Figure 11-1. Unit Converter Window.                                                   |                  |

| Figure 12-1. Loop Calculator Window                                                   |                  |

| Figure 12-2. Schematic of a Type II Compensation Network                              |                  |

| Figure 12-3. Schematic of a Type II Transconductance Compensation Network             |                  |

| Figure 12-4. Schematic of a Type III Compensation Network                             |                  |

| Figure 12-5. Schematic of an Isolated Type II Compensation Network With a Zener Clamp | 32               |

|                                                                                       |                  |

Trademarks www.ti.com

#### **Trademarks**

Power Stage Designer<sup>™</sup> is a trademark of Texas Instruments. Java<sup>®</sup> is a registered trademark of Oracle. All trademarks are the property of their respective owners.

# 1 Topologies Window

To start a power supply design with Power Stage Designer, first select a topology from the Topology menu. The window changes and displays the schematic of the selected topology with a set of input fields and various output values. After entering the parameters of the power supply specification, Power Stage Designer suggests a value for the output inductance to stay below the entered current ripple requirement. For isolated topologies, the tool also displays a recommendation for the transformer turns ratio (TTR) based on the selected maximum duty cycle and suggests a value for the magnetizing inductance. Users can enter values of their choice and evaluate their impact on voltage and current waveforms and other parameters like on-time, off-time, and duty cycle.

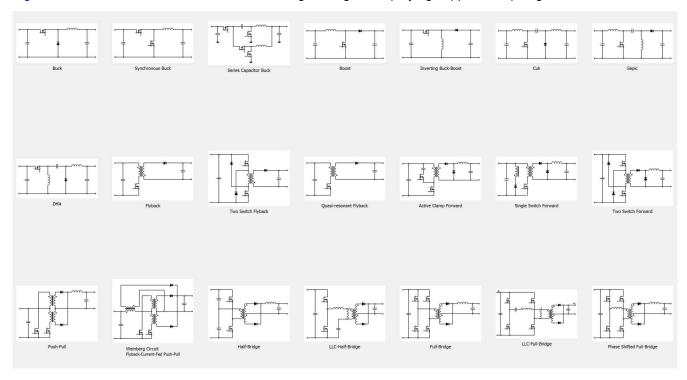

Figure 1-1 shows the main window of Power Stage Designer displaying supported topologies.

Figure 1-1. Main Window of Power Stage Designer Displaying Supported Topologies

www.ti.com Topologies Window

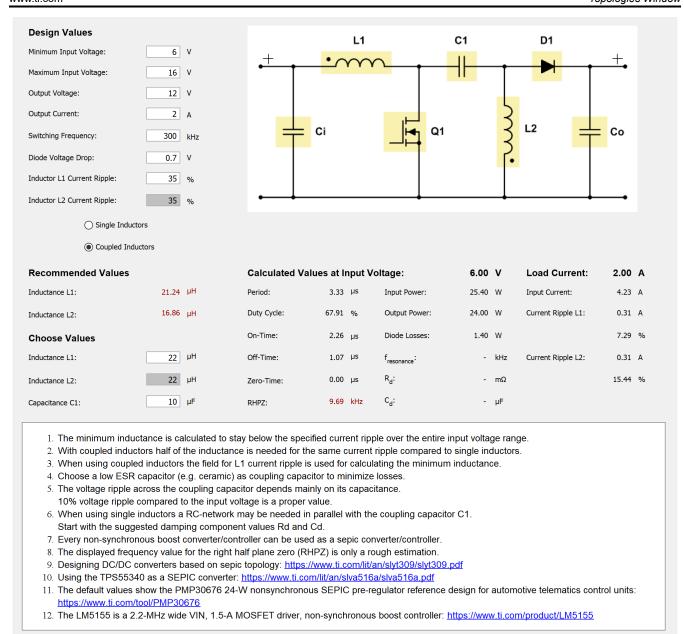

Figure 1-2. Topology Window for SEPIC

After clicking on one of the yellow highlighted components in the schematic (see Figure 1-2), a new window displays the voltage and current waveforms for this specific component (see Figure 1-3). Additional information like the minimum and maximum voltage, minimum and maximum current, as well as root mean square (RMS), average, and AC values for the current is also provided in this window. The input voltage can be changed across the entire input voltage range with a slider. For most topologies the load current can be altered in the range of 1% to 100% of the entered output current with a second slider. Some topology models do not support such a wide load current range, thus the load current slider can be changed only in the range of 50% and 100%. The Quasi-resonant Flyback model uses a fixed output power as base for all calculations. That is why the load current slider is not available for this specific topology.

Topologies Window www.ti.com

Figure 1-3. Graph Window for FET Q1 of a SEPIC Operating in CCM

#### Note

All equations used for calculations are ideal, with the only exception that the forward voltage of rectifier and freewheeling diodes is considered. For a collection of the equations behind certain topologies, see the Power Topologies Handbook.

www.ti.com FET Losses Calculator

#### 2 FET Losses Calculator

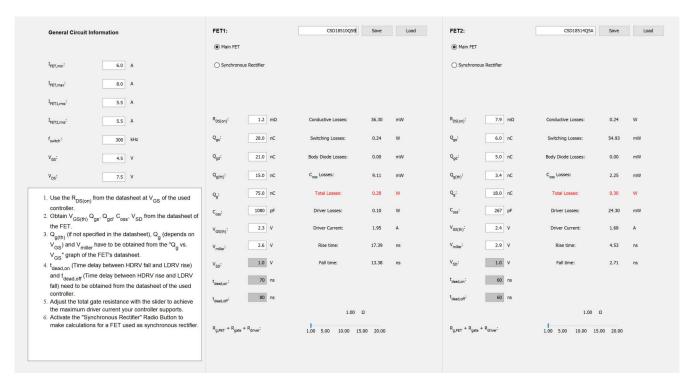

The FET Losses Calculator lets the user either compare two different FETs or calculate losses for the main FET and a synchronous rectifier in a hard-switching power stage. Figure 2-1 shows the FET Losses Calculator window.

#### Note

The Quasi-resonant Flyback, LLC-Half-Bridge, LLC-Full-Bridge, and Phase-Shifted Full-Bridge are resonant topologies. Manual inputs can provide more accurate results.

Figure 2-1. FET Losses Calculator Window

To attain the most accurate results, it is important to determine the gate drive voltage ( $V_{GS}$ ) of the power management controller since the values for  $Q_g$  (which is relevant for driver losses) and  $R_{DS(on)}$  are dependent on this voltage and must be obtained from graphs in the data sheet of the FET.

The different losses which can be seen in the FET of a power supply are conducted losses, switching losses, C<sub>oss</sub> losses, and body diode losses. Reverse recovery losses are neglected, but can become significant at high switching frequencies.

Conductive losses:

$$P_{cond} = I_{FET, rms}^{2} \times R_{DS(on)}$$

(1)

FET Losses Calculator Www.t

Switching losses:

$$t_{rise} = \frac{\left(Q_{gs} - Q_{g(th)}\right) \times R_{g,\,total}}{V_{GS} - \frac{V_{miller}}{2} - \frac{V_{GS(th)}}{2}} + \frac{Q_{gd} \times R_{g,\,total}}{V_{GS} - V_{miller}}$$

$$t_{fall} = \frac{Q_{gd} \times R_{g,\,total}}{V_{miller}} + \frac{\left(Q_{gs} - Q_{g(th)}\right) \times R_{g,\,total}}{\frac{V_{miller}}{2} + \frac{V_{GS(th)}}{2}}$$

$$P_{\text{switching}} = V_{\text{DS}} \times \frac{f_{\text{switch}}}{2} \times \left(t_{\text{rise}} \times I_{\text{FET, min}} + t_{\text{fall}} \times I_{\text{FET, max}}\right)$$

(2)

Coss losses:

$$P_{Coss} = C_{oss} \times V_{DS}^2 \times \frac{f_{switch}}{2}$$

(3)

Body Diode losses:

$$P_{body} = V_{SD} \times f_{switch} \times (t_{dead, on} \times I_{FET, min} + t_{dead, off} \times I_{FET, max})$$

(4)

The total losses for the main FET can be calculated as indicated in Equation 5

$$P_{\text{total}} = P_{\text{cond}} + P_{\text{switching}} + P_{\text{Coss}}$$

(5)

For synchronous rectifiers, the switching losses equal zero due to soft switching, but during the dead time the body diode is conducting. So the total losses result as indicated in Equation 6:

$$P_{\text{total}} = P_{\text{cond}} + P_{\text{body}} + P_{\text{Coss}} \tag{6}$$

Additionally, driver losses occur in the power management controller, which can be calculated as shown in Equation 7:

$$P_{driver} = Q_g \times V_{GS} \times f_{switch}$$

(7)

Power management controllers typically have a limited amount of gate drive current they can source and sink. Therefore, it is important to adjust the total resistance in the gate drive path so the resulting gate drive current is equal to or smaller than the limit in the data sheet.

www.ti.com Load Step Calculator

# 3 Load Step Calculator

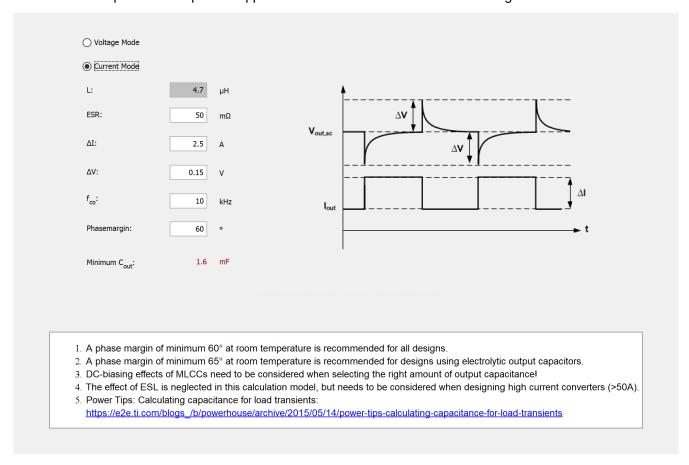

The *Load Step Calculator* enables the user to estimate the minimum required output capacitance to meet certain load transient requirement for power supplies that use current mode control or voltage mode control schemes.

Figure 3-1. Load Step Calculator Window

Current Mode Control (CMC):

$$C_{out} = \frac{1}{2 \times \pi \times f_{co} \times \left(\frac{\Delta V_{out}}{\Delta I_{tran}} - ESR\right) \times \sqrt{2 - 2 \times cos\left(\frac{PM \times \pi}{180^{\circ}}\right)}}$$

(8)

Voltage Mode Control (VMC):

$$C_{\text{out}} = \frac{1}{2 \times \pi \times f_{\text{co}} \times \left(\frac{1}{\frac{\Delta I_{\text{tran}}}{\Delta V_{\text{out}}} - \frac{1}{2 \times \pi \times f_{\text{co}} \times L}} - \text{ESR}\right) \times \sqrt{2 - 2 \times \cos\left(\frac{PM \times \pi}{180^{\circ}}\right)}}$$

(9)

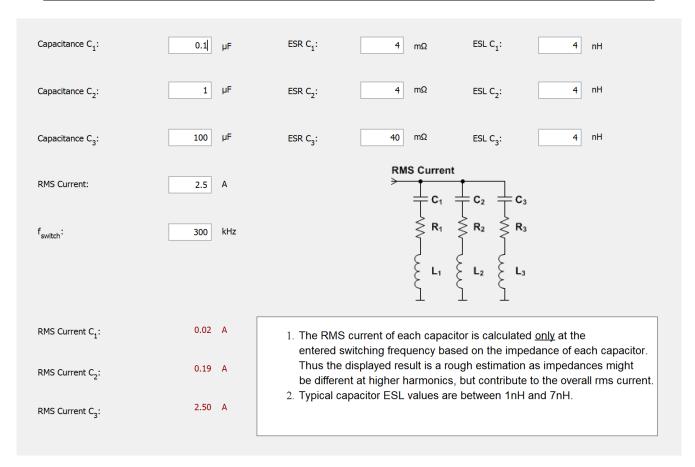

# **4 Capacitor Current Sharing Calculator**

When connecting different kinds of capacitors in parallel at the input or output of a power supply, the RMS current going through each capacitor is different as it depends on the impedance of the capacitors across the entire frequency range. For exact results for the RMS current per capacitor, impedances and currents must be calculated for all harmonics of the switching frequency. The RMS current for each harmonic must be derived with a Fast Fourier Transformation (FFT) of the total current signal based on the ratio between total impedance and single-capacitor impedance at that harmonic frequency.

Figure 4-1 shows the Capacitor Current Sharing Calculator.

#### Note

In Power Stage Designer, the impedances and the RMS currents are only calculated at the switching frequency. Thus, the resulting RMS currents are rough estimations.

Figure 4-1. Capacitor Current Sharing Calculator

The impedance for one capacitor at the switching frequency (n can be 1, 2, or 3 and refers to the capacitor index) can be calculated as indicated in Equation 10:

$$Z_{cap, n} = ESRC_n + i \times \left(2 \times \pi \times f_{switch} \times ESLC_n - \frac{1}{2 \times \pi \times f_{switch} \times C_n}\right)$$

(10)

Typical ESL values for capacitors are from 1 nH to 7 nH. By assuming 6 nH/cm as parasitic inductance for a conductor, the inductance for a ceramic capacitor can be estimated by multiplying this value with the capacitor length. PCB traces and vias can increase this value slightly (see [1]).

The total impedance of three parallel capacitors at the switching frequency results as seen in Equation 11:

$$Z_{\text{total}} = \frac{1}{\frac{1}{Z_{\text{cap, 1}}} + \frac{1}{Z_{\text{cap, 2}}} + \frac{1}{Z_{\text{cap, 3}}}}$$

(11)

The RMS current of one capacitor, while neglecting all other harmonics besides the switching frequency, can be calculated as seen in Equation 12:

$$I_{rms, cap, n} = I_{rms, total} \times \frac{|Z_{total}|}{|Z_{cap, n}|}$$

(12)

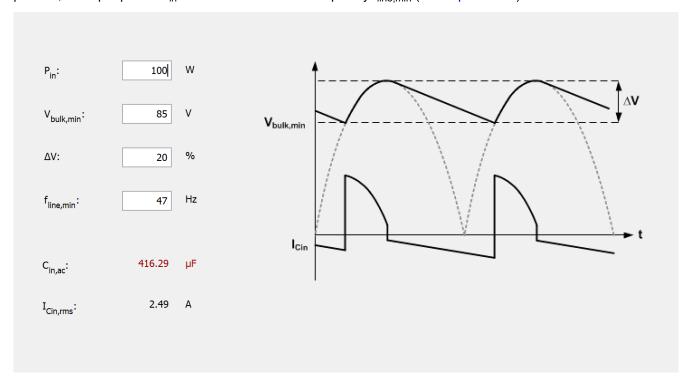

# 5 AC/DC Bulk Capacitor Calculator

AC/DC power supplies typically require a bulk capacitor behind the input rectifier that provides a quasi-constant input voltage for the converter stage (see Figure 5-1). Power Stage Designer can calculate the minimum capacitance based on the desired minimum bulk voltage  $V_{bulk,min}$ , the maximum acceptable voltage ripple  $\Delta V$  in percent, the input power  $P_{in}$  and the minimum line frequency  $f_{line,min}$  (see Equation 13).

Figure 5-1. Bulk Capacitor Calculator for AC/DC Power Supplies Window

$$\begin{split} V_{AC,\,min} &= \frac{V_{bulk,\,min}}{(1-\Delta V)\times\sqrt{2}} \\ t_{discharge} &= \frac{1}{4\times f_{line,\,min}} + \frac{1}{2\times\pi\times f_{line,\,min}} \times sin^{-1}(1-\Delta V) \\ t_{charge} &= \frac{1}{4\times f_{line,\,min}} - \frac{1}{2\times\pi\times f_{line,\,min}} \times sin^{-1}(1-\Delta V) \\ C_{bulk} &= \frac{2\times P_{in}\times t_{discharge}}{V_{bulk,\,min}^2\times\left(\left(\frac{1}{1-\Delta V}\right)^2-1\right)} \\ I_{bulk,\,rms} &= \sqrt{\left(\frac{C_{bulk}\times V_{bulk,\,min}\times\left(\frac{1}{1-\Delta V}-1\right)}{t_{charge}\times\sqrt{3}}\right)^2+\left(\frac{P_{in}}{V_{bulk,\,min}}\right)^2} \end{split} \tag{13}$$

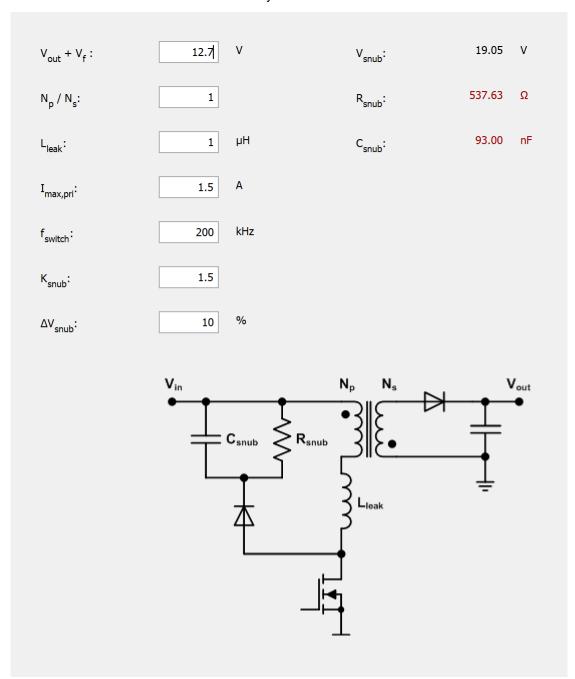

# 6 RCD-Snubber Calculator for Flyback Converters

In Flyback converters the output voltage is reflected from the secondary to the primary side. Additionally, parasitics caused by the layout and the Flyback transformer leakage inductance can cause a voltage spike followed by ringing when the MOSFET is turning off. The voltage spike and the ringing can be limited by implementing an RCD-snubber circuit in parallel to the primary winding. The energy of the high-frequency ringing is dissipated in the RCD-network. The RCD-Snubber Calculator for Flyback converters in Power Stage Designer helps the designer choose the starting values for snubber resistor and capacitor based on the user's inputs, which follow:

- · Sum of output voltage and rectifier voltage

- Flyback transformer turns ratio

- · Leakage inductance

- Maximum primary current

- Switching frequency

- Permitted voltage overshoot as a factor

- Snubber capacitor voltage ripple in percent

Figure 6-1 shows the RCD-Snubber Calculator for Flyback Converters window.

Figure 6-1. RCD-Snubber Calculator for Flyback Converters Window

$V_{snub}$  is the reflected output voltage plus the permitted overshoot caused by transformer leakage inductance and switching node parasitics. Thus  $K_{snub}$  has a value greater than 1. TI recommends a value of 1.5 for most applications, permitting 50% overshoot (see [1]). See Equation 14.

$$V_{snub} = K_{snub} \times \frac{N_p}{N_s} \times (V_{out} + V_f)$$

(14)

WWw.ti.com RC-Snubber Calculator

Starting Snubber resistance:

$$R_{snub} = \frac{V_{snub}^{2}}{\frac{1}{2} \times L_{leak} \times I_{max, pri}^{2} \times \frac{V_{snub}}{V_{snub} - \frac{N_{p}}{N_{s}} \times (V_{out} + V_{f})}} \times f_{switch}$$

(15)

Starting Snubber capacitance:

$$C_{\text{snub}} = \frac{V_{\text{snub}}}{\Delta V_{\text{snub}} \times V_{\text{snub}} \times R_{\text{snub}} \times f_{\text{switch}}}$$

(16)

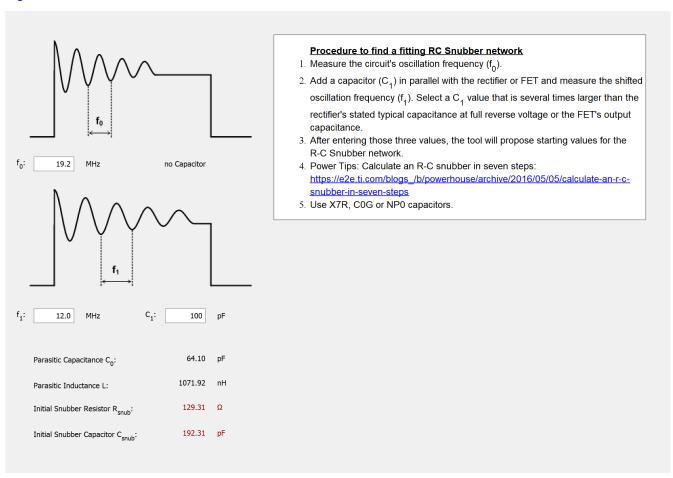

#### 7 RC-Snubber Calculator

An RC-Snubber circuit is one option to reduce ringing in a switch mode power supply. Alternatives are the use of MOSFET gate resistors or a resistor in series with the bootstrap capacitor to slow down rise and/or fall times. With the RC-Snubber Calculator, Power Stage Designer helps the designer determine starting values for the snubber resistor and capacitor.

Figure 7-1 shows the RC-Snubber Calculator window.

Figure 7-1. RC-Snubber Calculator Window

- Measure the oscillation frequency f<sub>0</sub> of the circuit without a snubber network.

- Add a capacitor C<sub>1</sub> in parallel with the rectifier or FET and measure the shifted oscillation frequency f<sub>1</sub>. Select

a C<sub>1</sub> value that is several times larger than the stated typical capacitance of the rectifier at full reverse voltage

or the output capacitance of the FET.

- After entering these three values, the tool will propose starting values for the R-C Snubber network.

RC-Snubber Calculator www.ti.com

Frequency shift ratio:

$$m = \frac{f_0}{f_1} \tag{17}$$

Parasitic capacitance:

$$C_0 = \frac{C_1}{m^2 - 1} \tag{18}$$

Parasitic inductance:

$$L = \frac{m^2 - 1}{(2 \times \pi \times f_0)^2 \times C_1}$$

(19)

Initial Snubber capacitance:

$$C_{\text{snub}} = 3 \times C_0 \tag{20}$$

Initial Snubber resistance:

$$R_{\rm snub} = \sqrt{\frac{L}{C_0}} \tag{21}$$

# 8 Output Voltage Resistor Divider

The Output Voltage Resistor Divider Tool calculates the closest resistor values of the chosen E-Series to match the specified output voltage based on the entered reference voltage, reference voltage tolerance, and desired resistance value. The resistance value can be entered for the high-side (HS) or the low-side (LS) resistor. It is also possible to parallel two resistors to get more precise results. The following equations calculate the resulting output voltage while respecting resistor tolerances and reference voltage tolerances. However, because effects caused by the bias current are not considered for the calculations, these values are estimates.

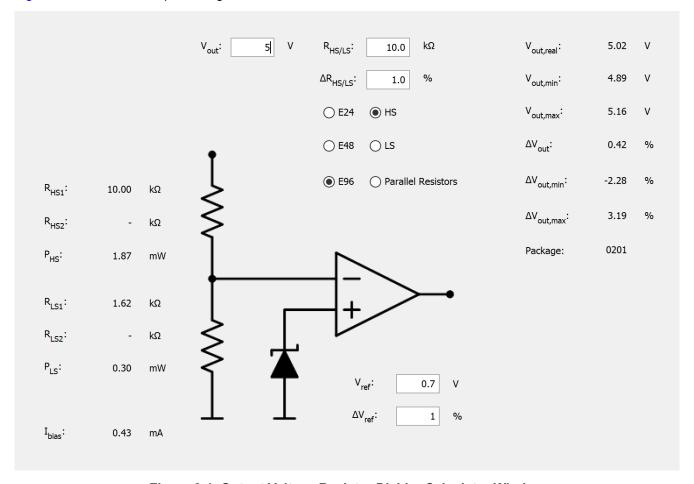

Figure 8-1 shows the Output Voltage Resistor Divider Calculator window.

Figure 8-1. Output Voltage Resistor Divider Calculator Window

Effective output voltage with chosen resistance values (see Equation 22):

$$V_{\text{out, real}} = V_{\text{ref}} \times \frac{R_{\text{HS}} + R_{\text{LS}}}{R_{\text{LS}}}$$

$$\Delta V_{\text{out}} = \frac{V_{\text{out, real}} - V_{\text{out}}}{V_{\text{out}}}$$

(22)

Bias current:

$$I_{bias} = \frac{V_{out, real}}{R_{HS} + R_{LS}}$$

(23)

Worst-case minimum output voltage:

$$V_{\text{out, min}} = V_{\text{ref, min}} \times \frac{R_{\text{HS, min}} + R_{\text{LS, max}}}{R_{\text{LS, max}}}$$

$$\Delta V_{\text{out, min}} = \frac{V_{\text{out, min}} - V_{\text{out}}}{V_{\text{out}}}$$

(24)

Worst-case maximum output voltage:

$$V_{out,\,max} = V_{ref,\,max} \times \frac{R_{HS,\,max} + R_{LS,\,min}}{R_{LS,\,min}}$$

$$\Delta V_{\text{out, max}} = \frac{V_{\text{out, max}} - V_{\text{out}}}{V_{\text{out}}}$$

(25)

# 9 Dynamic Analog Output Voltage Scaling

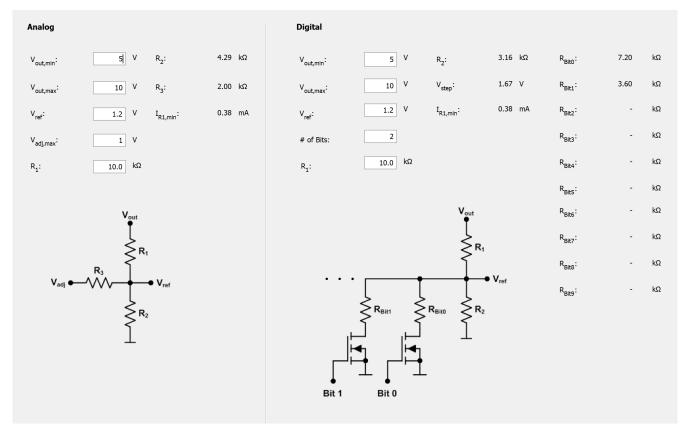

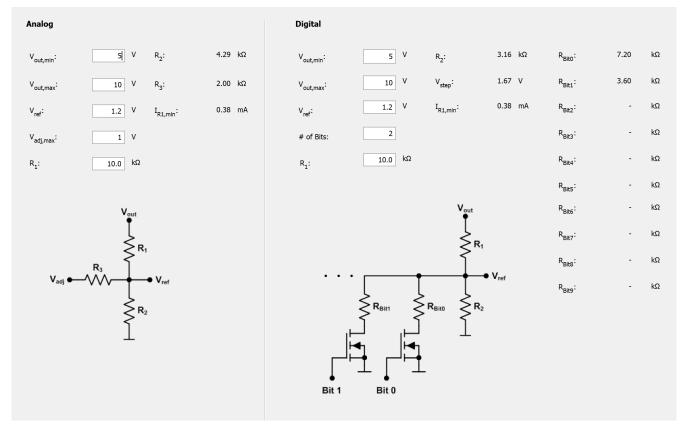

If the output voltage of a power supply must be adjustable, add a third resistor to the feedback resistor divider and apply an analog voltage to this resistor (for example, with the DAC of a microcontroller). The analog signal can also be provided by smoothing a PWM signal with a low-pass filter. After entering the minimum output voltage, maximum output voltage, reference voltage, maximum adjusting voltage signal, and the desired value for the top feedback resistor, Power Stage Designer calculates the required bottom feedback resistance and the adjusting voltage signal series resistance, as well as the minimum bias current going through the top feedback resistor.

Figure 9-1 shows the Dynamic Output Voltage Scaling Calculator window.

Figure 9-1. Dynamic Output Voltage Scaling Calculator Window

$$\begin{split} I_{R1,\,\text{min}} &= \frac{V_{\text{out},\,\text{min}} - V_{\text{ref}}}{R_1} \\ R_3 &= \frac{R_1 \times V_{\text{adj},\,\text{max}}}{V_{\text{out},\,\text{max}} - V_{\text{ref}} - R_1 \times I_{R1,\,\text{min}}} \\ R_2 &= \frac{R_1 \times R_3 \times V_{\text{ref}}}{R_3 \times V_{\text{out},\,\text{max}} - R_3 \times V_{\text{ref}} - R_1 \times V_{\text{ref}}} \end{split} \tag{26}$$

# 10 Dynamic Digital Output Voltage Scaling

Dynamic output voltage adjustment can also be achieved by applying GPIO signals to an array of resistors and signal FET combinations in parallel with the low-side resistor of the feedback divider. For most cases, a microcontroller output in open-drain configuration can be used instead of an external signal FET because it is already part of the system. Power Stage Designer calculates the low-side feedback resistor, the voltage per step, the bias current, and the series resistance for each bit based on the output voltage range, the reference voltage, the number of bits, and the value of the high-side feedback resistor.

Figure 10-1 shows the Dynamic Output Voltage Scaling Calculator window.

Figure 10-1. Dynamic Output Voltage Scaling Calculator Window

$$\begin{split} I_{R1,\,\text{min}} &= \frac{V_{\text{out},\,\text{min}} - V_{\text{ref}}}{R_1} \\ R_2 &= \frac{R_1 \times V_{\text{ref}}}{V_{\text{out},\,\text{min}} - V_{\text{ref}}} \\ V_{\text{step}} &= \frac{V_{\text{out},\,\text{max}} - V_{\text{out},\,\text{min}}}{2^{\text{Bits}} - 1} \\ R_{\text{Bit}\,n} &= \frac{1}{\frac{V_{\text{out},\,\text{min}} + 2^{\text{Bit}} \times V_{\text{step}} - V_{\text{ref}}}{R_1 \times V_{\text{ref}}} - \frac{1}{R_2} \end{split} \tag{27}$$

The LM10011 is a device that has this feature integrated for 4/6-Bit VID.

www.ti.com Unit Converter

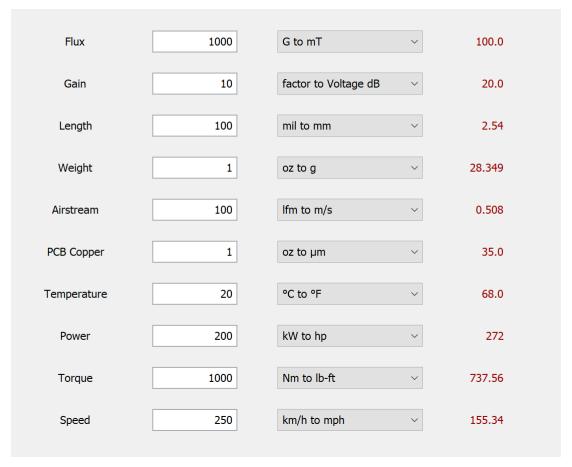

### 11 Unit Converter

The Unit Converter can help power supply designers convert typical parameters related to power supplies. These parameters are magnetic flux, gain, length, weight, airstream, PCB copper thickness, and temperature. Figure 11-1 shows the Unit Converter window.

Figure 11-1. Unit Converter Window

Loop Calculator www.ti.com

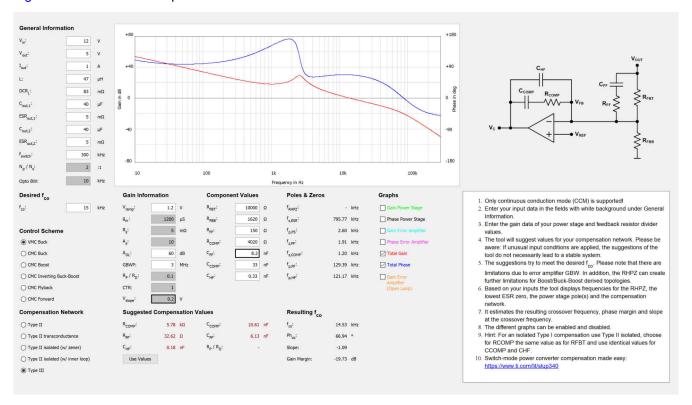

# 12 Loop Calculator

The Loop Calculator can help power supply designers with the compensation network for voltage mode controlled (VMC) buck converters or current mode controlled (CMC) buck, boost, inverting buck-boost, forward, and flyback converters operating in continuous conduction mode (CCM). The transfer functions have been simplified, thus the results give a first-order approximation of how the Bode plot of the power supply will appear. Figure 12-1 shows the Loop Calculator window.

Figure 12-1. Loop Calculator Window

The following steps apply when using the Loop Calculator.

- Select the topology/control scheme and the type of compensation for the design with the radio buttons in the bottom-left corner. Typically, only the VMC buck needs a Type III Compensation. For all CMC topologies, a Type II Compensation is usually sufficient.

- 2. Fill in all input fields with white background. If the Loop Calculator is started from one of the supported topologies, applicable values from the topologies window will directly transfer to the Loop Calculator window.

- Under General Information (from the schematic) sum the capacitance of the same output capacitor types and calculate their effective ESR. The DC-biasing effect for ceramic capacitors must be considered because it can have a major impact on the accuracy of the gain and phase plot of the power stage.

- 4. Enter the Gain Information (from the schematic and the data sheet for the controller).

- 5. Fill in the values for RFBT and RFBB. With this information the Loop Calculator can suggest values for the compensation network of the entered power supply design.

www.ti.com Loop Calculator

The compensation network suggestions are calculated as follows:

#### **CAUTION**

If unusual input conditions are applied, the suggestions of the tool do not necessarily lead to a stable system.

- Compensation zeroes are placed on the pole of the transfer function of the power stage (L and C<sub>out</sub> double pole for VMC, R<sub>out</sub> and C<sub>out</sub> single pole for CMC).

- Compensation poles are placed on the lower of either half of the switching frequency or the ESR zero for Buck derived topologies.

- Compensation poles are placed on the lower of either the right half plane zero (RHPZ) frequency or the ESR zero frequency for Boost/Buck-Boost derived topologies.

- The maximum achievable crossover frequency is approximately two decades below the GBWP (gain bandwidth product) of the error amplifier. The gain of the compensation network should never go above the open loop gain of the error amplifier. Otherwise, the error amplifier will be clipping.

- For Boost/Buck-Boost derived topologies the desired crossover frequency is automatically set to 1/5 of the RHPZ frequency.

#### 12.1 Inputs

Table 12-1 lists general information.

**Table 12-1. General Information**

| rabio 12 11 Gonoral Information |                                                                                                   |  |

|---------------------------------|---------------------------------------------------------------------------------------------------|--|

| V <sub>in</sub>                 | Input voltage                                                                                     |  |

| V <sub>out</sub>                | Output voltage                                                                                    |  |

| l <sub>out</sub>                | Load current                                                                                      |  |

| L                               | Inductance / Flyback primary inductance                                                           |  |

| DCR <sub>L</sub>                | Inductor DC resistance                                                                            |  |

| C <sub>out,1</sub>              | Capacitance output capacitor 1 For ceramic capacitors use the capacitance at the DC bias voltage. |  |

| ESR <sub>out,1</sub>            | Equivalent series resistance output capacitor 1                                                   |  |

| C <sub>out,2</sub>              | Capacitance output capacitor 2 For ceramic capacitors use the capacitance at the DC bias voltage. |  |

| ESR <sub>out,2</sub>            | Equivalent series resistance output capacitor 2                                                   |  |

| f <sub>switch</sub>             | Switching frequency                                                                               |  |

| $N_p/N_s$                       | Transformer turns ratio                                                                           |  |

| Opto BW                         | Optocoupler bandwidth                                                                             |  |

|                                 |                                                                                                   |  |

Table 12-2 lists gain information.

**Table 12-2. Gain Information**

| $V_{ramp}$         | PWM ramp voltage                       |

|--------------------|----------------------------------------|

| G <sub>m</sub>     | Error amplifier transconductance       |

| A <sub>s</sub>     | Current-sense amplifier gain           |

| R <sub>s</sub>     | Current-sense resistance               |

| A <sub>OL</sub>    | Error amplifier open-loop gain         |

| GBWP               | Error amplifier gain bandwidth product |

| $R_p/R_D$          | Optocoupler transfer ratio             |

| CTR                | Current Transfer Ratio                 |

| V <sub>slope</sub> | Slope compensation voltage             |

| SLM                | Slope compensation multiplier          |

Loop Calculator www.ti.com

Current-sense gain A<sub>s</sub> and current-sense resistance R<sub>s</sub>:

For converters with integrated current-sensing circuits, sometimes there are no specific values for  $A_s$  and  $R_s$  in the data sheet. Instead, a value for  $G_{m,ps}$  (can also appear as "COMP to switch current transconductance") is typically displayed. Equation 28 shows the relationship between these values.

$$G_{m, ps} = \frac{1}{A_s \times R_s} \tag{28}$$

In this case, values for  $A_s$  and  $R_s$  must be chosen to have the stated  $G_{m,ps}$  as a result. (For example, use the  $R_{DS(on)}$  of the internal FET for  $R_s$  and calculate  $A_s$  from Equation 28.)

The input field for  $V_{slope}$  offers the user the option to use either  $V_{slope}$  or a slope compensation multiplier (SLM), in case the value for  $V_{slope}$  cannot be calculated by the designer (for example, because of internal slope compensation). Switching between these two variables can be done by right-clicking on the  $V_{slope}$ /SLM input field.

# V<sub>slope</sub>:

Calculate the value for V<sub>slope</sub> with the equations from the data sheet. If the device has internal slope compensation, a value for V<sub>slope</sub> is typically given in the Electrical Characteristics section.

#### SLM:

- SLM is a variable to simulate the slope compensation under certain circumstances. How it affects calculations can be found in the subsections for each topology.

- Ideal slope compensation will be calculated with a value of 1.

- Values greater than 1 show how the converter will drift to VMC with increasing values of SLM, as the

information of the original current signal will be lost at a certain point. A Type III compensation network would

then be necessary to compensate the converter.

- Values in the range from 0 to 1 simulate conditions when not enough slope compensation is present, and a

resonance will become visible at half the switching frequency caused by the quality factor of the double pole

of the inductance.

Table 12-3 lists component values.

Table 12-3. Component Values

| R <sub>FBT</sub>  | Top feedback resistance                 |  |

|-------------------|-----------------------------------------|--|

| R <sub>FBB</sub>  | Bottom feedback resistance              |  |

| R <sub>FF</sub>   | Compensation feed-forward resistance    |  |

| R <sub>COMP</sub> | Compensation resistance                 |  |

| $C_{FF}$          | Compensation feed-forward capacitance   |  |

| $C_COMP$          | Compensation capacitance                |  |

| C <sub>HF</sub>   | Compensation high-frequency capacitance |  |

For Type II and Type II transconductance compensation networks, the Loop Calculator offers an option to use an additional Feed-Forward Capacitor in parallel with RFBT. This option can be enabled by right-clicking on the C<sub>FF</sub> input field and choosing *Use*.

At start-up the Loop Calculator displays only the resulting Bode plot for the Total Gain and Total Phase. The graphs for the Gain of the Power Stage, Phase of the Power Stage, Gain of the Error Amplifier, Phase of the Error Amplifier and the Error Amplifier Open Loop Gain can be switched on by selecting the respective checkbox.

www.ti.com Loop Calculator

#### 12.2 Transfer Functions

#### 12.2.1 Output Impedance Transfer Function

For two parallel capacitors the transfer function can be written as shown in Equation 29:

$$Z_{out} = \frac{R_{out} \times (s \times C_1 \times ESR_1 + 1) \times (s \times C_2 \times ESR_2 + 1)}{(s \times C_1 \times ESR_1 + 1) \times (s \times C_2 \times ESR_2 + 1) + R_{out} \times [s \times C_2 \times (s \times C_1 \times ESR_1 + 1) + s \times C_1 \times (s \times C_2 \times ESR_2 + 1)]}$$

(29)

#### 12.2.2 Transfer Function VMC Buck Power Stage

$$\frac{\hat{v}_{out}}{\hat{v}_c} = \frac{K_m \times Z_{out}}{Z_L + Z_{out}} \tag{30}$$

DC-Gain:

$$K_m = \frac{V_{in}}{V_{ramp}} \tag{31}$$

Filter-Inductor Impedance:

$$Z_L = s \times L + DCR_L \tag{32}$$

### 12.2.3 Transfer Function CMC Buck Power Stage

$$\frac{\widehat{V}out}{\widehat{V}c} = \frac{K_m \times Z_{out}}{Z_L + Z_{out} + K_m \times R_i \times H(s)}$$

(33)

Duty cycle:

$$D = \frac{V_{\text{out}}}{V_{\text{in}}}$$

(34)

DC-Gain:

$$K_{m} = \frac{1}{(0.5 - D) \times R_{S} \times A_{S} \times \frac{1}{f_{switch} \times L} + \frac{V_{slope}}{V_{in}}}$$

(35)

Sampling Gain Pole:

$$\omega_L = \pi \times f_{switch}$$

(36)

$$R_i = A_S \times R_S \tag{37}$$

$$H(s) = 1 + \frac{s}{Q_L \times \omega_L} + \frac{s^2}{\omega_L^2} \tag{38}$$

With  $V_{slope}$ :

$$s_{e} = V_{slope} \times f_{switch}$$

(39)

With SLM:

$$s_{e} = \frac{\text{SLM} \times \text{V}_{out} \times \text{A}_{\text{S}} \times \text{R}_{\text{S}}}{\text{L}}$$

$$s_n = \frac{(v_{in} - v_{out}) \times A_S \times R_S}{L}$$

$$Q_{L} = \frac{1}{\pi \times \left[ \left( 1 + \frac{s_{e}}{s_{n}} \right) \times (1 - D) - 0.5 \right]}$$

$$\tag{40}$$

### 12.2.4 Transfer Function CMC Boost Power Stage

$$\frac{\widehat{v}_{out}}{\widehat{v}_{c}} = \frac{K_{m} \times \left(1 - D\right) \times \left(1 - \frac{Z_{L}}{\left(1 - D\right)^{2} \times R_{out}}\right)}{\left(1 - D\right)^{2} + \frac{Z_{L}}{Z_{out}} + K_{m} \times R_{i} \times H(s) \times \left(\frac{1}{R_{out}} + \frac{1}{Z_{out}}\right) + K \times K_{m} \times (1 - D) \times \left(1 - \frac{Z_{L}}{\left(1 - D\right)^{2} \times R_{out}}\right)}$$

(41)

Duty cycle:

$$D = \frac{V_{\text{out}} - V_{\text{in}}}{V_{\text{out}}}$$

(42)

DC-Gain:

$$K_m = \frac{1}{(0.5 - D) \times R_S \times A_S \times \frac{1}{f_{switch} \times L} + \frac{V_{slope}}{V_{in}}}$$

$$\tag{43}$$

$$K = 0.5 \times R_S \times A_S \times \frac{1}{f_{switch} \times L} \times D \times (1 - D)$$

(44)

Sampling Gain Pole:

$$\omega_L = \pi \times f_{switch}$$

(45)

$$R_i = A_S \times R_S \tag{46}$$

$$H(s) = 1 + \frac{s}{Q_L \times \omega_L} + \frac{s^2}{\omega_L^2} \tag{47}$$

With V<sub>slope</sub>:

$$s_{e} = V_{slope} \times f_{switch} \tag{48}$$

www.ti.com Loop Calculator

#### With SLM:

$$s_e = \frac{\text{SLM} \times \text{V}_{out} \times \text{A}_\text{S} \times \text{R}_\text{S}}{\text{L}}$$

$$s_n = \frac{v_{in} \times A_s \times R_s}{L}$$

$$Q_{L} = \frac{1}{\pi \times \left[ \left( 1 + \frac{s_{e}}{s_{n}} \right) \times (1 - D) - 0.5 \right]}$$

$$\tag{49}$$

### 12.2.5 Transfer Function CMC Inverting Buck-Boost Power Stage

$$\frac{\widehat{v}_{out}}{\widehat{v}_{c}} = \frac{K_{m} \times \left(1 - D\right) \times \left(1 - \frac{D \times Z_{L}}{\left(1 - D\right)^{2} \times R_{out}}\right)}{\left(1 - D\right)^{2} + \frac{Z_{L}}{Z_{out}} + K_{m} \times R_{i} \times H(s) \times \left(\frac{D}{R_{out}} + \frac{1}{Z_{out}}\right) + K \times K_{m} \times (1 - D) \times \left(1 - \frac{D \times Z_{L}}{\left(1 - D\right)^{2} \times R_{out}}\right)}$$

(50)

Duty cycle:

$$D = \frac{-V_{\text{out}}}{-V_{\text{out}} + V_{\text{in}}} \tag{51}$$

Sampling Gain Pole:

$$\omega_{L} = \pi \times f_{\text{switch}} \tag{52}$$

$$R_i = A_S \times R_S \tag{53}$$

$$H(s) = 1 + \frac{s}{Q_L \times \omega_L} + \frac{s^2}{\omega_I^2} \tag{54}$$

$$K_m = \frac{1}{(0.5 - D) \times R_S \times A_S \times \frac{1}{f_{switch} \times L} + \frac{V_{slope}}{V_{in} - V_{out}}}$$

(55)

$$K = 0.5 \times R_S \times A_S \times \frac{1}{f_{switch} \times L} \times D \times (1 - D)$$

(56)

With V<sub>slope</sub>:

$$s_{e} = V_{slope} \times f_{switch}$$

(57)

Loop Calculator

With SLM:

$$s_{e} = \frac{\text{SLM} \times (-V_{out}) \times A_{S} \times R_{S}}{L}$$

$$s_{n} = \frac{V_{in} \times A_{S} \times R_{S}}{L}$$

$$Q_{L} = \frac{1}{\pi \times \left[ \left( 1 + \frac{s_{e}}{s_{n}} \right) \times (1 - D) - 0.5 \right]}$$

(58)

# 12.2.6 Transfer Function CMC Forward Power Stage

For interleaved topologies like Push-Pull, Half-Bridge, or Full-Bridge, twice as much FET switching frequency must be used for calculations because the output inductor "sees" twice the FET switching frequency.

$$\frac{\hat{v}_{out}}{\hat{v}_c} = \frac{K_m \times Z_{out} \times \frac{N_S}{N_p}}{Z_L + Z_{out} + K_m \times R_i \times \frac{N_S}{N_p}}$$

(59)

Duty cycle:

$$D = \frac{V_{\text{out}} \times \frac{N_p}{N_s}}{V_{\text{in}}}$$

(60)

DC-Gain:

$$K_{m} = \frac{1}{(0.5 - D) \times R_{S} \times A_{S} \times \frac{1}{f_{SW} \times L} + \frac{V_{slope}}{V_{in}}}$$

$$\tag{61}$$

Sampling Gain Pole:

$$\omega_L = \pi \times f_{switch} \tag{62}$$

$$R_i = A_S \times R_S \tag{63}$$

$$A_{\mathcal{S}} = \frac{1}{N'} \tag{64}$$

N' is the turns ratio between auxiliary and primary winding.

$$H(s) = 1 + \frac{s}{Q_L \times \omega_L} + \frac{s^2}{\omega_L^2} \tag{65}$$

With V<sub>slope</sub>:

$$s_{e} = V_{slope} \times f_{switch}$$

(66)

www.ti.com Loop Calculator

With SLM:

$$s_{e} = \frac{\text{SLM} \times \text{V}_{out} \times \frac{\text{N}_{p}}{\text{N}_{s}} \times \text{A}_{s} \times \text{R}_{s}}{\text{L} \times \left(\frac{\text{N}_{p}}{\text{N}_{s}}\right)^{2}}$$

$$s_{n} = \frac{\left(\text{V}_{in} \times \frac{\text{N}_{s}}{\text{N}_{p}} - \text{V}_{out}\right) \times \text{A}_{s} \times \text{R}_{s}}{\text{L}}$$

$$Q_{L} = \frac{1}{\pi \times \left[\left(1 + \frac{\text{S}_{e}}{\text{s}}\right) \times (1 - D) - 0.5\right]}$$

(67)

# 12.2.7 Transfer Function CMC Flyback Power Stage

$$= \frac{K_m \times \left(1 - D\right) \times \left(1 - \frac{D \times Z_L}{\left(1 - D\right)^2 \times R_{out} \times \left(\frac{N_p}{N_s}\right)^2}\right)}{\left(1 - D\right)^2 + \frac{Z_L}{Z_{out} \times \left(\frac{N_p}{N_s}\right)^2} + K_m \times R_i \times H(s) \times \left(\frac{D}{R_{out} \times} + \frac{1}{Z_{out} \times \left(\frac{N_p}{N_s}\right)^2}\right) + K \times K_m \times (1 - D) \times \left(1 - \frac{D \times Z_L}{\left(1 - D\right)^2 \times R_{out} \times \left(\frac{N_p}{N_s}\right)^2}\right)}$$

Duty cycle:

$$D = \frac{V_{\text{out}} \times \frac{N_p}{N_s}}{V_{\text{in}} + V_{\text{out}} \times \frac{N_p}{N_s}}$$

(69)

DC-Gain:

$$K_{m} = \frac{1}{(0.5 - D) \times R_{S} \times A_{S} \times \frac{1}{f_{SW} \times L} + \frac{V_{slope}}{V_{in} + \left(\frac{N_{p}}{N_{c}}\right) \times V_{out}}}$$

$$(70)$$

$$K = 0.5 \times R_S \times A_S \times \frac{1}{f_{switch} \times L} \times D \times (1 - D)$$

(71)

Sampling Gain Pole:

$$\omega_L = \pi \times f_{switch}$$

(72)

$$R_i = A_S \times R_S \tag{73}$$

$$H(s) = 1 + \frac{s}{Q_L \times \omega_L} + \frac{s^2}{\omega_L^2} \tag{74}$$

With V<sub>slope</sub>:

$$s_e = V_{slope} \times f_{switch} \tag{75}$$

(68)

Loop Calculator Www.

With SLM:

$$s_{e} = \frac{SLM \times V_{out} \times \frac{N_{p}}{N_{s}} \times A_{s} \times R_{s}}{L}$$

$$s_{n} = \frac{V_{in} \times A_{s} \times R_{s}}{L}$$

$$Q_{L} = \frac{1}{\pi \times \left[ \left( 1 + \frac{S_{e}}{S_{r}} \right) \times (1 - D) - 0.5 \right]}$$

(76)

#### 12.2.8 Transfer Function Closed Loop

Closed-loop error amplifier transfer function for non-isolated feedback:

$$\frac{\widehat{\mathbf{v}}_{\mathrm{c}}}{\widehat{\mathbf{v}}_{\mathrm{out}}} = -\mathbf{G}_{\mathrm{EA}}(\mathbf{s}) \times \frac{1}{1 + \left(\frac{1}{\mathrm{A}_{\mathrm{OL}}} + \frac{\mathbf{s}}{\omega_{\mathrm{BW}}}\right) + (1 + \mathbf{G}_{\mathrm{FB}}(\mathbf{s}))}$$

(77)

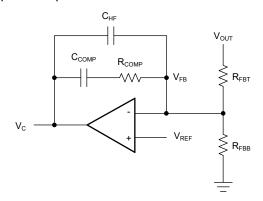

#### 12.2.8.1 Transfer Function Type II Compensation Network

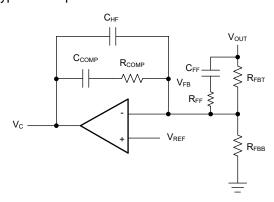

Figure 12-2 is a schematic of a Type II compensation network.

Figure 12-2. Schematic of a Type II Compensation Network

Type II with feed forward:

$$G_{EA}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right) \times \left(1 + \frac{s}{\omega_{ZFF}}\right)}{\left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(78)

$$G_{FB}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right) \times \left(1 + \frac{s}{\omega_{ZFF}}\right)}{\frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times \left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(79)

Type II:

$$G_{EA}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(80)

$$G_{FB}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times \left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(81)

www.ti.com Loop Calculator

Compensation zero:

$$\omega_{\rm ZEA} = \frac{1}{R_{\rm COMP} \times C_{\rm COMP}}$$

(82)

Compensation pole:

$$\omega_{HF} = \frac{1}{R_{COMP} \times C_{HF}} \tag{83}$$

With additional feed-forward capacitor in parallel with R<sub>FBT</sub>:

$$\omega_{ZFF} = \frac{1}{R_{FBT} \times C_{FF}}$$

$$\omega_{PFF} = \frac{1}{\left(\frac{1}{R_{RFBB}} + \frac{1}{R_{RFBT}}\right) \times C_{FF}}$$

(84)

Loop Calculator Www.ti.com

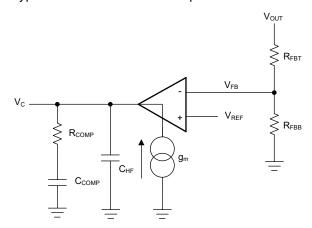

#### 12.2.8.2 Transfer Function Type II Transconductance Compensation Network

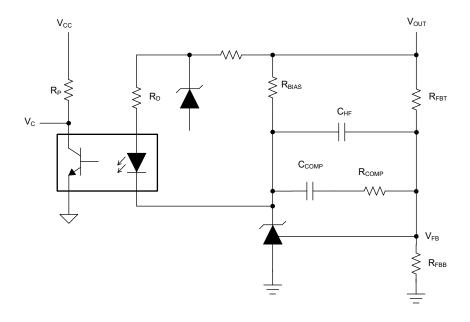

Figure 12-3 is a schematic of a Type II transconductance compensation network.

Figure 12-3. Schematic of a Type II Transconductance Compensation Network

Type II Transconductance with feed-forward:

$$G_{EA}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right) \times \left(1 + \frac{s}{\omega_{ZFF}}\right)}{\left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{PFF}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(85)

$$G_{FB}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right) \times \left(1 + \frac{s}{\omega_{ZFF}}\right)}{\frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times \left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{PFF}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(86)

Type II Transconductance:

$$G_{EA}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(87)

$$G_{FB}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times \left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(88)

DC-Gain:

$$A_{VM} = \frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times G_m \times R_{COMP}$$

(89)

Compensation zero:

$$\omega_{\text{ZEA}} = \frac{1}{\text{RCOMP} \times \text{CCOMP}} \tag{90}$$

Compensation Pole:

$$\omega_{\rm HF} = \frac{1}{R_{\rm COMP} \times C_{\rm HF}} \tag{91}$$

www.ti.com Loop Calculator

With additional feed-forward capacitor in parallel with R<sub>FBT</sub>:

$$\omega_{ZFF} = \frac{1}{R_{FBT} \times C_{CFF}}$$

$$\omega_{PFF} = \frac{1}{\frac{1}{R_{RFBB}} + \frac{1}{R_{RFBT}}} \times C_{FF}$$

(92)

# 12.2.8.3 Transfer Function Type III Compensation Network

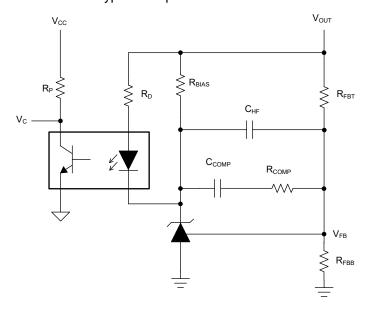

Figure 12-4 is a schematic of a Type III compensation network.

Figure 12-4. Schematic of a Type III Compensation Network

Type III:

$$G_{EA}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right) \times \left(1 + \frac{s}{\omega_{ZFF}}\right)}{\left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{PFF}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(93)

$$G_{FB}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right) \times \left(1 + \frac{s}{\omega_{ZFF}}\right)}{\frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times \left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{PFF}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(94)

DC-Gain:

$$A_{VM} = \frac{R_{COMP}}{R_{FBT}}$$

(95)

Compensation zero 1:

$$\omega_{\text{ZEA}} = \frac{1}{R_{\text{COMP}} \times C_{\text{COMP}}}$$

(96)

Compensation zero 2:

$$\omega_{\rm ZFF} = \frac{1}{R_{\rm FBT} \times C_{\rm FF}} \tag{97}$$

Loop Calculator Www.ti.com

Compensation pole 1:

$$\omega_{\rm FP} = \frac{1}{R_{\rm FF} \times C_{\rm FF}} \tag{98}$$

Compensation pole 2:

$$\omega_{\rm HF} = \frac{1}{R_{\rm COMP} \times C_{\rm HF}} \tag{99}$$

# 12.2.9 Transfer Function Isolated Type II Compensation Network With a Zener Clamp

Figure 12-5 is a schematic of an isolated Type II compensation network with a Zener clamp.

Figure 12-5. Schematic of an Isolated Type II Compensation Network With a Zener Clamp

Closed loop error amplifier transfer function for isolated feedback.

Type II Isolated with Zener Clamp:

$$\frac{\hat{v}_C}{\hat{v}_{out}} = -CTR(s) \times \frac{R_P}{R_D} \times G_{EA}(s) \times \frac{1}{1 + \left(\frac{1}{A_{OL}} + \frac{s}{\omega_{BW}}\right) + (1 + G_{FB}(s))}$$

(100)

$$G_{EA}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(101)

$$G_{FB}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times \left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(102)

$$CTR(s) = \frac{CTR}{1 + \frac{s}{\omega_{OPTO}}} \tag{103}$$

www.ti.com Loop Calculator

DC-Gain:

$$A_{VM} = CTR \times \frac{R_P}{R_D} \tag{104}$$

Power Stage Designer uses a constant value of 1 for CTR.

Compensation zero:

$$\omega_{\text{ZEA}} = \frac{1}{R_{\text{COMP}} \times C_{\text{COMP}}} \tag{105}$$

Compensation pole:

$$\omega_{\rm HF} = \frac{1}{R_{\rm COMP} \times C_{\rm HF}} \tag{106}$$

### 12.2.10 Transfer Function Isolated Type II Compensation Network Without a Zener Clamp

Figure 12-6 is a schematic of an isolated Type II compensation network without a Zener clamp.

Figure 12-6. Schematic of an Isolated Type II Compensation Network Without a Zener Clamp

$$\frac{\widehat{v}_{c}}{\widehat{v}_{out}} = -CTR(s) \times \frac{R_{P}}{R_{D}} \times \left[ 1 + G_{EA}(s) \times \frac{1}{1 + \left(\frac{1}{A_{OL}} + \frac{s}{\omega_{BW}}\right) + (1 + G_{FB}(s))} \right]$$

(107)

$$G_{EA}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(108)

$$G_{FB}(s) = \frac{A_{VM} \times \frac{\omega_{ZEA}}{s} \times \left(1 + \frac{s}{\omega_{ZEA}}\right)}{\frac{R_{FBB}}{R_{FBB} + R_{FBT}} \times \left(1 + \frac{C_{HF}}{C_{COMP}}\right) \times \left(1 + \frac{s}{\omega_{HF}}\right)}$$

(109)

$$CTR(s) = \frac{CTR}{1 + \frac{s}{\omega_{OPTO}}}$$

(110)

Loop Calculator www.ti.com

DC-Gain:

$$A_{VM} = CTR \times \frac{R_P}{R_D} \tag{111}$$

Compensation Zero:

$$\omega_{\text{ZEA}} = \frac{1}{R_{\text{COMP}} \times C_{\text{COMP}}} \tag{112}$$

Compensation pole:

$$\omega_{\rm HF} = \frac{1}{R_{\rm COMP} \times C_{\rm HF}} \tag{113}$$

#### Note

### **Loop Calculator Tips**

A Type I compensation network can be simulated by choosing a Type II compensation (Type II, Type II isolated with a Zener clamp, Type II isolated with inner loop) and setting  $R_{COMP}$  equal to  $R_{FBT}$ . The crossover frequency depends on the value of  $C_{COMP}$ . Set  $C_{HF}$  equal to  $C_{COMP}$ .

www.ti.com Filter Designer

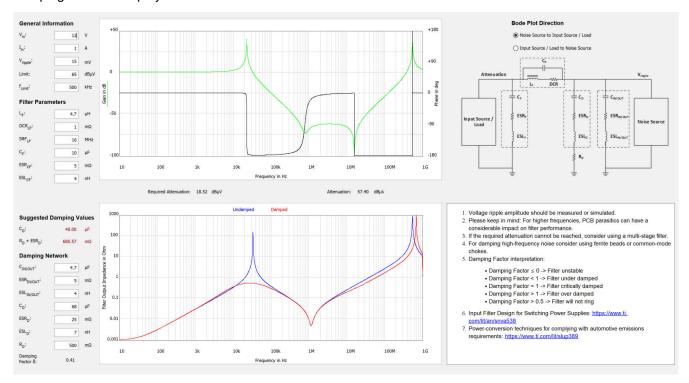

# 13 Filter Designer

The Filter Designer enables the user to design a differential mode filter, such as the input filter for a power supply. The tool shows the Bode plot of the filter transfer function and the damping circuit and helps with finding a desirable damping circuit (see example in Figure 13-1). In addition, the filter impedance with and without the damping circuit is displayed to determine if the filter is stable or not.

Figure 13-1. Filter Designer Window

#### 13.1 Impedances

$$Z_{IN/OUT}(s) = ESR_{IN/OUT} + s \times ESL_{IN/OUT} + \frac{1}{s \times C_{IN/OUT}}$$

(114)

$$Z_{D}(s) = R_{D} + ESR_{D} + s \times ESL_{D} + \frac{1}{s \times C_{D}}$$

$$(115)$$

$$Z_{F}(s) = ESR_{F} + s \times ESL_{F} + \frac{1}{s \times C_{F}}$$

(116)

$$C_{L} = \frac{1}{L_{F}} \times \left(\frac{1}{2 \times \pi \times SRF}\right)^{2} \tag{117}$$

$$Z_{L}(s) = \frac{DCR + s \times L}{s \times C_{L} \times (DCR + s \times L) + 1}$$

$$\tag{118}$$

### 13.2 Transfer Functions

Noise source to input source, load:

$$G_{F}(s) = \frac{Z_{F}(s)}{Z_{F}(s) + Z_{L}(s)}$$

(119)

Input source, load to noise source:

$$G_{D}(s) = \frac{\frac{Z_{D}(s) \times Z_{IN/OUT}(s)}{Z_{D}(s) + Z_{IN/OUT}(s)}}{\frac{Z_{D}(s) \times Z_{IN/OUT}(s)}{Z_{D}(s) + Z_{IN/OUT}(s)} + Z_{L}(s)}$$

(120)

# 13.3 Filter Output Impedance

Undamped:

$$Z_{out, undamped}(s) = \frac{|Z_{L}(s) \times Z_{IN/OUT}(s)|}{|Z_{L}(s) + |Z_{IN/OUT}(s)|}$$

(121)

Damped:

$$Z_{\text{out, damped}}(s) = \begin{vmatrix} Z_{L}(s) \times \frac{Z_{D}(s) \times Z_{IN/OUT}(s)}{Z_{D}(s) + Z_{IN/OUT}(s)} \\ Z_{L}(s) + \frac{Z_{D}(s) \times Z_{IN/OUT}(s)}{Z_{D}(s) + Z_{IN/OUT}(s)} \end{vmatrix}$$

(122)

# 13.4 Damping Factor

$f_{\rm damp}$  is the filter frequency of the filter inductor and the parallel input/output capacitor and damping capacitor network.

$$X_{Cin/out} = \frac{1}{2 \times \pi \times f_{damp} \times C_{IN/OUT}}$$

(123)

$$X_{Cd} = \frac{1}{2 \times \pi \times f_{damp} \times C_D}$$

(124)

Effective impedance at  $f_{\text{damp}}$

$$Z_{eff} = \frac{\sqrt{ESR_{IN/OUT}^{2} + X_{Cin/out}^{2}} \times \sqrt{(R_{D} + ESR_{D})^{2} + X_{Cd}^{2}}}{\sqrt{(R_{D} + ESR_{D} + ESR_{IN/OUT})^{2} + (X_{Cd} + X_{Cin/out})^{2}}}$$

(125)

Effective phase angle at  $f_{\rm damp}$ .

$$\varphi_{eff} = \tan^{-1} \left( \frac{X_{Cin/out}}{ESR_{IN/OUT}} \right) + \tan^{-1} \left( \frac{X_{Cd}}{R_D + ESR_D} \right) - \tan^{-1} \left( \frac{X_{Cin/out} + X_{Cd}}{ESR_{IN/OUT} + R_D + ESR_D} \right)$$

(126)

Effective capacitance:

$$C_{\text{eff}} = \frac{1}{2 \times \pi \times f_{\text{damp}} \times Z_{\text{eff}} \times \sin(\varphi_{\text{eff}})}$$

(127)

Effective ESR:

$$ESR_{eff} = Z_{eff} \times cos(\varphi_{eff})$$

(128)

Damping factor:

$$\delta = 0.5 \times \left( \frac{DCR + ESR_{eff}}{\sqrt{\frac{L_F}{C_{eff}}}} + \frac{\sqrt{\frac{L_F}{C_{eff}}}}{-\frac{V_{in}}{I_{in}}} \right)$$

(129)

www.ti.com Additional Information

### 14 Additional Information

The following list contains references to additional information for various topics in this user's guide.

- 1. Mammano, Robert A.; Kollmann, Robert; Fundamentals of Power Supply Design, Chapter 13: Power-Supply Construction, Texas Instruments, ISBN: 978-0-9985994-0-3 (see Section 4)

- 2. Dinwoodie, L.; Exposing the Inner Behavior of a Quasi-Resonant Flyback Converter, Texas Instruments Power Supply Design Seminar SEM2000, 2012/2013 (see Section 5)

- 3. Keogh, Bernard; Cohen, Isaac; Flyback transformer design considerations for efficiency and EMI, Texas Instruments Power Supply Design Seminar SEM2200, 2016/2017 (see Section 6)

- 4. Dinwoodie, Lisa; Design Review: Isolated 50-Watt Flyback Converter Using the UCC3809 Primary Side Controller and the UC3965 Precision Reference and Error Amplifier (see Section 6)

- 5. Dinwoodie, Lisa; Application Report: UCC38C44 12-V Isolated Bias Supply (see Section 6)

- 6. Betten, John; Power Tips: Calculate an R-C snubber in seven steps (see Section 7)

- 7. Sheehan, R.; Diana, L.; Switch-mode power converter compensation made easy, Texas Instruments Power Supply Design Seminar SEM2200, 2016/2017 (see Section 12.2)

- 8. Ridley, R.; A More Accurate Current-Mode Control Model, Texas Instruments Power Supply Design Seminar SEM1400, 2000 (see Section 12.2)

### 15 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (November 2017) to Revision B (February 2023)                                                                                                                                                                                                                                                       |      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| <ul> <li>Updated the numbering format for tables, figures, and cross-references throughout the document</li> <li>Replaced several figures to represent the new UI. Updated equations for Capacitor Current Sharing Calculator and Loop Calculator. Added new tools, the Load Step Calculator and Filter Designer</li> </ul> |      |  |

| Changes from Revision * (November 2017) to Revision A (February 2018)                                                                                                                                                                                                                                                       | Page |  |

| Changed fourth line of Equation 13                                                                                                                                                                                                                                                                                          | 10   |  |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated