# Using The Manual Reset On Voltage Supervisors to Debounce a Pushbutton Switch

## Michael DeSando

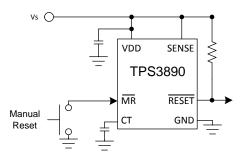

There are many applications that utilize a pushbutton switch to force a system reset. A typical voltage supervisor with a manual reset ( $\overline{MR}$ ) pin is shown in Figure 1. The  $\overline{MR}$  pin is typically connected to a GPIO from a MCU or directly to a pushbutton switch for forcing a reset. Issues arise when the pushbutton switch has parasitic transients as shown in Figure 2 that can cause the output to falsely reset or function improperly.

#### Figure 1. Pushbutton Switch Debounce Circuit Using Manual Reset on TPS3890

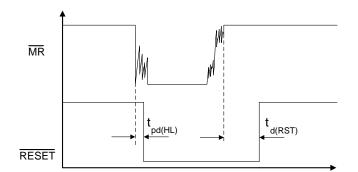

Normally, when a pushbutton switch is pressed or released, the electrical signal is noisy and if the output responds directly to the pushbutton switch, the noise will propagate through directly to the output. Using voltage supervisors that feature the manual reset (MR) pin, the pushbutton switch can be debounced such that the first falling transition on the MR pin caused by pressing the pushbutton switch will cause the output to reset regardless of how much noise there is on the pushbutton switch. The device keeps the output in the reset condition until the pushbutton switch is released long enough so that the MR pin is inactive and thus settled for the duration of the reset delay  $(t_{d(RST)})$ . Once the MR pin is inactive for the reset delay set by the CT capacitor, the device will release the reset back to the inactive state. The timing diagram in Figure 2 shows the benefit of using manual reset to debounce a pushbutton switch.

# Texas Instruments

### Figure 2. Timing Diagram of Manual Reset Debounce

In addition to pushbutton switch debouncing, the  $\overline{\text{MR}}$  pin also includes high frequency noise filtering. Every device that has the manual reset feature has a minimum pulse width for the  $\overline{\text{MR}}$  pin to be triggered. This means if a very fast high frequency pulse arrives on the  $\overline{\text{MR}}$  pin, the signal will be ignored unless the duration of the pulse meets the specification required for the minimum pulse width.

Table 1 notes that the  $\overline{MR}$  pin glitch immunity specification can also be defined as  $\overline{MR}$  pin minimum pulse width which is an inversely related. A pulse that is ignored because it transitions too fast can also be defined as not meeting the minimum pulse width to cause a trigger.

### **Table 1. Alternative Device Recommendations**

| Device                                      | MR Glitch Immunity | MR Pulse Width<br>(Minimum) |

|---------------------------------------------|--------------------|-----------------------------|

| TPS3890                                     | 100 ns             | х                           |

| TPS3895,<br>TPS3896,<br>TPS3897,<br>TPS3898 | 1 us               | 1 ns                        |

| TPS3808                                     | х                  | 1 ns                        |

| TPS3840                                     | Х                  | 300 ns                      |

1

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated