# Technical Article **Design, Optimize and Simulate an Active Filter within Minutes**

Alfred Chong

You are on a quest to design an active filter. You have the specifications of the filter's frequency response, but how do you create a circuit that does just what you want?

If you took the conventional approach, you would need to manipulate the second-order control system equations by consulting multiple filter-response coefficient tables; plot and compare multiple filter responses; select the filter response that best meets your specification; choose a circuit topology and calculate the passive component values by solving complex quadratic equations; and pick standard, graded passive components and an operational amplifier (op amp) that closely match the calculated values. You'll need to repeat component selection and calculations until you achieve the desired performance – a process that could easily take weeks, if not months.

TI's Filter Design Tool streamlines the system design, circuit design and circuit verification process and helps you select a filter circuit that has high chance for first-pass success.

### Designing a robust filter circuit, made easy

Design, optimize and simulate complete multistage active filter solutions within minutes. Launch the tool now.

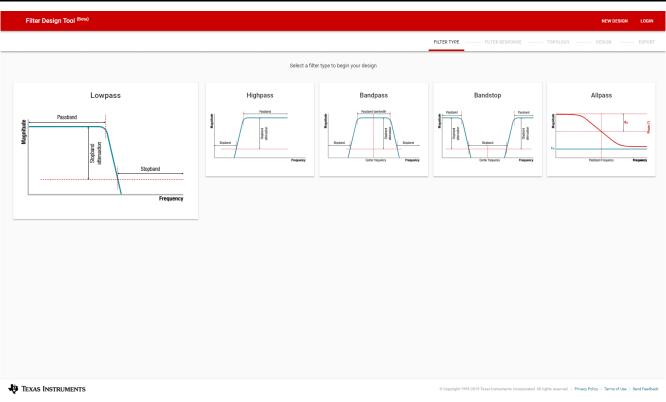

The Filter Type tab in the tool (Figure 1) gives you the option to select low-pass, high-pass, band-pass, band-stop (notch) or all-pass filters.

Figure 1. Filter Type Selection Screen

Click one of the filter types to move forward to the Filter Response screen (Figure 2).

| Filter Design Tool (Beta)                                |                                        |       |               |              |                           | NEW DESIGN LOG       |

|----------------------------------------------------------|----------------------------------------|-------|---------------|--------------|---------------------------|----------------------|

| wpass Filter                                             |                                        |       |               | FILTER T     | YPE FILTER RESPONSE       | TOPOLOGY DESIGN EXPO |

| specification <del>C</del>                               | View                                   |       |               |              |                           |                      |

| assband ^                                                | Magnitude Phase Group Delay Step Respo | nse   |               |              |                           |                      |

| in (Ao)                                                  | 50                                     |       |               |              |                           | Q Show all           |

| dB V/V     quency (Fp)                                   | ( <b>qB</b> )                          |       |               |              |                           |                      |

| 00 Hz *                                                  | -50                                    |       |               |              |                           |                      |

| ple (Rp) dB                                              | -100                                   |       |               |              |                           |                      |

| )<br>Cheby's passband is set at the final rolloff of its | шове<br>-150                           |       |               |              |                           |                      |

| ople. All others' passband are set at -3dB               | -200                                   | 1     |               |              | 10k                       | 100k                 |

| topband ^                                                | Butterworth 7th order                  |       | F             | equency (Hz) |                           |                      |

| ter order                                                | Butterworth /th order                  |       |               |              |                           |                      |

| rquency (Fs)                                             |                                        |       |               | _            |                           |                      |

| 1-10) Hz                                                 | Select a filter response               |       |               |              |                           |                      |

| anuation (Aub)<br>0 dB<br>20-0)                          | View Filter Response                   | Order | No. of Stages | Max Q        | Stopband Attenuation (dB) | Select               |

|                                                          | ✓ Butterworth                          | 7     | 4             | 2.247        | -42.15                    | SELECT >             |

|                                                          |                                        |       | 3             | 5.557        | -45.30                    |                      |

|                                                          | Chebyshev                              | 5     | 3             | 0.007        |                           | SELECT >             |

### Figure 2. Filter Response Screen

As you enter your design specifications on the left, the chart on the right updates the waveform to reflect the characteristics of your selected filter response. You can switch between magnitude, phase, group delay and step response by clicking the button above the chart.

The table beneath the waveform presents the filter responses that meet your design specifications. The first filter response is displayed by default, but you can check or uncheck multiple other filter responses to compare or hide their characteristics and performance.

To advance to the Topology screen (Figure 3), click Select to the right of the filter response you want.

| wpass Filter-7th order Butterworth<br>sband: Ao: 1.000 V/V, Fp: 1 kHz, Rp: 1.000 dB St |                    | b: -40.00 dB   |                           |                     | FILTER TYPE | FILTER RESPONSE | TOPOLOGY DESIGN EXPO                                                                                                                        |

|----------------------------------------------------------------------------------------|--------------------|----------------|---------------------------|---------------------|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| opology         ←           Use same topology for all stages         allen-Key         | View<br>Circuit Ma | sgnitude Phase | Group Delay Step Response | Stage 1 Single      | Pole        |                 |                                                                                                                                             |

|                                                                                        |                    |                | ,                         |                     | Nove        |                 | <ul> <li>First order lowpass filter topology</li> <li>Non-inverting gain</li> <li>Unity gain</li> <li>Use 2 parasitic components</li> </ul> |

|                                                                                        |                    |                |                           |                     | _           |                 |                                                                                                                                             |

|                                                                                        | Stage              | Order          | Topology                  | Gain (V/V)          | Q           | fp (Hz)         | GBW Reqd (Hz)                                                                                                                               |

|                                                                                        | Stage<br>1         | Order<br>1     | Topology<br>Single Pole   | 0ain (V/V)<br>1.000 | Q<br>0.5000 | fp (Hz)<br>1 k  | 08W Reqd (Hz)<br>50 k                                                                                                                       |

|                                                                                        |                    |                |                           |                     |             |                 |                                                                                                                                             |

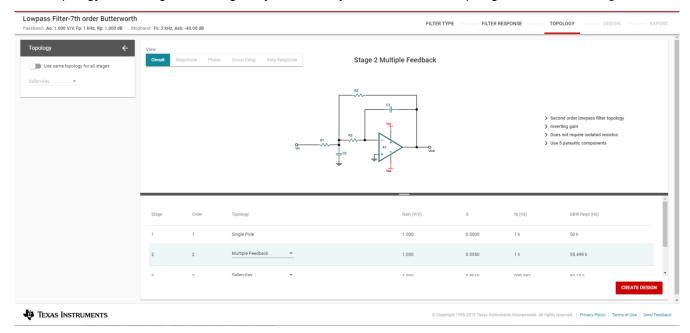

#### Figure 3. Topology Screen

The Filter Design Tool currently supports Sallen-Key and Multiple Feedback topologies for low-, high- and band-pass filters. Band-stop filters only supports Bainter topology because of the challenges in suppressing ringing within the stop-band region for Sallen-Key topology, and the difficulty in meeting the gain and natural frequency for the Multiple Feedback topology.

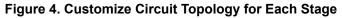

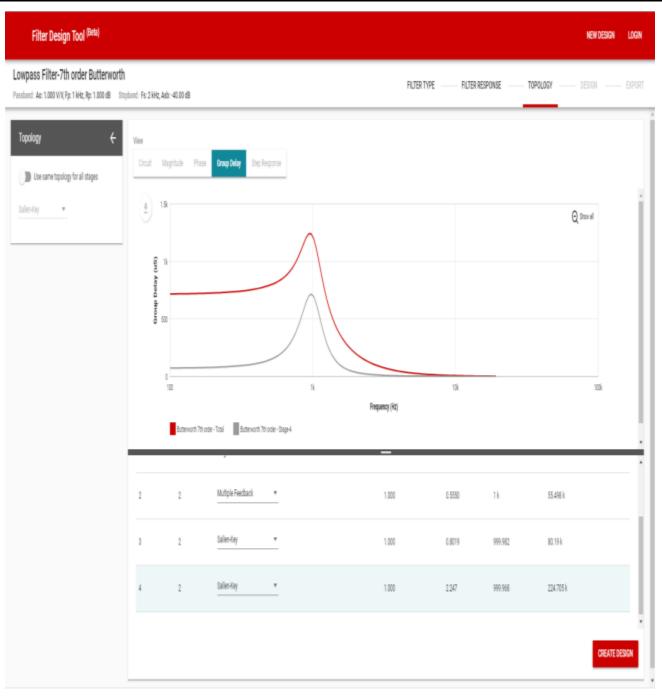

The Filter Design Tool recommends the best topology based on your filter specification and applies this circuit to all stages. You have the option to choose an alternate topology to meet your design priorities. Toggling the "Use same topology for all stages" switch gives you the ability to mix and match topologies, as shown in Figure 4.

You can observe the characteristics of each stage by clicking a particular row in the table, as shown in Figure 5. Advanced users could potentially rearrange the circuit sequence in the exported TINA-TI<sup>™</sup> software schematic to meet their design priorities.

TEXAS INSTRUMENTS

4

© Copyright 1995-2019 Texas Instruments Incorporated, All rights reserved. | Privacy Policy | Terms of Use | Servi Fredback

## TEXAS INSTRUMENTS

© Copyright 1995-2019 Texas Instruments Incorporated, All rights reserved. | Privacy Policy | Terms of Use | Send Feedback

### Figure 5. Evaluate Characteristics of Each Stage

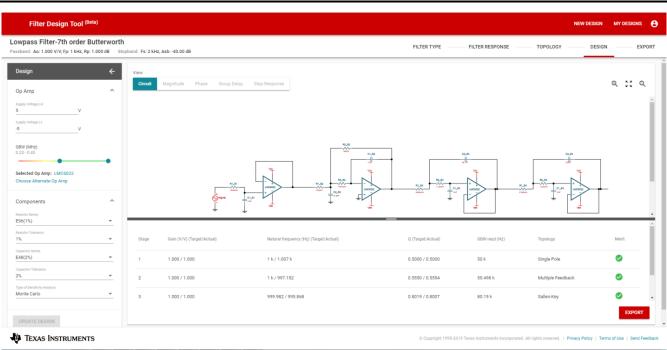

The Design tab (Figure 6) lets you quickly complete three crucial design steps: schematic creation, op amp selection and component tolerance analysis.

Figure 6. Design Screen

The complete schematic with the actual amplifier and passive components is displayed on the Design screen. The tool uses the standard resistor and capacitor values that closely match the calculated values. It is always a design challenge to balance between performance and component cost.

The default power supply is  $\pm 5$  V and can be easily updated on the top left window of the design screen. The gain bandwidth slider range is set to 10 to 200 times the calculated gain bandwidth. The left slider bar is set to the recommended 100 times the calculated gain bandwidth by default. You can lower the gain bandwidth margin by sliding it to the left, to the yellow and red region of the heat map.

It's good practice to perform a simulation if you choose a lower gain-bandwidth amplifier. If you have a specific design priority such as low power, high precision or number of lanes, you can click Select Alternate Op Amp on the design screen. This brings you to a dedicated op-amp selection screen, as shown in Figure 7. On this screen, you will be able to specify your design priorities and pick the best TI op amp for your design. Click Select to pick your op amp or Cancel to return to the Design screen.

| wpass Filter-7th                                | order Butterwo | rth                  |                                                        |                                 |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

|-------------------------------------------------|----------------|----------------------|--------------------------------------------------------|---------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-----------------------|---------------------------------|----------------------|------------------------------------------------------|----------|------------------------------------|---------|---------------------------------------|------------------|---------------------------|

| band: Ao: 1.000 V/V, Fp:                        |                | Stopband: Fs: 2 kHz, | Asb: -40.00 dB                                         |                                 |                                                             |                                                             | FILTER T              | YPE                             | FIL                  | TER RESPO                                            | NSE      | TOPOL                              | DGY     | DESIGN                                |                  | EXPOR                     |

| esign                                           | ÷              | 4 matching o         | ternate Op Amp - LMC60                                 | 22                              |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

| p Amp<br>ipply Voltage (+)<br>ipply Voltage (-) | V              | Select               | Part Number<br>Q. Part Number                          | Number<br>of<br>Channels<br>(#) | Total<br>Supply<br>Voltage<br>(Min)<br>(+5V=5,<br>+/-5V=10) | Total<br>Supply<br>Voltage<br>(Max)<br>(+5V=5,<br>+/-5V=10) | GBW<br>(typ)<br>(MHz) | Slew<br>Rate<br>(Typ)<br>(V/us) | Rail-<br>to-<br>Rail | Vos<br>(Offset<br>Voltage<br>@ 25C)<br>(Max)<br>(mV) | Features | lq per<br>channel<br>(Typ)<br>(mA) | Rating  | Operating<br>Temperature<br>Range (C) | Package<br>Group | Apj<br>pric<br>(US<br>1k) |

| 3 <=                                            | V              |                      | LMC6022 - Low Power CMOS Dual<br>Operational Amplifier | 2                               | 4.750                                                       | 15.50                                                       | 0.3500                | 0.1100                          | In to<br>V-,Out      | 9.000                                                | N/A      | 0.04300                            | Catalog | -40:85                                | SOIC 8           | 0.5                       |

| 2                                               | mV             | SELECT               | LMC6024 - Low Power CMOS<br>Quad Operational Amplifier | 4                               | 4.750                                                       | 15.50                                                       | 0.3500                | 0.1100                          | In to<br>V-,Out      | 9.000                                                | N/A      | 0.04000                            | Catalog | -40:85                                | SOIC 14          | 0.                        |

| 0                                               | MA             | SELECT               | LPC662 - Low Power CMOS Dual<br>Operational Amplifier  | 2                               | 5.000                                                       | 15.00                                                       | 0.3500                | 0.1100                          | In to<br>V-,Out      | 3.000                                                | N/A      | 0.04300                            | Catalog | -40:85                                | SOIC 8           | 1.                        |

| W (MHz)<br>12 - 0.45                            | •              | SELECT               | LPC660 - Low Power CMOS Quad<br>Operational Amplifier  | 4                               | 5.000                                                       | 15.00                                                       | 0.3500                | 0.1100                          | In to<br>V-,Out      | 3.000                                                | N/A      | 0.04000                            | Catalog | -40:85                                | SOIC 14          | 1.3                       |

| Imber of Channels:                              |                |                      |                                                        |                                 |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

| 1 2                                             | 3 4            |                      |                                                        |                                 |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

| ice Model:                                      |                |                      |                                                        |                                 |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

| Yes No                                          |                |                      |                                                        |                                 |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

| ating:                                          |                |                      |                                                        |                                 |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

| Catalog                                         |                |                      |                                                        |                                 |                                                             |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       |                  |                           |

| Automotive                                      |                | Note: Ideal O        | o Amp model will be used for Sim Expo                  | rt for On Amn                   | that doesn't ha                                             | ve a Snice Mor                                              | ol                    |                                 |                      |                                                      |          |                                    |         |                                       | CANC             | FI                        |

| Hi-Rel                                          |                | Note. Ideal of       |                                                        |                                 | and according                                               |                                                             |                       |                                 |                      |                                                      |          |                                    |         |                                       | 0,110            |                           |

TEXAS INSTRUMENTS

### Figure 7. Select Alternate Amplifier

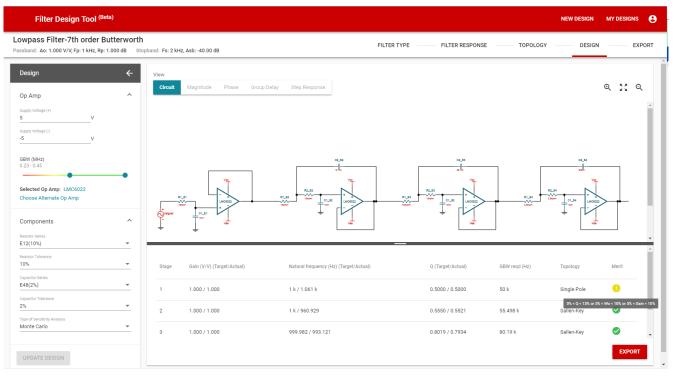

The default resistor and capacitor grades are set to ensure that the deviation between the actual and target values is less than 5% for gain, natural frequency and Q. You can trade off performance and accuracy by choosing a lower-grade capacitor and resistor for reduced costs. The tool will recalculate the actual gain, natural frequency and Q with your new selection. If any of the values deviate more than 5%, the circle of the last column on the table will turn from green to yellow. If the deviation is greater than 10%, the circuit will turn red on the design screen as shown in Figure 8.

The rule of thumb to achieving high accuracy and low cost is to lower the grade for the passive components and still keep the color of the circles green. If you must operate within yellow or red, export the design and run a thorough analysis to ensure that the design still meets your specifications.

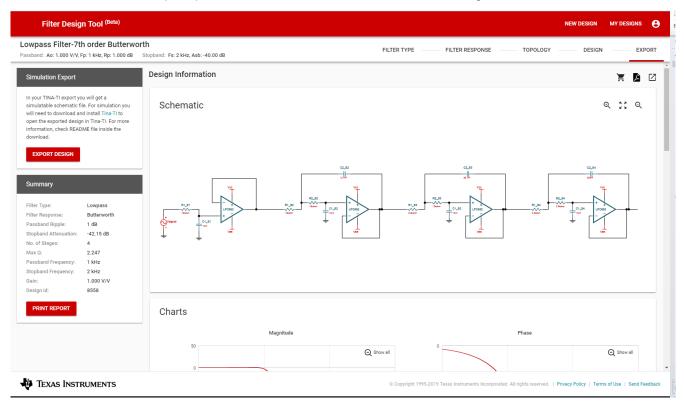

Once you have successfully created and analyzed your design, you can export the design information to a PDF report, and the schematic to TINA-TI software as shown in Figure 9. It's also a good idea to perform a Spice simulation, as not all the op-amp characteristics have been included in the design considerations.

The new Filter Design Tool has a simple user interface powered by intelligent and computation-intensive algorithms. It drastically enhances your experience in designing a robust filter circuit from the first step to the last.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated