# LM311,MF10

Application Note 307 Introducing the MF10: A Versatile Monolithic Active Filter Building Block

Literature Number: JAJA379

## MF10 スイッチト・キャパシタ・フィルタ 汎用:モノリシック・アクティブフィルタを 実現するピルディングブロック

National Semiconductor Application Note 307 Tim Regan August 1982

MF10は、アクティブフィルタを設計する上で独自の新方式を提供します。この最新CMOSデバイスの使用により、リアクタンス部品を必要とせずに、高精度で高次のフィルタ機能を構成することができます。

フィルタの設計方法には、パッシブ(受動)型とアクティブ(能動)型の2通りがあります。パッシブフィルタは、抵抗、コンデンサ、コイルから構成され、精度よりも量産性を重視するアプリケーションで、特定周波数のフィルタリングに使用されます。高周波のアプリケーションの多くは、パッシブフィルタだけを使用します。

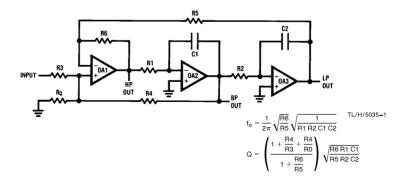

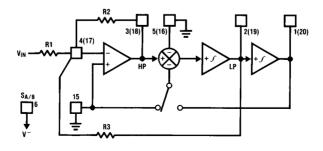

アクティブフィルタは、オペアンプとディスクリート・トランジスタ (主に抵抗とコンデンサ)から構成され、インピーダンスのパッファリングやフィルタのパラメータ調整に使用します。高精度のフィルタでは、共振周波数 ( $f_0$ )、クォリティ・ファクタ(Q)、通過域ゲイン( $H_0$ )の基本的な3つのフィルタのパラメータを個々に調整できることが必要です。一般に、使用アンプ数が多くなる程パラメータの調整が容易になります。最も一般的な2次フィルタ例として、3個のオペアンプで構成するステート・パリアブル(状態変数)型アクティブフィルタがあります(Fig.1参照)

この種のフィルタの大きな欠点として、共振周波数の精度が使用コンデンサの性能に左右される点が挙げられます。このため、大量生産時には、フィルタの調整工程を最小限に抑えるために、高価で許容誤差の小さい低ドリフトのコンデンサが必須となります。さらに、この種のフィルタの構成には、かなりの部品数(各2次セクションでオペアンプ3個、抵抗7個、コンデンサ2個)を使用します。1個のアンプで最適な2次フィルタを実現する上でも、3~5個の抵抗と2個のコンデンサが必要です。

優れたアクティブフィルタを設計する際、以下のデバイス要件を満たす必要があります。

- 1)高精度のコンデンサを排除

- 2)最小の総部品点数

- 3)フィルタ・パラメータが容易に調整可能

- 4)5種類のフィルタ応答特性が全て設計可能

- 5)単純な設計式

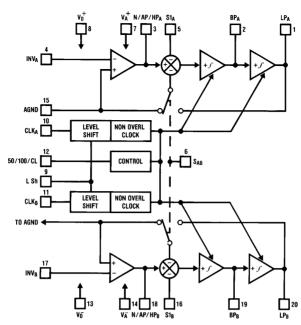

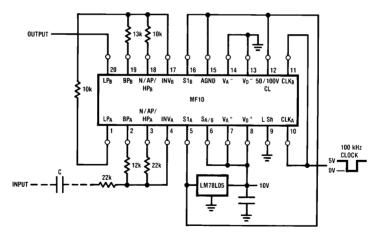

前述の要件は、ナショナルセミコンダクター社がMF10の開発時に定めた設計目標です。近年のデータサンプリング手法の進歩にともない、外付けコンデンサを必要とせずにモノリシック基板上にオペアンプ積分回路を構成することが可能になりました(11ページ、「スイッチト・キャパシタの積分器機能」を参照)、積分器は、フィルタ全体の時定数と共振周波数を設定する上で、フィルタ設計の要となる部分です。MF10の20ピンDIPパッケージ1個には、全ての必要な能動部品とリアクタンス部品が内蔵されており、2つの2次ステート・パリアブル・アクティブフィルタの完全な構成が可能です(Fig. 2参照)、唯一の外付け部品として抵抗が必要ですが、これはフィルタのパラメータを設定するために使用します。

#### MF10 の基本回路

各フィルタ・セクションには、可能な限り汎用性を保持するための出力を備えており、ローパス、パンドパス、ハイパス、オールパス、ノッチ(またはパンドリジェクト)の5種類のフィルタ全てを構成することができます。1パッケージに2つの2次セクションを独立に設けているため、4次応答を得るためのカスケード接続も容易に行えます。また、パタワース、チェビシェフ、ペッセル、コーアなど、"古典的"なフィルタ応答タイプも構成可能です。

Fig. 2に示す加算オペアンプの出力と第1積分器の入力間には、独自の3入力加算段が接続されており、2つの入力と3番目の入力の電圧差を引き出します。2つの(-)入力のうち、1つはフィルタの構成用に信号入力として使用し、もう1つは内部スイッチを介して、ローパス出力またはアナログ・グランドのいずれかに接続されます(選択したフィルタ構成により異なる)。この入力の切換え制御は、MF10の2つのセクションに共通しており、SAB入力端子の電圧レベルで行います。

FIGURE 1. The Universal State Variable 2nd Order Active Filter (note the complexity of design equations and the number of critical external components)

COPS™はナショナル セミコンダクター社の商標です。

FIGURE 2. Block Diagram of the MF10

TL/H/5035-2

つまり、 $S_{AB}$ 端子が $V_D$ \*(正電源)に接続されるとスイッチ接続がローパス出力に切り換わり、 $V_D$ \*(負電源)に接続されるとグランドに切り換わります。アプリケーションによっては、MF10の2つのフィルタ・セクションの片側で加算アンプの両(-)入力を接地し、同時にMF10の 役り半分で(-)入力の1つをローパス出力に接続、残りの(-)入力を接地することが必要になります。この場合、 $S_{AB}$ 制御端子を $V_D$ \*に接続し、ローパス出力への接続は $SI_A$ ( $SI_B$ )端子に外部接続します。

フィルタの共振周波数の制御には、約50%のデューティ・サイクルを持つクロックが必要です。MF10の±両電源動作または単一動作に関わらず、レベルシフト(LSh)制御端子を接地するだけで、TTLまたはCMOSのいずれかのロジック・レベルのクロックに対応できます。

各フィルタの共振周波数は、フィルタのクロックで直接制御します。 各フィルタ部のクロック周波数、中心周波数比は、3レベルの制御端子 (50/100/CL 端子)で設定します。この端子をV\*に接続するとクロック周波数/中心周波数比が50:1になり、中間電位(±両電源のパイアス時にはグランド)に接続すると100:1になります。また、V\*に接続すると、省電力用の電源電流制限回路によるシャットダウン機能が働き、電源電流を70%まで抑制します。

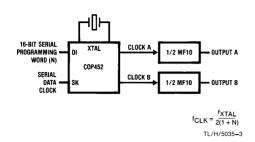

フィルタの中心周波数の精度と安定度は唯一クロックで決まります。 標準の水晶発振器とデジタル・カウタを組み合わせると、特定のフィル タ周波数で非常に安定したクロックが得られます。また、ナショナル セミコンダクター社の最新のCOPS™ファミリ、マイクロコントロー ラ/ペリフェラル・デバイス(COP452 プログラマブル周波数ジェネレータ/カウンタ)を用いると、MF10とのユニークな構成が可能になります(Fig. 3)。この低コストのデバイスは、2 つの独立した50%デューティ・サイクル周波数を生成します。各クロックの出力設定は16 ピットのシリアル・データ・ワード(N)で行うため、MF10では水晶発振子1個で64,000余りの異なるクロック周波数が得られます。

MF10は20kHzの最大中心周波数で使用でき、1MHzの最大クロッ ク周波数の動作が保証されています。中心周波数が10kHzを超える場 合には、50:1のクロック制御を選択する必要があります。100:1また は50:1のクロック周波数/中心周波数比を選択すると、"階段"状の波 形が出力されます。MF10は、連続型フィルタ(RCアクティブフィル タなど)にかなり近い時間領域と周波数領域を持っていますが、この 近似性はサンプリング手法によって実現しています。クロック周波数/ 中心周波数比を設定することで、中心周波数1サイクル当たりのサン プリング数(1回/クロック・サイクル)が決まります。このため、Fig. 4のサンプリングデータ出力波形写真に示すように、100:1のクロック を選択すると、サイクル当たりのサンプリング数が2倍になり、一層 滑らかな出力波形が得られます。オーディオ関連の一般的なアプリ ケーションでは、これらの階段エッジや出力部のクロック周波数成分 は20kHz 以上なので無視できます。ノイズのない"クリーン"な出力 波形を得るには、出力部に単純なパッシブ型RCローパスフィルタを 接続し、MF10のフィルタ機能に影響を与えずに調整用フィルタとし ての機能を持たせます。

FIGURE 3. A Programmable Dual Clock Generator

100:1 50:1 TL/H/5035-4

FIGURE 4. The Sampled-Data Output Waveform

いくつかの動作モード(後の項で説明)では、外付け抵抗比によって クロック周波数/中心周波数比を変更したり、50:1や100:1以外の比率も設定することができます。例えば、複数段のスタガ同調フィルタ などは、抵抗によって各段の中心周波数を個別に設定でき、1クロック周波数だけでフィルタ全体を制御することができます。

MF10の使用時には、サンプリング定理の全てのルールが適用になります。MF10が連続時間系フィルタと同様に機能するためには、最低でも最大入力周波数の2倍のサンプリング・レート(クロック周波数)が必要です。これは、入力信号の高周波成分がクロック周波数に近づくと、低周波フィルタの出力部で信号の折返しが発生し(エイリアシング現象)、有効な通過帯域信号との区別がつかなくなるためです。エイリアシング切象の最善の防止策として、入力信号に帯域制限をかけてエイリアシングが起きる周波数を減衰することを推奨します。通常のアプリケーションの場合、クロック周波数は問題の通過域よりも十分に高いため、エイリアシングが問題になることはありません。更に高いクロック周波数を必要とする場合には、外付け抵抗比により、100:1以上のクロック周波数中心周波数比の動作モードを選択することができます。クロック周波数を高くすると、同様にエイリアシングが起きる周波数も高くなります。クロック周波数/中心周波数と内間波数と同様にエイリアシングが起きる周波数も高くなります。クロック周波数/中心周波数比を上げると、各出力のDCオフセット電圧が高くなる制限があります。

#### フィルタの基本構成

MF10の2次セクションは6種類の基本構成(動作モード)に設定可能で、各種のフィルタ応答が得られます。全ての動作モードでは、外付けコンデンサは不要です。2、3の抵抗比を設定するだけの簡単な設計手法により、適過域ゲインとQを任意に設定したり、適切な共振周波数を得るためのクロックを生成することができます。1パッケージ、あるいは複数パッケージ内の2セクションをカスケード接続して高次のフィルタを構成する場合は、各2次セクションをそれぞれの中心周波数、Qおよびゲインを基準にして1種のモジュールとして扱うことができます。この2次セクションの独立性は、パターワース、チェビシェできます。この2次セクションの独立性は、パターワース、チェビシェ

フなど様々な応答特性を実現する上で重要です。

以下は、全動作モードに共通するデザインヒントの要約です。

- 1)MF10の最大電源電圧は±7V(単一電源動作では+14V)最小パイアス電源電圧は8V。

- 2)出力部の最大電圧振幅は両電源電圧の1 V以内(代表値)。

- 3)内部オペアンプのソース電流は3mA、シンク電流は1.5mA。最小 抵抗値を選択する際に重要です。

- 4)最大クロック周波数は1.5MHz(代表値)

- 5)適切なフィルタ応答を得るには、MF10で各段のf<sub>6</sub>×Q積を設定します。5kHzの中心周波数では、f<sub>6</sub>×Q積を300kHzまで高く設定できます(Qは150以下)、例えば、3kHzのパンドパスフィルタの場合は、Qは1セクションだけで100になります。中心周波数が20kHz以下の場合は、設定可能なf<sub>6</sub>×Q積は200kHzに制限されます。1つの2次セクションを用いる10kHzのパンドパス設計では、Qが20を超えることはありません。

- 6)特定周波数における中心周波数とクロック周波数の部分的整合の許容範囲は±0.2%(代表値)、中心周波数の温度ドリフトは(クロック周波数のドリフトを除き)、50:1のスイッチングでは±10ppm/(代表値)、100:1では±100ppm/(代表値)になります。

- 7)Qの部分精度は、± 500ppm/ の温度係数で± 2%(代表値)です。

- 8)各動作モードの頃に示す回路のダイナミック特性の計算式は重要です。この計算式から回路(の関数として各出力の電圧振幅を求めます。()が高いパンドパスフィルタでは、中心周波数でローパス出力応答がかなり高いピークを生成します。

- 9)MF10の2つの2次セクションは、電源電圧、アナログ・グランド、 クロック周波数/中心周波数比の設定、3入力の加算段の内部ス イッチ設定を除き、それぞれ独立しています。

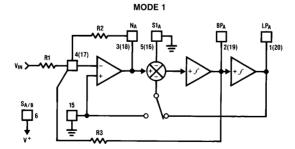

以降のフィルタ構成の説明では、フィルタの中心周波数を $f_o$ 、通過域 ゲインを $H_o$ 、複素極ペアのクォリティ・ファクタをQ で表します。Q は $f_o$ BW に等しく、BW はパンドパス出力で測定された - 3dB 帯域幅 を表します。 MODE 1A: 非反転型バンドパス、反転型バンドパス、ローパス出力 MODE 1: ノッチ、バンドパス、ローパス出力

最小の外付け部品で構成(2個の抵抗のみ) 〇が低いローパスとバ ンドパスのアプリケーションに適しています。非反転型バンドパス出 力は最小の位相フィルタ設計に必要です。

設計式

$$\begin{split} f_0 &= \frac{f_{CLK}}{100} \sharp \, \hbar c \, l \, \sharp \frac{f_{CLK}}{50} \\ Q &= \frac{R3}{R2} \\ H_{OLP} &= -1 \\ H_{OBP_1} &= -\frac{R3}{R2} \end{split}$$

H<sub>OBP2</sub> = 1(非反転)

回路のダイナミック特性

H<sub>OBPI</sub> = - Q(したがって、低いQを推奨します)

$$H_{OLP(peak)} = Q \times H_{OLP}$$

外付け抵抗を更に1個接続することで、MODE 1Aに比べて優れた 出力ダイナミック特性を備えた、非常に高いQを持つパンドパス設計 を実現します。ノッチ出力の特長として、ノッチ周波数の上下でゲイ ンが等しくなります。

設計式

$$f_{o} = \frac{f_{CLK}}{100}$$

または $\frac{f_{CLK}}{50}$

$$f_{notch} = f_{o}$$

$$Q = \frac{R3}{R2}$$

$$H_{OLP} = -\frac{R2}{R1}$$

$$H_{OBP} = -\frac{R3}{R1}$$

$$H_{ON} = -\frac{R2}{R1} \left( f \longrightarrow 0 \text{かつ} f \longrightarrow \frac{f_{CLK}}{2} \right)$$

回路のダイナミック特性

$H_{OBP} = H_{OLP} \times Q = H_{ON} \times Q$

$H_{OLP(peak)}$  = Q ×  $H_{OLP}$ (LP出力のDC ゲインが高過ぎると、高いQ に よりローパス出力部でクリッピングが生じ、バンドパス出力部でゲイ ンが非直線的になったり、歪みを起こす原因になります。

#### MODE 1A

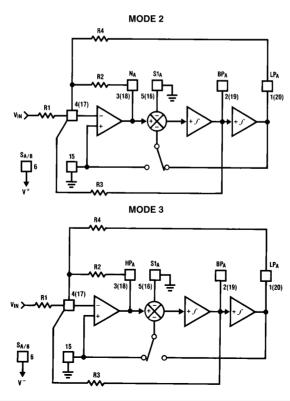

MODE 2:  $/ ッチ(f_o f_o f_o h_o)$  バンドパス、ローパス出力

100:1または50:1以上のクロック周波数/中心周波数比の設定が可能な構成です。必要な複素ゼロ周波数( $f_{noich}$ )が複素極周波数( $f_o$ )よりも低いために、ノッチ出力はエリピティック型ハイパスフィルタの設計に適しています。

授計式

$$f_{O} = \frac{f_{CLK}}{100} \sqrt{1 + \frac{R2}{R4}} \pm \pi \text{Liz} \frac{f_{CLK}}{50} \sqrt{1 + \frac{R2}{R4}}$$

$f_{O} = \frac{f_{CLK}}{100} \pm \pi \text{Liz} \frac{f_{CLK}}{50}$   $Q = \frac{\sqrt{R_2/R_4 + 1}}{R_2/R_3}$   $Q = \frac{\sqrt{R_2/R_4 + 1}}{R_2/R_3}$   $Q = \frac{-\frac{R2}{R1}}{1 + \frac{R2}{R4}}$   $Q = \frac{-\frac{R2}{R1}}{1 + \frac{R2}{R4}}$   $Q = \frac{-\frac{R3}{R1}}{1 + \frac{R2}{R4}}$   $Q = \frac{-\frac{R3}{R1}}{1 + \frac{R2}{R4}}$   $Q = \frac{-\frac{R2}{R1}}{1 + \frac{R2}{R4}}$

回路のダイナミック特性

$$H_{OBP} = Q\sqrt{H_{OLP} \times H_{ON_2}} = Q\sqrt{H_{ON_1} \times H_{ON_2}}$$

MODE 3:ハイパス、バンドパス、ローパス出力

4個の外付け抵抗だけで構成する"古典的"なステート・パリアプル型フィルタです(Fig.1の回路参照)。100:1または50:1以上のクロック周波数/中心周波数比を外部設定できる、最も汎用性を備えた動作モードです。この回路は1クロックで制御する複数段のチェビシェフ型フィルタに適しています。

設計式

$$\begin{split} f_0 &= \frac{f_{CLK}}{100} \sqrt{\frac{R2}{R4}} \ \sharp \ \hbar c \ l \ \sharp \frac{f_{CLK}}{50} \sqrt{\frac{R2}{R4}} \\ Q &= \sqrt{\frac{R2}{R4}} \times \frac{R3}{R2} \\ H_{OHP} &= -\frac{R2}{R1} \end{split}$$

$$H_{OBP} = -\frac{R3}{R1}$$

$$H_{OLP} = -\frac{R4}{R1}$$

回路のダイナミック特性

$$H_{OHP} = H_{OLP} \left( \frac{R2}{R4} \right)$$

$H_{OLP (peak)} = Q \times H_{OLP}$  $H_{OBP} = Q \sqrt{H_{OHP} \times H_{OLP}}$

$H_{OHP (peak)} = Q \times H_{OHP}$

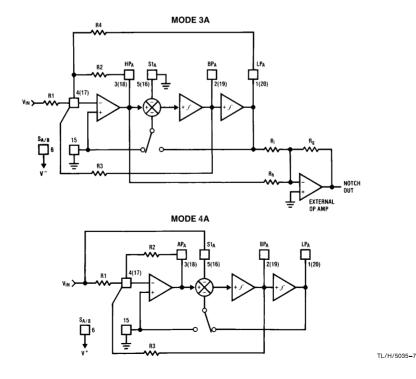

MODE 3A: ハイパス、バンドパス、ローパス、ノッチ出力

外付けオペアンプを介してハイパス出力とローパス出力を加算すると、MODE3の回路でノッチ出力を構成することができます。加算抵抗R<sub>h</sub>とR<sub>t</sub>比により、中心周波数とは独立してノッチ周波数を調整することができます。エリピティック型フィルタの設計では、各段でf<sub>0</sub>の複素極ペアと f<sub>noch</sub>の複素ゼロ・ペアを組み合わせ、これらの周波数をそれぞれ任意の応答タイプに容易に調整することができます。MF10を数段カスケード接続する場合は、最終出力段でのみ外付けオペアンプが必要です。各中間段の加算接合部は、内部オペアンプの反転入力にすることができます。

$$\begin{aligned} &H_{ON_{I}}(f\longrightarrow 0) = \frac{R_{g}}{R_{I}} \times H_{OLP} \\ &H_{ON_{h}}\left(f \longrightarrow \frac{f_{CLK}}{2}\right) = \frac{R_{g}}{R_{h}} \times H_{OHP} \end{aligned}$$

MODE 4:オールパス、バンドパス、ローパス出力

$S1_A(S1_B)$ 端子を信号入力として使用すると、オールパス機能が得られます。オールパスでは出力の周波数が一定の遅延時間のもと、直線的な位相変化が得られます。この構成における制約として、オールパス出力ゲインが1になります。

設計式

$$\begin{split} f_o &= \frac{f_{CLK}}{100} \sqrt{\frac{R2}{R4}} \, \text{\#} \, \text{Lis} \frac{f_{CLK}}{50} \sqrt{\frac{R2}{R4}} \\ Q &= \sqrt{\frac{R2}{R4}} \times \frac{R3}{R2} \\ f_{notch} &= \frac{f_{CLK}}{100} \sqrt{\frac{R_h}{R_l}} \, \text{\#} \, \text{Lis} \frac{f_{CLK}}{50} \sqrt{\frac{R_h}{R_l}} \\ H_{OHP} &= -\frac{R2}{R1} \\ H_{OLP} &= -\frac{R4}{R1} \\ H_{OBP} &= -\frac{R3}{R1} \\ H_{ON} \left( f = f_o \right) &= \left| Q \left( \frac{R_g}{R_l} \, H_{OLP} - \frac{R_g}{R_h} \, H_{OHP} \right) \right| \end{split}$$

設計式

$$\begin{split} f_0 &= \frac{f_{CLK}}{100} \text{ $\pm k$ ti} \frac{f_{CLK}}{50} \\ f_z &= \left( \frac{R3}{R2} \right) + \left( \frac{R3}{R2} \right) = f_0 \\ Q &= \frac{R3}{R2} \\ Q_z &= \left( \frac{R3}{R2} \right) + \left( \frac{R3}{R1} \right) + \left( \frac{R3}{R1} \right) + \left( \frac{R3}{R1} \right) + \left( \frac{R3}{R2} \right) + \left( \frac{R3}{R2} \right) + \left( \frac{R3}{R1} \right) + \left( \frac{R3}{R2} \right) + \left($$

$H_{OBP} = H_{OLP} \times Q = (H_{OAP} + 1)Q$

6

http://www.national.com

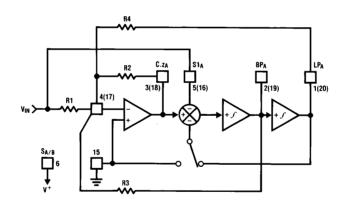

MODE 5: 複素ゼロ(C.z)、バンドパス、ローパス出力

この MODE の特長として、複素ゼロ(C.z)出力の周波数振幅を 更に一定状態に保つ点で、MODE 4に比べて改善されています。極ペ アとゼロ・ペアの周波数は抵抗で調整可能です。

設計式

$$f_0 = \frac{f_{CLK}}{100}\sqrt{1+\frac{R2}{R4}} \text{ $\sharp$ $t$-id} \ \frac{f_{CLK}}{50}\sqrt{1+\frac{R2}{R4}}$$

$$f_z = \frac{f_{CLK}}{100} \sqrt{1 - \frac{R1}{R4}} \ \pm \hbar c l \pm \frac{f_{CLK}}{50} \sqrt{1 - \frac{R1}{R4}}$$

$$Q = \frac{R3}{R2} \sqrt{1 + \frac{R2}{R4}}$$

$$Q_z = \frac{R3}{R1}\sqrt{1 - \frac{R1}{R4}}$$

$$H_{O(C.z)} f \longrightarrow 0 = \frac{R2(R4 - R1)}{R1(R2 + R4)}$$

$$H_{O(C.z)} f \longrightarrow \frac{f_{CLK}}{2} = \frac{R2}{R1}$$

$$H_{OBP} = \frac{R3}{R2} \left( 1 + \frac{R2}{R1} \right)$$

$$H_{OLP} = \frac{R4}{R1} \left( \frac{R2 + R1}{R2 + R4} \right)$$

MODE 6A: 単一極、ハイパス、ローパス出力

内部積分器1個だけを使用し、カスケード接続の奇数次フィルタ応答を生成するのに適しています。他の2次MF10フィルタ・セクションの共振周波数のトラッキングは、実極をクロック調整して行います。コーナ周波数は抵抗で調整可能です。

設計式

$$f_{C}(カットオフ周波数) = \frac{f_{CLK}}{100} \left(\frac{R2}{R2}\right)$$

または $\frac{f_{CLK}}{50} \left(\frac{R2}{R2}\right)$

$$H_{OLP} = -\frac{R3}{R1}$$

$$H_{OHP} = -\frac{R2}{R1}$$

#### MODE 5

#### MODE 6A

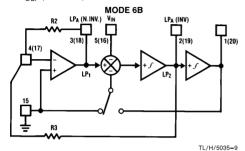

MODE 6B: 単一極ローパス(反転、非反転)出力

このモードでは、積分器 1 個、また反転型アンプとして入力オペアンプを使用して非反転型ローパス出力を得ます。このモードも奇数次ローパスフィルタの設計に適しています。

#### 設計式

$$f_c$$

(カットオフ周波数) =  $\frac{f_{CLK}}{100}$   $\left(\frac{R2}{R3}\right)$ または $\frac{f_{CLK}}{50}$   $\left(\frac{R2}{R3}\right)$  H<sub>OLP</sub> (反転出力) =  $-\frac{R3}{R3}$

HOLP (非反転出力)=+1

#### アプリケーション例

単一電源動作では、MF10のいくつかの端子を1/2電源電圧( $V_{\rm CC}/2$ )にパイアスすることが重要です。単一電源の設計例として、Mode 1を用いた 1kHz の4 次パタワース・ローパスフィルタ(ロールオフ率: 24dB/octave、または80dB/decade)の構成図を示します( $F_{\rm IB}$ .5 参照) この構成例では、アナログ・グランド端子(ピン15)加算入力端子 $S1_{\rm A}$ と $S1_{\rm BC}$ (ピン15)加算入の全て

を  $V_{\rm CC}/2$  にパイアスしています。対称的な $\pm$  両電源動作の場合、これらの端子は接地します。入力信号を $V_{\rm CC}/2$ にパイアスしない場合は、入力カップリング・コンデンサが必要です。2段のパタワース応答出力では、両段とも同じコーナ周波数を持ち、このためクロックは両サイドで共通です。図中の抵抗は約5%の許容範囲値を持ち、フィルタ全体のゲインを調整したり、1段目 (A サイド)のQ を 0.504、2段目 (B サイド)のQ を 1.306 に設定して平坦な通過帯域応答を得るために使用します。

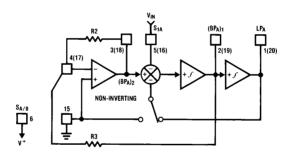

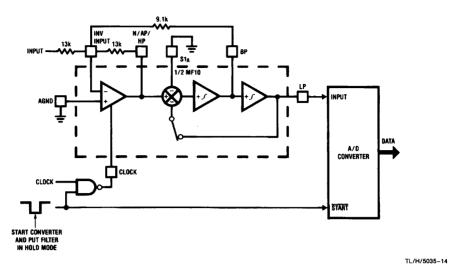

Fig. 6に、MF10独自の利点を活かしたスイッチト・キャパシタ・フィルタの設計例を示します。この例のデータ・アクイジション・システムでは、MF10は帯域制限とエイリアシング防止用の入力フィルタ機能。また大きな振幅を持つ高周波入力信号を得るためのサンブル/ホールド機能の2つの機能を備えています。供給クロックがゲート〇FFされると、スイッチ・キャパシタの積分器により最終サンプリング電圧値をホールドします。ホールド・タイム時の出力電圧のドループ・レートは約0.1mV/msです。

Fig. 7に、フィルタ以外のMF10のアプリケーション例を示します。この回路では、MF10とLM311コンパレータを組み合わせて共振器を構成し、AGC回路を用いずに安定した振幅の正弦(サイン)波出力と余弦(コサイン)波出力を生成します。MF10はパンドパスフィルタ(Q=10)として動作し、ステップ入力が変化すると共振周波数でリンギングが生じます。このリンギング信号はLM311に取り込まれ、ここでパンドパスフィルタに対して方形波入力信号を生成し、再度発振を起こします。パンドパス出力は、50%のデューティ・サイクルの方形波基本周波数をフィルタに通したものです。90度の位相シフトを持つ同じ振幅の信号は、MF10内の2番目の積分器を介してローパス出力に出力されます。発振周波数の設定はフィルタの中心周波数で行い、調整はクロックと50:1/100:1制御端子で行います。出力振幅の設定は方形波入力のピーク・ツー・ピーク振幅で行いますが、この回路ではLM311出力部のパック・ツー・パック接続クランプ・ダイオードで設定します。

FIGURE 5. Only 6 resistors required for this 4th order, 1 kHz Butterworth lowpass filter. This example also illustrates single-supply biasing.

FIGURE 6. An MF10 as an Input Filter and Sample/Hold

51k

51k

V<sub>D</sub> SIN (2x \frac{k\_{LK}}{100} t)

N/AP/

SIA=

172 MF10

V<sub>D</sub> COS (2x \frac{k\_{LK}}{100} t)

V<sub>D</sub> COS (2x \frac{k\_{LK}}{100} t)

1NG 14s

1NG 14s

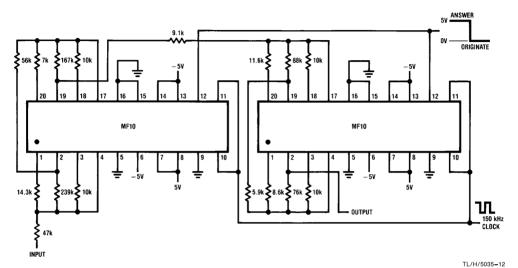

FIGURE 7. Generating Quadrature Sine Waves from a T<sup>2</sup>L Clock

最後に、Fig. 8 に完全な300ボー、全二重のモデム・フィルタの構成 図を示します。この図から分かるように、MF10を用いて簡単にフィル プフィルタ方式よりも更にコンパクトにでき、精度を重要視する場合 タを構成することができます。このフィルタは8次の1dBリップル・ チェビシェフ型パンドパスフィルタで、1170Hz の呼出しフィルタと 2125Hzの応答フィルタの両機能を備えています。応答・呼出し動作の 制御は50/100/CL入力端子のロジック・レベルで行うため、必要とする クロック周波数はひとつだけです。フィルタ全体のゲインは 22dB で す。

プリント回路基板上でこのフィルタを構成する場合は、RCアクティ にはコスト面で更に効率的です。省スペースの点で更に魅力的な構成 方法として、ハイブリッド回路を用いる方法があります。2つのMF10 のダイにフィルム抵抗を接続すると、フィルタ全体を1個のパッケー ジに収納することができ、入力、出力、電源用に7本の外部接続だけで 済みます。

FIGURE 8. A Complete Full-Duplex 300 Baud Modem Filter

10

#### スイッチト・キャパシタの積分器機能

MF10の最大の特長は、外付けコンデンサが不要であり、しかも高周 波フィルタを実現できる点です。2個の非反転積分器の時定数はクロッ クで制御します。MF10を最大限に動作させるためには、この制御方法 の理解が不可欠です。

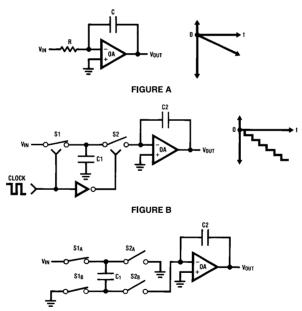

この制御方法を容易に理解するために、反転積分器(Fig. A)を説明 し、その入力抵抗をスイッチ2個とコンデンサ(Fig. B)に置き換える 方法を説明します。Fig. A では、帰還コンデンサCを流れる電流は V<sub>IN</sub>/R に等しく、また回路の時定数はRCとなります。この時定数の精 度は、完全に異なる2個のディスクリート部品の絶対精度によって決 まります。Fig. B では、スイッチ S1 と S2 がクロックにより交互にク ローズします。スイッチS1がクローズすると(S2がオープン)、コン デンサC1はV<sub>M</sub>まで充電されます。クロック半周期分で、C1(OC1) の電荷量が $V_{IN} \times C1$  に等しくなります。クロック状態が遷移すると、 S1がオープンしてS2がクローズします。このクロック半周期間にC1 の電荷が帰還コンデンサ C2 に送られます。

入力に送られる電荷量は、V<sub>IN</sub> × C1 となります。電気電流とは一定時 間に伝導路を流れる電荷量(1A = 1クーロン/秒)であることから、C2 を介して出力に流れる回路電流は、次式から求めることができます。

$$I = \frac{\Delta Q}{\Delta t} = \frac{V_{IN}C1}{T} = V_{IN}C1 f_{CLK}$$

ここで、T = クロック周期

V<sub>IN</sub>と(-)入力間の等価抵抗は、次式から得られます。

$$R = \frac{V_{IN}}{1} = \frac{1}{C1 f_{CLK}}$$

すなわち、Fig. B のクロック入力時に S1、S2、C1 は Fig. A の抵抗 と同様に動作し、この結果、クロックで調整可能な時定数を次式から 求めることができます。

$$\tau = \frac{\text{C2}}{\text{C1 f}_{\text{CLK}}}$$

スイッチト・キャパシタの積分器の時定数は、2個のコンデンサ値の 比で決まり、同一ダイ上に配置されていれば、制御が非常に容易にな ります。この結果、デバイス単位で、また温度変化に対してフィルタの 共振周波数を正確に制御できます。

MF10で実際に使用している積分器は非反転型で、スイッチング方 式が多少複雑になります(Fig. C参照)。この回路では、先ずSlaとSla 1クロック周期間に入力電圧 $V_{IN}$ からオペアンプの加算接合点(-) が両方クローズしてC1を $V_{IN}$ まで充電します。続いて、 $S2_{\Delta}$ と $S2_{R}$ が クローズし、コンデンサの極性が逆状態でC1を加算接合点に接続し、 非反転動作になります。 $V_{\rm IN}$ の極性が( + )ならば、C1 から C2 に充電 が行われる度に VOLT は正方向に進みます。

FIGURE C. The Non-Inverting Integrator Used in the MF10

#### 生命維持装置への使用について

弊社の製品はナショナル セミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用 することはできません。

- れることを意図されたもの、または(b)生命を維持あるいは支持す るものをいい、ラベルにより表示される使用法に従って適切に使用 された場合に、これの不具合が使用者に身体的障害を与えると予想 されるものをいいます。

- 1. 生命維持用の装置またはシステムとは(a)体内に外科的に使用さ 2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべ ての部品をいい、これの不具合が生命維持用の装置またはシステム の不具合の原因となりそれらの安全性や機能に影響を及ぼすことが 予想されるものをいいます。

## ナショナル セミコンダクター ジャパン株式会社

本 社/〒135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300

http://www.nsjk.co.jp/

製品に関するお問い合わせはカスタマ・レスポンス・センタのフリーダイヤルまでご連絡ください。

0120-666-116

この紙は再生紙を使用しています

本資料に掲載されているすべての回路の使用に起因する第三者の特許権その他の権利侵害に関して、弊社ではその責を負いません。また掲載内容 は予告無く変更されることがありますのでご了承下さい。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上