TPD2S703-Q1

JAJSD28A - MARCH 2017 - REVISED MAY 2017

# TPD2S703-Q1 車載用、USB 2チャネル・データ・ライン、バッテリ短絡 保護、V<sub>BUS</sub>短絡保護、IEC ESD保護付き

## 1 特長

- AEC-Q100認定済み

- -40℃~+125℃の動作温度範囲

- VD+、VD-上でのバッテリ短絡保護(最高18V)およびVBUS短絡保護

- VD+、VD-のESD性能

- 接触放電±8kV (IEC 61000-4-2およびISO 10605 330pF、330Ω)

- エアギャップ放電±15kV (IEC 61000-4-2および ISO 10605 330pF、330Ω)

- 高速データ・スイッチ(1GHz帯域幅)

- 5V電源のみで動作

- OVPスレッショルドを変更可能

- 短い過電圧応答時間(標準値200ns)

- サーマル・シャットダウン機能

- 入力イネーブルおよびフォルト出力信号を内蔵

- フロースルー配線によるデータ整合性

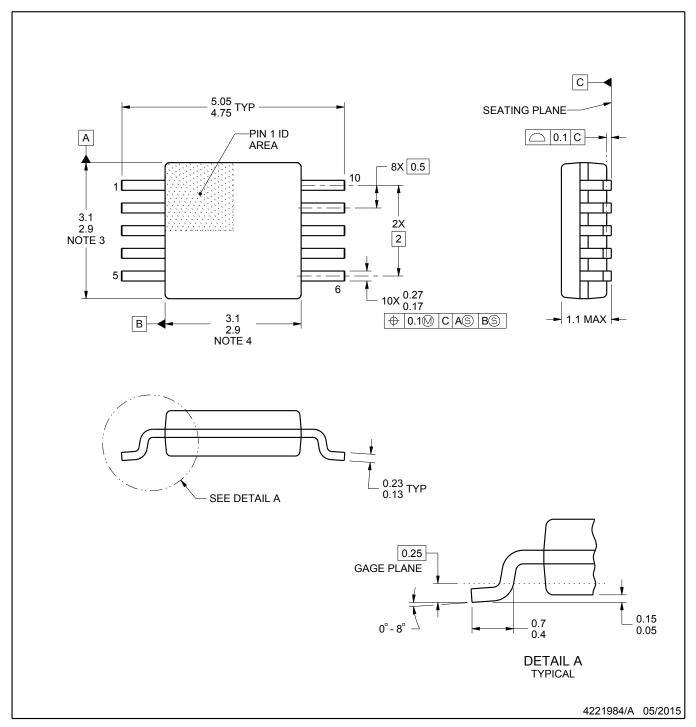

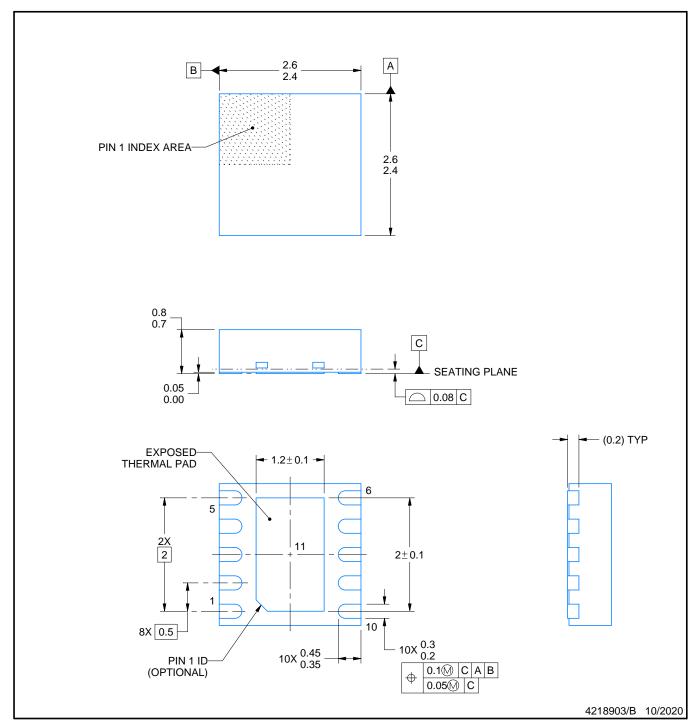

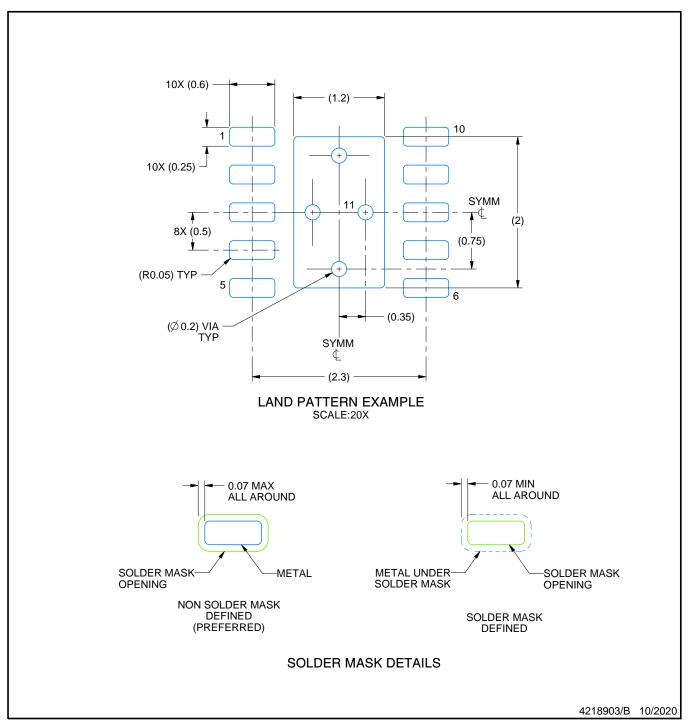

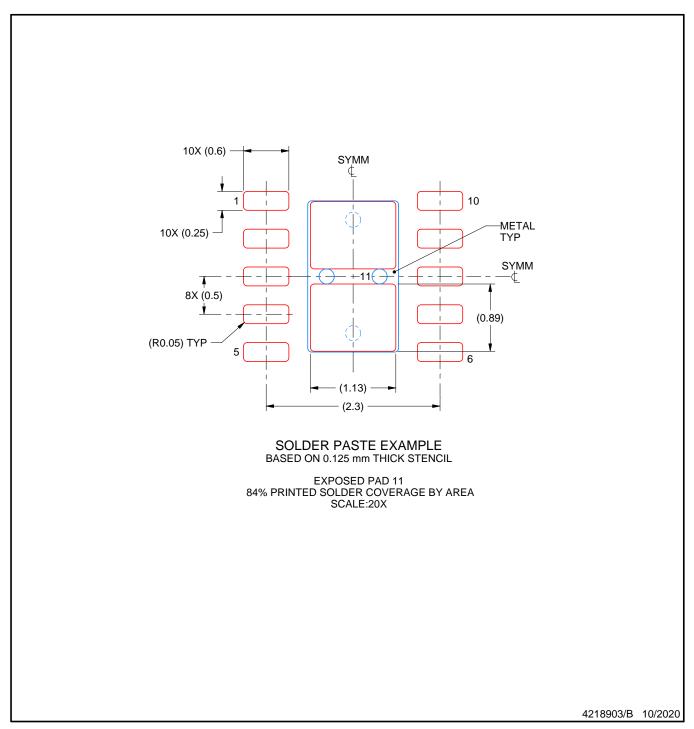

- 10ピンのVSSOPパッケージ(3mmx3mm)

- 10ピンのWSONパッケージ(2.5mm×2.5mm)

# 2 アプリケーション

## • 最終製品

- ヘッド・ユニット

- リアシート用エンターテイメント

- テレマティクス

- USBハブ

- ナビゲーション・モジュール

- メディア・インターフェイス

- インターフェイス

- USB 2.0

- USB 3.0

# 3 概要

TPD2S703-Q1は、USB 2.0などの車載用高速インターフェイス向けに設計された、2チャネルのデータ・ライン、バッテリ短絡保護、V<sub>BUS</sub>短絡保護、およびIEC61000-4-2 ESD保護デバイスです。TPD2S703-Q1には2つのデータ・ラインnFETスイッチが内蔵されており、クラス最高の帯域幅により信号の劣化を最小限に抑えて安全なデータ通信を保証しながら、同時にVD+およびVD-ピンの過電圧状況からも内部のシステム回路を保護します。デバイスはこれらのピンで、最高18V DCまでの過電圧保護に対応できます。これによって、データ・ラインが車のバッテリやUSB V<sub>BUS</sub>レールに短絡した場合にも十分な保護が得られます。過電圧保護回路は業界でも最も信頼性の高いバッテリ短絡絶縁を行い、200nsでデータ・スイッチをシャットオフして、危険な電圧や電流スパイクから上流の回路を保護します。

さらに、TPD2S703-Q1は5Vの単一電源のみで動作するため、電源ツリーのサイズとコストを最適化できます。OVPスレッショルドおよびクランプ回路は抵抗分圧回路により設定できるため、あらゆるトランシーバについて、単純かつコスト効果の高い方法でシステム保護を最適化できます。また、TPD2S703-Q1にはFLTピンが搭載され、デバイスが過電圧状況を検出したことを通知します。過電圧状況が解消されると、このピンは自動的にリセットされます。

さらに、TPD2S703-Q1ではシステム・レベルのIEC 61000-4-2およびISO 10605 ESDクランプがVD+および VD-ピンに統合されているため、アプリケーションで外付けの高電圧、低容量TVSクランプ回路を使用する必要がありません。

#### 製品情報<sup>(1)</sup>

| 型番          | パッケージ      | 本体サイズ(公称)     |

|-------------|------------|---------------|

| TPD2S703-Q1 | VSSOP (10) | 3.00mm×3.00mm |

|             | WSON (10)  | 2.50mm×2.50mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

## バッテリ短絡保護およびIEC ESD保護機能を持つUSB 2.0ポート

# 目次

| 1 | 特長1                                             |    | 8.2 Functional Block Diagram   | 15 |

|---|-------------------------------------------------|----|--------------------------------|----|

| 2 | アプリケーション1                                       |    | 8.3 Feature Description        | 16 |

| 3 | 概要1                                             |    | 8.4 Device Functional Modes    | 17 |

| 4 | 改訂履歴2                                           | 9  | Application and Implementation | 18 |

| 5 | Pin Configuration and Functions                 |    | 9.1 Application Information    | 18 |

| 6 | Specifications4                                 |    | 9.2 Typical Application        | 18 |

| U | 6.1 Absolute Maximum Ratings                    | 10 | Power Supply Recommendations   | 21 |

|   | 6.2 ESD Ratings—AEC Specification               |    | 10.1 V <sub>PWR</sub> Path     | 21 |

|   | 6.3 ESD Ratings—AEC Specification               |    | 10.2 V <sub>REF</sub> Pin      |    |

|   | 6.4 ESD Ratings—ISO Specification               | 11 | Layout                         |    |

|   | 6.5 Recommended Operating Conditions            |    | 11.1 Layout Guidelines         |    |

|   | 6.6 Thermal Information                         |    | 11.2 Layout Example            |    |

|   | 6.7 Electrical Characteristics 6                | 12 | デバイスおよびドキュメントのサポート             |    |

|   | 6.8 Power Supply and Supply Current Consumption |    | 12.1 ドキュメントのサポート               |    |

|   | Chracteristics                                  |    | 12.2 ドキュメントの更新通知を受け取る方法        |    |

|   | 6.9 Timing Requirements 8                       |    | 12.3 コミュニティ・リソース               |    |

|   | 6.10 Typical Characteristics                    |    | 12.4 商標                        |    |

| 7 | Parameter Measurement Information 14            |    | 12.5 静電気放電に関する注意事項             | 23 |

| 8 | Detailed Description 15                         |    | 12.6 Glossary                  | 23 |

| - | 8.1 Overview                                    | 13 | メカニカル、パッケージ、および注文情報            |    |

|   |                                                 |    |                                |    |

# 4 改訂履歴

| 20 | <b>017</b> 年 <b>3</b> 月発行のものから更新                                                 | Page |

|----|----------------------------------------------------------------------------------|------|

| •  | Updated description from enable to FLT in Recommended Operating Conditions table | !    |

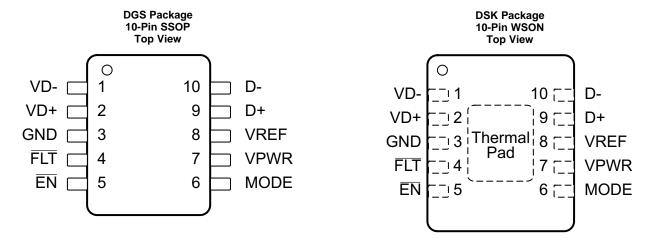

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN |      |        | DECORPORTOR                                                                                                                                                                         |

|-----|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME | TYPE   | DESCRIPTION                                                                                                                                                                         |

| 1   | VD-  | I/O    | High voltage D– USB data line, connect to USB connector D+, D– IEC61000-4-2 ESD protection                                                                                          |

| 2   | VD+  | I/O    | High voltage D+ USB data line, connect to USB connector D+, D- IEC61000-4-2 ESD protection                                                                                          |

| 3   | GND  | Ground | Ground pin for internal circuits and IEC ESD clamps                                                                                                                                 |

| 4   | FLT  | 0      | Open-drain fault pin. See 表 1                                                                                                                                                       |

| 5   | EN   | I      | Enable active-low input. Drive $\overline{\text{EN}}$ low to enable the switches. Drive $\overline{\text{EN}}$ high to disable the switches. See $\frac{1}{8}$ 1 for mode selection |

| 6   | MODE | I      | Selects between device modes. See the <i>Detailed Description</i> section. Acts as LDO reference voltage for mode 1                                                                 |

| 7   | VPWR | 1      | 5-V DC supply input for internal circuits. Connect to internal power rail on PCB                                                                                                    |

| 8   | VREF | I/O    | Pin to set OVP threshold. See the <i>Detailed Description</i> section for instructions on how to set OVP threshold                                                                  |

| 9   | D+   | I/O    | I/O protected low voltage D+ USB data line, connects to transceiver                                                                                                                 |

| 10  | D-   | I/O    | Protected low voltage D– USB data line, connects to transceiver                                                                                                                     |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                      |                                                  | MIN  | MAX             | UNIT |

|----------------------|--------------------------------------------------|------|-----------------|------|

| $V_{PWR}$            | 5-V DC supply voltage for internal circuitry     | -0.3 | 7.7             | V    |

| $V_{REF}$            | Pin to set OVP threshold                         | -0.3 | 6               | V    |

| VD+,<br>VD–          | Voltage range from connector-side USB data lines | -0.3 | 18              | V    |

| D+, D-               | Voltage range for internal USB data lines        | -0.3 | $V_{REF} + 0.3$ | V    |

| $V_{MODE}$           | Voltage on MODE pin                              | -0.3 | 7.7             | V    |

| $V_{\overline{FLT}}$ | Voltage on FLT pin                               | -0.3 | 7.7             | V    |

| VEN                  | Voltage on enable pin                            | -0.3 | 7.7             | V    |

| T <sub>A</sub>       | Operating free air temperature <sup>(3)</sup>    | -40  | 125             | °C   |

| T <sub>STG</sub>     | Storage temperature                              | -65  | 150             | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings—AEC Specification

|                         |                         |                                                         |                          | VALUE | UNIT |

|-------------------------|-------------------------|---------------------------------------------------------|--------------------------|-------|------|

| V <sub>(ESD)</sub> Elec |                         | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | All pins                 | ±2000 |      |

|                         | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011            | All pins besides corners | ±500  | V    |

|                         |                         |                                                         | Corner pins              | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 ESD Ratings—IEC Specification

|                    |                         |                                 |                              | VALUE  | UNIT |

|--------------------|-------------------------|---------------------------------|------------------------------|--------|------|

| V <sub>(ESD)</sub> |                         | IEC 61000-4-2 contact discharge | VD+, VD- pins (1)            | ±8000  | V    |

|                    | Electrostatic discharge | IEC 61000-4-2 air-gap discharge | VD+, VD- pins <sup>(1)</sup> | ±15000 | V    |

<sup>(1)</sup> See 23 for details on system level ESD testing setup.

# 6.4 ESD Ratings—ISO Specification

|                                     |                         |                                                                          |               | VALUE  | UNIT |

|-------------------------------------|-------------------------|--------------------------------------------------------------------------|---------------|--------|------|

|                                     |                         | ISO 10605 (330 pF, 330 $\Omega$ ) contact discharge (10 strikes)         | VD+, VD- pins | ±8000  |      |

|                                     |                         | ISO 10605 (330 pF, 330 $\Omega$ ) air-gap discharge (10 strikes)         | VD+, VD- pins | ±15000 |      |

|                                     |                         | ISO 10605 (150 pF, 330 $\Omega$ ) contact discharge (10 strikes)         | VD+, VD- pins | ±8000  |      |

| V <sub>ESD</sub> <sup>(1)</sup> Ele | Electrostatic discharge | ISO 10605 (150 pF, 330 $\Omega$ ) air-gap discharge (10 strikes)         | VD+, VD- pins | ±15000 | V    |

|                                     |                         | ISO 10605 (330 pF, 2 k $\Omega$ ) contact discharge (10 stikes) $^{(2)}$ | VD+, VD- pins | ±8000  |      |

|                                     |                         | ISO 10605 (330 pF, 2 kΩ) air-gap discharge (10 VD+, VD– pins strikes)    | VD+, VD- pins | ±15000 |      |

|                                     |                         | ISO 10605 (150 pF, 2 k $\Omega$ ) air-gap discharge (10 discharges)      | VD+, VD- pins | ±25000 |      |

<sup>(1)</sup> See 23 for details on system level ESD testing setup.

<sup>2)</sup> The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

<sup>(3)</sup> Thermal limits and power dissipation limits must be observed.

<sup>(2)</sup> VREF > 3 V.

# 6.5 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                                                                                  |                                                                                                               | MIN  | TYP | MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| V <sub>PWR</sub>    | 5-V DC supply voltage                                                            | for internal circuitry                                                                                        | 4.5  |     | 7   | V    |

| V <sub>REF</sub>    | Mode 0. Voltage range                                                            | for V <sub>REF</sub> pin (for setting OVP threshold)                                                          | 3    |     | 3.6 | V    |

| $V_{REF}$           | Mode 1. Voltage range                                                            | for V <sub>REF</sub> pin (for setting OVP threshold)                                                          | 0.63 |     | 3.8 | V    |

| VD+, VD-            | Voltage range from co                                                            | nnector-side USB data lines                                                                                   | 0    |     | 3.6 | V    |

| D+, D-              | Voltage range for inter                                                          | nal USB data lines                                                                                            | 0    |     | 3.6 | V    |

| VEN                 | Voltage range for enab                                                           | ole                                                                                                           | 0    |     | 7   | V    |

| V <sub>FLT</sub>    | Voltage range for FLT                                                            |                                                                                                               | 0    |     | 7   | V    |

| I <sub>FLT</sub>    | Current into open drain                                                          | FLT pin FET                                                                                                   | 0    |     | 3   | mA   |

| C <sub>VPWR</sub>   | V <sub>PWR</sub> capacitance <sup>(1)</sup>                                      | V <sub>PWR</sub> pin                                                                                          | 1    | 10  |     | μF   |

| C <sub>VREF</sub>   | V <sub>REF</sub> capacitance                                                     | V <sub>REF</sub> pin                                                                                          | 0.3  | 1   | 3   | μF   |

| C <sub>MODE</sub>   | Allowed parasitic capacitance on mode pin from PCB and mode 1 external resistors |                                                                                                               |      |     | 20  | pF   |

| R <sub>MODE_0</sub> | Resistance to GND to                                                             | Resistance to GND to set to mode 0                                                                            |      |     | 2.6 | kΩ   |

| R <sub>MODE_1</sub> | Resistance to GND to $R_{\text{BOT}}$ )                                          | Resistance to GND to set to mode 1 (calculate parallel combination of $R_{\text{TOP}}$ and $R_{\text{BOT}}$ ) |      |     |     | kΩ   |

<sup>(1)</sup> For recommended values for capacitors and resistors, the typical values assume a component placed on the board near the pin. Minimum and maximum values listed are inclusive of manufacturing tolerances, voltage derating, board capacitance, and temperature variation. The effective value presented should be within the minimum and maximums listed in the table.

## 6.6 Thermal Information

|                         |                                              | TPD2        |            |      |

|-------------------------|----------------------------------------------|-------------|------------|------|

|                         | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP) | DSK (WSON) | UNIT |

|                         |                                              | 10 PINS     | 10 PINS    |      |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 167.3       | 61.5       | °C/W |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 56.9        | 51.3       | °C/W |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 87.6        | 34         | °C/W |

| ΨЈТ                     | Junction-to-top characterization parameter   | 7.7         | 1.3        | °C/W |

| ΨЈВ                     | Junction-to-board characterization parameter | 86.2        | 34.3       | °C/W |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | N/A         | 7.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.7 Electrical Characteristics**

| MODE 1 ADJUS              | PARAMETER                                                                |                   | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MIN                           | TYP                                      | MAX                        | UNIT       |

|---------------------------|--------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------|----------------------------|------------|

| V <sub>MODE_CMP</sub>     | Mode 1 V <sub>REF</sub> feedback regulator voltage                       | V <sub>MODE</sub> | Standard mode 1 set-up. $\overline{EN} = 0$ V. Once $V_{REF} = 3.3$ V, measure voltage on mode pin                                                                                                                                                                                                                                                                                                                                                                                        | 0.47                          | 0.5                                      | 0.53                       | V          |

| I <sub>MODE_LEAK</sub>    | Mode pin mode 1 leakage current                                          | I <sub>MODE</sub> | Standard mode 1. Remove RTOP and RBOT. Power up device and wait until start-up time has passed. Then force 0.53 V on the MODE pin and measure current into pin                                                                                                                                                                                                                                                                                                                            |                               | 50                                       | 200                        | nA         |

| V <sub>REF_ACCURACY</sub> | V <sub>REF</sub> accuracy                                                | V <sub>REF</sub>  | Informative, test parameters below; accuracy with R <sub>TOP</sub> and R <sub>BOT</sub> as ±1% resistors                                                                                                                                                                                                                                                                                                                                                                                  | -8%                           |                                          | 8%                         |            |

| V <sub>REF_3.3V</sub>     | Mode 1 VREF set to 3.3 V                                                 | V <sub>REF</sub>  | Standard mode 1 set-up. $R_{TOP}=140~k\Omega\pm1\%,$ $R_{BOT}=24.9~k\Omega\pm1\%.~ \overline{EN}=0.$ Measure value of $V_{REF}$ once it settles                                                                                                                                                                                                                                                                                                                                           | 3.04                          | 3.31                                     | 3.58                       | V          |

| V <sub>REF_0.66V</sub>    | Mode 1 V <sub>REF</sub> set to 0.66 V                                    | V <sub>REF</sub>  | Standard mode 1 set-up. $R_{TOP} = 47.5 \text{ k}\Omega \pm 1\%$ , $R_{BOT} = 150 \text{ k}\Omega \pm 1\%$ . EN = 0. Measure value of $V_{REF}$ once it settles                                                                                                                                                                                                                                                                                                                           | 0.6                           | 0.66                                     | 0.72                       | V          |

| V <sub>REF_3.8V</sub>     | Mode 1 V <sub>REF</sub> set to 3.8 V                                     | V <sub>REF</sub>  | Standard mode 1 set-up. $R_{TOP}=165~k\Omega\pm1\%,$ $R_{BOT}=24.9~k\Omega\pm1\%.~ \overline{EN}=0.$ Measure value of $V_{REF}$ once it settles                                                                                                                                                                                                                                                                                                                                           | 3.5                           | 3.81                                     | 4.12                       | ٧          |

| EN, FLT PINS              |                                                                          | 1.                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                                          | -                          |            |

| $V_{IH}$                  | High-level input voltage                                                 | EN                | Mode 0. Connect VPWR = 5 V; $V_{REF}$ = 3.3 V; $VD+$ = 3.3 V; Set $VIH(\overline{EN})$ = 0 V; Sweep VIH from 0 V to 1.4 V; Measure when D+ drops low (less than or equal to 5% of 3.3 V) from 3.3 V                                                                                                                                                                                                                                                                                       | 1.2                           |                                          |                            | V          |

| VIH                       | Low-level input voltage                                                  | LIN               | Mode 0. Connect VPWR = 5 V; $V_{REF}$ = 3.3 V; $VD+$ = 3.3 V. Set $VIH(\overline{EN})$ = 3.3 V; Sweep VIH from 3.3 V to 0.5 V; Measure when D+ rise to 95% of 3.3 V from 0 V                                                                                                                                                                                                                                                                                                              |                               |                                          | 0.8                        | V          |

| I <sub>IL</sub>           | Input leakage current                                                    | ĒN                | Mode 0. VPWR = 5 V; $V_{REF}$ = 3.3 V; VI (EN) = 3.3 V; Measure current into EN pin                                                                                                                                                                                                                                                                                                                                                                                                       |                               |                                          | 1                          | μΑ         |

| V <sub>OL</sub>           | Low-level output voltage                                                 | FLT               | Mode 0. Drive the TPS2S703-Q1 in OVP to assert $\overline{\text{FLT}}$ pin. Source $I_{QL} = 1$ mA into $\overline{\text{FLT}}$ pin and measure voltage on $\overline{\text{FLT}}$ pin when asserted                                                                                                                                                                                                                                                                                      |                               |                                          | 0.4                        | V          |

| T <sub>SD_RISING</sub>    | The rising over-temperature protection shutdown threshold                |                   | VPWR = 5 V, ENZ = 0 V, T <sub>A</sub> stepped up until FLTZ is asserted                                                                                                                                                                                                                                                                                                                                                                                                                   | 140                           | 150                                      | 165                        | °C         |

| T <sub>SD_FALLING</sub>   | The falling over-temperature protection shutdown threshold               |                   | VPWR = 5 V, ENZ = 0 V, $T_A$ stepped down from $T_{SD\_RISING}$ until FLTZ is cleared                                                                                                                                                                                                                                                                                                                                                                                                     | 125                           | 138                                      | 150                        | °C         |

| T <sub>SD_HYST</sub>      | The over-temperature protection shutdown threshold hysteresis            |                   | T <sub>SD_RISING</sub> - T <sub>SD_FALLING</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                            | 12                                       | 15                         | $^{\circ}$ |

| OVP CIRCUIT—\             | /D±                                                                      |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                                          |                            |            |

| V <sub>OVP_RISING</sub>   | Input overvoltage protection threshold, $V_{\text{REF}} > 3.6 \text{ V}$ | VD±               | Mode 1. Set $V_{PWR}=5$ V; $\overline{EN}=0$ V; $R_{TOP}=165$ k $\Omega$ , $R_{BOT}=24.9$ k $\Omega$ . Connect D± to 40- $\Omega$ load. Increase VD+ or VD– from 4.1 V to 4.9 V. Measure the value at which FLTZ is asserted                                                                                                                                                                                                                                                              | 4.3                           | 4.5                                      | 4.7                        | V          |

| Vovp_rising               | Input overvoltage protection threshold                                   | VD±               | Mode 1. Set $V_{PWR}=5$ V; $\overline{EN}=0$ V; $R_{TOP}=140$ k $\Omega$ , $R_{BOT}=24.9$ k $\Omega$ . Increase VD+ or VD– from 3.6 V to 4.6 V. Measure the value at which FLTZ is asserted. Repeat for $R_{TOP}=39$ k $\Omega$ , $R_{BOT}=150$ k $\Omega$ . Increase VD+ or VD– from 0.6 V to 0.9 V. Measure the value at which FLTZ is asserted. See the resultant values meet the equation, and make sure to observe data switches turnoff. Also check for mode 0 when $V_{REF}=3.3$ V | 1.19<br>×<br>V <sub>REF</sub> | 1.25<br>×<br>V <sub>REF</sub>            | 1.31 ×<br>V <sub>REF</sub> | V          |

| V <sub>HYS_OVP</sub>      | Hysteresis on OVP                                                        | VD±               | Difference between rising and falling OVP thresholds on VD±                                                                                                                                                                                                                                                                                                                                                                                                                               |                               | 25                                       |                            | mV         |

| V <sub>OVP_</sub> FALLING | Input overvoltage protection threshold                                   | VD±               | After collecting each rising OVP threshold, lower the VD± voltage until you see FLT deassert. This gives the falling OVP threshold. Use this value to calculate V <sub>HYS_OVP</sub>                                                                                                                                                                                                                                                                                                      |                               | VOV<br>P_RI<br>SING<br>-<br>VHYS<br>_OVP |                            | V          |

| I <sub>VD_LEAK_0</sub> v  | Leakage current on VD± during normal operation                           | VD±               | Standard mode 0 or mode 1. Set VD± = 0 V. D± = floating. Measure current flowing into VD±                                                                                                                                                                                                                                                                                                                                                                                                 | -0.1                          |                                          | 0.1                        | μA         |

# **Electrical Characteristics (continued)**

|                                 | PARAMETER                                         |     | TEST CONDITIONS                                                                                                                                                                                                                                  | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|---------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>VD_LEAK_3.6V</sub>       | Leakage current on VD± during normal operation    | VD± | Standard mode 0 or mode 1. Set VD± = 3.6 V. D± = floating. Measure current flowing into VD±                                                                                                                                                      |      | 2.5  | 4    | μΑ   |

| V <sub>OVP_3.3V</sub>           | Input overvoltage threshold for VREF = 3.3 V      | VD± | Standard mode 1. $R_{TOP}$ = 140 k $\Omega$ ± 1%, $R_{BOT}$ = 24.9 k $\Omega$ ± 1%. Connect D± to 40- $\Omega$ load. Measure the value at which FLTZ is asserted                                                                                 | 3.61 | 4.14 | 4.67 | V    |

| V <sub>OVP_0.66V</sub>          | Input overvoltage threshold for VREF = 0.66 V     | VD± | Standard mode 1. $R_{TOP}=47.5~k\Omega\pm1\%,~R_{BOT}=150~k\Omega\pm1\%.$ Connect D± to $40$ - $\Omega$ load. Measure the value at which FLTZ is asserted                                                                                        | 0.72 | 0.83 | 0.94 | V    |

| SHORT-TO-BATTER                 | RY                                                |     |                                                                                                                                                                                                                                                  |      |      |      |      |

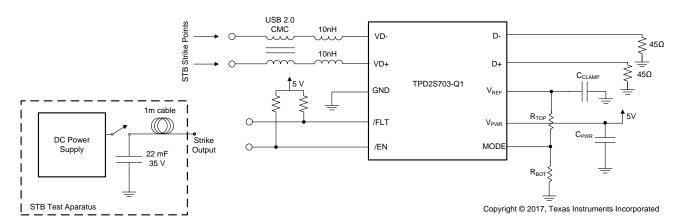

| V <sub>DATA_STB</sub>           | Data line hotplug short-to-<br>battery tolerance  | V±  | Charge battery-equivalent capacitor to test voltage then discharge to pin under test through a 1 meter, 18-ga wire. (See ☒ 23 application information for more details)                                                                          |      |      | 18   | V    |

| V <sub>CLAMP_STB_DP/M_3V3</sub> | Data line system side clamping voltage during STB | D±  | Test both D+ and D- FETs. Test D+ and D- independently. Short VD+ and VD- to 18 V via hotplug to a battery-equivalent capacitor with a 1 meter, 18-ga wire. V <sub>REF</sub> = 3.3 V, V <sub>PWR</sub> = 5 V. Test in standard mode 0 and mode 1 |      | 5.5  | 6    | V    |

| V <sub>CLAMP_STB_DP/M_0V6</sub> | Data line system side clamping voltage during STB | D±  | Test both D+ and D- FETs. Short VD+ and VD- to 18 V via hotplug to a battery-equivalent capacitor with a 1 meter, 18-ga wire. V <sub>REF</sub> = 0.63 V, V <sub>PWR</sub> = 5 V. Test in standard mode 0 and mode 1                              |      | 3.2  | 3.5  | V    |

| DATA LINE SWITCH                | HES - VD+ to D+ or VD- to D-                      |     |                                                                                                                                                                                                                                                  |      |      |      |      |

| R <sub>ON</sub>                 | On resistance                                     |     | Mode 0 or 1. Set V <sub>PWR</sub> = 5 V; V <sub>REF</sub> = 3.3 V; $\overline{\text{EN}}$ = 0 V; Measure resistance between D+ and VD+ or D- and VD-, voltage between 0 and 0.4 V                                                                |      | 4    | 6.5  | Ω    |

| R <sub>ON(Flat)</sub>           | On resistance flatness                            |     | Mode 0 or 1. Set V <sub>PWR</sub> = 5 V; V <sub>REF</sub> = 3.3 V; $\overline{\text{EN}}$ = 0 V; Measure resistance between D+ and VD+ or D- and VD-, sweep voltage between 0 and 0.4 V. Take difference of resistance at 0.4-V and 0-V VD± bias |      |      | 1    | Ω    |

| BW <sub>ON</sub>                | On bandwidth (-3-dB)                              |     | Mode 0 or 1. Set $V_{PWR} = 5 \text{ V}$ ; $V_{REF} = 3.3 \text{ V}$ ; $\overline{EN} = 0 \text{ V}$ ; Measure S21 bandwidth from D+ to VD+ or D- to VD- with voltage swing = 400 mVpp, Vcm = 0.2 V                                              |      | 960  |      | MHz  |

# 6.8 Power Supply and Supply Current Consumption Chracteristics

over operating free-air temperature range (unless otherwise noted)

|                                      | PARAMETER                                      | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                       | MIN | TYP  | MAX | UNIT |

|--------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| V <sub>UVLO_RISING_</sub><br>VPWR    | V <sub>PWR</sub> rising UVLO threshold         | Use standard mode 0 set-up. Set $\overline{\text{EN}}$ = 0 V, load D+ to 45 $\Omega$ , VD+ = 3.3 V. Set V <sub>PWR</sub> = 3.5 V, and step up V <sub>PWR</sub> until 90% of VD+ appears on D+                                                                                                                                                         | 3.7 | 3.95 | 4.2 | V    |

| V <sub>UVLO_HYST_V</sub><br>PWR      | VPWR UVLO hysteresis                           | Use standard mode 0 set up. Set $\overline{\text{EN}}$ = 0 V, load D+ to 45 $\Omega$ , VD+ = 3.3 V. Set V <sub>PWR</sub> = 4.3 V, and step down V <sub>PWR</sub> until D+ falls to 10% of VD+. This gives V <sub>UVLO_FALLING_VPWR</sub> . V <sub>UVLO_RISING_VPWR</sub> - V <sub>UVLO_FALLING_VPWR</sub> = V <sub>UVLO_HYST_VPWR</sub> for this unit | 250 | 300  | 400 | mV   |

| V <sub>UVLO_RISING_</sub><br>VREF    | VREF rising UVLO threshold in mode 0           | Use standard mode 0 set up. Set $\overline{\text{EN}}$ = 0V, load D+ to 45 $\Omega$ , VD+ = 3.3 V. Set VREF = 2.5 V, and step up VREF until 90% of VD+ appears on D+                                                                                                                                                                                  | 2.6 | 2.7  | 2.9 | V    |

| V <sub>UVLO_HYST_</sub> V<br>REF     | VREF UVLO hysteresis                           | Use standard mode 0 set up. Set $\overline{\text{EN}}$ = 0 V, load D+ to 45 $\Omega$ , VD+ = 3.3 V. Set VREF = 3 V, and step down VREF until D+ falls to 10% of VD+. This gives Vuvlo_Falling_vref. Vuvlo_Rising_vref or this unit                                                                                                                    | 75  | 125  | 200 | mV   |

| I <sub>VPWR_DISABLE</sub><br>D_MODE0 | V <sub>PWR</sub> disabled current consumption  | Use standard mode 0. $\overline{\text{EN}}$ = 5 V . Measure current into $V_{\text{PWR}}$                                                                                                                                                                                                                                                             |     |      | 110 | μΑ   |

| I <sub>VPWR_DISABLE</sub><br>D_MODE1 | V <sub>PWR</sub> disabled current consumption  | Use standard mode 1. $\overline{\text{EN}}$ = 5 V. Measure current into $V_{\text{PWR}}$                                                                                                                                                                                                                                                              |     |      | 110 | μA   |

| I <sub>VREF_DISABLE</sub>            | VREF disabled current consumption mode 0       | Use standard mode 0. $\overline{\text{EN}}$ = 5 V. Measure current into VREF                                                                                                                                                                                                                                                                          |     |      | 10  | μA   |

| I <sub>VPWR_MODE0</sub>              | V <sub>PWR</sub> pperating current consumption | Use standard mode 0. $\overline{\text{EN}}$ = 0 V. Measure current into $V_{\text{PWR}}$                                                                                                                                                                                                                                                              |     |      | 250 | μΑ   |

| I <sub>VPWR_MODE1</sub>              | V <sub>PWR</sub> operating current consumption | Use standard mode 1. $\overline{\text{EN}}$ = 0 V. Measure current into $V_{\text{PWR}}$                                                                                                                                                                                                                                                              |     |      | 350 | μA   |

| I <sub>VREF</sub>                    | VREF operating current consumption mode 0      | Use standard mode 0. $\overline{\text{EN}}$ = 0 V. Measure current into $V_{\text{REF}}$                                                                                                                                                                                                                                                              |     | 12   | 20  | μΑ   |

| I <sub>CHG_VREF</sub>                | VREF fast charge current                       | Standard mode 1. 0.1 $\mu$ F < $C_{VREF}$ < 3 $\mu$ F. Set-up for charging to 3.3 V. Use a high voltage capacitor that does not derate capacitance up the 3.3 V. Measure slope to calculate the current when $C_{VREF}$ cap is being charged. Test to check this OPEN LOOP method                                                                     |     | 22   |     | mA   |

| I <sub>D_OFF_LEAK_S</sub><br>TB      |                                                | Mode 0. Measured flowing into D+ or D– supply, $V_{PWR} = 0$ V, VD+ or VD– = 18 V, $\overline{EN} = 0$ V, $V_{REF} = 0$ V, D± = 0 V                                                                                                                                                                                                                   | -1  |      | 1   | μA   |

| I <sub>D_ON_LEAK_ST</sub><br>B       |                                                | Mode 0. Measured flowing into D+ or D- supply, $V_{PWR} = 5$ V, VD+ or VD- = 18 V, $\overline{EN} = 0$ V, $V_{REF} = 3.3$ V, D± = 0 V                                                                                                                                                                                                                 | -1  |      | 1   |      |

| I <sub>VD_OFF_LEAK_</sub><br>STB     |                                                | Mode 0. Measured flowing out of $\overline{VD}$ + or $\overline{VD}$ - supply, $\overline{V_{PWR}} = 0$ V, $\overline{VD}$ + or $\overline{VD}$ - = 18 V, $\overline{EN}$ = 0 V, $\overline{V_{REF}}$ = 0 V, $\overline{D\pm}$ = 0 V                                                                                                                  |     |      | 120 | μA   |

| I <sub>VD_ON_LEAK_</sub> S<br>TB     |                                                | Mode 0. Measured flowing out of VD+ or VD- supply, $V_{PWR}$ = 5 V, VD+ or VD- = 18 V, $\overline{EN}$ = 0 V, $V_{REF}$ = 3.3 V, D± = 0 V                                                                                                                                                                                                             |     |      | 120 | μA   |

| I <sub>VPWR_TO_VRE</sub><br>F_LEAK   | Leakage from VPWR to VREF                      | Use standard mode 0. Set VREF = 0 V. Measured current flowing out of VREF pin                                                                                                                                                                                                                                                                         |     |      | 1   | μA   |

| I <sub>VREF_TO_VPW</sub>             | Leakage from VREF to VPWR                      | Use standard mode 0. Set VPWR = 0 V. Measured as current flowing out of VPWR pin                                                                                                                                                                                                                                                                      |     |      | 1   | μΑ   |

# 6.9 Timing Requirements

|                       |                        |                                                                                                                                                                                           | MIN | NOM | MAX | UNIT |

|-----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| ENABLE PI             | N AND VREF FAST CHARGE |                                                                                                                                                                                           |     |     |     |      |

| T <sub>VREF_CHG</sub> | VREF fast charge time  | Time between when 5 V is applied to V <sub>PWR</sub> , and V <sub>REF</sub> reaches V <sub>VREF_FAST_CHG</sub> . Needs to happen before or at same time t <sub>ON_STARTUP</sub> completes |     | 0.5 | 1   | ms   |

# **Timing Requirements (continued)**

|                                        |                                            |                                                                                                                                                                                                                                                                                                     | MIN NOM                                                                             | MAX  | UNIT |

|----------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|

| T <sub>ON_STARTU</sub><br>P_MODE0      | Device turnon time from UVLO mode 0        | Mode 0. $\overline{\text{EN}}$ = 0 V, measured from V <sub>PWR</sub> and V <sub>REF</sub> = UVLO <sup>+</sup> to data FET ON, V <sub>PWR</sub> comes to UVLO <sup>+</sup> second. Place 3.3 V on VD±. Ramp VREF to 3.3 V, then VPWR to 5 V and measure the time it takes for D± to reach 90% of VD± | 0.5                                                                                 | 1    | ms   |

| T <sub>ON_STARTU</sub><br>P_MODE1      | Device turnon time from UVLO mode 1        | Informative. mode 1. $\overline{\text{EN}}$ = 0 V, measured from V <sub>PWR</sub> = UVLO <sup>+</sup> to data FET ON                                                                                                                                                                                | 0.5 +<br>T <sub>CHG_C</sub><br>VREF                                                 |      | ms   |

| T <sub>ON_STARTU</sub><br>P_MODE1_3.3V | Device turnon time from UVLO mode 1        | Mode 1. $\overline{\text{EN}}$ = 0 V, measured from V <sub>PWR</sub> = UVLO <sup>+</sup> to data FET ON, C <sub>VREF</sub> = 1 $\mu$ F, V <sub>REF_FINAL</sub> = 3.3 V. Measure the time it takes for D± to reach 90% of VD±                                                                        | 0.6                                                                                 | 1    | ms   |

| T <sub>ON_EN_MOD</sub><br>E0           | Device turnon time mode 0                  | Mode 0. $V_{PWR} = 5 \text{ V}$ , $V_{REF} = 3.3 \text{ V}$ , time from $\overline{\text{EN}}$ is asserted until data FET is ON. Place 3.3 V on VD±, measure the time it takes for D± to reach 90% of VD±                                                                                           | 150                                                                                 |      | μs   |

| T <sub>ON_EN_MOD</sub><br>E1           | Device turnon time mode 1                  | Mode 1. $V_{PWR} = 5 \text{ V}$ , $V_{REF\_INITIAL} = 0 \text{ V}$ , time from $\overline{EN}$ is asserted until data FET is $\overline{ON}$ . Place 3.3 V on VD±, measure the time it takes for D± to reach 90% of VD±                                                                             | 150 +<br>T <sub>CHG_V</sub><br>REF                                                  |      | μs   |

| T <sub>ON_EN_MOD</sub><br>E1_3.3V      | Device turnon time mode 1 for VREF = 3.3 V | Mode 1. $V_{PWR} = 5$ V, $V_{REF\_INITIAL} = 0$ V, time from $\overline{EN}$ is asserted until data FET is ON. Place 3.3 V on VD±, measure the time it takes for D± to reach 90% of VD±. $C_{VREF} = 1$ $\mu$ F, VREF_FINAL = 3.3 V                                                                 | 300                                                                                 |      | μs   |

| T <sub>OFF_EN</sub>                    | Device turnoff time                        | Mode 0 or 1. $V_{PWR}$ = 5 V, $V_{REF}$ = 3.3 V, time from $\overline{EN}$ is deasserted until data FET is off. Place 3.3 V on VD±, measure the time it takes for D± to fall to 10% of VD±, $R_{D\pm}$ = 45 $\Omega$                                                                                | 5                                                                                   |      | μs   |

| $T_{CHG\_CVREF}$                       | Time to charge C <sub>VREF</sub>           | Informative. Mode 1. Time from $V_{REF}$ = 0 V to 80% × $V_{REF\_FINAL}$ after $\overline{EN}$ transitions from high to low                                                                                                                                                                         | (C <sub>VREF</sub> × 0.8<br>(V <sub>REF</sub> FI<br>NAL)/(I <sub>C</sub><br>HG_VREF |      | s    |

| T <sub>CHG_CVREF</sub>                 | Time to charge $C_{\text{VREF}}$ to 3.3 V  | Mode 1. Time from $V_{REF}$ = 0 V to 90% × 3.3 V after $\overline{EN}$ transitions from high to low, $C_{VREF}$ = 1 $\mu F$                                                                                                                                                                         | 132                                                                                 |      | μs   |

| T <sub>CHG_CVREF</sub><br>_0.66V       | Time to charge C <sub>VREF</sub> to 0.66 V | Mode 1. Time from V <sub>REF</sub> = 0 V to 90% × 0.63 V after $\overline{\text{EN}}$ transitions from high to low, C <sub>VREF</sub> = 1 $\mu$ F. R <sub>TOP</sub> = 47.5 $k\Omega$ ± 1%, R <sub>BOT</sub> = 150 $k\Omega$ ± 1%                                                                    | 26                                                                                  |      | μs   |

| OVER VOLT                              | AGE PROTECTION                             |                                                                                                                                                                                                                                                                                                     |                                                                                     |      |      |

| t <sub>OVP_response</sub><br>_VBUS     | OVP response time to VBUS                  | Mode 0 or 1. Measured from OVP condition to FET turn off . Short VD± to 5 V and measure the time it takes D± voltage to reach 0.1 x V <sub>D±_CLAMP_MAX</sub> from the time the 5-V hot-plug is applied. $R_{LOAD\_D\pm} = 45 \ \Omega$ . (1) (2)                                                   | 2                                                                                   |      | μs   |

| t <sub>OVP_response</sub>              | OVP response time                          | Mode 0 or 1. Measured from OVP condition to FET turn off . Short VD± to 18 V and measure the time it takes D± voltage to reach 0.1 × VD±_CLAMP_MAX from the time the 18-V hot-plug is applied. $R_{LOAD\_D\pm} = 45~\Omega^{(1)}$ (2)                                                               | 0.1                                                                                 | 1    | μs   |

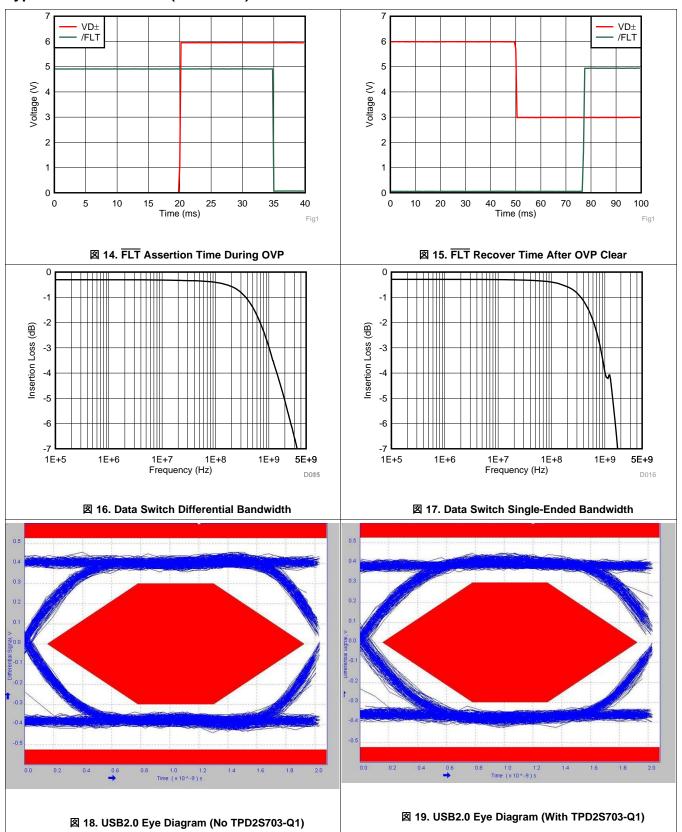

| t <sub>OVP_Recov</sub><br>_FLT         | Recovery time FLT pin                      | Measured from OVP clear to FLT deassertion <sup>(1)</sup>                                                                                                                                                                                                                                           | 32                                                                                  |      | ms   |

| t <sub>OVP_Recov</sub><br>_FET         | Recovery time for data FET to turn back on | Measured from OVP clear until FET turns back on. Drop VD+ from 16 V to 3.3 V with $V_{REF}$ = 3.3 V, measure time it takes for D+ to reach 90% of 3.3 V                                                                                                                                             | 32                                                                                  |      | ms   |

| t <sub>OVP_ASSERT</sub>                | FLT assertion time                         | Measured from OVP on VD+ or VD- to FLT assertion                                                                                                                                                                                                                                                    | 12.6 18                                                                             | 23.4 | ms   |

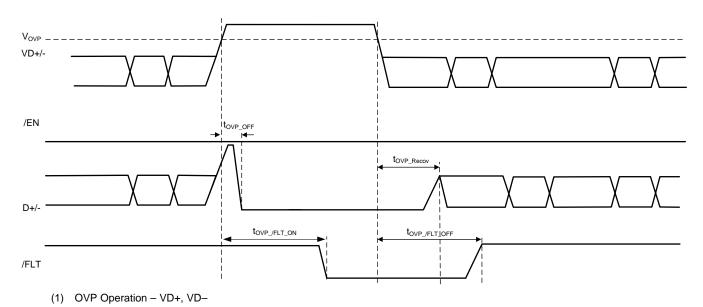

<sup>(1)</sup> Shown in 図 1.(2) Specified by design, not production tested.

図 1. TPD2S703-Q1 Timing Diagram

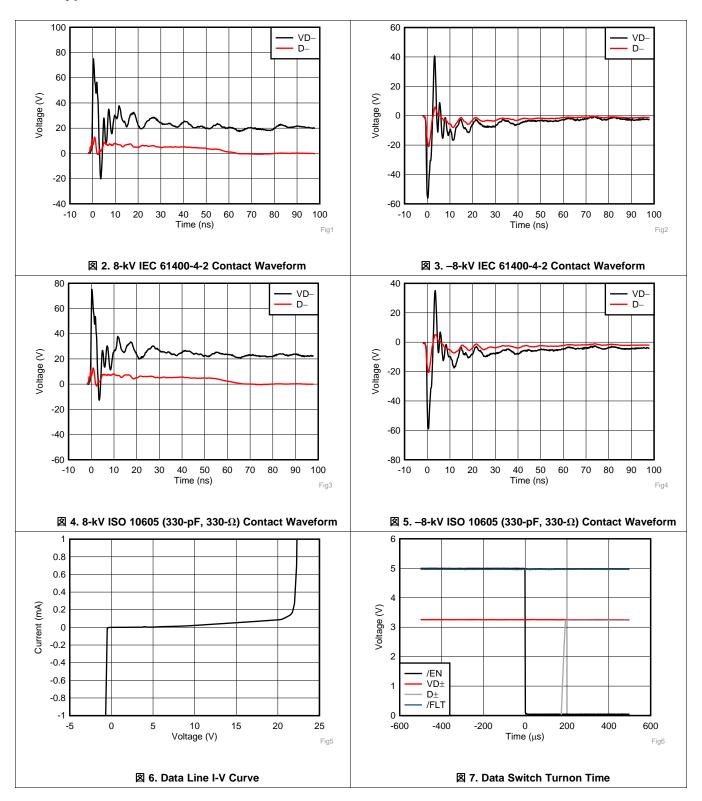

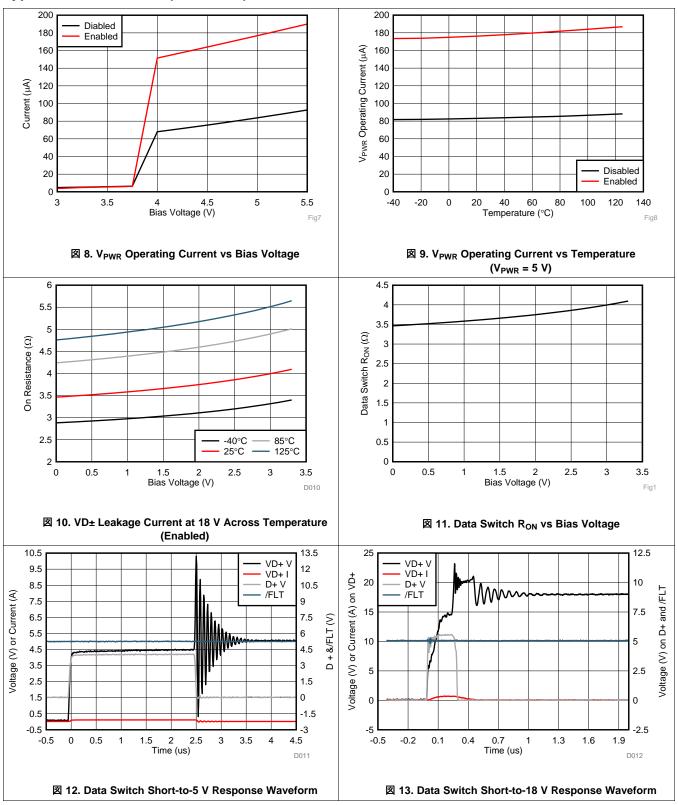

# 6.10 Typical Characteristics

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# 7 Parameter Measurement Information

Copyright © 2017, Texas Instruments Incorporated

図 20. ESD Setup

図 21. Short-to-Battery Setup

# 8 Detailed Description

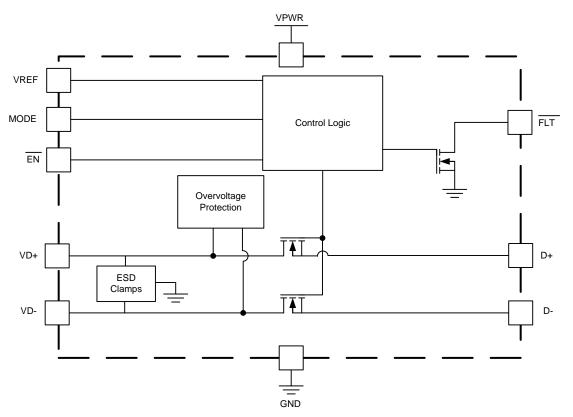

#### 8.1 Overview

The TPD2S703-Q1 is a 2-Channel Data Line Short-to-Battery, Short-to- $V_{BUS}$ , and IEC61000-4-2 ESD protection device for automotive high-speed interfaces like USB2.0. The TPD2S703-Q1 contains two data line nFET switches which ensure safe data communication while protecting the internal system circuits from any overvoltage conditions at the VD+ and VD- pins. On these pins, this device can handle overvoltage protection up to 18-V DC. This provides sufficient protection for shorting the data lines to the car battery as well as the USB  $V_{BUS}$  rail.

Additionally, the TPD2S703-Q1 has a FLT pin which provides an indication when the device sees an overvoltage condition and automatically resets when the overvoltage condition is removed. The TPD2S703-Q1 also integrates IEC ESD clamps on the VD+ and VD- pins, thus eliminating the need for external TVS clamp circuits in the application.

The TPD2S703-Q1 has an internal oscillator and charge pump that controls the turnon of the internal nFET switches. The internal oscillator controls the timers that enable the charge pump and resets the open-drain FLT output. If VD+ and VD- are less than  $V_{OVP}$ , the internal charge pump is enabled. After an internal delay, the charge-pump starts-up, turning on the internal nFET switches. At any time, if VD+ or VD- rises above  $V_{OVP}$ , TPD2S703-Q1 asserts FLT pin LOW and the nFET switches are turned off.

#### 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 OVP Operation

When the VD+, or VD- voltages rise above  $V_{OVP}$ , the internal nFET switches are turned off, protecting the transceiver from overvoltage conditions. The response is very rapid, with the FET switches turning off in less than 1  $\mu$ s. Before the OVP condition, the FLT pin is High-Z, and is pulled HIGH via an external resistor to indicate there is no fault. Once the OVP condition occurs, the FLT pin is asserted LOW. When the VD+, or VD-voltages returns below VOVP – VHYS-OVP, the nFET switches are turned on again. When the OVP condition is cleared and the nFETs are completely turned on, the FLT is reset to high-Z.

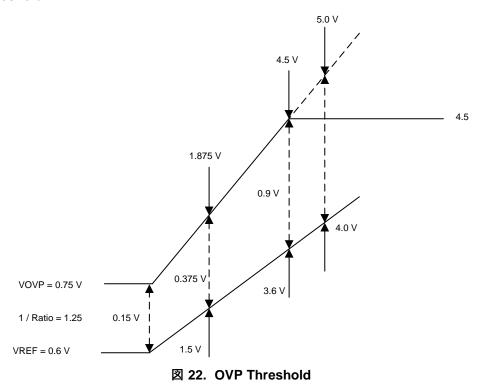

#### 8.3.2 OVP Threshold

The OVP Threshold  $V_{OVP}$  is set by  $V_{REF}$  according to  $\pm$  1,  $\pm$  2 and  $\pm$  3.

$$VOVP = 1.25 \times VREF$$

(1)

$$VREF \leq 3.6 V$$

(2)

$$VOVP = 4.5 \text{ V for VREF} > 3.6 \text{ V}$$

$V_{REF}$  can be set either by an external regulator (Mode 0) or an internal adjustable regulator (Mode 1). See the  $V_{REF}$  Operation section for more details on how to operate  $V_{REF}$  in Mode 0 and Mode 1.

## 8.3.3 D± Clamping Voltage

The TPD2S703-Q1 provides a differentiated device architecture which allows the system designer to control the clamping voltage the protected transceiver sees from the D+ and D- pins. This architecture allows the system designer to minimize the amount of stress the transceiver sees during Short-to-Battery and ESD events. The clamping voltage that appears on the D+ and D- lines during a short-to-battery or ESD event obeys  $\pm$  4.

$$VCLAMP_DP/M = VREF + VBR + IRDYN$$

(4)

#### **Feature Description (continued)**

Where  $V_{BR}$  approximately = 0.7 V,  $IR_{DYN}$  approximately = 1 V. By adjusting  $V_{REF}$ , the clamping voltage of the D+ and D- lines can be adjusted. As  $V_{REF}$  also controls the OVP threshold, take care to insure that the  $V_{REF}$  setting both satisfies the OVP threshold requirements while simultaneously optimizing system protection on the D+ and D- lines.

The size of the capacitor used on the  $V_{REF}$  pin also influences the clamping voltage as transient currents during Short-to-Battery and ESD events flow into the  $V_{REF}$  capacitor. This causes the  $V_{REF}$  voltage to increase, and likewise the clamping voltage on D± according to  $\pm$  4. The larger capacitor that is used, the better the clamping performance of the device is going to be. See the parametric tables for the clamping performance of the TPD2S703-Q1 with a 1- $\mu$ F capacitor.

#### 8.4 Device Functional Modes

The TPD2S703-Q1 has two modes of operation which vary the way the VREF pin functions. In Mode 0, the VREF pin is connected to an external regulator which sets the voltage on the VREF pin. In Mode 1, the TPD2S703-Q1 uses an adjustable internal regulator to set the VREF voltage. Mode 1 enables the system designer to operate the TPD2S703-Q1 with a single power supply, and have the flexibility to easily set the VREF voltage to any voltage between 0.6 V and 3.8 V with two external resistors.

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

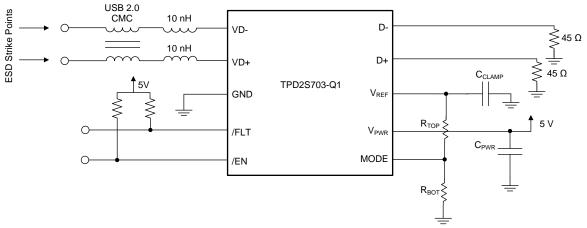

## 9.1 Application Information

The TPD2S703-Q1 offers 2-channels of short-to-battery protection (up to 18-V DC), short-to-VBUS protection, and IEC ESD protection for automotive high speed interfaces such as USB 2.0. For the overvoltage protection (OVP), this device integrates N-channel FET's which quickly isolate (200 ns) the protected circuitry in the event of an overvoltage condition on the VD+ and VD- lines. With respect to the ESD protection, the TPD2S703-Q1 has an internal clamping diode on each data line (VD+ and VD-) which provides 8-kV contact ESD protection and 15-kV air-gap ESD protection. More details on the internal components of the TPD2S703-Q1 can be found in the *Overview* section.

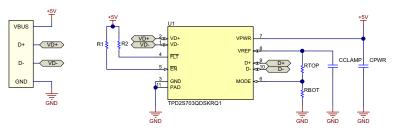

The TPD2S703-Q1 also has the ability to vary the OVP threshold based on the configuration of the Mode pin and the voltage present on the VREF pin (0.6 V-4.5 V). This functionality is discussed in greater depth in the OVP Threshold section. Once the VREF threshold is crossed, a fault is detectable to the user through the FLT pin, where 5 V on the pin indicates no fault is detected, and 0 V-0.4 V represents a fault condition. ☒ 23 shows the TPD2S703-Q1 in a typical application, interfacing between the protected internal circuitry and the connector side, where ESD vulnerability is at its highest.

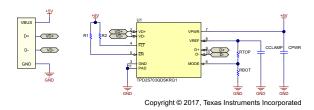

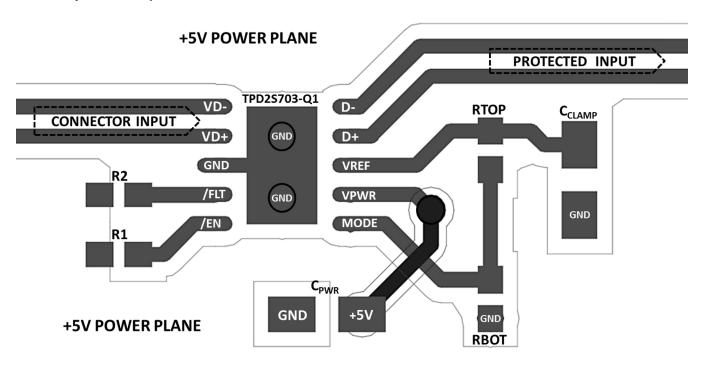

#### 9.2 Typical Application

Copyright © 2017, Texas Instruments Incorporated

図 23. USB 2.0 Port With Short-to-Battery and IEC ESD Protection

# **Typical Application (continued)**

#### 9.2.1 Design Requirements

#### 9.2.1.1 Device Operation

$\frac{1}{8}$  1 gives the complete device functionality in response to the  $\overline{\text{EN}}$  pin, to overvoltage conditions at the connector (VD± pins), to thermal shutdown, and to the conditions of the V<sub>PWR</sub>, V<sub>REF</sub>, and MODE pins.

表 1. Device Operation Table

| Functional Mode         | EN | MODE                                             | 衣 1. Device                                     | VPWR          | VD±                                                                                                                                                                                                  | TJ                                                                                                                                                                           | FLT | Comments                                                                                                                                 |

|-------------------------|----|--------------------------------------------------|-------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| NORMAL OPERA            |    | IIIODE                                           | TILL                                            | <b>VI VII</b> | VDI                                                                                                                                                                                                  | 10                                                                                                                                                                           | 1   | Comments                                                                                                                                 |

| Mode 0<br>unpowered 1   | Х  | $R_{bot} \le 2.6 \text{ k}\Omega$                | Х                                               | Х             | х                                                                                                                                                                                                    | Х                                                                                                                                                                            | Н   | Device unpowered, data switches open                                                                                                     |

| Mode 0<br>unpowered 2   | Х  | $R_{bot} \le 2.6 \text{ k}\Omega$                | Х                                               | х             | Х                                                                                                                                                                                                    | Х                                                                                                                                                                            | Н   | Device unpowered, data switches open                                                                                                     |

| Mode 1<br>unpowered     | Х  | $R_{top} \mid \mid R_{bot} > 14 \text{ k}\Omega$ | Х                                               | Х             | х                                                                                                                                                                                                    | Х                                                                                                                                                                            | Н   | Device unpowered, data switches open                                                                                                     |

| Mode 0 disabled         | Н  | $R_{bot} \le 2.6 \text{ k}\Omega$                | >UVLO                                           | >UVLO         | Х                                                                                                                                                                                                    | <tsd< td=""><td>Н</td><td>Device disabled, data switches open</td></tsd<>                                                                                                    | Н   | Device disabled, data switches open                                                                                                      |

| Mode 1 disabled         | Н  | $R_{top} \mid \mid R_{bot} > 14 \text{ k}\Omega$ | Set by R <sub>top</sub><br>and R <sub>bot</sub> | >UVLO         | х                                                                                                                                                                                                    | <tsd< td=""><td>Н</td><td>Device disabled, data switches open, V<sub>REF</sub> is disabled</td></tsd<>                                                                       | Н   | Device disabled, data switches open, V <sub>REF</sub> is disabled                                                                        |

| Mode 0 enabled          | L  | $R_{bot} \le 2.6 \text{ k}\Omega$                | >UVLO                                           | >UVLO         | <ovp< td=""><td><tsd< td=""><td>Н</td><td>Device enabled, data switches closed, V<sub>REF</sub> is the value set by the power supply on V<sub>REF</sub></td></tsd<></td></ovp<>                      | <tsd< td=""><td>Н</td><td>Device enabled, data switches closed, V<sub>REF</sub> is the value set by the power supply on V<sub>REF</sub></td></tsd<>                          | Н   | Device enabled, data switches closed, V <sub>REF</sub> is the value set by the power supply on V <sub>REF</sub>                          |

| Mode 1 enabled          | L  | $R_{top} \mid \mid R_{bot} > 14 \text{ k}\Omega$ | Set by R <sub>top</sub><br>and R <sub>bot</sub> | >UVLO         | <ovp< td=""><td><tsd< td=""><td>Н</td><td>Device enabled, data switches closed, V<sub>REF</sub> is the value set by the R<sub>top</sub> and R<sub>bot</sub> resistor divider</td></tsd<></td></ovp<> | <tsd< td=""><td>Н</td><td>Device enabled, data switches closed, V<sub>REF</sub> is the value set by the R<sub>top</sub> and R<sub>bot</sub> resistor divider</td></tsd<>     | Н   | Device enabled, data switches closed, V <sub>REF</sub> is the value set by the R <sub>top</sub> and R <sub>bot</sub> resistor divider    |

| FAULT CONDITIO          | NS |                                                  |                                                 |               | '                                                                                                                                                                                                    |                                                                                                                                                                              |     |                                                                                                                                          |

| Mode 0 thermal shutdown | Х  | $R_{bot} \le 2.6 \text{ k}\Omega$                | Х                                               | >UVLO         | х                                                                                                                                                                                                    | >TSD                                                                                                                                                                         | L   | Thermal shutdown, data switches opened, FLT pin asserted                                                                                 |

| Mode 1 thermal shutdown | Х  | $R_{top} \mid \mid R_{bot} > 14 \text{ k}\Omega$ | Set by R <sub>top</sub> and R <sub>bot</sub>    | >UVLO         | х                                                                                                                                                                                                    | >TSD                                                                                                                                                                         | L   | Thermal shutdown, data switches opened, V <sub>REF</sub> is disabled, FLT pin asserted                                                   |

| Mode 0 OVP fault        | L  | R <sub>bot</sub> ≤ 2.6 kΩ                        | >UVLO                                           | >UVLO         | >OVP                                                                                                                                                                                                 | <tsd< td=""><td>L</td><td>Data line overvoltage protection mode. OVP is set relative to the voltage on V<sub>REF</sub>. Data switches opened, FLT pin asserted</td></tsd<>   | L   | Data line overvoltage protection mode. OVP is set relative to the voltage on V <sub>REF</sub> . Data switches opened, FLT pin asserted   |

| Mode 1 OVP fault        | L  | $R_{top} \mid \mid R_{bot} > 14 \text{ k}\Omega$ | Set by R <sub>top</sub><br>and R <sub>bot</sub> | >UVLO         | >OVP                                                                                                                                                                                                 | <tsd< td=""><td>L</td><td>Data line overvoltage protection mode. OVP is set relative to the voltage on V<sub>REF</sub>. Data switches opened, fault pin asserted</td></tsd<> | L   | Data line overvoltage protection mode. OVP is set relative to the voltage on V <sub>REF</sub> . Data switches opened, fault pin asserted |

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 $V_{REF}$ Operation

The TPD2S703-Q1 has two modes of operation which vary the way the  $V_{REF}$  pin functions. In Mode 0, the  $V_{REF}$  pin is connected to an external regulator which sets the voltage on the  $V_{REF}$  pin. In Mode 1, the TPD2S703-Q1 uses an adjustable internal regulator to set the  $V_{REF}$  voltage. Mode 1 enables the system designer to operate the TPD2S703-Q1 with a single power supply, and have the flexibility to easily set the  $V_{REF}$  voltage to any voltage between 0.6 V and 3.8 V with two external resistors.

#### 9.2.2.1.1 Mode 0

To set the device into Mode 0, ensure that  $R_{bot}$ , resistance between the MODE pin and ground, is less than 2.6 k $\Omega$ . The easiest way to implement Mode 0 is to directly connect the mode pin to GND on your PCB. With this resistance condition met, connect  $V_{REF}$  to an external regulator to set the  $V_{REF}$  voltage.

#### 9.2.2.1.2 Mode 1

To operate in Mode 1, ensure that  $R_{top} \parallel R_{bot}$ , resistance between the MODE pin and ground, is greater than 14 k $\Omega$ . This is accomplished by insuring  $R_{top} \parallel R_{bot} > 14$  k $\Omega$  because when the device is initially powered up,  $V_{REF}$  is at ground until the internal circuitry recognizes if the device is in Mode 1 or Mode 2.

In Mode 1,  $V_{REF}$  is set by using an internal regulator to set the voltage. Using a resistor divider off of a feedback comparator is how to set  $V_{REF}$ , similar to a standard LDO or DC/DC.  $V_{REF}$  is set in Mode 1 according to  $\pm$  5.

$$V_{REF} = \frac{V_{MODE}(R_{TOP} + R_{BOT})}{R_{BOT}}$$

(5)

式 5 yields the typical value for  $V_{REF}$ . When using ±1% resistors  $R_{TOP}$  and  $R_{BOT}$ ,  $V_{REF}$  accuracy is going to be ±5%. Therefore, the minimum and maximum values for  $V_{REF}$  can be calculated off of the typical  $V_{REF}$ . The parametric tables above give example  $R_{TOP}$  and  $R_{BOT}$  resistors to use for standard output  $V_{REF}$  voltages for Mode 1.

# 9.2.2.2 Mode 1 Enable Timing

In Mode 1, when the TPD2S703-Q1 is disabled, the output regulator is disabled, leading  $V_{REF}$  to discharge to 0 V through  $R_{TOP}$  and  $R_{BOT}$ . It is desired for  $V_{REF}$  to be at 0 V when the device is disabled to minimize the clamping voltage during a power disabled Short-to-Battery or ESD event. If  $V_{REF}$  is at 0 V, this holds D± near ground during these fault events.

When enabling the TPD2S703-Q1,  $V_{REF}$  is quickly charged up to insure a quick turnon time of the Data FETs. Data FET turnon is gated by  $V_{REF}$  reaching 80% of its final voltage plus 150  $\mu$ s to insure a proper OVP threshold is set before passing data. This prevents false OVPs due to normal operation. Because Data FET turnon is gated by charging the  $V_{REF}$  clamping capacitor, the size of the capacitor influences the turnon time of the Data switches. The TPD2S703-Q1's internal regulator uses a constant current source to quickly charge the  $V_{REF}$  clamping capacitor, so the charging time of  $C_{VREF}$  can easily be calculated with  $\pm$  6.

$$tchg\_cvref = \frac{Cvref \times 0.8(VREFfinal)}{Ichg\_vref}$$

(6)

Where  $C_{VREF}$  is the clamping capacitance on  $V_{REF}$ ,  $VREF_{FINAL}$  is the final value  $V_{REF}$  is set to, and  $I_{CHG\_VREF} = 22$  mA (typical). If  $V_{REF} = 1$  V, 0.8 is used in the above equation because 80% of  $V_{REF}$  is the amount of time that gates the turnon of the Data FETs. Once  $t_{CHG\_CVREF}$  is calculated, the typical turnon time of the Data FETs can be calculated from  $\vec{\pm}$  7.

$$ton_{pn} = tch_{cvref} + 150 \mu s$$

(7)

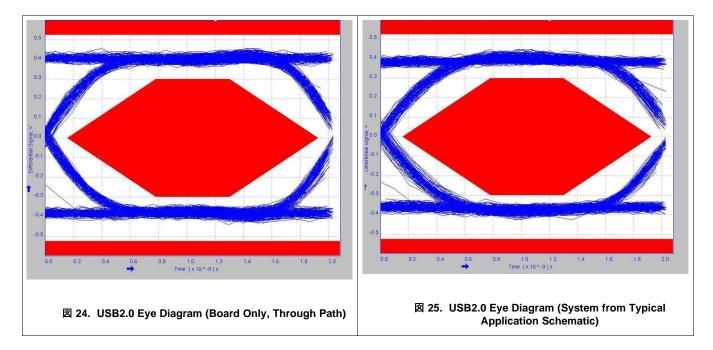

#### 9.2.3 Application Curves

# 10 Power Supply Recommendations

# 10.1 V<sub>PWR</sub> Path

The  $V_{PWR}$  pin provides power to the TPD2S703-Q1. A 10- $\mu$ F capacitor is recommended on  $V_{PWR}$  as close to the pin as possible for localized decoupling of transients. A supply voltage above the UVLO threshold for  $V_{PWR}$  must be supplied for the device to power on.