## Design Guide: TIDM-02009 ASIL D 安全性コンセプト検証済み、高速トラクション、双方向 DC/DC 変換のリファレンス・デザイン

## **TEXAS INSTRUMENTS**

## 概要

このリファレンス・デザインでは、1 つの TMS320F28388D C2000<sup>™</sup> リアルタイム MCU を使って HV/EV (ハイブリッド車と電気自動車)のトラクション・イン バータと双方向 DC/DC コンバータを制御する方法を示し ます。トラクション制御機能はソフトウェア・ベースのリゾル バ / デジタル・コンバータ (RDC)を使用し、最高 20,000RPM に達する高速でモーターを駆動します。この

DC/DC コンバータは、ピーク電流モード制御 (PCMC) 方 式を採用しています。ASIL 分割ベースのシステム向け機 能安全コンセプトであり、TÜV SÜD がすでに評価を完了 しているので、ISO 26262 ASIL D までのシステム・レベル 安全性インテグリティ・レベル (SIL) の提示に適しており、 代表的な安全性の目標を達成できます。

## リソース

| TIDM-02009                 | デザイン・フォル<br>ダ  |

|----------------------------|----------------|

| TMS320F28388D、UCC5870-Q1   | プロダクト・フォ<br>ルダ |

| AMC1302-Q1, AMC1311-Q1     | プロダクト・フォ<br>ルダ |

| TMS570LS1227、TCAN4550-Q1   | プロダクト・フォ<br>ルダ |

| C2000WARE-DIGITALPOWER-SDK | ツール・フォル<br>ダ   |

Ask our TI E2E<sup>™</sup> support experts

## 特長

- SiC 電力段を採用し、(最高 20,000RPM の) 高速で 動作する EV トラクション・インバータ

- SiC 製の 1 次側 FET を採用した、双方向 HV-LV (高 電圧 / 低電圧変換) 位相シフト・フルブリッジ (PSFB) DC/DC コンバータ

- 高速回転するモーターをサポートする、ソフトウェア・ベースのリゾルバ / デジタル変換 (RDC)

- 1 つの TMS320F28388D を使用したトラクション・イン バータと DC/DC コンバータの制御機能を内蔵

- ASIL 分割に基づく ASIL-D 機能安全コンセプトの評価を TÜV SÜD が実施済み

- ピーク電流モード制御 (PCMC) を目的とした外部サポ ート回路を使用せずに、同期整流 (SR) スイッチング 方式を使用する PCMC 機能を実現

## アプリケーション

- インバータおよびモーター制御

- **DC/DC** コンバータ

## **1** System Description

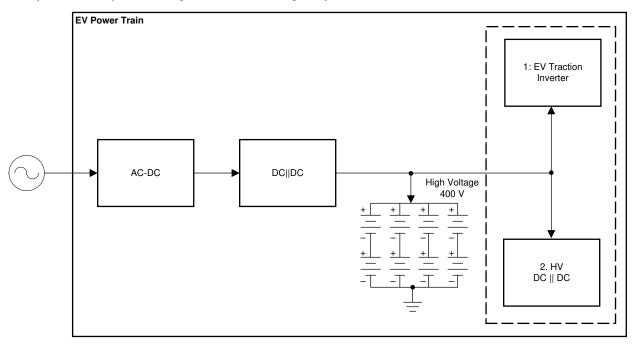

The power-train system is the core component in an electric vehicle as shown in ⊠ 1-1. It mainly contains three sub-modules, on board charger (OBC), traction inverter, and high voltage (HV) to low voltage (LV) DC-DC converter. The current trend in the industry is to integrate the OBC, traction inverter and DC-DC sub-systems into fewer enclosures, and control them with fewer MCU to reduce system cost and complexity. This will require MCU to have high real-time control performance. In this reference design, the traction inverter and bi-directional DC-DC converter are controlled with one C2000<sup>™</sup> TMS320F28388D microcontroller. When this DC-DC is made bi-directional, it can be used to pre-charge the DC bus capacitor in the traction inverter system, which can reduce system cost by eliminating the current limiting relay and resistor.

## 図 1-1. Electric Vehicle Power-Train System

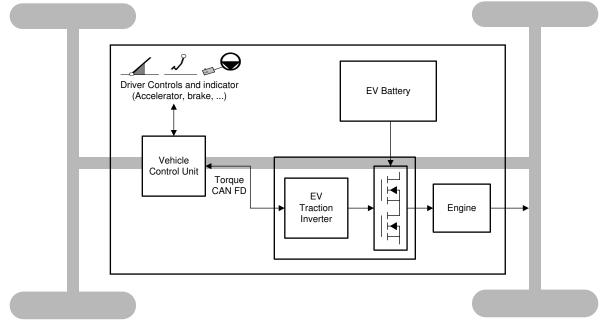

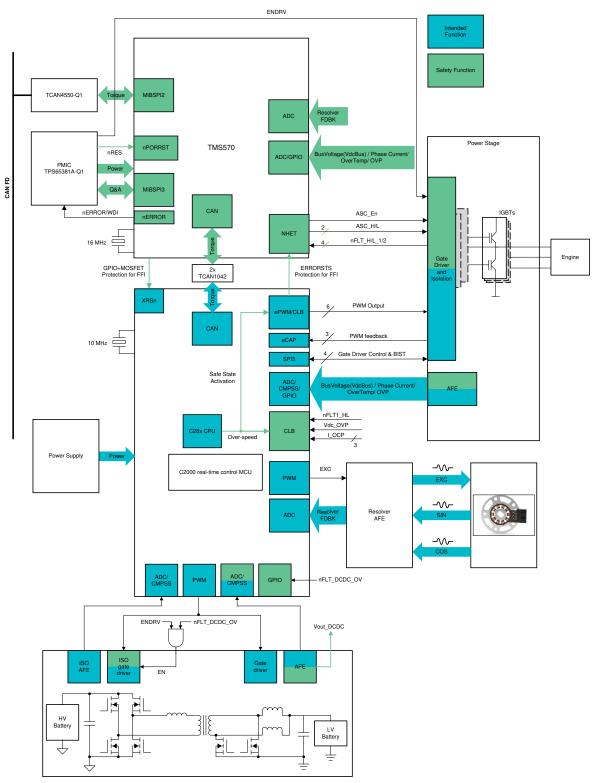

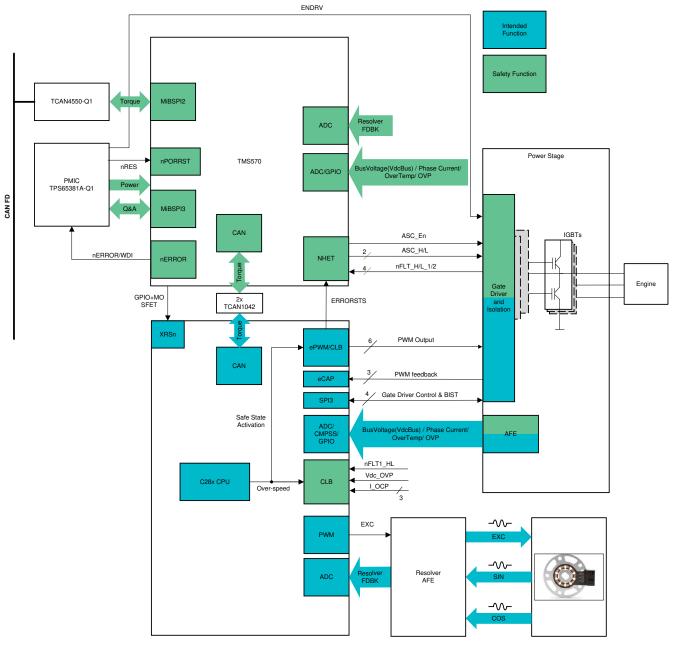

⊠ 1-2 shows the high-level block diagram of the Traction Inverter system. This reference includes a CAN FD interface to receive torque command, SiC inverter power stage with isolated sensing, and a resolver to digital converter system for position feedback.

Copyright © 2022 Texas Instruments Incorporated

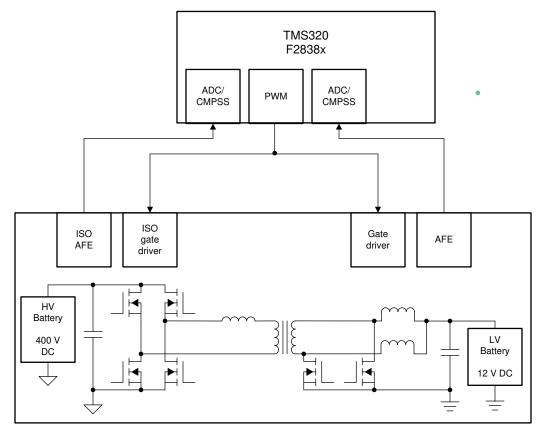

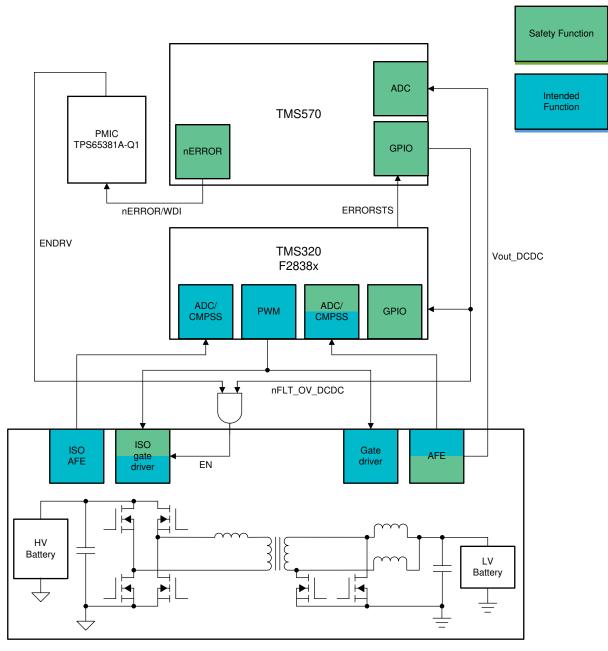

The block diagram of bi-directional DC-DC converter is shown in 🛛 1-3. A phase shifted full bridge (PSFB) converter with synchronous rectification is. In this reference design, ZVS for switches in the one leg of the full bridge, and zero or low-voltage switching for switches in the other leg, is achieved. In this design, current doubler synchronous rectification is implemented on the secondary side with different switching schemes to achieve optimum performance under varying load conditions.

## 図 1-3. DC-DC System Block Diagram

#### WARNING

TI intends this reference design to be operated in a *lab environment only and does not consider it to be a finished product* for general consumer use.

TI Intends this reference design to be used only by *qualified engineers and technicians* familiar with risks associated with handling high-voltage electrical and mechanical components, systems, and subsystems.

There are *accessible high voltages present on the board*. The board operates at voltages and currents that may cause shock, fire, or injury if not properly handled or applied. Use the equipment with necessary caution and appropriate safeguards to avoid injuring yourself or damaging property.

#### CAUTION

Do not leave the design powered when unattended.

**High voltage!** There are *accessible high voltages present on the board*. Electric shock is possible. The board operates at voltages and currents that may cause shock, fire, or injury if not properly handled. Use the equipment with necessary caution and appropriate safeguards to avoid injuring yourself or damaging property. For safety, use of isolated test equipment with over-voltage and over-current protection is highly recommended.

TI considers it the user's responsibility to confirm that the voltages and isolation requirements are identified and understood before energizing the board or simulation. *When energized, do not touch the design or components connected to the design.*

#### Hot surface! Contact may cause burns. Do not touch!

Some components may reach high temperatures >55°C when the board is powered on. The user must not touch the board at any point during operation or immediately after operating, as high temperatures may be present.

## 2 System Overview

## 2.1 Block Diagram

図 2-1. TIDM-02009 Block Diagram

## 2.2 Design Considerations

The traction drive subsystem is designed to drive an AC induction motor or some combination of interior permanent magnet synchronous motor (IPMSM) and synchronous reluctance motor (SynRM). High bandwidth field oriented control (FOC) scheme with dynamic decoupling is implemented with C2000 real-time control MCU together with field-weakening and over-modulation techniques to driver motor to industry-leading high speed up to 20,000 RPM, which can enable cost and weight reduction to the traction motor.

Traction drive system normally uses a variable reluctance (VR) resolver, which matches the pole count of the motor, to directly measure the electric angle of the rotor. Resolver to digital conversion (RDC) is required to measure position and speed using resolver signal. RDC is traditionally handled by a separate IC, such as PGA411-Q1. With C2000 MCU, RDC for high-speed traction inverter can be integrated into main control MCU, where the excitation generation can be handled with DMA without CPU involvement, and feedback is read through ADC and decoded with CPU.

A PSFB topology allows the switching devices to switch with zero voltage switching (ZVS) resulting in lower switching losses and higher efficiency. PCMC is a highly desired control scheme for power converters because of its inherent voltage feed forward, automatic cycle-by-cycle current limiting, flux balancing, and other advantages, which requires generating complex PWM drive waveforms along with fast and efficient control loop calculations. This is made possible on C2000 microcontrollers by advanced on-chip control peripherals like PWM modules, analog comparators with DAC and slope compensation hardware and 12-bit high-speed ADCs coupled with an efficient 32-bit CPU.

## 2.3 Highlighted Products

### 2.3.1 C2000<sup>™</sup> MCU F2838x

C2000 MCUs are part of an optimized MCU family for real-time control application. Fast and high-quality analogto-digital controller (ADC) enables accurate measurement of the current and voltage signals, and an integrated comparator subsystem (CMPSS) provides protection for over-current and over-voltage without use of any external devices. The optimized CPU core enables fast execution of control loop. Trigonometric operations are accelerated using the on-chip trigonometric math unit (TMU). The solution also provides an option to use the control law accelerator (CLA) on the F2838x. The CLA is a co-processor that can be used to alleviate CPU burden and enable faster-running loops or more functions on the C2000 MCU.

#### 2.3.2 UCC5870-Q1 Gate Driver

The UCC5870-Q1 device is a functional safety compliant, isolated, highly configurable single channel gate driver targeted to drive high power SiC MOSFETs and IGBTs in EV/HEV traction inverter applications. Power transistor protections such as shunt resistor based over-current, NTC based over-temperature, and DESAT detection, including selectable soft turn off or two-level turn off during these faults. To further reduce the application size, the UCC5870-Q1 integrates a 4A active Miller clamp during switching, and an active gate pull-down while the driver is unpowered. An integrated 10-bit ADC enables monitoring of up to 6 analog inputs and the gate driver temperature for enhanced system management. Diagnostics and detection functions are integrated to simplify the design of ASIL-D compliant systems. The parameters and thresholds for these features are configurable using the SPI interface, which allows the device to be used with nearly any SiC MOSFET or IGBT.

## 3 Hardware, Software, Testing Requirements, and Test Results

## 3.1 Hardware Requirements

The TIDM-02009 reference design kit consists of the following hardware modules

- 1. A F28388D controlCARD TMDSCNCD28388D F28388 controlCARD Evaluation Module

- 2. A TMS570 controlCARD

- 3. EV Traction and DC-DC converter Module

- a. Control module

- i. Control Mother Board

- ii. Vbat to 5V / 5A power supply modules

- iii. Vbat to 12V power supply module

- iv. 5V to 15V power supply

- v. Resolver interface module

- vi. Analog back end interface module

- vii. TCAN4550 module

- viii. TCAN1042 module

- b. Inverter module

- i. Inverter mother board

- ii. UCC5870 Gate driver module

- iii. Gate drive power supply module

- iv. Phase voltage sense module

- v. Phase current sense module

- c. DC-DC module

- i. DC-DC mother board

- ii. Gate driver module

#### 3.1.1 Hardware Overview

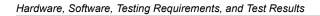

The evaluation kit is a open unit with no enclosures as shown in  $\boxtimes$  1-1. The kit is built together by assembling various submodules as discussed in earlier sections. The kit can be broadly divided into various functional blocks, such as the following:

- · Control Module for control, real time connectivity and functional safety

- Traction Inverter Module

- DC-DC converter Module

This section provides detailed information about the various modules. This section also provide information about considerations for power supply design and the various power supply modules.

#### WARNING

For laboratory evaluations with high voltages, it is recommended to take appropriate safety precautions for personnel and equipment safety such as HV safety enclosures, isolated power supplies, instrumentation and scopes.

#### 3.1.1.1 Control Module

Control module is the central unit that provides control and functional safety for the traction motor and dc-dc converter. It consists of various sub-modules for various functions as listed below.

- 1. Control card for control processor (TMDSCNCDF28388D)

- 2. Control card for safety processor (TMS570LS1227)

- 3. 5V / 5A power supply modules

- 4. 12V/1A power supply module

- 5. 15V/0.5A power supply module

- 6. Analog back end module

- 7. Resolver module

- 8. CAN interface modules based on TCAN4550 and TCAN1042

- 9. On board section to help monitor various power supplies

- 10. On board section to regulate inverter heat sink blower speed

- 11. Debug header to support JTAG and provide ETAS link

A fully assembled control module is shown in  $\boxtimes$  3-1.

## 🗷 3-1. Control Module

#### 3.1.1.1.1 Control Mother Board

Control mother board is the host board in control module. Most functions of the control module are realized on separate daughter cards that would plug into the control mother board. This helps with easy debugging and to easily replace modules in case of error or if improvements are needed. Here below is the list of modules it supports

- 1. HSEC180 connector slot to host the control card for control processor (TMDSCNCDF28388D)

- 2. DIMM100 connector slot to host the safety processor (TMS570)

- 3. Connectors to connect to traction inverter module

- 4. Connectors to connect to dc-dc converter module

- 5. Connectors to host 5-V/5-A power supplies for the control unit and inverter gate driver power supply.

- 6. Connectors to host 12-V/1-A power supply for the DC-DC converter gate driver and 15-V/0.5-A power supply for resolver

- 7. Connectors to host analog back end module to process the analog signal feedback from inverter. The close proximity of this module to the processor slot is to increase integrity of analog signal chain.

- 8. Connectors to host resolver module that act as an analog front end between the resolver and MCUs.

- 9. Connectors to host CAN interface modules based on TCAN4550 and TCAN1042

- 10. Module to help monitor various power supplies

- 11. Module to control blower fan for inverter heatsink thermal dissipation

- 12. Debug header to support JTAG and provide ETAS link

The bare control mother board is shown in  $\boxtimes$  3-2.

### 図 3-2. Control Mother Board

12-V power from a battery or power supply is fed to the mother board through a power jack receptacle J14. A single pole double throw switch is used to turn on/ off the power to the control module. This 12-V power supply feeds two 5-V/5-A power supplies, one to supply power to entire control module (from which 3.3 V is obtained) and the other to primarily feed the inverter gate driver power supply. The 12-V power supply also feeds a SEPIC 12 power supply module to feed the dc-dc converter gate driver. For flexibility sake during testing, certain options are built in the mother board to select the choice of MCU for certain controls and choice of power supply for resolver interface. These are described in sections below

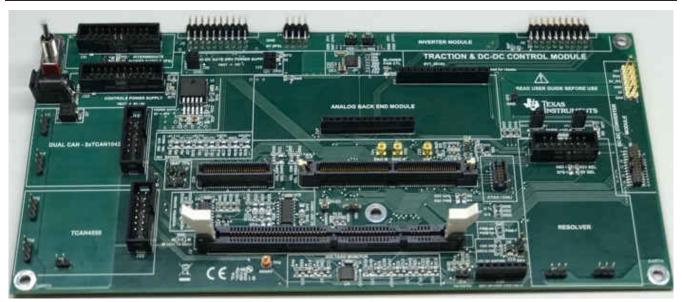

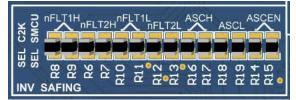

#### 3.1.1.1.1.1 Inverter Safing - UCC5870 ASC and Fault Control

Safe operation of traction inverter for the assumed safety goals is critical to system level ASIL-D compliance. Over current protection is handled by CMPSS of the C2000 device. This is a software programmable limit. There is also a redundant hardware detection for over current for a certain absolute maximum limit of the inverter. In the event of these hardware not able to detect the over current limits in a timely manner, such as a short circuit, a quick response is needed to protect the inverter. UCC5870 is an ASIL-D compliant gate driver with many features.

For active short circuit (ASC) protection, it gives the user a choice to configure the logic state of the driver if such an event is detected. For example, the user could shut down all switches or shut down only the bottom switches or top switches. In this reference design, there are two MCUs each having a certain level of functional safety requirement. During development and testing, there should be an option to set these up by either safety MCU or control MCU or be put in a default setting.

In the first stage, an arbitration between being set by safety MCU and default hard settings is chosen with a multiplexer. Default setting is done using resistors connected to XX\_IN pins of CD4053 MUX and is shown in 3-3. These resistors can be tied to one of the power rails to set the desired logic level. Selection between these two signal sources (Safety MCU vs default settings) is done by EN\_DRV signal that is generated by a PMIC device on safety MCU control card. If EN\_DRV is activated, then the hard choices chosen by default resistor settings will be chosen for ASC otherwise the settings provided safety MCU will be chosen.

図 3-3. ASC Logic Selection between Safety MCU and Default Setting

#### **CAUTION** DO NOT populate resistors (R22 & R26) or (R24 & R27) or (R25 & R28) together as it will lead to vertical short circuit across the control power rail Vcc to GND.

In the second stage, a further arbitration is done between the output of first stage and that of the C2000MCU. This is done using 0E resistors that will act as a switch. These will connect the arbitration stage outputs and UCC5870 gate drivers. Besides the ASC signals, there nFLTx\_y signals that represent the primary and secondary side faults of low side and high side gate drivers. These are linked to either the safety MCU or C2000 MCU through a bunch of 0E resistors that are present alongside that of ASC second stage arbitration 0E resistors as shown in 🛛 3-4. Populating resistors on the left side will select C2000 MCU and that on the right will select Safety MCU.

図 3-4. Selection Between C2000 and Safety MCUs to Connect ASC and nFLT

## CAUTION

DO NOT populate both resistors of ASCx selection with an intent to connect to both MCUs. Since the ASC signals are either tied to power rails or digital outputs driven by respective MCUs, connecting them together can damage the GPIOs that are at different logic levels.

nFLTxy signals are inputs to MCUs and hence it is OK to populate both resistors to connect with both MCUs.

## 3.1.1.1.1.2 DC-DC Safing

DC-DC converter deals with high voltages and currents and a safe operation of the converter for assumed safety goals is critical to ASIL D compliance. In the event of an over voltage detected in the converter, it is designed to be shut down. The safety MCU will monitor the safe operation of DC-DC converter and send the shut down signals as needed. In the event of PMIC device on the safety MCU control card determining unsafe power levels, it can also shut down the converter. However, during development and testing, C2000 MCU may be needed to generate the shut down signal. The choice between C2000 and safety MCU can be made by selection of 0E resistors, R71 and R72 respectively, on the control mother board. This section of the board is shown in 🛛 3-5.

## 図 3-5. MCU Selection for DC-DC Safing

Copyright © 2022 Texas Instruments Incorporated

#### CAUTION

- DO NOT populate resistors R71 and R72 at the same time as that will tie the outputs of two MCUs together. If they were configured for different polarities, it may damage the output pins of MCUs tied to these resistors.

- If jumper J34 is removed, then it will continuously enable the converter. This can be used during low votlage debug times. When full operation is required, this jumper must be populated.

#### 3.1.1.1.1.3 DC-DC Converter Secondary PWM Selection

DC-DC converter requires 4 PWMs on the primary side and 2 on the secondary. The first PWM for secondary side is taken from EPWM6A. For flexibility sake, the second PWM is taken either from EPWM6B or EPWM7A. One of them will become redundant, but it can give some design options for experimenting during implementation. The related section on the control mother board is shown in 🛛 3-6.

図 3-6. Secondary PWM Source Selection

A 0E resistor on R65 will select EPWM6B as the source for 6th PWM (PWM F), whereas a 0E resistor on R63 will select EPWM7A for the same.

#### CAUTION

It is not advisable to mount both R63 and R65 together, and better be kept mutually exclusive to avoid malfunction or electrical damage to the pins if the other pin were to be used accidentally.

The unused GPIO pin between EPWM6B and EPWM7A could be used as a general purpose flag if required and could be monitored on the open terminal side of R63 or R65.

#### 3.1.1.1.1.4 Blower Fan Control

The traction inverter deals with pretty high power levels (about 10KVA) and that at high switching frequencies (40KHz), the switching losses and conduction losses are pretty high (>300W). Since the EVM is a laboratory model and is not supposed to be retrofitted into an EV/HEV, an appropriate blower cooled heatsink is used to control the temperature of inverter power module. The blowers used are 12 V operated (Dayton 2RTH4) and its speed can be regulated by C2000 MCU. The PWM pulses from the C2000 MCU are driven by TI driver DRV8876-Q1 to boost the power levels before being applied to the fan motor. The section of the control mother board hosting blower control is shown in  $\bowtie$  3-7.

図 3-7. Blower Fan control

Resistors R97 and R99 should be populated with 0E to connect the driver with blower fans . Headers J11 and J15 are where two blower motors can be connected. The blower fans can be noisy running at 12 V and high

speed. If such high speeds are not needed for any lab evaluations (such as lower traction power levels), it can be reduced by adjusting the PWM pulses from C2000.

#### Note

When low speed running of blower fans is preferred, they can be run off 5 V (intermediate power supply). The blowers can still blow some air good enough to move some heat away from heatsink. For this, 0E resistors is populated on R95 and R98, while removing the resistors R97 and R99. The user needs to monitor and ascertain the thermal safeness of such usage. If it is not enough, then discard this method.

#### CAUTION

With PWM control, at lower duty cycles, the on chip free wheeling diode in DRV8876 will have a larger conduction time. Since the diode drop is higher than the channel drop (during ON time), this can lead to over heating of the driver if two fans are used together. To avoid this, either the note given above could be used OR duty cycles above 65% could be used OR only one fan can be used. In all these cases, ensure that the inverter heatsink is cooled down to safe limits by the fan.

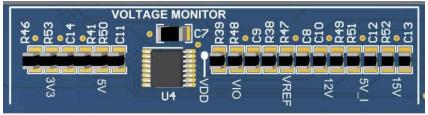

#### 3.1.1.1.1.5 Voltage Monitor

The PMIC module on board the safety MCU control card monitors the power supplies on its control card. The same power supplies are not used by the remainder of the control module. For the safety MCU to monitor all power supplies on the control module, those external power supplies are brought in to the analog channel of the safety MCU through an analog multiplexer. These power supplies include that of C2000 MCU, resolver and gate driver input power supply. The section of mother board hosting this monitoring circuit is shown in 🗵 3-8.

**図** 3-8. External Power Monitoring by Safety MCU

Note

The resistor dividers of various power supplies are designed such that their Thevenin's voltages are apart by few hundred millivolts. The difference should be large enough to avoid overlap with any others even in the worst case variation of their input voltages.

The safety MCU periodically monitors these voltages to ensure their wellness. In the event of any of these voltages moving outside the safe limits, the safety MCU will shutdown the traction inverter and DC-DC converter to safe state.

#### 3.1.1.1.1.6 Resolver Interface Control

Resolver requires an excitation signal and it is sourced by C2000 MCU. There are a couple of choices, either a DAC or a PWM could be used. EPWM8A and DAC-C are the possible sources. An 0 Ohm resistor on R5 will chose DAC as the excitation source whereas a 0 Ohm resistor on R4 will select EPWM8A as the excitation source.

#### **図** 3-9. Resolver Carrier Excitation Source Selection

#### CAUTION

R4 and R5 should not be placed together and are mutually exclusive. Otherwise it may damage the associated DAC and PWM pins of the C2000 MCU.

#### 3.1.1.1.1.7 Test Points on Control Module

There are general purpose analog and digital test points provided on the control mother board for debug purposes. They are listed below.

- **TP1 and TP2** DAC output signal ports for debugging. These two test points are designed to use MMCX connector and coaxial cable for better noise immunity. These are used to display any C2000 variable of user choice. It can help to track intermediate variables in control loops.

- **TP3** VDD. This is the supply voltage of C2000 MCU core.

- TP4 VDDIO This is the supply voltage of C2000 MCU IOs.

- TP5 ERRORSTS This is the error status as reported by C2000 MCU

- **TP6** EN\_DRV This is the power monitor IC (PMIC) output that informs the healthiness of safety MCU power supply. This is used as a drive enabler.

- **TP7 to TP10** Digital ports connected to CLB output Xbar. This helps to display any digital signal that has access to CLB output Xbar besides being a digital port.

#### 3.1.1.1.1.8 General Purpose Ports

The EVM is designed for custom function addressing core functions. In order to provide a certain level of flexibility to the kit to perform or facilitate certain functions, certain test ports are provided on the control mother board. They are shown in  $\boxtimes$  3-10.

☑ 3-10. General Purpose Ports

J18 and J25 are the test ports. They provide limited flexibility as given below

- J18 It can be connected to a potentiometer to provide a variable voltage to an ADC input of C2000. This can be used to control the blower fan speed as the silk screen indicates. Alternately, this analog input can also be used as a means of feeding in variable input for any regulation purposes during development.

- J25 It can provide two different functions

- QEP port interface to a QEP for bench testing with a different motor for evaluating certain algorithms

- SPI port interface to any external SPI connectable devices

#### 3.1.1.1.1.9 Connectors and Headers on Control Mother Board

#### 表 3-1. Connectors and Headers on Control Mother Board

| Connectors and Headers | Description                                                                                                                    |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| J1, J19                | 180 pin HSEC control card to host C2000 MCU control card (TMDSCNCDF28388D)                                                     |  |

| J2                     | 100 pin DIMM connector to host Safety MCU control card (xxx)                                                                   |  |

| J3, J6                 | 10x2 header to connect to inverter module                                                                                      |  |

| J4                     | 4x2 header to connect to inverter module                                                                                       |  |

| J3, J6                 | 0x2 header to connect to inverter module                                                                                       |  |

| J5                     | Samtec 26 pin 50 mil header to connect to DC-DC converter                                                                      |  |

| J7                     | 6x2 header to connect to DC-DC converter                                                                                       |  |

| J8                     | 3 pin header to provide mechanical support to resolver module                                                                  |  |

| J9                     | 7x2 header to connect to resolver module                                                                                       |  |

| J10                    | 3 pin header to provide mechanical support to resolver module besides providing EARTH link to resolver cable through heat sink |  |

| J11, J15               | 2 pin headers to connect to inverter cooling fans                                                                              |  |

| <b>Connectors and Headers</b> | Description                                                                                                                 |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| J12, J17                      | 3 pin headers to provide mechanical support to Dual TCAN1042 module and to provide EARTH link to CAN cable through heatsink |  |  |

| J13                           | 7x2 header to connect to Dual TCAN1042 module                                                                               |  |  |

| J14                           | Power jack receptacle that receives power input to the control module                                                       |  |  |

| J16, J27                      | 14 pin single strip header to connect to analog back end module                                                             |  |  |

| J18                           | 2 pin header to connect to a potentiometer                                                                                  |  |  |

| J20, J21                      | 10x2 header to connect to 5V/ 5A power supply modules                                                                       |  |  |

| J22                           | 7x2 header to connect to TCAN4550 module                                                                                    |  |  |

| J23, J26                      | 3 pin header to provide mechanical support to TCAN4550 module and to provide EARTH link to CAN cable through heat sink      |  |  |

| J24                           | 2 pin header to provide Vbat power supply to TCAN4550 module                                                                |  |  |

| J25                           | 7 pin strip connector carrying QEP / SPI signals for open external interface                                                |  |  |

| J28                           | 14 pin 50 mil Samtec's Tiger Eye terminal strip for ETAS / JTAG interface                                                   |  |  |

| J29, J30                      | 2 pin headers to connect to 12/ 1A power supply                                                                             |  |  |

| J31, J32                      | 2 pin header to connect to 15V / 0.5A power supply                                                                          |  |  |

| J33                           | MMCX-TH Jack connector to connect to DC-DC primary current signal from DC-DC converter                                      |  |  |

| J34                           | 2 pin jumper header to disengage DC-DC safing control                                                                       |  |  |

#### 表 3-1. Connectors and Headers on Control Mother Board (continued)

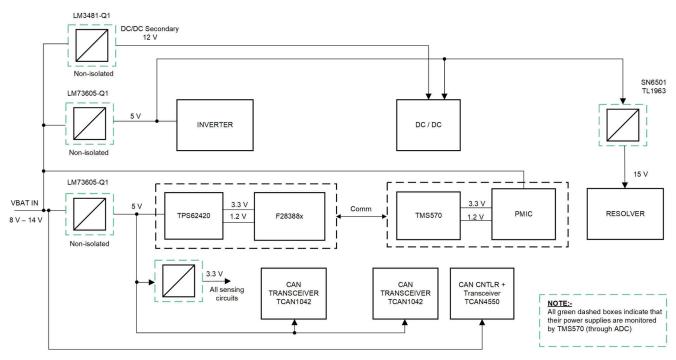

#### 3.1.1.1.2 Power Supplies

Power supply is a critical requirement of the control electronics and is split up into multiple units based on isolation, noise and safety considerations. A brief outline of the power supply distribution diagram is shown in 3-11. Power input to the control electronics is supposed to be from vehicle battery. For lab purposes, a power supply of 12V / 5A rating would be sufficient to feed the controller.

#### 図 3-11. Power supply distribution

An exclusive power supply of 5-V/5-A is designed for the C2000 MCU control card and its associated circuitry. A linear regulator is used to provide 3.3 V for the peripheral modules on the mother board that interacts with C2000 MCU.

Copyright © 2022 Texas Instruments Incorporated

The safety MCU control card takes in the battery voltage of 12 V. This control card has a PMIC (TPS65381A-Q1) that provides the operational voltages needed for the safety MCU and its associated on card circuits.

Another exclusive power supply of 5-V/5-A is designed primarily for generating isolated power supplies for traction inverter gate drivers. This 5-V supply is basically an intermediate stage that helps to simplify the design of subsequent gate driver power supplies. This supply is also used to feed a 15-V power supply for resolver front end and to run a blower fan for cooling inverter heat sink if needed. This power supply can be turned ON / OFF by the control and safety MCUs.

#### A 12-V/1-A power supply is designed to feed the secondary gate drivers of DC-DC converter

Even though these power supplies share the same GND, care is taken to separate the GND planes where ever needed and connecting them together close to the power entry to board. In the sections below, each of the power supply modules are described.

#### 3.1.1.1.2.1 Power Supply 5V /5A

This is a compact power brick based on LM73605-Q1. The design is based off LM73605/ LM73606 EVM User Guide. Detailed design information is available in this user guide. The layout of this module is customized to fit the requirements of this EV traction reference design and is shown in  $\boxtimes$  3-12.

図 3-12. Vbat to 5V/ 5A power supply module

This module has a 3 pin jumper J1. If pins 1 and 2 are connected, then it will automatically deliver 5 V as soon as it gets an input supply. Alternately, if pins 2 and 3 are connected, then it is enabled by the logic level of the signal on pin 6 of connector J3. There are two instances of this module used in the reference design and are mounted on 20 pin connectors J20 and J21 of the control mother board. The power brick mounted on J20 will power the control MCU circuits in the mother board and so it should be ON whenever the power is made available to this unit. Therefore its jumper on J1 should connect pins 2 and 3. The component side of this power brick should face diode D7 on the mother board while mounting.

Note

#### Pin 1 of J1 is facing the board edge

The power brick mounted on J21 will act as an intermediate power stage that helps to power the isolated power supplies for gate drivers and 15 V power supply for resolver. This power supply is designed to be turned ON / OFF by the control and safety MCUs and therefore the jumper on J1 of this brick should connect pins 1 and 2. The component side of this power brick should face diode D7 on the mother board while mounting. It is made available to inverter and resolver modules through connectors J4 and J31 respectively on the mother board.

#### 3.1.1.1.2.2 Power Supply 12-V/1-A

This is a compact SEPIC power module based on LM3481-Q1. The design is based off TI user guide LM3481 SEPIC Evaluation Board. Detailed design information is available in this user guide. The layout of this module is customized to fit the requirements of EV traction reference design and is shown in  $\boxtimes$  3-13.

図 3-13. Vbat to 12-V/1-A Power Supply Module

This module mounts on mother board connectors J29 and J30, with its component side facing the inverter connectors. This will feed the gate driver circuits of DC-DC converter and is made available through connector J7 of mother board.

#### 3.1.1.1.2.3 Power Supply 15-V/0.5-A

This is another compact power module based on SN6501-Q1 and TL1963A-Q1. The design is based off Signal and power isolation with 3.3 V / 5 V input and 12 V / 15 V output. Design information is available in this user guide. The layout of this module is customized to fit the requirements of this EV traction reference design and is shown in  $\boxtimes 3$ -14.

図 3-14. 5-V to 15-V/0.5-A power supply module

This module is fed by the intermediate 5-V power supply and its output will power the resolver module. This module will mount on control mother board connectors J31 and J32 and its component side will face the resolver module connector J9 on mother board.

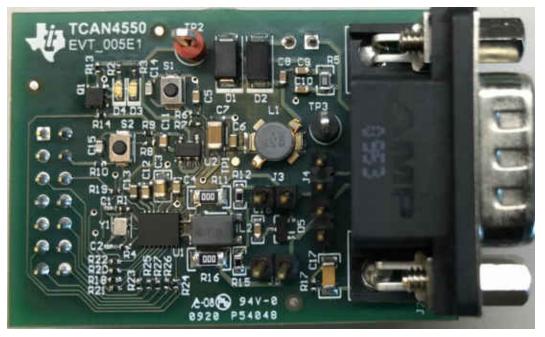

#### 3.1.1.1.3 TCAN4550 module

This module gives CAN-FD feature to safety MCU besides helping to meet signal interface requirements. The module is designed using TCAN4550-Q1 and is based on TCAN4550EVM. The layout of this module is customized to meet the requirements of this EV traction reference design and is shown in  $\boxtimes$  3-15.

図 3-15. TCAN4550 module

It is mounted on connector headers J22, J23, J24 and J26. Header J24 connects the board input power supply to the module, while signals are handled by J22. Headers J23 and J26 provide the EARTH path for noise picked up on TCAN cable.

#### 3.1.1.1.4 Dual TCAN Module

This module provides basic CAN communication interface for both C2000 and Safety MCUs. The module is designed using TCAN1042-Q1 and is based off TCAN Evaluation Module. The schematic and layout of this module are quite simplified to meet the requirements of the EV traction reference design and is shown in  $\boxtimes$  3-16.

🛛 3-16. Dual TCAN module

It is mounted on connector headers J12, J13 and J17. Header J13 connects the 5 V power supply and signals to the module. Headers J12 and J17 provide the EARTH path for noise picked up on TCAN cable.

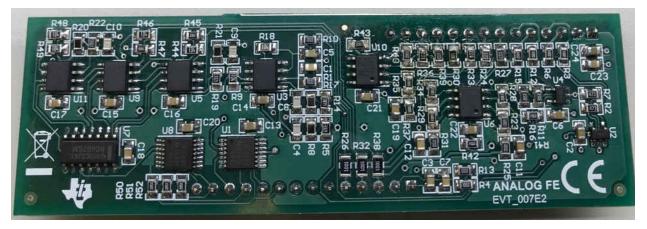

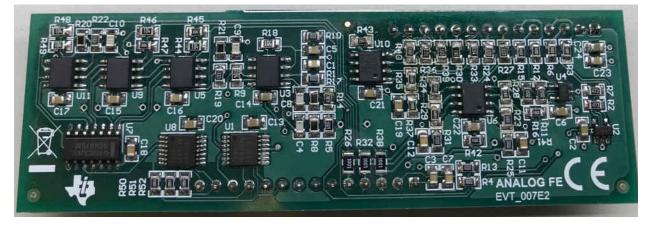

#### 3.1.1.1.5 Analog Back End Module

Analog back end module acts as a back end analog reconstruction module for the differential feedback signals received from the traction inverter module and DC-DC converter module. It is designed using TLV6001 and OPA2350 and other standard linear parts. The module is shown in  $\boxtimes$  3-17.

図 3-17. Analog Back End Module

It is mounted on control mother board headers J16 and J27. Basically this module reconstructs the phase current and DC bus voltage signals of the traction inverter and DC-DC converter into low voltage analog signals. These are fed as ADC inputs for control and safety MCUs in the mother board. Besides, the module also provides a digital status feedback for absolute over current, where the limit can be set by resistors R19, R20, R21 and R22 in this module. A digital status feedback for over voltage is also provided, where the limit is set by resistors R14 and R17. There is also over temperature sensing circuit but is re-purposed to measure the DC-DC converter voltage, and its limit protection is ignored. The limit crossing status are latched and is left for the MCUs to clear them per user choice.

#### 3.1.1.1.6 Resolver Analog Front End Module

Resolver analog front end module deals with all the analog interface requirements of the resolver to work with MCUs. It has two main functions:

- Excitation signal amplification: This module filters the sinusoidal signal generated from MCU via DAC or PWM interface into a smooth sinusoidal excitation carrier signal and amplifies it into appropriate voltage and power level to feed the excitation winding of resolver.

- Feedback signal conditioning: the bipolar sine and cosine outputs of the resolver into unipolar signals to fit within ADC measurement range of MCUs

The module is designed using ALM2402F-Q1 and standard linear parts. ALM2402F-Q1 is a dual channel high power operational amplifier with integrated protection for resolver against current limit and over temperature. The module is shown in  $\boxtimes$  3-18.

図 3-18. Resolver Analog Front End Module

It is mounted on control mother board headers J8, J9 and J10. All power and signals are flow through J9, while J10 provides EARTH access to noise signals picked by resolver cable. J8 provides mechanical support for the module. The module has a multiplexer CD4053B-Q1 that helps to cross feed the sine and cosine signals into ADC to verify signal and channel integrity to ensure safe estimation of rotor position. The module also interfaces with resolver thermistor and provides an analog signal representing resolver temperature for the MCUs to track.

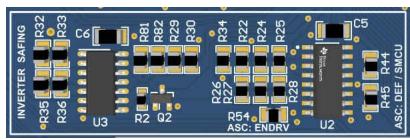

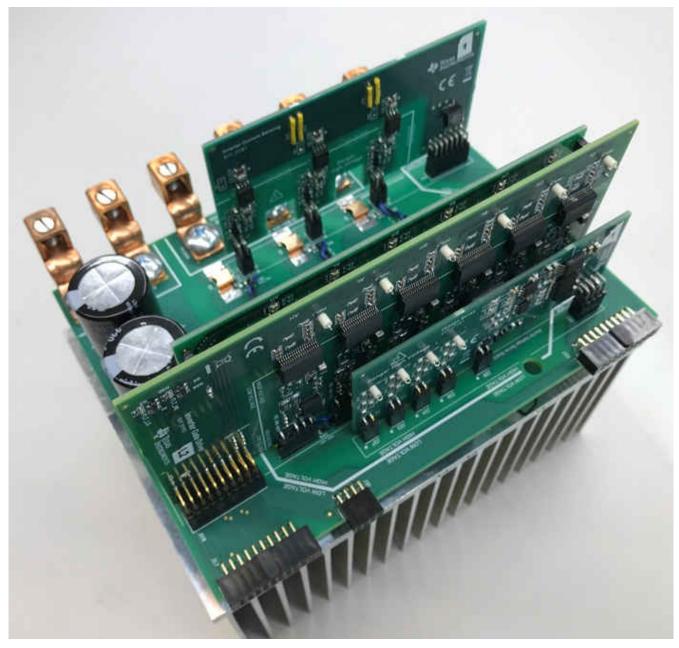

#### 3.1.1.2 Inverter Module

Inverter module is used to power the traction motor to run at a certain torque. It is a separate module that plugs into control mother board to receive control power and signals and to send back inverter voltage and current sense signals as feedback. It consists of various sub-modules for various functions as listed below

- 1. Inverter Mother Board

- 2. UCC5870 ASIL-D Gate Driver Module

- 3. Gate Drive Power Supply Module

- 4. Voltage Sense Module

- 5. Current Sense Module

A block diagram of the traction inverter sub-system is shown in  $\boxtimes$  3-19.

図 3-19. EV Traction Inverter System Block Diagram

A fully assembled picture of inverter module is shown in  $\boxtimes$  3-20. Details of various sub-modules will be discussed in subsequent sections

🗷 3-20. Inverter Module

The inverter module mounts flat on headers J3, J4 and J6 of control mother board.

#### 3.1.1.2.1 Inverter Mother Board

Inverter mother board is the host board in inverter module. It consists of a 3-phase SiC inverter module rated at 1200V/ 50A, a heat-sink and a blower fan for thermal dissipation. Certain functions of the inverter module are realized on separate daughter cards or sub modules that would plug into inverter mother board. This helps with easy debugging and to easily replace modules in case of error or if improvements are needed. It has various connectors to connect to the control module and various sub modules. Besides it has appropriate PCB terminations for mounting high power lugs to feed in high power DC and to draw high power inverter output to motor. Here below is the list of modules it supports

- 1. UCC5870 ASIL-D Gate Driver Module

- 2. Voltage Sense Module

- 3. Current Sense Module

The inverter mother board is shown in  $\boxtimes$  3-21.

図 3-21. Inverter Mother Board

The inverter mother board is fabricated with 2-oz copper on either side and high current traces / planes are parallel routed on either sides to give a 4oz effective thickness. Its connectors J17, J21 and J22 will mate with control mother board headers J3, J4 and J6 to receive control signals and send feedback signals.

#### 3.1.1.2.1.1 Connectors and Headers on Inverter Mother Board

| 致 5-2. Connectors and Headers on inverter Mother Board |                                                                                              |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| <b>Connectors and Headers</b>                          | Description                                                                                  |  |

| J1, J3, J6, J18                                        | 5 pin 100mil socket header (polarized open in 2nd position) to connect to gate driver module |  |

| J5, J8, J11                                            | 2x2 100mil socket header to connect to current sense module                                  |  |

| J10, J13                                               | 4 pin 100mil socket header (polarized open in 2nd position) to connect to gate driver module |  |

| J15                                                    | 2 pin socket header to connect to gate driver module                                         |  |

| J16                                                    | 4x2 socket header to connect to current sense module                                         |  |

| J17, J22                                               | 10x2 right angle socket header to connect to control mother board                            |  |

| J19                                                    | 10x3 socket header to connect to gate driver module                                          |  |

| J20                                                    | 4x2 socket header to connect to voltage sense module                                         |  |

| J21                                                    | 4x2 right angle socket header to connect to control mother board                             |  |

| J23, J24, J25, J26, J27                                | 2 pin strip socket header to connect to voltage sense module                                 |  |

| T1, T2, T3, T4, T5, T6                                 | Lug terminal pads on PCB to connect to HV power supply, traction motor and EARTH             |  |

|                                                        |                                                                                              |  |

#### 表 3-2. Connectors and Headers on Inverter Mother Board

#### 3.1.1.2.1.2 Jumper and Test Points on Inverter Module

Some test points are provided on the inverter module for debug purposes, especially on all gate drive pins of the SiC inverter power module. While some other test points are used to make connections between them, essentially acting as jumper points.

#### 表 3-3. Jumper Points Table

| Jumper Points | Purpose                                                                                                                   |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| TP1 and TP2   | Connecting DC bus voltage Vdc to gate driver module to facilitate protection of high side switches by gate driver UCC5870 |  |  |

| TP3 and TP7   | Connecting isolated 15V + for phase A. Needed to feed hot side power supply for isolated current sensing of phase A       |  |  |

| TP4 and TP8   | Connecting isolated 15V - for phase A *                                                                                   |  |  |

| TP5 and TP6   | Connecting isolated 15V + for phase B. Needed to feed hot side power supply for isolated current sensing of phase B       |  |  |

| TP11 and TP12 | Connecting isolated 15V - for phase B *                                                                                   |  |  |

| TP9 and TP10  | Connecting isolated 15V + for phase C. Needed to feed hot side power supply for isolated current sensing of phase C       |  |  |

**TRUMENTS**

www.tij.co.jp

| 表 3-3. Jumper Points Table (continued) |                                         |  |

|----------------------------------------|-----------------------------------------|--|

| Jumper Points Purpose                  |                                         |  |

| TP13 and TP14                          | Connecting isolated 15V - for phase C * |  |

| 委 3-4. IEST POINTS TABLE Test Points Signal Name |                                           |  |  |

|--------------------------------------------------|-------------------------------------------|--|--|

| TP15 and TP16                                    | Gate and Source respectively of switch AH |  |  |

| TP17 and TP18                                    | Gate and Source respectively of switch BH |  |  |

| TP19 and TP20                                    | Gate and Source respectively of switch CH |  |  |

| TP21 and TP22                                    | Gate and Source respectively of switch AL |  |  |

| TP23 and TP24                                    | Gate and Source respectively of switch BL |  |  |

| TP25 and TP26                                    | Gate and Source respectively of switch CL |  |  |

### 表 3-4. Test Points Table

#### 3.1.1.2.2 Inverter Gate Driver Module

The gate driver module is built using UCC5870-Q1 isolated gate driver. The UCC5870-Q1 device is a functional safety compliant, isolated, highly configurable single channel gate driver targeted to drive high power SiC MOSFETs and IGBTs in EV/HEV applications. Power transistor protections such as shunt resistor based overcurrent, NTC based over-temperature, and DESAT detection, including selectable soft turn off or two-level turn off during these faults are available. It is capable of sourcing and sinking 15 A of gate drive current, supporting highly capacitive high current, high voltage power switches and also integrates a 4A active Miller clamp during switching, and an active gate pull-down while the driver lost power. The gate driver operation mode and protection functionality is programmed at power-up via SPI by C2000 MCU. It uses SPI for verification, supervision, and diagnosis as well. Since there is a higher integration of diagnostics and detection functions, it simplifies the design of ISO 26262 ASIL D compliant systems.

The design of gate driver board is based on UCC5870QDWJEVM-026 Evaluation Module User's Guide. Detailed design information is available in this user guide. Due to the compact form factor of power module, all gate drivers are designed into a single board to optimize the trace lengths while ensuring appropriate and safe spatial distances between each driver stage as shown in 🛛 3-22.

#### 図 3-22. UCC5870 Gate Driver Module

Interface to MCU is done through a 3x10 header that links the PWM, SPI signals from MCU to UCC5870s and nFLT signals from UCC5870s to MCU. As the size of gate driver board is restricted, a separate power supply module is designed to cater to isolated power supply requirements of the secondary side of gate drivers. This power supply module is mounted on the rear side of gate driver board on its headers J2, J4, J4\_x and two additional headers (J3, J6) for mechanical support to make the gate driver module.

The gate driver module is mounted on inverter mother board socket headers J1, J3, J6, J10, J13, J15, J18 and J19.

#### 3.1.1.2.2.1 Inverter Gate Drive Power Supply Module

Isolated gate drive power supply for the secondaries of all UCC5870s are designed in a separate board and mounted on the back of gate driver card. This is to reduce contact lengths between power supplies and gate driver secondary circuits. This module is designed using SN6501-Q1 and is based on the *HEV/EV Traction Inverter Power Stage with 3 Types of IGBT/SiCBias-Supply Solutions reference design*. The chosen secondary voltages are +18 V and -4 V and current rating of about 180mA. The supply can cater to momentary current spike demand using the energy stored in its output capacitor.

The power supply is designed based on a regulated 5 V input with no secondary regulation. It generates a fixed boost secondary voltage. For the given load level of power supplies, secondary regulation is not considered mandatory. The six power supplies are designed on a single board with sufficient spacing between them to ensure safe voltage compliance. A picture of the board is shown in  $\boxtimes$  3-23.

図 3-23. Gate Driver Power Supply Module

Gate drive power supply module is mounted on the rear side of gate drive board on headers J2, J4\_x, J3 and J6. J4\_x is a 3 pin connector used that takes in the power supply for each driver. J3 and J6 are non-electric connectors whose only intent is to provide mechanical stability and spacing in the mated position between the gate driver and gate drive power supply boards.

#### 3.1.1.2.3 Inverter Current Sense Module

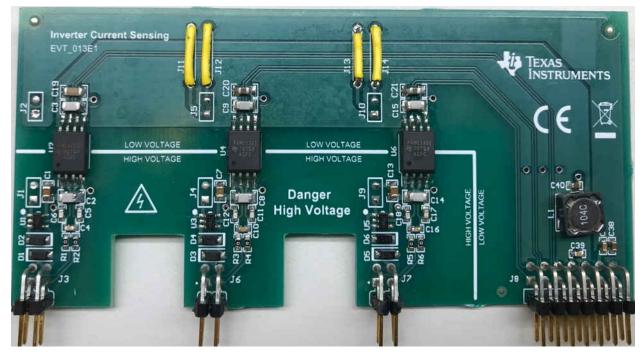

Current sense module is designed to provide isolated differential analog feedback of inverter phase currents. This is designed using isolation amplifier AMC1302-Q1 and is based on AMC130x Evaluation Module. A picture of this board is shown in 🛛 3-24.

図 3-24. Inverter Current Sense Board

AMC1302 measures phase current by measuring voltage drop across a shunt resistor. Since its designed input voltage range is  $\pm$ 50mV, a low value shunt resistor is only needed thereby leading to a lower power dissipation. It has a fixed gain with low drift: 41  $\pm$  0.3%,  $\pm$ 50 ppm/°C, low input offset and drift of, low non-linearity and drift, output bandwidth above 200KHz and a rise time/fall time of sub 2µs. All these features make it suitable for this application.

AMC1302 will require separate power supplies for the high voltage (HOT) and low voltage (COLD) sides. Isolated power supply for the HOT side of AMC1302 for each phase is derived from that phase's high side gate drive's secondary power supply (AH, BH, CH) and drop regulated to 3.3 V. Alternately, using the intermediate 5 V power supply routed to this board via J8, supplementary 5 V to 5 V isolated modules can be mounted on its headers J1, and J2, J4 and J5 and J9 and J10 for phases A, B and C respectively. COLD side power supply is provided from control mother board on a 8x2 header. This module is mounted on headers J5, J8, J11 and J16 of the inverter mother board. Feedback signals are brought out to 8x2 connector J16 of the inverter mother board.

| Header  | Description                                                       |  |

|---------|-------------------------------------------------------------------|--|

| J1, J2  | Backup 5 V to Iso 5 V module for phase A hot current sensing side |  |

| J4, J5  | ackup 5 V to Iso 5 V module for phase B hot current sensing side  |  |

| J9, J10 | Backup 5 V to Iso 5V module for phase C hot current sensing side  |  |

#### 表 3-5. Supplemental Headers

#### 3.1.1.2.4 Inverter Voltage Sense Module

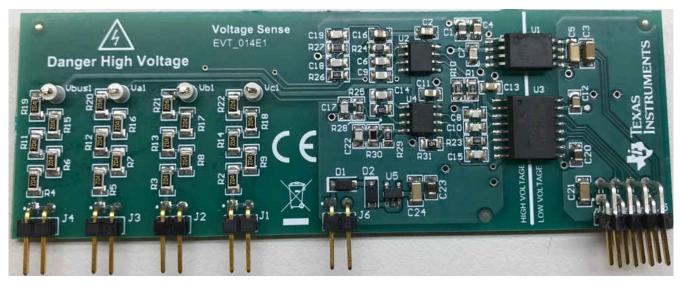

Voltage sense module is designed to provide digital feedback of inverter phase output voltages and analog feedback of DC bus voltage. All feedback signals are isolated. Digital feedback is provided by ISO7240CF-Q1 and some standard linear parts. Analog differential feedback is provided by TI's isolation amplifier AMC1311-Q1 and is based on  $\pm$ 480-V isolated voltage-sensing circuit with differential output. A picture of this board is shown in  $\boxtimes$  3-25.

図 3-25. Inverter Voltage Sense Board

AMC1311 provides a good linear performance for an input voltage range of 2 V with high source impedance. It has low offset error and drift, fixed gain of 1 with very low gain error and drift and low non-linearity and drift, and has an output bandwidth of above 200 KHz. For DC measurement, this is substantially superior.

AMC1311 requires separate power supplies for the high voltage (HOT) and low voltage (COLD) sides. Isolated power supply for the HOT side of AMC1311 is derived from one of the low side gate drive's secondary power supply (CL) and drop regulated to 3.3 V. COLD side power supply is fed in through a 4x2 connector. This module is mounted on headers J20, J23, J24, J25, J26 and J27 of the inverter mother board. Feedback signals are brought out to 4x2 connector J20 of the inverter mother board.

## 3.1.1.3 DC-DC Bidirectional Converter Module

The bi-directional DC-DC converter module is designed to charge the LV battery from HV battery bus when operate in forward direction and per-charge the DC bus capacitor in reverse direction. It is a separate module that plugs into control mother board to receive control power and signals and to send back inverter voltage and current sense signals as feedback. It consists of a main board and two gate driver daughter boards for isolated primary gate driver and power supply.

A block diagram of the traction inverter sub-system is shown in  $\boxtimes$  3-26.

図 3-26. DC-DC System Block Diagram

A fully assembled picture of inverter module is shown in  $\boxtimes$  3-27. Details of various sub-modules will be discussed in subsequent sections.

図 3-27. DC-DC Converter Module

#### 3.1.1.3.1 DC-DC Converter Mother Board

The DC-DC sub-system is designed to take 400V normal HV input. After input filter and capacitor, it drives a SiC full bridge, with a inductor between the center point of left lag and main transformer primary. Current transformer of 100:1 ratio is used for primary inductor current sensing for PCMC control. The characteristic of the main transformer can be found in  $\pm$  3-6.

| Item      | L (1-2)    | L (1-2)  | L (1-2)  | Dielectric Strength / |

|-----------|------------|----------|----------|-----------------------|

|           | @100kHz/1V | @15A     | DCR      | Hi-pot (Vac):         |

|           | (µH)       | (µH)     | (mΩ)     |                       |

| VI-19152B | 3.1 TYP.   | 3.1 TYP. | 2.0 TYP. | 2500                  |

#### 表 3-6. Characteristic of Main Transformer

The secondary is designed to be current doubler topology, with 4 MOSFET in parallel for each lag to carry the high current on LV output. Output current is measured with a set of parallel shunt resistor. Since the negative output has a long path on the PCB and high current, a high current bus-bar is designed to carry current between the MOSFETs and the output terminal (mounted on back side of the board).

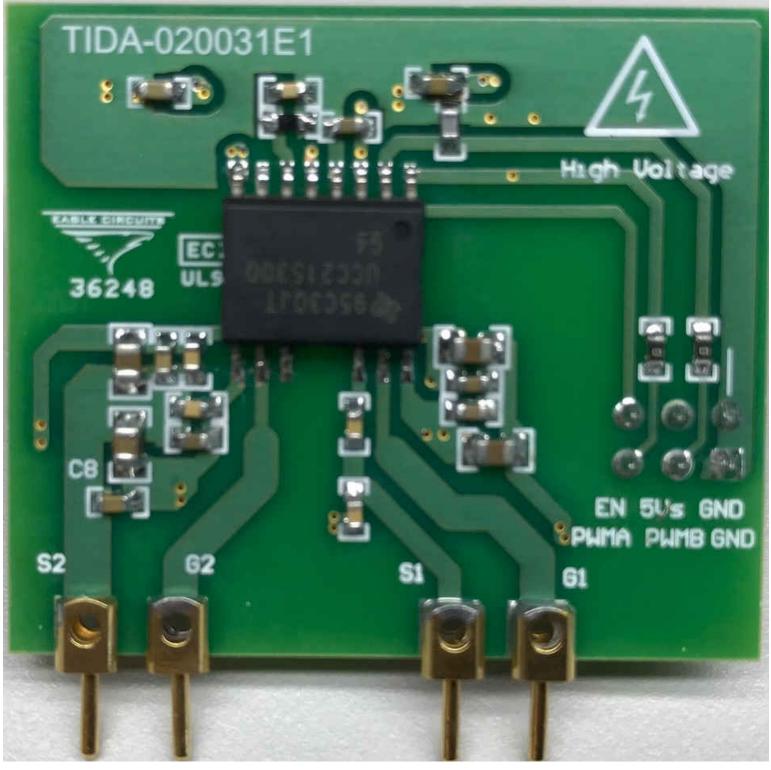

#### 3.1.1.3.2 DC-DC Gate Driver Module

Isolated gate drive module for DC-DC is designed as a separate daughter card to drive a high voltage halfbridge. This is to reduce contact lengths between power supplies and gate driver secondary circuits and reduce routing complexity. This module is designed using UCC21530-Q1 isolated half bridge gate driver and SN6505-Q1 isolated power supply driver. The UCC21530 supports enable function which allows the MCU to disable power stage independent of PWM output. The isolated power supply is designed with a second layer of enable and designed to generate gate drive voltages of +15 V and -4 V for the SiC MOSFET selected for the primary full bridge. The power supply is designed based on a regulated 5 V input with no secondary regulation. A picture of the board is shown in 🛛 3-28.

## 図 3-28. DC-DC Isolated Gate Driver

## 3.2 Resource Mapping

This section describes the pin mapping of C2000 and Safety MCUs for target functions.

| 表 3-7. Functional mapping of Digital Signals of C2000 MCU |          |                                    |                                         |

|-----------------------------------------------------------|----------|------------------------------------|-----------------------------------------|

| SIGNAL NAME                                               | MCU GPIO | MCU PERIPHERAL LINKED WITH<br>GPIO | FUNCTION                                |

| IN+A                                                      | 0        | EPWM 1A                            | PWM for inverter phase A high side      |

| IN-A                                                      | 1        | EPWM 1B                            | PWM for inverter phase A low side       |

| IN+B                                                      | 2        | EPWM 2A                            | PWM for inverter phase B high side      |

| IN-B                                                      | 3        | EPWM 2B                            | PWM for inverter phase B low side       |

| IN+C                                                      | 4        | EPWM 3A                            | PWM for inverter phase C high side      |

| IN-C                                                      | 5        | EPWM 3B                            | PWM for inverter phase C low side       |

| PWMA                                                      | 6        | EPWM 4A                            | PWM for DC-DC primary phase A high side |

| PWMB                                                      | 7        | EPWM 4B                            | PWM for DC-DC primary phase A low side  |

| PWMC                                                      | 8        | EPWM 5A                            | PWM for DC-DC primary phase B high side |

| PWMD                                                      | 9        | EPWM 5B                            | PWM for DC-DC primary phase B low side  |

| PWME                                                      | 10       | EPWM 6A                            | PWM for DC-DC secondary side A          |

| PWMF (option-1)                                           | 11       | EPWM 6B                            | PWM for DC-DC secondary side B          |

| PWMF (option-2)                                           | 12       | EPWM 7A                            | PWM for DC-DC secondary side (backup)   |

| DC_DC_ENABLE                                              | 13       | GPIO                               | Enable DC-DC                            |

| Resolver Exc (Option)                                     | 14       | EPWM 8A                            | PWM for resolver carrier excitation     |

| C2K_SoC_SYNC                                              | 15       | GPIO                               | Sync to SMCU for ADCSoC from C2000      |

| SDI                                                       | 24       | SPIB-SIMO                          | SPI link to UCC5870 gate drivers        |

| SDO                                                       | 25       | SPIB-SOMI                          | SPI link to UCC5870 gate drivers        |

| CLK                                                       | 26       | SPIB-CLK                           | SPI link to UCC5870 gate drivers        |

| nCS                                                       | 27       | SPIB-STE                           | SPI link to UCC5870 gate drivers        |

| TP10                                                      | 35       | GPIO / Output XBAR                 | Test point for monitoring               |

| TP9                                                       | 36       | GPIO / Output XBAR                 | Test point for monitoring               |

| TP8                                                       | 37       | GPIO / Output XBAR                 | Test point for monitoring               |

| TP7                                                       | 38       | GPIO / Output XBAR                 | Test point for monitoring               |

| CTRL                                                      | 41       | GPIO                               | Resolver - analog mux control           |

| VinvA                                                     | 48       | GPIO                               | Inverter output A digital status        |

| VinvB                                                     | 96       | GPIO                               | Inverter output B digital status        |

| VinvC                                                     | 98       | GPIO                               | Inverter output C digital status        |

| FSITX_D0                                                  | 49       | FSI                                | Interface to ETAS / JTAG header         |

| FSITX_D1                                                  | 50       | FSI                                | Interface to ETAS / JTAG header         |

| FSITX_CLK                                                 | 51       | FSI                                | Interface to ETAS / JTAG header         |

| INH                                                       | 52       | GPIO                               | Resolver - analog mux inhibit           |

| OT/SHDN                                                   | 53       | GPIO                               | Resolver - Exc amp ALM2403 status       |

| QEPA                                                      | 54       | QEP / SPI                          | Test port for QEP or SPI (optional)     |

| QEPB                                                      | 55       | QEP / SPI                          | Test port for QEP or SPI (optional)     |

| QEPS                                                      | 56       | QEP / SPI                          | Test port for QEP or SPI (optional)     |

| QEPI                                                      | 57       | QEP / SPI                          | Test port for QEP or SPI (optional)     |

| PMIC_DRVEN                                                | 58       | GPIO                               | FuSa signal from SMCU                   |

| nSTB                                                      | 60       | CAN                                | CAN interface                           |

|                                                           |          |                                    |                                         |

JAJU806 – APRIL 2021 Submit Document Feedback ASIL D 安全性コンセプト検証済み、高速トラクション、双方向 DC/DC 変換のリファ 31 レンス・デザイン

| 表 3-7. Functional mapping of Digital Signals of C2000 MCU (continued) |          |                                    |                                              |

|-----------------------------------------------------------------------|----------|------------------------------------|----------------------------------------------|

| SIGNAL NAME                                                           | MCU GPIO | MCU PERIPHERAL LINKED WITH<br>GPIO | FUNCTION                                     |

| TxD                                                                   | 61       | CAN                                | CAN interface                                |

| RxD                                                                   | 62       | CAN                                | CAN interface                                |

| C2K PS EN                                                             | 64       | GPIO                               | 5V IPS enable (int power supply)             |

| Clr_OXP_latch                                                         | 66       | GPIO                               | Clear OCP/OVP latched fault on ABE           |

| OVP_latch                                                             | 68       | GPIO                               | OVP latched fault from ABE                   |

| SCI - C2K_TX - SM_RX                                                  | 70       | SCI                                | Serial comm with SMCU                        |

| SCI - C2K_RX - SM_TX                                                  | 71       | SCI                                | Serial comm with SMCU                        |

| OVP                                                                   | 74       | GPIO                               | OVP from hot side sensing                    |

| OTP_Latch                                                             | 78       | GPIO                               | OTP latched fault from ABE                   |

| OCP_Latch                                                             | 82       | GPIO                               | OCP latched fault from ABE                   |

| ASC_EN                                                                | 86       | GPIO                               | ASC enable for UCC5870 drivers               |

| ASC_L                                                                 | 88       | GPIO                               | ASC low side control of UCC5870              |

| ASC_H                                                                 | 90       | GPIO                               | ASC high side control of UCC5870             |

| nFLT2_L                                                               | 92       | GPIO                               | Secondary fault status of low side UCC5870s  |

| nFLT1_L                                                               | 94       | GPIO                               | Primary fault status of low side UCC5870s    |

| nFLT2_H                                                               | 127      | GPIO                               | Secondary fault status of high side UCC5870s |

| nFLT1_H                                                               | 147      | GPIO                               | Primary fault status of high side UCC5870s   |

#### 表 3-7 Functional mapping of Digital Signals of C2000 MCII (continued)

### 表 3-8. Functional mapping of Analog Signals of C2000 MCU

| SIGNAL NAME      | ANALOG CHANNEL | FUNCTION                                  |

|------------------|----------------|-------------------------------------------|

| TP2              | A0             | General purpose DAC                       |

| TP1              | A1             | General purpose DAC                       |

| VdcFbk           | A2             | HV DC feedback signal                     |

| VREF1/2          | A3             | Resolver sin/cos level shift              |

| lfb_A            | A4             | Inverter phase current A                  |

| Temp2            | A5             | DC-DC transformer temparature             |

| CT_OUT           | A14            | DC-DC primary side CT current             |

| Vfb_Vo2          | В0             | DC-DC secondary output voltage            |

| EXC              | B1             | Resolver carrier exc DAC                  |

| Vfb_lo / Vfb_lo2 | B2             | DC-DC secondary current                   |

| Vfb_lo           | В3             | DC-DC secondary current                   |

| NTC              | B4             | Resolver temperature from NTC             |

| Temp1            | B5             | DC-DC heatsink temperature                |

| lfb_C            | C2             | Inverter phase current C                  |

| Vdc2Fbk          | C3             | HV DC redundant feedback signal           |

| OEXC             | C4             | Resolver excitation feedback              |

| OCOS             | C5             | Resolver cosine feedback                  |

| lfb_B            | D0             | Inverter phase current B                  |

| Vfb_Vo           | D2             | DC DC secondary output voltage            |

| ΤοΡΟΤ            | D3             | General purpose external input from a pot |

| OSIN             | D5             | Resolver sine feedback                    |

|                      |      | apping of Digital Signals      |                                              |

|----------------------|------|--------------------------------|----------------------------------------------|

| SIGNAM NAME          | GPIO | PERIPHERAL LINKED<br>WITH GPIO | FUNCTION                                     |

| nFLT2_H              | 0    |                                | Secondary fault status of high side UCC5870s |

| nFLT2_L              | 1    |                                | Secondary fault status of low side UCC5870s  |

| nFLT1_H              | 2    |                                | Primary fault status of high side UCC5870s   |

| nFLT1_L              | 3    |                                | Primary fault status of low side UCC5870s    |

| OTP_Latch            | 4    |                                | OTP latched fault from ABE                   |

| OCP_Latch            | 5    |                                | OCP latched fault from ABE                   |

| OVP                  | 6    |                                | OVP from protection logic                    |

| ASC_H                | 7    |                                | ASC high side control of UCC5870             |

| ASC_L                | 8    |                                | ASC low side control of UCC5870              |

| ASC_EN               | 9    |                                | ASC enable for UCC5870 drivers               |

| PM_MUXA              | 10   |                                | Power monitor analog mux sel A               |

| PM_MUXB              | 11   |                                | Power monitor analog mux sel B               |

| MUX_INH              | 85   |                                | Power monitor analog mux inhibit             |

| CAN_GPO2             | 12   |                                | TCAN4550 interface                           |

| CAN_GPO1             | 14   |                                | TCAN4550 interface                           |

| CAN_nINT             | 15   |                                | TCAN4550 interface                           |

| SPI_MOSI             | 16   | SPI                            | TCAN4550 interface                           |

| SPI_MISO             | 17   | SPI                            | TCAN4550 interface                           |

| SPI_CLK              | 18   | SPI                            | TCAN4550 interface                           |

| SPI_CS               | 19   | SPI                            | TCAN4550 interface                           |

| GPIO_RST             | 33   |                                | TCAN4550 interface                           |

| SM PS EN             | 23   |                                | 5V IPS enable (int power supply)             |

| C2K RST              | 24   |                                | Reset C2000 MCU                              |

| VinvA                | 25   | ECAP                           | Inverter output A digital status             |

| VinvB                | 48   | ECAP                           | Inverter output B digital status             |

| VinvC                | 49   | ECAP                           | Inverter output C digital status             |

| SCI - C2K_TX - SM_RX | 28   | UART                           | SCI comm with C2K                            |

| SCI - C2K_RX - SM_TX | 29   | UART                           | SCI comm with C2K                            |

| RxD2                 | 30   | CAN                            | CAN interface                                |

| TxD2                 | 31   | CAN                            | CAN interface                                |

| nSTB2                | 34   | CAN                            | CAN interface                                |

| C2K_SoC_SYNC         | 32   |                                | SoC Sync from C2K                            |

| DC_DC_ENABLE         | 59   |                                | Enable DC-DC                                 |

| Clr_OXP_latch        | 60   |                                | Clear OCP/OVP latched fault on ABE           |

| C2K_ERRSTS           | 86   |                                | Error status signal from C2K                 |

| EN DRV               | 87   |                                | PMIC signal                                  |

### 表 3-9. Functional Mapping of Digital Signals of TMS570LS1227

## 表 3-10. Functional ,Mapping of Analog Signals of Safety MCU

| SIGNAL NAME | ANALOG CHANNEL | FUNCTION                      |

|-------------|----------------|-------------------------------|

| VdcFbk      | ADINA0         | HV DC feedback signal         |

| lfb_A       | ADINA1         | Inverter phase current A      |

| NTC         | ADINA2         | Resolver temperature from NTC |

| OSIN        | ADINA3         | Resolver sine feedback        |

| 1-COM       | ADINA4         | Power monitor analog mux COM1 |

| lfb_B       | ADINB0         | Inverter phase current B      |

JAJU806 – APRIL 2021 Submit Document Feedback ASIL D 安全性コンセプト検証済み、高速トラクション、双方向 DC/DC 変換のリファ 33 レンス・デザイン

English Document: TIDUEY6 Copyright © 2022 Texas Instruments Incorporated

| 表 3-10. Functional ,Mapping of Analog Signals of Safety MCU (continued) |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

| SIGNAL NAME | ANALOG CHANNEL | FUNCTION                        |

|-------------|----------------|---------------------------------|

| lfb_C       | ADINB1         | Inverter phase current C        |

| OEXC        | ADINB2         | Resolver excitation feedback    |

| OCOS        | ADINB3         | Resolver cosine feedback        |

| 2-COM       | ADINB4         | Power monitor analog mux COM2   |

| Vdc2Fbk     | ADINB5         | HV DC redundant feedback signal |

| Vfb_Vo2     | ADINB6         | DC-DC secondary output voltage  |

| Vfb_Vo      | ADINB7         | DC DC secondary output voltage  |

## 3.3 Test Setup

Items not included in the list but needed for evaluation are:

- 1. Power supply (or 12-V battery) to drive control electronics

- 2. Traction motor

- 3. High voltage DC power supply

- 4. High current electronic load

#### 3.4 Test Results

The traction inverter is tested with a 3-pole pair Internal Permanent Magnet Synchronous Reluctance Motor (IPM-SynRM), with 450-V DC input. The motor can run at 17,000 RPM at 50A current and can run up to 20,000 RPM with up to 200A phase current.

The efficiency of the HV-LV DC-DC converter is measured under 400 V input and 12 V output condition with output current up to 150 A. The synchronous rectification (SR) scheme is enabled. The peak efficiency is around 95.5%.

# 4 General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

Always follow TI's setup and application instructions, including use of all interface components within their recommended electrical rated voltage and power limits. Always use electrical safety precautions to help ensure your personal safety and those working around you. Contact TI's Product Information Center http://support/ti./com for further information.

#### Save all warnings and instructions for future reference.

#### WARNING

Failure to follow warnings and instructions may result in personal injury, property damage or death due to electrical shock and burn hazards.

The term TI HV EVM refers to an electronic device typically provided as an open framed, unenclosed printed circuit board assembly. It is *intended strictly for use in development laboratory environments, solely for qualified professional users having training, expertise and knowledge of electrical safety risks in development and application of high voltage electrical circuits. Any other use and/or application are strictly prohibited by Texas Instruments.* If you are not suitable qualified, you should immediately stop from further use of the HV EVM.

- 1. Work Area Safety

- a. Keep work area clean and orderly.

- b. Qualified observer(s) must be present anytime circuits are energized.

- c. Effective barriers and signage must be present in the area where the TI HV EVM and its interface electronics are energized, indicating operation of accessible high voltages may be present, for the purpose of protecting inadvertent access.

- d. All interface circuits, power supplies, evaluation modules, instruments, meters, scopes and other related apparatus used in a development environment exceeding 50Vrms/75VDC must be electrically located within a protected Emergency Power Off EPO protected power strip.

- e. Use stable and non conductive work surface.

- f. Use adequately insulated clamps and wires to attach measurement probes and instruments. No freehand testing whenever possible.

- 2. Electrical Safety

As a precautionary measure, it is always a good engineering practice to assume that the entire EVM may have fully accessible and active high voltages.

- a. De-energize the TI HV EVM and all its inputs, outputs and electrical loads before performing any electrical or other diagnostic measurements. Re-validate that TI HV EVM power has been safely de-energized.