Design Guide: TIDA-010072

# 呼吸アプリケーション用の空気ブロワおよびバルブ制御のリファレ ンス・デザイン

# TEXAS INSTRUMENTS

# 概要

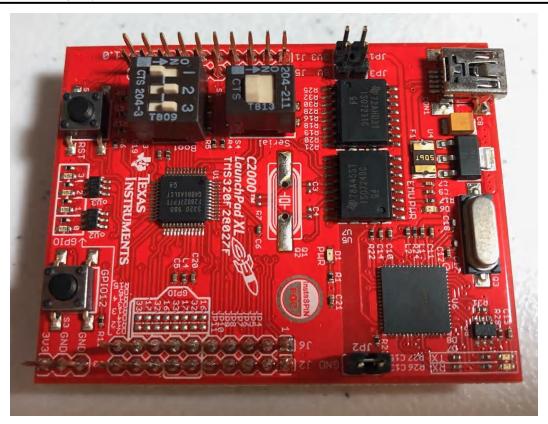

このリファレンス・デザインでは、最大 ±200kRPM/s のレートでモーターの加速と減速をサポートする、コンパクトなシステムの設計を示します。この加減速レートは、多くの呼吸器アプリケーションにとって重要な要件です。この設計は、TMS320F28027F など多数のオフボード C2000 コントローラをサポートしており、低コストのセンサレス FOC (フィールド・オリエンテッド制御) を実現できます。加えて、この設計は広い入力電圧範囲 (6~28V) もサポートしており、レギュレートされたライン電源とバッテリ電源の両方に対応できます。この設計では、空気ブロワやバルブを駆動するため、DRV8323R スマート・ゲート・ドライバとDRV8847 モーター・ドライバをそれぞれ使用しています。

# リソース

TIDA-010072 デザイン・フォルダ

DRV8323R、DRV8847 プロダクト・フォルダ

LM5122、LMR33630 プロダクト・フォルダ

MSP430FR2155、TMP1075 プロダクト・フォルダ

TPS62840、TPS7A02 プロダクト・フォルダ

Ask our TI E2E™ support experts

# 特長

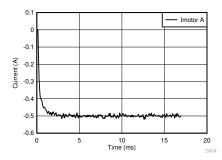

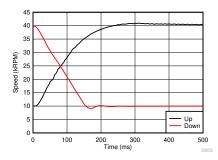

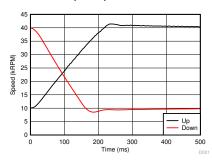

- 最大 ±200kRPM/s の迅速な加速と減速

- 250ms の期間で 10kRPM から 40kRPM への速度変 更が可能 (C65MS1-L5)

- 200ms の期間で 40kRPM から 10kRPM への速度変 更が可能 (C65MS1-L5)

- 広い入力電圧範囲 (6~28V) をサポートしており、レギュレートされた DC 入力とバッテリ入力に対応できるほか、電源保護機能の搭載によりサージ、過電流、逆極性から保護

- DRV8323R モーター・ドライバと、オフボードの FOC 制御機能とを組み合わせることにより、静かで効率的 に圧縮空気を生成

- UVLO、過電流、過熱などのドライバ保護機能を内蔵

- デュアル DRV8847 H ブリッジ・ステッパ・ドライバにより 6 個のソレノイド・バルブを制御

# アプリケーション

- 呼吸補助装置

- 麻酔供給システム

- CPAP マシン

- 酸素濃縮器

# 1 System Description

# 1.1 Medical Respiratory Systems

There are several instances where it may become medically necessary for machines to assist with patient respiration, and these machines may require motors and valves depending on the specific application. For example, ventilators use motors to generate pressurized air and a system of valves to either deliver pressurized air or release air in the lungs back to the atmosphere to mechanically assist respiration. Ventilators can also be coupled with anesthesia delivery systems to keep the patient in a safe and anesthetized state. Anesthesia delivery systems incorporate numerous valves for drug mixing and patient protection. Ventilators are typically used in hospital, institutional, transport, and home environments.

There are three basic drive mechanisms in a ventilator system: bellows, piston, and turbine. For a bellows system, typically the air compression of a bellows is from a pneumatic force controlled by servo valves. For a piston system, typically the air compression is achieved from a BLDC or DC servo motor to move a piston. For a turbine system, typically a BLDC motor is used to drive a turbine (blower).

図 1-1. Ventilator system showing patient vital parameters

The key system requirements for a ventilator system are shown in 表 1-1.

表 1-1. Ventilator System Requirements

| X 1 1. Ventuator dystem requirements                              |  |  |  |

|-------------------------------------------------------------------|--|--|--|

| TYPICAL                                                           |  |  |  |

| IEC 60601-1, ISO 80601-2                                          |  |  |  |

| flow, pressure, respiration rate, FiO2, temperature, and humidity |  |  |  |

| AC or DC                                                          |  |  |  |

| 8-10 hours of continuous use on battery                           |  |  |  |

| 6-28 V                                                            |  |  |  |

| 150-200 W                                                         |  |  |  |

| 5-40 °C                                                           |  |  |  |

| 0 – 90 cmH <sub>2</sub> O                                         |  |  |  |

| 0-200 L/m                                                         |  |  |  |

| ± 5 L/min or 20% of reading                                       |  |  |  |

| ± 0.5 cmH <sub>2</sub> O or 10% of reading                        |  |  |  |

|                                                                   |  |  |  |

www.tij.co.jp System Description

表 1-1. Ventilator System Requirements (continued)

| KEY REQUIREMENTS                    | TYPICAL          |

|-------------------------------------|------------------|

| Minimum inspiratory/expiratory time | 200 ms           |

| Valve response time                 | < 5ms            |

| Motor operating voltage             | 24 V             |

| Motor operating current             | 3-5 A continuous |

| High speed operation                | 40-60 kRPM       |

| Wide operating speed range          | 1-60 kRPM        |

| High accelerations and braking      | 150-200 kRPM/s   |

Note, many medical ventilators will also support continuous positive airway pressure (CPAP) operating mode and include an oxygen concentrator (for example, Ventec VOCSN, Medtronic Puritan Bennett™ 980). However, there are many standalone CPAP machines (for example, Philips DreamStation, ResMed AirMini™) and oxygen concentrators used for home healthcare. For CPAP machines, the pressurized air is delivered to sleeping patients through a mask to treat sleep apnea by helping to prevent the throat from closing.

Similar to ventilators, many CPAP machines and oxygen concentrators rely on a BLDC motor in their application to pressurize the air due their reliability, efficiency, and audible noise characteristics. In general, these standalone machines are designed to be portable and many weights less than 10 lbs. Standalone CPAP machines have less stringent motor requirements compared to ventilators. In addition, CPAP machines typically specify a lower sound level (~29 dBA) compared to ventilators (~50 dBA) and they have a narrower operating pressure range compared to ventilators.

The key system requirements for a CPAP system are shown in 表 1-2.

表 1-2. CPAP System Requirements

| KEY REQUIREMENTS                             | TYPICAL                                                       |

|----------------------------------------------|---------------------------------------------------------------|

| System reliability and functional safety     | IEC 60601-1, ISO 80601-2                                      |

| Accurate sensing of key parameters           | Flow, pressure, temperature, and humidity                     |

| Power source                                 | AC or DC                                                      |

| Efficient system design for portable systems | 8-12 hours of continuous use on battery                       |

| DC power input voltage                       | 6-28 V                                                        |

| Input power                                  | 30-80 W                                                       |

| Operation temperature range                  | 5 to 35 °C                                                    |

| Operating pressure range                     | 4-20 cmH <sub>2</sub> O, sensor range 0-40 cmH <sub>2</sub> O |

| Operating flow range                         | 0-150 L/min                                                   |

| Flow accuracy                                | ± 1.5 L/min or ± 2.7 % of reading (ISO 80601-2-70)            |

| Static and dynamic pressure accuracy         | ± 0.15 , ± 0.27 cmH <sub>2</sub> O (ISO 80601-2)              |

| Sound level / noise emissions                | <29 dBA (ISO 4871)                                            |

| Service life                                 | 5 years                                                       |

| Physical weight                              | 1-4 lbs                                                       |

| Motor operating voltage                      | 12 or 24 V                                                    |

| Motor operating current                      | 2-3 A continuous                                              |

| High speed operation                         | 30-40 kRPM                                                    |

| Wide operating speed range                   | 1-40 kRPM                                                     |

Standalone oxygen concentrators will similarly use a motor to pressurize air and will use multiple valves to mix air with pure oxygen to increase the oxygen concentration in the mixture delivered to the patient. One of the key differences in requirements compared to the previous applications is the lower motor speed (2-4 kRPM) due to a lower flow rate requirement (typically less than 2 L/min).

The key system requirements for an oxygen concentrator are shown in 表 1-3.

表 1-3. Oxygen Concentrator System Requirements

| KEY REQUIREMENTS                             | TYPICAL                                         |

|----------------------------------------------|-------------------------------------------------|

| System reliability and functional safety     | IEC 60601-1, ISO 8359, ISO 80601-2-67           |

| Accurate sensing of key parameters           | Flow, pressure, FiO2, temperature, and humidity |

| Power source                                 | AC or DC                                        |

| Efficient system design for portable systems | 4-10 hours of continuous use on battery         |

| DC power input voltage                       | 10-28V                                          |

| Input power                                  | 100-150W                                        |

| Operation temperature range                  | 5 to 35 °C                                      |

| Maximum outlet pressure                      | 30 to 90 psi                                    |

| FiO2 Range                                   | 21-100 %                                        |

| O2 sensor accuracy                           | 3-6 %                                           |

| Operating flow range                         | 0-10 L/min                                      |

| Flow accuracy                                | +/- 15 %                                        |

| Sound level / noise emissions                | 40 dBA                                          |

| Service life                                 | 5 years                                         |

| Physical weight                              | 5-10 lbs                                        |

| Motor operating voltage                      | 12 or 24 V                                      |

| Motor operating current                      | 2-5 A continuous                                |

| Motor speed                                  | 2-4 kRPM                                        |

www.tij.co.jp

# 1.2 Respirator System Components

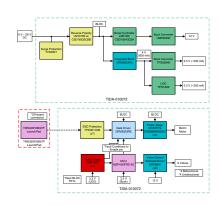

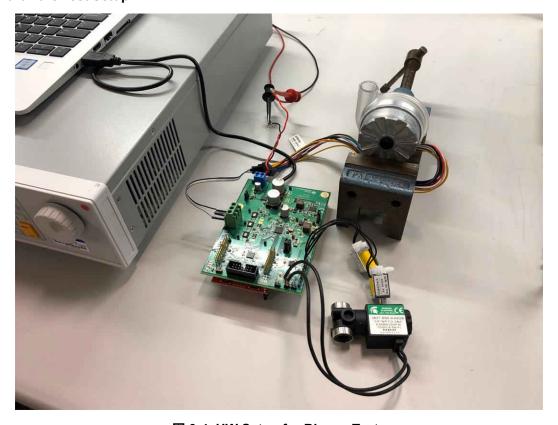

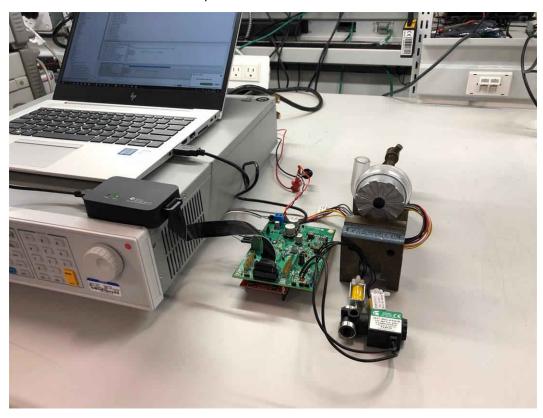

Different respiratory applications will require various aspects of this reference design. CPAP machines will mainly need the BLDC motor driver portion of the design while Anesthesia delivery systems will require the valve driver portion. Oxygen concentrators and ventilators will use a combination of both. 🗵 1-2 shows a high-level block diagram of the system and delineates the separation between the valve drivers and motor driver. The system connects to a C2000 Launchpad to drive the BLDC motor.

図 1-2. Respirator system block diagram

# 1.3 Key System Specifications

This reference design showcases a compact driver system design used to drive a single brushless DC (BLDC) motor and up to six solenoid valves. The BLDC motor is used to quietly and efficiently generate pressurized airflow. The solenoid valves are used to both create different gas mixtures and to provide safety mechanisms in the event of failures. The design supports up to 10 A of continuous motor drive, which can cover the motor operating requirements in most respirator applications. Additionally, this design includes a power tree capable of handling typical regulated DC voltage rails and battery voltage levels (6-28 V) for applications that are moving to portable designs.

表 1-4 lists the different characteristics and specifications of the TIDA-010072 board.

| 表 | 1-4. | TIDA-0 | 10072 | Key | <b>System</b> | Specifications |

|---|------|--------|-------|-----|---------------|----------------|

|   |      |        |       |     |               |                |

|                                            | <u> </u>                            |

|--------------------------------------------|-------------------------------------|

| KEY REQUIREMENTS                           | TYPICAL                             |

| Input Voltage                              | 6-28 V                              |

| BLDC Motor Current                         | 10 A Continuous, 20 A peak          |

| Max electrical frequency                   | 1.2 kHz                             |

| Max Pulse Width Modulation (PWM) Frequency | 45 kHz                              |

| Key Protection Features                    | Surge, OCP, UVLO, OTW/OTSD, and RVP |

| BLDC Motor Max Acceleration                | 200 kRPM/s                          |

| Solenoid Operating Voltage                 | 12 V                                |

| -1 5 5                                     |                                     |

表 1-4. TIDA-010072 Key System Specifications (continued)

| KEY REQUIREMENTS              | TYPICAL                                             |

|-------------------------------|-----------------------------------------------------|

| Unidirectional Solenoid Drive | 4 Channels                                          |

| Bidirectional Solenoid Drive  | 2 Channels                                          |

| Solenoid Drive Current        | 4x 0.5 A (unidirectional), 2x 0.5 A (bidirectional) |

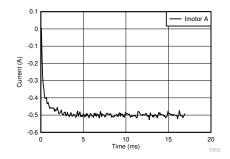

| Max valve response time       | 1 ms                                                |

| Operation Temperature Range   | 5 to 40 °C                                          |

# **DRV8323RS Integrated Protection Features:**

- VM Undervoltage Lockout (UVLO)

- Charge Pump Undervoltage (CPUV)

- MOSFET Overcurrent Protection (OCP)

- Gate Driver Fault (GDF)

- Thermal Warning and Shutdown (OTW/OTSD)

- Fault Condition Indicator (nFAULT)

# **DRV8847 Integrated Protection Features:**

- VM undervoltage lockout

- · Overcurrent protection

- Open load detection

- Thermal shutdown

- Fault condition indication pin (nFAULT)

www.tij.co.jp

# 2 System Overview

# 2.1 Block Diagram

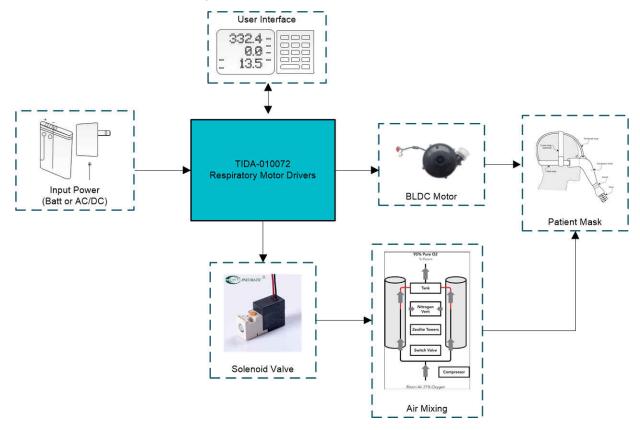

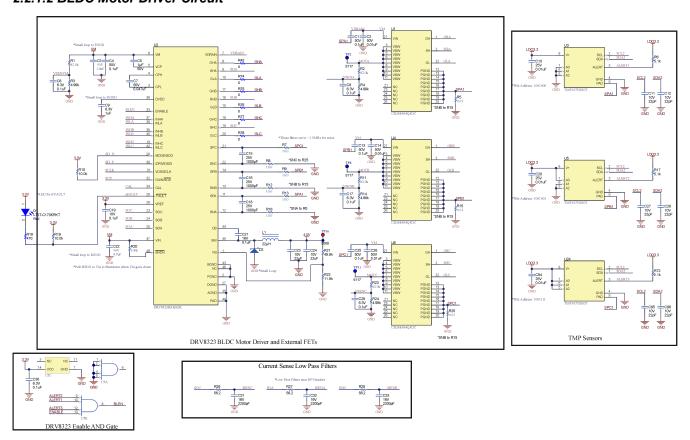

図 2-1. TIDA-010072 Block Diagram

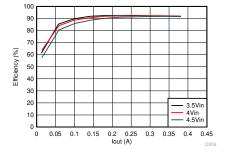

This reference design is capable of driving a BLDC motor, four unidirectional valves, and two bidirectional valves in a compact and efficient platform. The DRV8323RS is selected as the BLDC motor driver with FOC control provided from an off-board Piccolo MCU. Three TMP1075 Integrted Circuits (ICs) are selected to monitor the temperature of the BLDC half-bridges to prevent over-temperature conditions. Two DRV8847 ICs are selected to drive the solenoid valves with control provided by the MSP430FR2155.

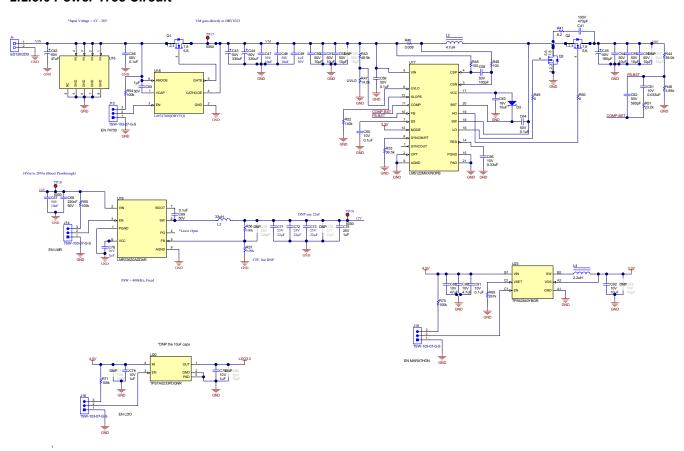

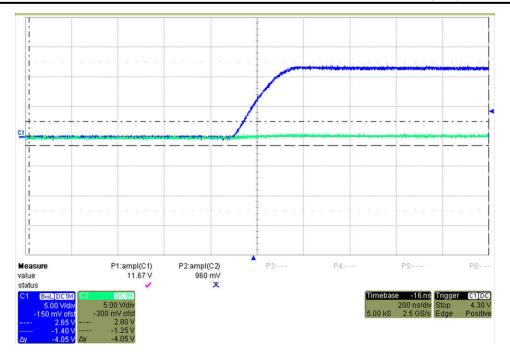

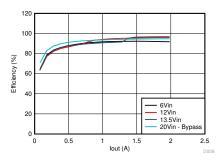

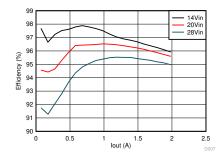

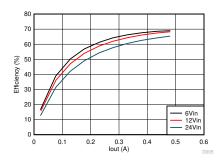

The system is capable of running off of a wide input voltage range of 6-28 V. This range covers typical battery input voltages as well as typical regulated DC voltages that are seen in many respiratory systems. The LM5122 boost controller is used to convert lower input voltages to 14 V, with a pass-through mode for higher voltages. The LMR33630 buck converter is used to step the output of the LM5122 down to a regulated 12 V, which is used by the DRV8847 ICs. The DRV8323RS uses the full input voltage range, and also integrates a buck converter, which is used to step the full input voltage range down to 4 V. The TPS7A02 low-dropout linear regulator (LDO) is selected to step 4 V down to a clean 3.3 V to power the temperature sensors. The TPS62840 buck converter

System Overview www.tij.co.jp

is selected to step 4 V down to 3.3 V to provide power for the remaining digital devices including the MCU, and system pull-up resistors.

# 2.2 Design Considerations

This reference design targets two key challenges for respiratory applications including CPAP machines, oxygen concentrators, ventilators, and anesthesia delivery systems. The first challenge is to achieve an efficient and quiet design for operating a three-phase BLDC air blower with multiple solenoid valve configuration options. The second challenge is to power the system from a wide input voltage range to account for typical regulated DC rails and newer portable 3s/4s battery applications.

# 2.2.1 Brushless DC Motor (BLDC)

Pressurized air for these applications can be generated using several motor types including brushed-DC (BDC), BLDC, and even AC motors. Of the three types mentioned, AC motors are the easiest to control. However, AC motors use additional energy to create the electromagnet, which decreases their efficiency, and they tend to be physically larger than both BDC and BLDC motors. AC motors also do not have capability to change speed quickly. BDC motors tend to have a lower cost and simpler control schemes than BLDC motors. However, BLDC motors offer several advantages that make them especially desirable for respiratory medical applications. The largest benefit of these motors is that they lack the brushes and are contactless, which means that they are inherently much quieter than BDC motors and will have a longer lifetime. Brushed-DC motors will wear out more quickly due to the brushes degrading over time. Additionally, while the control can be far more complex for BLDC motors, BLDC motors are the most efficient motor type and smallest in size for a given motor power. Brushless-DC motors are also capable of the highest speed and best dynamic speed performance (acceleration and deceleration) compared to other motor types.

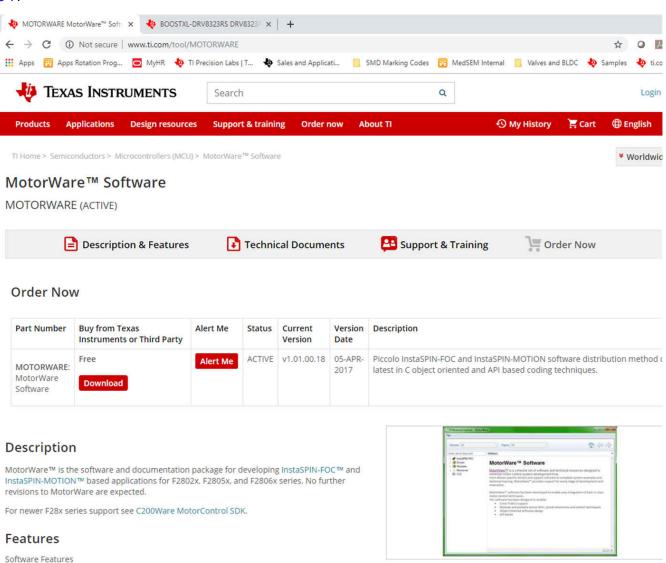

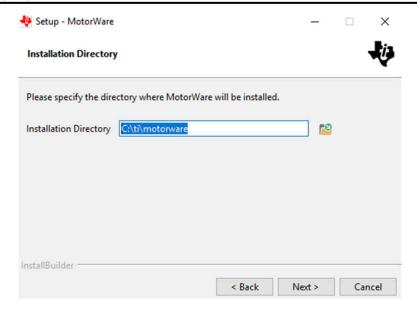

To achieve the quietest and most efficient operation, field-oriented control (FOC) is often used as a control algorithm. FOC is a technology that applies all torque on the motor perpendicular to the rotor; this allows for maximum drive effectiveness. Additionally, many systems implement a sensorless control scheme, meaning that there are no Hall-Effect sensors embedded on the motor itself. Sensorless drive schemes allow a wider range of motors to be used, however sensored drive systems may also be implemented if the motor used has sensors built in. TI features a technology called <a href="InstaSpin-FOC">InstaSpin-FOC</a>, which runs on select Piccolo series MCU and can be a quicker way to bring up sensorless FOC compared to designing the control scheme from the ground up.

The DRV8323RS was selected as the motor gate driver for this design based on several features. For example, the DRV8323RS has three integrated half-bridge drivers capable of sourcing 2 A and sinking 1 A to the MOSFET gates. It also integrates the charge pump for the high side MOSFETs for 100% duty cycle, an asynchronous buck converter capable of supporting up to 600 mA for external use, and three low-side current sense amplifiers to sense the motor current. Another important aspect in the selection of this device is that it is capable of handling the entire voltage range desired for this reference design, 6-28 V.

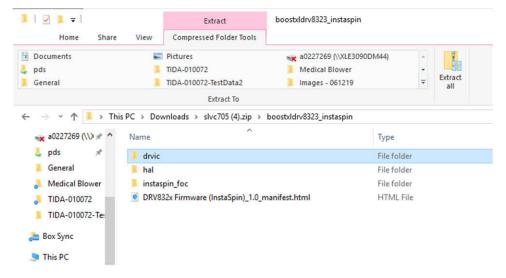

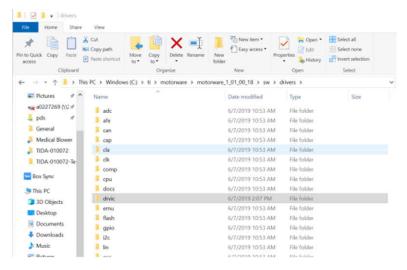

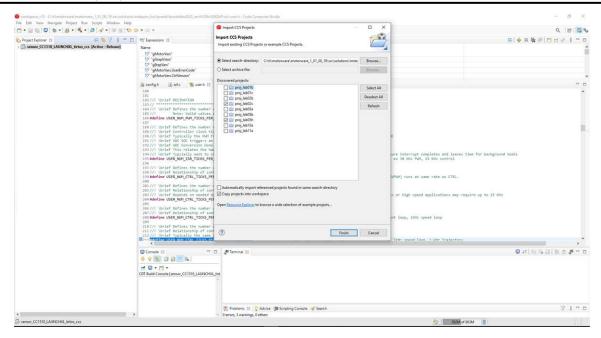

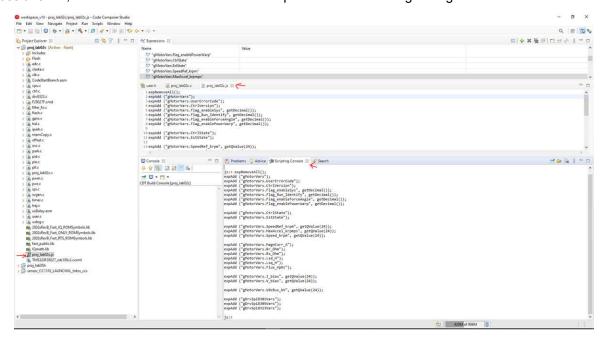

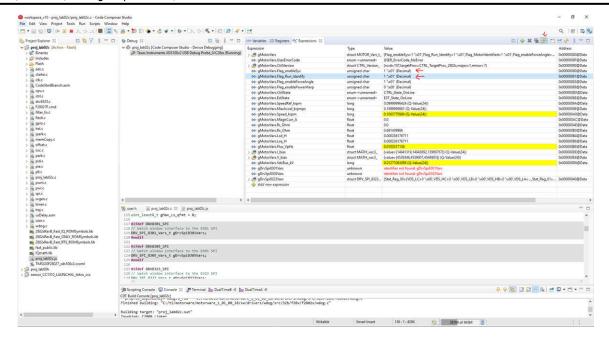

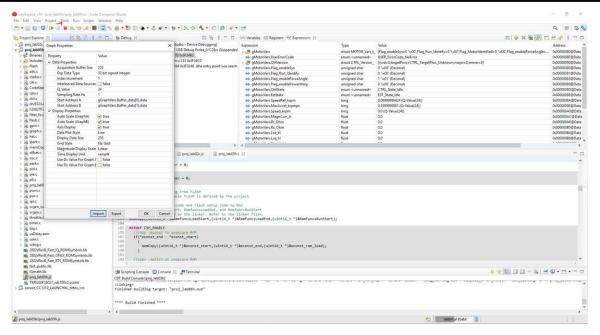

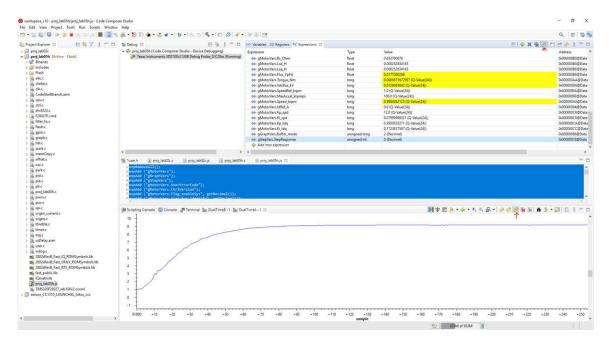

To achieve the desired FOC algorithm, the latest Piccolo MCU, TMS320F28027F, has been selected to run TI's InstaSpin-FOC control software. The reference design includes connectors to attach to the Piccolo's Launchpad. In this way, FOC is integrated into the design through a plug-and-play peripheral to allow users to easily test this control algorithm.

## 2.2.1.1 DRV8323RS BLDC Motor Driver Design Calculations

# **External MOSFET Support**

The DRV832x MOSFET support is based on the capacity of the charge pump and PWM switching frequency of the output. For a quick calculation of MOSFET driving capacity, use the following equations for three phase BLDC motor applications.

Trapezoidal 120° Commutation:

$$I_{VCP} > Q_g \times f_{pwm} \tag{1}$$

Sinusoidal 180° Commutation and FOC:

$$I_{VCP} > 3 \times Q_g \times f_{pwm} \tag{2}$$

where

- f<sub>pwm</sub> is the maximum desired PWM switching frequency

- $I_{\text{VCP}}$  is the charge pump capacity, which depends on the VM pin voltage

- · The multiplier based on the commutation control method, may vary based on implementation

- Q<sub>a</sub> is the total gate charge

The DRV8323RS device is capable of supporting PWM frequencies up to 200 kHz and the selected CSD88584Q5DC power block is capable of 50 kHz. However, the actual PWM frequency will be limited by the charge pump specification. For a VM supply voltage  $\geq$  13 V, the charge pump is rated for 25 mA and the V<sub>cp</sub> operating voltage is 11 V relative to VM. From the CSD88584Q5DC data sheet, the typical Q<sub>g</sub> is rated at 137 nC (178 nC max).

The maximum 24-V application PWM frequency operating FOC is:

$$f_{\text{pwm}} < \frac{I_{\text{VCP}}}{3 \times Q_{\text{g}}} = \frac{25 \text{ mA}}{3 \times 178 \text{ nC}} = 46.8 \text{ kHz}$$

(3)

In this design, the PWM frequency was set to 45 kHz.

## **Power Dissipation Calculations**

The maximum input supply of 28 V and I<sub>load</sub> of 10 A were used for the following calculations. These calculations are applicable for sinusoidal PWM (SPWM) and FOC motor controls. Note, for sinusoidal and FOC, each FET has 180° of conduction. The CSD88584q5dc and DRV8323RS data sheets were referenced for the electrical specifications. Each loss type is split evenly between the high and low FETs.

## Half-bridge FET Losses

The max conduction loss for the half-bridge is:

$$P_{COND} = I_{RMS}^{2} \times R_{DS\_ON} \times 1.5 = I_{load}^{2} \times R_{DS\_ON} \times 1.5$$

$$P_{COND} = I_{load}^{2} \times R_{DS\_ON} \times 1.5 = 10A^{2} \times 0.95m\Omega \times 1.5 = 143 \text{ mW}$$

(4)

The 1.5 correction factor accounts for junction temperature effect on the FET resistance. That is, a 50% increase in resistance due to temperature. This is a rule-of-thumb for moderate junction temperature (50-100 °C). If the FET junction operates at 125 °C, this factor must be adjusted accordingly (e.g. 1.8 instead).

The DRV8323 can source and sink up to 1A and 2A, respectively. The rise and fall switching times are:

$$t_{R} = \frac{Q_{gs (afterVth )} + Q_{gd}}{I_{source}} = \frac{Q_{gs} - Q_{g,Vth} + Q_{gd}}{I_{source}} = \frac{24 \text{ nC} - 16 \text{ nC} + 26 \text{ nC}}{1 \text{A}} = 34 \text{ ns}$$

$$t_{F} = \frac{Q_{gs (afterVth )} + Q_{gd}}{I_{sink}} = \frac{Q_{gs} - Q_{g,Vth} + Q_{gd}}{I_{sink}} = \frac{24 \text{ nC} - 16 \text{ nC} + 26 \text{ nC}}{2 \text{ A}} = 17 \text{ ns}$$

(5)

where  $t_R$  and  $t_F$  are the switching times (including the rise and fall times) corresponding to the rise and fall transitions.

The max switching loss for the half-bridge is (assume negligible soft switching losses):

$$P_{SW} = 0.5 \times VM \times I_{load} \times (t_R + t_F) \times f_{sw} P_{SW} = 0.5 \times 28V \times 10A \times (34 \text{ ns} + 17 \text{ ns}) \times 45 \text{ kHz} = 321 \text{ mW}$$

(6)

注

The recommended rise and fall times for most applications is around 100 ns.

The dead time loss is:

$$P_{DT} = V_D \times I_{load} \times t_{dead} \times f_{sw}$$

(7)

$$P_{DT} = 1 \text{ V} \times 10 \text{ A} \times 200 \text{ ns} \times 45 \text{ kHz} = 90 \text{ mW}$$

(8)

The DRV8323RS's dead time is programmable with 50-ns, 100-ns, 200-ns, and 400-ns options. The default setting is 100 ns. There are two instances of dead time per a switching cycle.

The reverse recovery charge loss is:

$$\begin{aligned} P_{RR} &= Q_{rr} \times VM \times f_{sw} \\ P_{RR} &= 34 \text{ nC} \times 28 \text{ V} \times 45 \text{ kHz} = 43 \text{ mW} \end{aligned} \tag{9}$$

The gate drive voltage is 11 V (typical) for VM >13 V and the  $Q_g$  ( $V_{gs}$  =10 V) is 178 nC from the data sheet.

Assume half of the gate charge loss is on the FET side and half on the driver IC side. The half-bridge gate charge loss is:

$$P_{G} = 0.5 \times V_{gs} \times (Q_{G(LS)} + Q_{G(HS)}) \times f_{sw}$$

$$P_{G} = 0.5 \times 11V \times 356nC \times 45kHz = 88mW$$

(10)

The total half-bridge loss is:

$$P_{LOSS} = P_{COND} + P_{SW} + P_{DT} + P_{RR} + P_{G}$$

$$P_{LOSS} = 143 \text{ mW} + 321 \text{ mW} + 90 \text{ mW} + 43 \text{ mW} + 88 \text{ mW} = 685 \text{ mW}$$

(11)

#### **DRV8323RS Driver Losses**

The operating supply current loss is:

$$P_{VM} = VM \times I_{VM}$$

$P_{VM} = 28 \text{ V} \times 14 \text{ mA} = 392 \text{ mW}$  (12)

$$P_{\text{DVDD}} = (\text{VM} - \text{VDD}) \times I_{\text{VDD}}$$

$$P_{\text{DVDD}} = 0$$

(13)

For high-side (HS) driver supply loss, assume a 50% charge pump efficiency:

$$\begin{split} P_{\text{CP\_GH}} &= P_{\text{out}} \times \frac{1 - \eta}{\eta} = 3 \times (V_{\text{gs}} \times Q_{\text{g}} \times f_{\text{sw}}) \times \frac{1 - \eta}{\eta} \\ P_{\text{CP\_GH}} &= 3 \times 11 \text{ V} \times 178 \text{ nC} \times 45 \text{ kHz} \times \frac{1 - 0.5}{0.5} = 264 \text{ mW} \end{split} \tag{14}$$

For low-side (LS) driver supply loss:

$$\begin{aligned} P_{LDO\_GL} &= 3 \times (VM - V_{gs}) \times Q_g \times f_{sw} \\ P_{LDO\_GL} &= 3 \times (28 \, V - 11 \, V) \times 178 \, nC \times 45 \, kHz = 408 \, mW \end{aligned} \tag{15}$$

For gate drive loss inside driver IC, again assume half is on the driver side. Note, the driver drives three half-bridges:

$$\begin{split} P_{G\_IC} &= 0.5 \times V_{gs} \times 3 \times (Q_{g(LS)} + Q_{g(HS)}) \times f_{sw} \\ P_{G\_IC} &= 0.5 \times 11V \times 3 \times 356 \text{ nC} \times 45 \text{ kHz} = 264 \text{ mW} \end{split} \tag{16}$$

For the DRV8323RS integrated buck (LMR16006X), assume a maximum load of 200 mA and an 85% efficiency:

$$P_{BUCK} = P_{out} \times \frac{1 - \eta}{\eta}$$

$$P_{BUCK} = (4 \text{ V} \times 200 \text{ mA}) \times \frac{1 - 0.85}{0.85} = 141 \text{ mW}$$

(17)

The total driver IC loss is:

$$\begin{aligned} P_{LOSS\_DRV\_IC} &= P_{VM} + P_{CP\_GH} + P_{LDO\_GL} + P_{G\_IC} + P_{BUCK} \\ P_{LOSS\_DRV\_IC} &= 392 \text{ mW} + 264 \text{ mW} + 408 \text{ mW} + 264 \text{ mW} + 141 \text{ mW} = 1.5 \text{ W} \end{aligned} \tag{18}$$

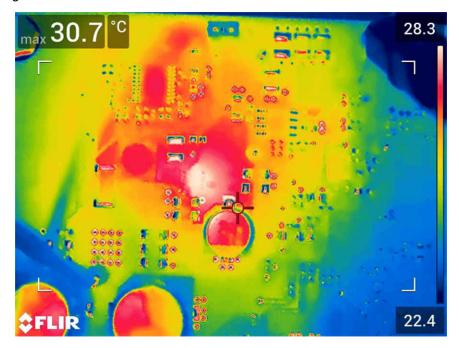

#### **Junction Temperature Estimation**

For CSD88584q5dc power block, assume a  $R_{\theta JA}$  = 50 °C/W (1 in<sup>2</sup> of 2-oz Cu) based on the data sheet:

$$T_{J} = T_{ambient} + R_{\theta JA} \times P_{d}$$

(19)

$$T_J = 40 \text{ C} + \frac{50 \text{ C}}{W} \times (685 \text{ mW}) = 74 \text{ C}$$

(20)

For DRV8323RS (RGZ package) driver, assume a  $R_{\theta JA}$  = 26.6 °C/W based on the data sheet:

$$T_J = 40 \text{ C} + \frac{26.6 \text{ C}}{\text{W}} \times (1.5 \text{ W}) = 80 \text{ C}$$

(21)

These temperature estimates are well below the max ratings, which allows for an adequate operating margin.

# **IDRIVE Configuration**

The strength of the gate drive current, IDRIVE, is selected based on the gate-to-drain charge of the external MOSFETs and the target rise and fall times at the outputs. If IDRIVE is selected to be too low for a given MOSFET, then the MOSFET may not turn on completely within the tDRIVE time and a gate drive fault may be asserted. In this design, the default IDRIVE was set to 1A/2A (default). However, for most applications, a lower drive current is recommended to reduce EMI.

### **VDS Overcurrent Monitor Configuration**

The VDS monitors are configured based on the worst-case motor current and the  $R_{DS(on)}$  of the external MOSFETs. Using a 1.8 temperature factor for 0.95 m $\Omega$ , the max  $R_{DS(on)}$  is 1.7 m $\Omega$ . The target OCP threshold is 30 A so  $V_{DS\ OCP}$  must be:

$$V_{DS\_OCP} > I_{max} \times R_{DS(on)max}$$

$$V_{DS\_OCP} > 30 \text{ A} \times 1.7 \text{ m}\Omega = 51 \text{ mV}$$

(22)

The V<sub>DS OCP</sub> threshold was set to 60 mV (closest available) and the OCP deglitch time was set to 4 µs (default).

#### **Unidirectional Current Sense Operation**

The sense amplifier gain and sense resistor values are selected based on the target current range,  $V_{REF}$ , power rating of the sense resistor, and operating temperature range. In unidirectional operation of the sense amplifier, use the following equation to calculate the approximate value of the dynamic range at the output:

$$V_{0_{DR}} = (V_{ref} - 0.25 \text{ V}) - 0.25 \text{ V}$$

$V_{0_{DR}} = 3.3 \text{ V} - 0.5 \text{ V} = 2.8 \text{ V}$

(23)

Using the default gain of 20 V/V and the maximum input current of 12 A (10 A plus a 20% margin):

$$R_{sense} < \frac{V_{0\_DR}}{Gain \times I_{max}}$$

$$Rsense < \frac{2.8 \text{ V}}{20 \text{ V/V} \times 12 \text{ A}} = 11.7 \text{ m}\Omega$$

(24)

10 m $\Omega$  was selected for Rsense. The minimum power rating for Rsense must be:

$$P_{R\_SENSE} > I^2 \times R = 12 \text{ A}^2 \times 10 \text{ m}\Omega = 1.44 \text{ W}$$

(25)

In this design, a 10-m $\Omega$ , 3-W Rsense was used for each of the three channels. In addition, 1.3-kHz RC low pass filters were used for these sensing channels to limit noise.

The full scale ADC current is (ignore the headroom limitation):

$$I = \frac{V_{\text{ref}}}{\text{Gain} \times R_{\text{sense}}}$$

(26)

$$I_{FS(ADC)} = \frac{3.3 \text{ V}}{20\text{V/V} \times 10 \text{ m}\Omega} = 16.5 \text{ A}$$

(27)

注

This value is defined as USER\_ADC\_FULL\_SCALE\_CURRENT\_A in the user.h file.

# **Buck Regulator Configuration**

The LMR16006 buck is capable of supplying up to 600 mA. The switching frequency is fixed at 700 kHz (typical). In this design, the buck was configured for a 4-V output. The expected application load is 200 mA. This 4-V rail is the primary supply for the digital loads. The basic inductor calculations are shown below. For more information, please reference the LMR16006 data sheet design example.

The first step to calculate the peak inductor/switch current is to determine the duty cycle, D, for the maximum input voltage. The maximum input voltage is used because this leads to the maximum switch current:

$$D_{\min} = \frac{V_{\text{out}}}{V_{\text{in}}} = \frac{4 \text{ V}}{28 \text{ V}} = 0.143 \tag{28}$$

The parameters for selecting the inductor are the inductance and saturation current. The inductance is based on the desired peak-to-peak ripple current and is normally chosen to be in the range of 20 to 40 % of the maximum output current. Note that when selecting the ripple current for applications with much smaller maximum load (0.2 A) than the maximum available from the device (0.6 A), the maximum device current should be used:

$$L = \frac{V_{out}}{I_{out} \times RR \times f_{sw}} \times (1 - D)$$

$$L = \frac{4 V}{0.6 A \times 0.4 \times 700 \text{ kHz}} \times (1 - 0.143) = 20.4 \mu\text{H}$$

(29)

RR of 0.4 was selected.

For this design, 22 µH was selected.

The actual worst-case ripple current is:

$$\Delta I_{L} = \frac{V_{out}}{f_{sw} \times L} \times (1 - D)$$

$$\Delta I_{L} = \frac{4 \text{ V}}{700 \text{ kHz} \times 22 \text{ }\mu\text{H}} \times (1 - 0.143) = 0.22 \text{ A}$$

(30)

The actual ripple ratio is:

$$RR = \frac{\Delta I_L}{I_{\text{out}}} = \frac{0.22A}{0.6A} = 0.37$$

(31)

The peak inductor/switch/diode current and the minimum saturation current rating of the inductor plus a 25% margin are calculated as follows:

$$I_{\text{peak}} = I_{\text{out}} \times \left(1 + \frac{RR}{2}\right)$$

$I_{\text{peak}} = 0.6 \text{ A} \times \left(1 + \frac{0.37}{2}\right) \times 1.25 = 0.89 \text{ A}$

(32)

The LMR16006 has a current limit at 1.7 A (max). Using a saturation rating near 1.7 A will enable the LMR16006 to current limit without saturating the inductor. This is preferable to the LMR16006 going into thermal shutdown mode and the possibility of damaging the inductor if the output is shorted to ground or other long-term overload.

In this design, the selected inductor (74438356220) has saturation ratings of 1.85 A ( $\Delta L$ =-20%). Based on the data sheet, this inductor RMS rating is well suited to handle 1.7 A with a 40 °C rise.

For the RMS current calculations, the 0.2 A max application current is used instead of the device maximum:

$$I_{RMS} = I_{out} \sqrt{1 + \frac{RR^2}{12}}$$

$$I_{RMS} = 0.2A \sqrt{1 + \frac{0.37^2}{12}} = 0.2 A$$

(33)

Note, I<sub>RMS</sub> is approximately I<sub>out</sub> given a small RR value.

Inductor wire loss is calculated as follows:

$$P_{IND\_DC} = I_{RMS}^2 \times R \cong I_{out}^2 \times R = 0.2A^2 \times 250 \text{ m}\Omega = 10 \text{ mW}$$

(34)

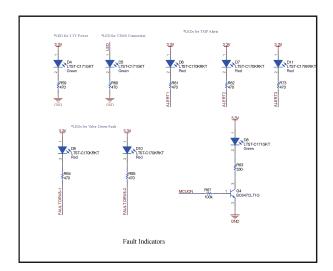

# Temperature monitor and over temperature protection

The design is equipped with three TMP1075 digital temperature sensors designed to monitor and protect the power blocks. Three TMP1075 ALERT outputs (active low) and the DRV8323RS Enable control signal are connected to a quad-input AND gate. The DRV8323RS will be disabled if one of the inputs is logic LOW.

**ISTRUMENTS** System Overview www.tij.co.jp

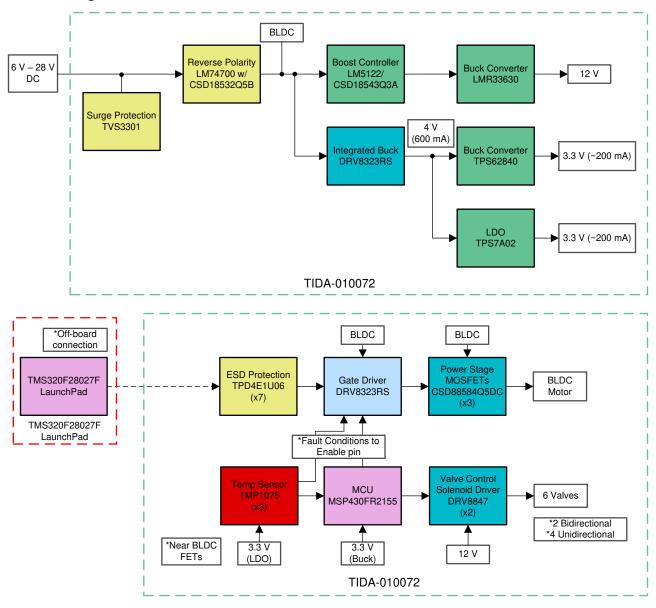

#### 2.2.1.2 BLDC Motor Driver Circuit

図 2-2. BLDC Motor Driver Circuit

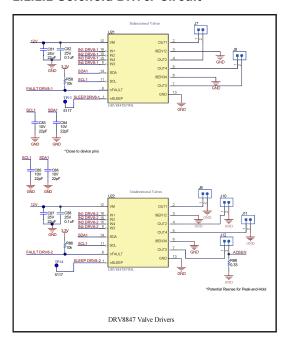

#### 2.2.2 Solenoid Valve Drivers

Solenoid valves are a key component of many respiratory applications, such as oxygen concentrators, and are used to accomplish multiple functions. Oxygen concentrators use a compressor to separate air and oxygen into separate canisters. Solenoid valves are then activated to release specified amounts of each gas into a chamber, which then uses a separate valve to supply the mixture to the patient through a mask. Solenoid valves can also be used to stop the flow of gas to the mask if a fault is detected. These valves are similarly useful in anesthesia delivery systems where multiple gases are typically mixed together before delivery to the patient. Oxygen concentrators tend to have 4 - 6 such valves while anesthesia delivery systems tend to have more than 15.

Solenoid valves have different configurations for how they can control the flow of fluid or gas. The simplest configuration is a 2-way valve that connects two pipes or tubes together, but there are also options for 3-way and 4-way junctions that can simple on/off, binary/latching or dithering valves. Each different valve type requires a different control method, but this reference design focused only on controlling the simplest, the on/off valves. On/off valves have a natural, un-energized position and are operated by applying current to energize the solenoid, which changes the position of the valve. In a naturally closed 2-way valve, the valve will be closed and prevent the flow of fluid or gas until the solenoid is energized, which will open the valve to flow. As an alternative example, in a 3-way junction valve, the natural position will connect two of the three pipes together and will connect two different pipes when the valve is energized.

The control for on/off valves can be straight forward implementation in which current needs to be applied to the solenoid to energize the valve. Some on/off valves are unidirectional, in that they can only accept current in a single direction to be energized, while others are bidirectional. The amount of current required depends on the specific valve, but the current waveform for solenoid valves is consistent. A peak current is required to energize the valve initially while a lower amount of current is required to maintain the energized state. Regardless of directionality, these valves can be minimally controlled by a low-side or high-side MOSFET and valve driver that can receive input from an MCU to energize the valve. While simple, this control scheme can be inefficient because it will maintain current flow at the peak current rather than reducing to maintain the energized state. By System Overview

adding a current feedback path it is possible to implement peak-and-hold control which backs off the current but maintains the energized state to increase system efficiency. Some valve drivers integrate the peak-and-hold control while others will require the MCU to read the current and implement that control.

For this reference design, the DRV8847, an 18-V, 2-A dual H-bridge motor driver, was selected to drive the solenoid valves. Each of the half bridges in the device can be independently controlled, which means that the DRV8847 is capable of driving up to four unidirectional valves or two bidirectional valves. This design has two DRV8847 ICs, one for unidirectional control and one for bidirectional control. The DRV8847 is capable of driving 1 A through each half bridge and the integrated MOSFETs have a 1- $\Omega$  R<sub>DS(on)</sub>. The device also integrates a current sense amplifier to do overcurrent protection; however, the driver does not incorporate options for peakand-hold control, so this would have to be implemented by the MCU. Each half-bridge of the DRV8847 is driven by PWM from a local MCU, which was selected as the MSP430FR2155. This MCU was selected because it has all of the required peripherals, is physically small, and is cost-effective.

Pumps are also an integral part of ventilation system that helps with pumping air and medicine to the lungs. These pumps often need precise and fine motorized control that can operate electrically. Stepper motor and dual H Bridge drivers are favored with high microstepping like DRV8825 and DRV8886AT.

As system requirements can vary, solenoids/valves and pumps may be connected to a 12-V, 24-V, 36-V or even 48-V rail with varying current requirement. Some other key devices to be considered based on system requirements are as follows:

| 表 2-1. Alternative Devices to be Considered Based on System Requirements |                                                                                  |                        |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------|--|

| DEVICE                                                                   | SYSTEM CONDITION                                                                 | FUNCTION               |  |

| DRV8876, DRV8874                                                         | 37 V, 3.5 A peak for bidirectional control or independent control for 2 solenoid | Operate solenoid/valve |  |

| DRV8844                                                                  | Up to 60 V, 2.5 A drive quad independent half bridge for 4 solenoid control      | Operate solenoid/valve |  |

| DRV8886AT                                                                | 40 V, 1 A to 2 A FS dual H-bridge motor driver                                   | Operate pump           |  |

| DRV8825                                                                  | 47 V. 1.6 A FS dual H-Bridge motor driver                                        | Operate pump           |  |

#### 2.2.2.1 DRV8847 Solenoid Driver Design Calculations

The DRV8847 device is configured for independent half-bridge operation. Mode selection is done using the I<sup>2</sup>C registers in the DRV8847S device variant. Refer to the data sheet for more details. The solenoid driver design is summarized below:

| 表 2-2. Solenoid Driv | er Design Summary |

|----------------------|-------------------|

|                      |                   |

| <b>2</b> , = =                |                                                     |  |

|-------------------------------|-----------------------------------------------------|--|

| PARAMETER                     | SPECIFICATION                                       |  |

| Solenoid operating voltage    | 12 V                                                |  |

| Unidirectional solenoid drive | 4 Channels                                          |  |

| Bidirectional solenoid drive  | 2 Channels                                          |  |

| Solenoid drive current        | 4x 0.5 A (unidirectional), 2x 0.5 A (bidirectional) |  |

| Max valve response time       | 1 ms                                                |  |

| Operation temperature range   | 5-40 °C                                             |  |

Based on the data sheet, the DRV8847 integrated FET max  $R_{DS(on)}$  is 700 m $\Omega$  (VM = 12 V;  $I_{OUT}$  = 0.5 A;  $I_{A}$  = 85 °C). For unidirectional drive, each channel conduction loss is:

$$P_{\text{COND}} = I_{\text{load}}^2 \times R_{\text{DS}_{\text{ON}}} = 0.25 A^2 \times 700 \text{ m}\Omega = 175 \text{ mW}$$

(35)

For four active channels, the total conduction loss is 700 mW. The junction temperature is calculated as follows:

$$T_J = T_{ambient} + R_{\theta JA} \times P_d = 40 \text{ C} + \frac{108 \text{ C}}{W} \times (4 \times 175 \text{ mW}) = 116 \text{ C}$$

(36)

For bidirectional drive, each channel conduction loss is

$$P_{\text{COND}} = I_{\text{load}}^2 \times (R_{\text{DS\_ON\_HS}} + R_{\text{DS\_ON\_LS}}) = 0.5 \text{ A}^2 \times 1.4 \Omega = 350 \text{ mW}$$

(37)

For two active channels, the total conduction loss is 700 mW. The junction temperature is calculated as follows:

$$T_{\rm J} = T_{\rm ambient} + R_{\rm \theta JA} \times P_{\rm d} = 40 \text{ C} + \frac{108 \text{ C}}{\text{W}} \times (2 \times 350 \text{ mW}) = 116 \text{ C}$$

(38)

This junction temperature allows some margin for other sources of power dissipation and design tolerances.

The switching frequency for solenoid is expected to be relatively low (e.g. 200 Hz), thus the switching loss is negligible:

$$\begin{split} P_{SW} &= 0.5 \times VM \times I_{load} \times (t_R + t_F) \times f_{sw} \\ P_{SW} &= 0.5 \times 12 \text{ V} \times 0.5 \text{ A} \times (300 \text{ns}) \times 200 \text{ Hz} = 0.18 \text{ mW} \end{split} \tag{39}$$

#### 2.2.2.2 Solenoid Driver Circuit

図 2-3. Solenoid Driver Circuit

#### 2.2.3 Power Tree Architecture

Historically, these respiratory applications have used isolated AC/DC power bricks to provide 12 V, 19 V, or 24 V DC bus voltages to the system. The system then either uses the higher DC bus voltage to drive the motors and valves directly, or they step down the voltage through a buck converter. However, as the market for many of these systems move towards portability, they will have to be operated off of battery voltages which are estimated to range from 6-14 V. Given this shift, the reference design has a defined input voltage range of 6-28 V. Additionally, the transition to portability means that the key system requirements include high efficiency to allow longer battery lifetimes. Generally, solution size also has a higher priority for these systems, which was considered in this reference design.

The DRV8323RS is capable of operating under the full voltage range, so the DRV8323RS and BLDC motor has been tied directly to the input voltage source. However, solenoid valves need to operate at a single DC voltage,

so a stable 12 V DC voltage was selected as a required rail. Given that 12 V falls in the middle of the input voltage range a buck-boost or SEPIC topology converter would be the optimal choice to generate the 12 V DC rail. However, with the understanding that some manufacturers will only need a buck converter (for regulated DC inputs) or a boost converter (for battery inputs), separate buck and boost converters were selected to work in sequence to generate the 12 V rail.

The LM5122 wide input synchronous boost controller was selected as the first stage of the power tree after the input. The device was configured to boost to 14 V to cover the battery voltage range and was also selected to get the highest efficiency as a synchronous controller offers the opportunity to select both switching MOSFETs. Additionally, this device has the unique feature of an external charge-pump that can drive the high-side MOSFET when the input voltage goes higher than the set output voltage. This mode is called pass-through and allows power to be efficiently delivered through the high-side MOSFET without changing the input voltage. It is also useful to note that the device operates in peak current-mode control for fast transient response. The LMR33630 is a 3 A synchronous buck converter that was selected due to its small size and high efficiency. The device has been configured to step down to 12 V from the possible input range of 14-28 V, covering the rest of the input voltage range. Placement was optimized in the design for these two devices to showcase their individual solution sizes.

#### 2.2.3.1 Input protection - overvoltage and reverse voltage

This system input voltage range is 6-28 V. A general rule-of-thumb for selecting a transient-voltage-suppression (TVS) device is by selecting the standoff voltage rating 25% above the maximum input voltage (i.e. 35 V). This will allow some margin for device process and temperature variations to minimize unnecessary TVS activation during normal operation. In this design, TVS3301 was selected to provide the input overvoltage protection (OVP). The device has a standoff rating of 33 V and IEC 61000-4-5 clamp rating of 40 V.

The target reverse voltage protection (RVP) should include the maximum input voltage 28 V plus at least a 25% margin to account for transient behaviors and device tolerances (i.e. 35 V). For this design, a 60 V reverse voltage protection target was chosen.

The RVP circuit included an ideal diode controller (LM74700) and an NMOS (CSD18532Q5B). The MOSFET selection for the reverse voltage protection circuit is guided by the typical application conduction current and the VDS voltage rating. There is a tradeoff between reverse voltage detection and conduction loss. As recommended by the LM74700 data sheet, the  $R_{DS(ON)}$  should be (20 mV /  $I_{Load(Nominal)}$ )  $\leq R_{DS(ON)} \leq$  (50 mV /  $I_{Load(Nominal)}$ ). This guideline balances reverse current detection sensitivity and conduction loss. In this design,  $I_{Load(Nominal)}$  is 5 A. Thus, 4 m $\Omega \leq R_{DS(ON)} \leq$  10 m $\Omega$ .

CSD18532Q5B was selected to provide a -60V RVP and it is rated at:

- 60-V V<sub>DS(MAX)</sub> and ±20-V V<sub>GS(MAX)</sub>

- R<sub>DS(ON)</sub> 3.3-mΩ typical and 4.3-mΩ maximum rated at 4.5-V V<sub>GS</sub>

- MOŠFÉT V<sub>th</sub>: 2.2-V maximum

#### 表 2-3. Input protection design summary

| PARAMETER               | SPECIFICATION                | COMMENTS               |

|-------------------------|------------------------------|------------------------|

| Clamping voltage        | 40 V at 27-A (IEC 61000-4-5) | Limited by TVS3301     |

| Maximum reverse voltage | -60 V                        | Limited by CSD18532Q5B |

| Reverse block time      | <0.75 µs                     | Limited by LM74700     |

#### **Input Inrush Protection**

Although not implemented in this design, it is recommended to add inrush current protection (for example, soft-start) to the design. Due to the inherent path from input to output, a large inrush current can flow when the input voltage rises quickly and charges the output capacitor. The slew rate of input voltage rising should be controlled by a hot-swap controller or by starting the input power supply softly for the inrush current not to damage the inductor, sense resistor or high-side N-channel MOSFET switch. An alternative low-cost option is to use a NTC or PTC thermistor for soft-start.

#### 2.2.3.2 LM5122 Boost Design Calculations

Based on the key system specification, the maximum solenoid load is 1.7 A. The boost-buck DC-DC power stage, consisting of LM5122 and LMR33630, is designed to support 2 A of continuous load. Note, WEBENCH® Power Designer was used to help design the power stage. The key design calculations for the LM5122 Boost Stage are shown below. For more details on design considerations, please refer to the device data sheet.

| PARAMETER        | SPECIFICATION | COMMENTS                         |

|------------------|---------------|----------------------------------|

| Input Voltage    | 6-28 V        | From input supply                |

| Input Power      | 31.1 W        | Max, η = 90%                     |

| UVLO             | 5.5 V & 5 V   | Start and Shutdown               |

| F <sub>sw</sub>  | 250 kHz       | Switching frequency              |

| Output Voltage   | 14-28 V       | If Vin >14 V, Vin passes through |

| Output Power     | 28 W          | Max                              |

| Max Load Current | 2 A           | Vout = 14 V (28 W)               |

# **Timing Resistor RT (R53)**

The boost switching frequency of 250 kHz was selected as a good compromised between size and efficiency. The RT resistor is calculated as follows:

$$RT = \frac{9 \times 10^9}{f_{sw}} = \frac{9 \times 10^9}{250 \text{ kHz}} = 36 \text{ k}\Omega$$

(40)

A standard value of 36.5 k $\Omega$  was selected for RT.

# UVLO Divider RUV2 (R43), RUV1 (R47)

The desired startup voltage and the hysteresis are set by the voltage divider RUV2, RUV1. The UVLO shutdown voltage should be high enough to enhance the low-side N-channel MOSFET switch fully. For this design, the startup voltage was set to 5.5 V, which is 0.5 V below the minimum input voltage. VHYS was set to 0.5 V. This resulted in an input-voltage shutdown threshold of 5 V. The values of RUV2, RUV1 are calculated as follows:

$$RUV2 = \frac{VHYS}{IHYS} = \frac{0.5 \text{ V}}{10 \text{ }\mu\text{A}} = 50 \text{ }k\Omega$$

(41)

$$RUV1 = \frac{1.2 \text{ V} \times RUV2}{V_{\text{in\_startup}} - 1.2 \text{ V}} = \frac{1.2 \text{ V} \times 50 \text{ k}\Omega}{5.5 \text{ V} - 1.2 \text{ V}} = 14 \text{ k}\Omega$$

(42)

49.9 k $\Omega$  and 14 k $\Omega$  were selected for RUV2 and RUV1, respectively.

### Input Inductor LIN (L2)

The first step is to calculate the maximum duty cycle and maximum input current. Assuming an efficiency of 0.9:

$$D_{\text{max}} = \left(1 - \frac{V_{\text{in}}}{V_{\text{out}}}\right) = \left(1 - \frac{6 \,\text{V}}{14 \,\text{V}}\right) = 0.57 \tag{43}$$

$$I_{in} = \frac{I_{out} \times V_{out}}{V_{in} \times \eta} = \frac{I_{out}}{(1 - D_{max}) \times \eta} = \frac{2 A}{(1 - 0.57) \times 0.9} = 5.2 A$$

(44)

The inductor ripple current is typically set between 20% and 40% of the full load current, known as a good compromise between core loss and copper loss of the inductor. Higher ripple current allows for a smaller inductor size, but places more of a burden on the output capacitor to smooth the ripple voltage on the output. In addition, a higher ripple may require a higher inductor saturation rating. For this example, a high ripple ratio (RR)

of 0.6, 60% of the input current was chosen to minimize inductor size. Knowing the switching frequency and the typical input voltage, the inductor value can be calculated as follows:

$$L_{in} = \frac{V_{in}}{I_{in} \times RR} \times \frac{1}{f_{sw}} \times D_{max} = \frac{6 \text{ V}}{5.2 \text{ A} \times 0.6} \times \frac{1}{250 \text{ kHz}} \times 0.57 = 4.4 \text{ }\mu\text{H}$$

(45)

The closest standard value of 4.7  $\mu$ H (XAL6060-472ME) was chosen for L<sub>in</sub> (i.e. L2) for this design. Alternatively, if a ripple ratio of 0.3 is desired, a 10  $\mu$ F (XAL6060-103ME) could be chosen.

The saturation current rating of inductor should be greater than the peak inductor current, which is calculated at the minimum input voltage and full load:

$$\Delta I_{L} = \frac{V_{in}}{L_{in} \times f_{sw}} \times D_{max} = \frac{6 \text{ V}}{4.7 \,\mu\text{H} \times 250 \,\text{kHz}} \times 0.57 = 2.9 \,\text{A}$$

(46)

$$I_{\text{peak}} = I_{\text{in}} + 0.5 \times \Delta I_{\text{L}} = 5.2 \text{ A} + 0.5 \times 2.9 \text{ A} = 6.7 \text{ A}$$

(47)

To account for tolerances (i.e. inductor, frequency, voltage) a 25% margin is added to the result. The Ipeak =  $6.7A \times 1.25 = 8.4 A$  (worst-case). The chosen inductor (XAL6060-472ME) saturation current rating is 10.5 A.

Note, I<sub>RMS</sub> is approximately I<sub>IN</sub> given a small RR value:

$$I_{RMS} = \frac{I_{out}}{1 - D} \sqrt{1 + \frac{RR^2}{12}} = I_{in} \sqrt{1 + \frac{RR^2}{12}}$$

(48)

Inductor wire loss is calculated as follows:

$$P_{IND\_DC} = I_{RMS}^2 \times R \cong I_{in}^2 \times R = 5.2A^2 \times 14.4 \text{ m}\Omega = 0.39 \text{ W}$$

(49)

Note: for higher power applications (i.e. higher flux density), inductor core losses may be significant.

#### **Current Sense Resistor RS (R40)**

The maximum peak input current capability should be 20% to 50% higher than the required peak current at low input voltage and full load, accounting for tolerances (that is,  $V_{CS-TH1}$ , peak current). For this design, a 40% margin was selected.

$$Rs = \frac{V_{CS-TH1}}{I_{peak}} = \frac{75 \text{ mV}}{6.74 \times 1.4} = 8 \text{ m}\Omega$$

(50)

$8 \text{ m}\Omega$  was selected for Rs. The maximum power loss of Rs is calculated as follows:

$$P_{loss\_rs} = I^2 \times R = (6.7 \text{ A} \times 1.4)^2 \times 8 \text{ m}\Omega = 0.7 \text{ W}$$

(51)

To account for the sense resistor temperature derating and tolerance, a minimum power rating of 1 W is required. For this design, the chosen Rs (PMR100HZPFU8L00) is rated for 2 W.

#### Current Sense Filter RCSFP (R45), RCSFN (R46), CCS (C58)

The current sense filter is optional. Based on the data sheet recommendations, 100 pF for CCS and 100  $\Omega$  for RCSFP, RCSFN were chosen.

## Slope Compensation Resistor RSLOPE

For duty cycles greater than 50%, peak current mode regulators are subject to sub-harmonic oscillation. In this design the maximum duty cycle is about 57% when V<sub>in</sub> is 6 V. Subharmonic oscillation is normally characterized by observing alternating wide and narrow duty cycles. This subharmonic oscillation can be eliminated by a technique, which adds an artificial ramp, known as slope compensation, to the sensed inductor current.

The K value was selected to be 0.6 at the minimum input voltage.  $R_{slope}$  should be carefully selected so that the sum of sensed inductor current and slope compensation is less than COMP output high voltage. In any case, K should be greater than at least 0.5. At higher switching frequency over 500 kHz, K factor is recommended to be greater than or equal to 1 because the minimum on-time affects the amount of slope compensation due to internal delays.

$$R_{\text{slope}} > \frac{8 \times 10^{9}}{f_{\text{sw}}} = \frac{8 \times 10^{9}}{250 \text{ kHz}} = 32 \text{ k}\Omega$$

(52)

$$R_{slope} = \frac{L_{in} \times 6 \times 10^{9}}{\left[K \times V_{out} - V_{in(min)}\right] \times Rs \times 10} = \frac{4.7 \,\mu\text{H} \times 6 \times 10^{9}}{(0.6 \times 14V - 6V) \times 8m\Omega \times 10} = 146.9 \,\text{k}\Omega \tag{53}$$

For this design, 140 k $\Omega$  was selected for R<sub>slope</sub>.

# **Output Capacitor COUT**

The output voltage ripple is dominated by ESR of the output capacitors. Paralleling output capacitor is a good choice to minimize effective ESR and split the output ripple current into capacitors. In this design, one 180- $\mu$ F bulk aluminum capacitor (EEE-FK1H181SP) and three 10- $\mu$ F ceramic capacitors (UMK316BBJ106KL-T) were used to share the output ripple current and source the required charge. Assuming an effective 50 m $\Omega$  ESR for the hybrid output capacitor network, the output voltage peak-peak ripple at the minimum input voltage is calculated as follows:

$$V_{\text{ripple }\_\text{max} (C_{\text{out}})} = \frac{I_{\text{out}}}{V_{\text{in} (\text{min})}/V_{\text{out}}} \times \left(R_{\text{ESR}} + \frac{1}{4 \times C_{\text{out}} \times f_{\text{sw}}}\right) = I_{\text{in}} \times \left(R_{\text{ESR}} + \frac{1}{4 \times C_{\text{out}} \times f_{\text{sw}}}\right)$$

$$V_{\text{ripple }\_\text{max} (C_{\text{out}})} = 5.2 \text{ A} \times \left(50 \text{ m}\Omega + \frac{1}{4 \times 210 \text{ \mu}\text{F} \times 250 \text{ kHz}}\right) = 285 \text{ mV}$$

(54)

The calculated output ripple voltage is 2% of the output voltage, which is dominated by the effective output ESR. Adding a 25% margin to account for tolerances, the worst-case output voltage ripple is 2.5%.

The output cap RMS current is:

$$I_{RMS\_Cout} = I_{out} \sqrt{\frac{D + \frac{RR^2}{12}}{1 - D}}$$

$$I_{RMS\_Cout} = 2 \text{ A} \times \sqrt{\frac{0.57 + \frac{0.6^2}{12}}{1 - 0.57}} = 2.4 \text{ A}$$

(55)

#### **Input Capacitor CIN**

The input capacitors smooth the input voltage ripple. In this design, two 330  $\mu$ F bulk aluminum capacitors (EMVA500ATR331MKE0S), five 10- $\mu$ F ceramic capacitors (CL31B106KBHNNNE), and one 1- $\mu$ F ceramic capacitor (UMK107AB7105KA-T) were used. The maximum input voltage peak-peak ripple which happens when the input voltage is half of the output voltage can be calculated as follows:

$$V_{\text{ripple \_max }(C_{\text{in}})} = \frac{V_{\text{out}}}{32 \times L_{\text{in}} \times C_{\text{in}} \times f_{\text{sw}}^2} = \frac{14V}{32 \times 4.7 \,\mu\text{H} \times 711 \,\mu\text{F} \times 250 \,\text{kHz}^2} = 2 \,\text{mV}$$

(56)

The input cap RMS current is:

System Overview

$$I_{RMS\_Cin} = \frac{I_{out}}{1 - D} \times \frac{RR}{\sqrt{12}}$$

$$I_{RMS\_Cin} = \frac{2A}{1 - 0.57} \times \frac{0.6}{\sqrt{12}} = 0.8 \text{ A}$$

(57)

## Bootstrap Capacitor CBST (C64) and Boost Diode DBST (D3)

The bootstrap capacitor between the BST and SW pin supplies the gate current to charge the high-side Nchannel MOSFET device gate during each cycle's turn-on and also supplies recovery charge for the bootstrap diode. These current peaks can be several amperes. CBST must be a good-quality, low-ESR, ceramic capacitor located at the pins of the device to minimize potentially damaging voltage transients caused by trace inductance. The minimum value for the bootstrap capacitor is calculated as follows:

$$C_{BST\_min} = \frac{Q_g}{\Delta V_{BST}}$$

(58)

#### where

- $Q_g$  is the high-side N-channel MOSFET gate charge  $\Delta V_{BST}$  is the tolerable voltage droop on CBST, which is typically less than 5% of VCC or 0.15 V, conservatively

The chosen CSD18543Q3A MOSFET has 10 nC at 10 V, which means the C<sub>BST min</sub> is only 66.7 nF:

$$C_{BST\_min} = \frac{10 \text{ nF}}{0.15 \text{ V}} = 66.7 \text{ nF}$$

(59)

In this design, a 0.1-µF ceramic capacitor (C1005X5R1H104K050BB) was used based on the data sheet recommended value.

The voltage rating of DBST must be greater than the peak SW node voltage plus 16 V. The maximum switch node voltage is approximately the output voltage plus some ringing. Thus a minimum diode voltage rating including the 16 V margin is 30 V. A low leakage diode is mandatory for the bypass operation. The leakage current of DBST must be low enough for the BST charge pump to maintain a sufficient high-side driver supply voltage at high temperature. For this design, a 100-V, 1-A Schottky diode (MBR1H100SFT3G) was chosen.

#### **VCC Capacitor CVCC**

The primary purpose of the VCC capacitor is to supply the peak transient currents of the LO driver and bootstrap diode as well as provide stability for the VCC regulator. These peak currents can be several amperes. The value of CVCC must be at least 10 times greater than the value of CBST (i.e. 1 μF) and should be a good-quality, low-ESR, ceramic capacitor. Also, to account for voltage derating, the voltage rating should be at least 2 times the VCC voltage. In this design, a 10-µF, 16-V ceramic capacitor (EMK107BBJ106MA-T) was used.

# Output Voltage Divider RFB1 (R44), RFB2 (R48)

RFB1 and RFB2 set the output voltage level. The ratio of these resistors is calculated as follows:

$$\frac{\text{RFB2}}{\text{RFB1}} = \frac{V_{\text{out}}}{1.2 \,\text{V}} - 1 \tag{60}$$

The ratio between R<sub>COMP</sub> and RFB2 determines the mid-band gain, AFB\_MID. A larger value for RFB2 may require a corresponding larger value for R<sub>COMP</sub>. RFB2 should be large enough to keep the total divider power dissipation small. In this design, 39.9 k $\Omega$  and 3.65 k $\Omega$  were chosen for RFB2 and RFB1, respectively (i.e. Vout = 14.3 V).

# **Soft-Start Capacitor CSS (C65)**

The soft-start time ( $t_{SS}$ ) is the time for the output voltage to reach the target voltage from the input voltage. The soft-start time is not only proportional with the soft-start capacitor, but also depends on the input voltage. With 0.1  $\mu$ F of CSS, the soft-start time is calculated as follows:

$$t_{ss(max)} = \frac{C_{ss} \times 1.2 \text{ V}}{I_{ss}} \times D_{max} = \frac{0.1 \text{ } \mu\text{F} \times 1.2 \text{ V}}{10 \text{ } \mu\text{A}} \times 0.57 = 6.8 \text{ ms}$$

(61)

## **Restart Capacitor CRES (C66)**

The restart capacitor determines restart delay time  $t_{RD}$  and hiccup mode off time  $t_{RES}$ .  $t_{RD}$  must be greater than  $t_{SS(MAX)}$ . The minimum required value of  $C_{RES}$  can be calculated at the low input voltage as follows:

$$C_{RES (min)} = \frac{I_{RES} \times t_{ss (max)}}{V_{RES}} = \frac{30 \ \mu A \times 6.8 \ ms}{1.2 \ V} = 0.17 \mu F$$

(62)

A standard value of 0.33  $\mu$ F was selected for C<sub>RES</sub> (i.e. t<sub>RD</sub> = 13.2 ms).

#### Low-Side Power Switch Q

Selection of the power N-channel MOSFET devices by breaking down the losses is one way to compare the relative efficiencies of different devices. Losses in the low-side N-channel MOSFET device can be separated into conduction loss, switching loss, and gate charge loss. Low-side conduction loss of CSD18543Q3A is approximately calculated as follows:

$$P_{\text{COND (LS)}} = I_{\text{RMS}}^{2} \times R_{\text{DS\_ON (LS)}} \times 1.5 = D_{\text{max}} \times I_{\text{in}}^{2} \times R_{\text{DS\_ON (LS)}} \times 1.5$$

$$P_{\text{COND (LS)}} = 0.57 \times 5.2 \text{ A}^{2} \times 12 \text{ m}\Omega \times 1.5 = 278 \text{ mW}$$

(63)

Where, D is the duty cycle and the factor of 1.5 accounts for the increase in the N-channel MOSFET device onresistance due to heating. The  $R_{DS(ON)}$  used here is based on a conservative estimate ( $V_{gs}$  = 4.5 V) since the actual  $V_{gs}$  drive is about 6 V.

Switching loss occurs during the brief transition period as the low-side N-channel MOSFET device turns on and off. During the transition period both current and voltage are present in the channel of the N-channel MOSFET device. The low-side switching loss is approximately calculated as follows:

$$P_{SW(LS)} = 0.5 \times V_{out} \times I_{in} \times (t_R + t_F) \times f_{sw}$$

$$P_{SW(LS)} = 0.5 \times 14 \text{ V} \times 5.2 \text{ A} \times (3.5 \text{ ns} + 1.6 \text{ ns}) \times 250 \text{ kHz} = 46 \text{ mW}$$

(64)

$t_R$  and  $t_F$  are the switching times (including the rise and fall times) corresponding to the rise and fall transitions. During these times switching loss occurs for the low-side N-channel MOSFET device. They are calculated as follows:

$$\begin{split} t_R &= \frac{Q_{gs\,(afterVth\ )} + Q_{gd}}{I_{source}} = \frac{Q_{gs} - Q_{g,Vth} + Q_{gd}}{I_{source}} = \frac{3.1\ nC - 2\ nC + 1.7\ nC}{0.8\ A} = 3.5\ ns \\ t_F &= \frac{Q_{gs\,(afterVth\ )} + Q_{gd}}{I_{sink}} = \frac{Q_{gs} - Q_{g,Vth} + Q_{gd}}{I_{sink}} = \frac{3.1\ nC - 2\ nC + 1.7\ nC}{1.8A} = 1.6\ ns \end{split}$$

MOSFET gate losses are caused by the energy required to charge the MOSFET gate. That is, the total  $Q_g$  at the gate voltage of the circuit. These are both turn-on and turn-off gate losses. The power dissipation is approximately split between the gate driver and the MOSFET:

$$P_{G(LS)} = Q_{G(LS)} \times V_{GS(LS)} \times f_{sw} = C_{G(LS)} \times V_{GS(LS)}^{2} \times f_{sw}$$

$$P_{G(LS)} = Q_{G(LS)} \times V_{GS(LS)} \times f_{sw} = 7 \text{ nC} \times 6 \text{ V} \times 250 \text{ kHz} = 10.5 \text{ mW}$$

(66)

Note, the temperature factor assumption can be verified afterwards by determining the junction temperature from the total power dissipation calculations. The  $R_{DS(ON)}$  of the MOSFET versus temperature is shown in the data sheet:

$$T_J = T_{ambient} + R_{\theta JA} \times P_d = 40 \text{ C} + \frac{45 \text{ C}}{W} \times (278 + 46 + 10.5) \text{ mW} = 55 \text{ C}$$

(67)

From the data sheet, the normalized on-state resistance for CSD18543Q3A ( $V_{gs}$  = 4.5 V) is well under 1.2 at this junction temperature so our initial assumption of 1.5 is still valid. Note, the case temperature is very close to the junction temperature since  $R_{\theta,JC}$  = 1.9 °C/W.

An alternative design approach is to start with the target FET junction temperature, working back to the maximum  $R_{DS(ON)}$ , and then cross check with the data sheet  $R_{DS(ON)}$  at that temperature.

#### High-Side Power Switch QH and Additional Parallel Schottky Diode

Losses in the high-side N-channel MOSFET device can be separated into conduction loss, dead-time loss, reverse recovery loss, and gate charge loss. Switching loss is calculated for the low-side N-channel MOSFET device only. Switching loss in the high-side N-channel MOSFET device is negligible because the body diode of the high-side N-channel MOSFET device turns on before and after the high-side N-channel MOSFET device switches (i.e. zero voltage switching).

High-side conduction loss is approximately calculated as follows:

$$P_{\text{COND (HS)}} = I_{\text{RMS}}^{2} \times R_{\text{DS\_ON (LS)}} \times 1.5 = (1 - D) \times I_{\text{in}}^{2} \times R_{\text{DS_{ON (HS)}}} \times 1.5$$

$$P_{\text{COND (HS)}} = (1 - 0.57) \times 5.2 \text{ A}^{2} \times 12 \text{ m}\Omega \times 1.5 = 209 \text{ mW}$$

(68)

Dead-time loss is approximately calculated as follows:

$$P_{DT (HS)} = V_D \times I_{in} \times (t_{DLH} + t_{DHL}) \times f_{sw}$$

$$P_{DT (HS)} = 0.8 \text{ V} \times 5.2 \text{ A} \times (80 \text{ ns} + 80 \text{ ns}) \times 250 \text{ kHz} = 166 \text{ mW}$$

(69)

where

- V<sub>D</sub> is the forward voltage drop of the high-side NMOS body diode.

- t<sub>DLH</sub> and t<sub>DHL</sub> are the low to high and high to low dead time delays, respectively.

Reverse recovery characteristics of the high-side N-channel MOSFET switch strongly affect efficiency, especially when the output voltage is high. Small reverse recovery charge helps to increase the efficiency while also minimizes switching noise. Reverse recovery loss is calculated as follows:

$$P_{RR(HS)} = V_{out} \times Q_{RR} \times f_{sw} = 14 \text{ V} \times 37 \text{ nC} \times 250 \text{ kHz} = 130 \text{ mW}$$

(70)

Gate charge loss is calculated as follows:

$$P_{G(HS)} = Q_{G(HS)} \times V_{GS(HS)} \times f_{sw} = 7 \text{ nC} \times 6 \text{ V} \times 250 \text{ kHz} = 10.5 \text{ mW}$$

(71)

Note, an additional Schottky diode can be placed in parallel with the high-side switch to improve efficiency. Usually, the power rating of this parallel Schottky diode can be less than the high-side switch's because the diode conducts only during dead-times. The power rating of the parallel diode should be equivalent or higher than high-side switch's if bypass operation is required, hiccup mode operation is required or any load exists before switching.

#### **Bias Losses**

An additional source of power loss includes bias losses. The total bias current budget is about 10 mA. With a 6 V input, the loss is 60 mW from biasing.

#### **Snubber Components**

A resistor-capacitor snubber network across the high-side N-channel MOSFET device reduces ringing and spikes at the switching node. Selecting the values for the snubber is best accomplished through empirical methods. A 470-pF capacitor and 8.2-Ω resistor were chosen as placeholders in this design.

## Loop Compensation Components CCOMP, RCOMP, CHF

$R_{COMP}$ ,  $C_{COMP}$  and  $C_{HF}$  configure the error amplifier gain and phase characteristics to produce a stable voltage loop. For a quick start, follow the following four steps:

#### 1. Select:

Select the cross over frequency (f<sub>cross</sub>) at one fourth of the RHP zero or one tenth of the switching frequency, whichever is lower. RHP zero at minimum input voltage should be considered if the input voltage range is wide.

$$f_{Z\_RHP} = \frac{R_{load} \times (1 - D)^2}{2\pi \times L} = 44 \text{ kHZ}$$

(72)

$$f_{cross} \le \frac{f_{sw}}{10} \text{ or } \frac{f_{Z\_RHP}}{4}$$

(73)

$$\frac{f_{sw}}{10} = 25 \text{ kHz} \tag{74}$$

$$\frac{f_{Z\_RHP}}{4} = \frac{R_{load} \times (1 - D)^2}{4 \times 2\pi \times L} = \frac{\frac{V_{out}}{I_{out}} \times (1 - D)^2}{4 \times 2\pi \times L} = \frac{\frac{14 \text{ V}}{2 \text{ A}} \times (1 - 0.57)^2}{4 \times 2\pi \times 4.7 \text{ }\mu\text{H}} = 11 \text{ kHZ}$$

(75)

In this design, a 5 kHz crossover frequency was used instead of 11 kHz for added margin.

Note, the size of the output capacitor plays a significant role in how wide the loop bandwidth is (Reference SLVA452). Once the minimum capacitance is met, meeting the output ripple specification, the following equation is used to estimate the output capacitance needed to meet the application's load transient requirement for the maximum voltage dip ( $V_{TRAN}$ ) after a given load step ( $\Delta I_{TRAN}$ ).  $V_{TRAN}$  is 2.5% of output voltage and  $\Delta I_{TRAN}$  is 2.5%.

$$C_{\text{out\_min}} = \frac{\Delta I_{\text{TRAN}}}{2\pi \times f_{\text{cross}} \times V_{\text{TRAN}}} = \frac{2 \text{ A}}{2\pi \times 5 \text{ kHZ} \times 0.35 \text{ V}} = 182 \,\mu\text{F}$$

(76)

#### 2. Determine required R<sub>COMP</sub> to set crossover.

Knowing f<sub>cross</sub>, R<sub>COMP</sub> is calculated as follows:

$$R_{COMP} = f_{cross} \times \pi \times Rs \times RFB2 \times 10 \times C_{out} \times \frac{V_{out}}{V_{in}}$$

$$R_{COMP} = 5 \text{ kHz} \times \pi \times 8 \text{ m}\Omega \times 39 \text{ k}\Omega \times 10 \times 210 \text{ }\mu\text{F} \times \frac{14 \text{ V}}{6 \text{ V}} = 24 \text{ k}\Omega$$

(77)

In this design, 23.2 k $\Omega$  was selected for R<sub>COMP</sub>.

## 3. Determine C<sub>COMP</sub> to cancel load pole.

Place error amplifier zero at the twice of load pole frequency. For boost converters with ceramic capacitor(s) in parallel with a much larger, high-ESR capacitor, use the total capacitance in parallel for  $C_{out}$  for this step (Reference SLVA452). Knowing  $R_{COMP}$ ,  $C_{COMP}$  is calculated as follows:

$$\omega_{P_{LF}} = \frac{2}{R_{load} \times C_{out}} = \frac{2}{7 \Omega \times 210 \,\mu\text{F}} = 1361 \frac{\text{rad}}{\text{s}} \text{ (i. e. } f_{P_{LF}} = 217 \text{ Hz)}$$

(78)

www.tij.co.jp

$$C_{COMP} = \frac{R_{load} \times C_{out}}{4 \times R_{COMP}} = \frac{\frac{14 \text{ V}}{2 \text{ A}} \times 210 \,\mu\text{F}}{4 \times 23.2 \,\text{k}\Omega} = 15.8 \,\text{nF}$$

(79)

A standard value of 15 nF is recommended.

4. Determine C<sub>HF</sub> to cancel ESR zero.

$$f_{Z\_EA} = \frac{1}{2\pi \times R_{COMP} \times C_{COMP}} = \frac{1}{2\pi \times 23.2 \text{ k}\Omega \times 15 \text{ nF}} = 457 \text{ Hz}$$

(80)

For boost converters with ceramic capacitor(s) in parallel with a much larger, high-ESR capacitor, only use the high-ESR capacitor's capacitance and ESR for this step (Reference SLVA452). Knowing  $R_{COMP}$ , RESR and  $C_{COMP}$ ,  $C_{HF}$  is calculated as follows:

$$C_{HF} = \frac{R_{ESR} \times C_{out} \times C_{COMP}}{R_{COMP} \times C_{COMP} - R_{ESR} \times C_{out}} = \frac{340 \text{ m}\Omega \times 180 \text{ }\mu\text{F} \times 33 \text{ nF}}{23.2 \text{ }k\Omega \times 33 \text{ nF} - 340 \text{ }m\Omega \times 180 \text{ }\mu\text{F}} = 2.87 \text{ nF}$$

(81)

A standard value of 2.7 nF is recommended.

$$f_{Z\_ESR} = \frac{1}{2\pi \times R_{ESR} \times C_{out}} = \frac{1}{2\pi \times 340 \text{ m}\Omega \times 180 \text{ }\mu\text{F}} = 2.6 \text{ kHz}$$

(82)

$$f_{P\_EA} = \frac{1}{2\pi \times R_{COMP} \times C_{HF}} = \frac{1}{2\pi \times 23.2 \text{ k}\Omega \times 2.7 \text{ nF}} = 2.54 \text{ kHz}$$

(83)

Alternatively, if a lower ESR bulk capacitor were used the  $f_{Z\_ESR}$  can be moved beyond the  $f_{cross}$ .

#### Bypass Operation (VOUT = VIN)

MODE pin is tied to 3.3 V to enable Forced-PWM (FPWM). Forced-PWM mode is the recommended PWM configuration when bypass operation is required.

#### 2.2.3.3 LMR33630 Buck Design Calculations

Based on the key system specification, the maximum solenoid load is 1.7 A. The boost-buck DC-DC power stage, consisting of LM5211 and LMR33630, is designed to support 2 A of continuous load. Note, WEBENCH® Power Designer was used to help design the power stage. The key design calculations for the LMR3360 Buck Stage are shown below. For more details on design considerations, please refer to the device data sheet.

表 2-5. Buck stage summary

| PARAMETER        | SPECIFICATION | COMMENTS           |

|------------------|---------------|--------------------|

| Input Voltage    | 14-28 V       | From boost stage   |

| Input Power      | 26.7 W        | Max, η = 90%       |

| Output Voltage   | 12 V          | For solenoid drive |

| Output Power     | 24 W          | Max                |

| Max Load Current | 2 A           | Vout = 12 V (24 W) |

The choice of switching frequency is a compromise between conversion efficiency and overall solution size. For this design, 400 kHz was chosen (i.e. LMR33630A variant) as a compromise between efficiency and overall solution size.

#### **Setting the Output Voltage**

The output voltage of the LMR33630 is externally adjustable using a resistor divider network. The target output is 12 V. Start with the recommended 100 k $\Omega$  value. The R<sub>FBB</sub> is:

$$R_{FBB} = \frac{R_{FBT}}{\frac{V_{out}}{V_{ref}} - 1}$$

$$R_{FBB} = \frac{100 \text{ k}\Omega}{\frac{12V}{1V} - 1} = 9.1 \text{ k}\Omega$$

(84)

#### 9.1 k $\Omega$ was selected.

#### **Inductor Selection**

The first step to calculate the peak inductor/switch current is to determine the duty cycle, D, for the maximum input voltage. The maximum input voltage is used because this leads to the maximum switch current:

$$D_{\min} = \frac{V_{\text{out}}}{V_{\text{in}}} = \frac{12 \text{ V}}{28 \text{ V}} = 0.43 \tag{85}$$

The parameters for selecting the inductor are the inductance and saturation current. The inductance is based on the desired peak-to-peak ripple current and is normally chosen to be in the range of 20-40 % of the maximum output current. Note that when selecting the ripple current for applications with much smaller maximum load (2 A) than the maximum available from the device (3 A), the maximum device current should be used.

$$L = \frac{V_{\text{out}}}{I_{\text{out}} \times RR \times f_{\text{sw}}} \times (1 - D)$$

(86)

The maximum inductance is limited by the minimum current ripple required for the current mode control to perform correctly. As a rule-of thumb, the minimum inductor ripple current must be no less than about 10% of the device maximum rated current under nominal conditions:

$$L_{\text{max}} = \frac{12 \text{ V}}{3 \text{ A} \times 0.1 \times 400 \text{ kHz}} \times (1 - 0.43) = 57 \text{ }\mu\text{H}$$

(87)

From the data sheet, the minimum inductance is given by:

$$\begin{split} L_{min} &= 0.28 \times \frac{V_{out}}{f_{sw}} \\ L_{min} &= 0.28 \times \frac{12 \text{ V}}{400 \text{ kHz}} = 8.4 \text{ } \mu\text{H} \end{split} \tag{88}$$

RR of 0.3 was selected for the following inductance calculation:

$$L = \frac{12 \text{ V}}{3A \times 0.3 \times 400 \text{ kHz}} \times (1 - 0.43) = 19 \,\mu\text{H}$$

(89)

For this design 33  $\mu$ H was selected. This value is inside the recommended inductance range. Alternatively, a smaller inductance 22  $\mu$ H (SPM7054VT-220M-D) could be used since the saturation current rating would be higher.

The actual worst-case ripple current is:

$$\Delta I_{L} = \frac{V_{out}}{f_{sw} \times L} \times (1 - D)$$

$$\Delta I_{L} = \frac{12V}{400 \text{kHz} \times 33 \text{ } \mu\text{H}} \times (1 - 0.43) = 0.52 \text{ A}$$

(90)

The actual ripple ratio is:

www.tij.co.jp

$$RR = \frac{\Delta I_L}{I_{\text{out}}} = \frac{0.52 \text{ A}}{3 \text{ A}} = 0.17$$

(91)

The peak inductor/switch/diode current and the minimum saturation current rating of the inductor plus a 25% margin are calculated as follows:

$$I_{\text{peak}} = I_{\text{out}} \times \left(1 + \frac{\text{RR}}{2}\right)$$

$$I_{\text{peak}} = 3 \text{ A} \times \left(1 + \frac{0.17}{2}\right) \times 1.25 = 4.1 \text{ A}$$

(92)

However, the LM33630 has specific inductor saturation requirement for its normal operation due to internal current limits. Ideally, the saturation current rating of the inductor must be at least as large as the high-side switch current limit, ISC. The ISC is 4.5 A typical and 5 A max.

In any case, the inductor saturation current must not be less than the device low-side current limit,  $I_{LIMIT}$ . The  $I_{LIMIT}$  is 3.5 A typical and 4.1 A max.

In this design, the selected inductor (SPM7054VT-330M-D) has saturation ratings of 3.6 A ( $\Delta L$ =-20%) and 4.9 A  $\Delta L$ =-30%). Based on the data sheet, this inductor RMS rating is well suited to handle 3.4 A with a 40 °C rise.

For the RMS current calculations, the 2 A max application current is used instead of the device maximum:

$$I_{RMS} = I_{out} \sqrt{1 + \frac{RR^2}{12}}$$

$$I_{RMS} = 2 A \sqrt{1 + \frac{0.17^2}{12}} = 2.01 A$$

(93)

Note, I<sub>RMS</sub> is approximately I<sub>out</sub> given a small RR value.

Inductor wire loss is calculated as follows:

$$P_{IND\_DC} = I_{RMS}^2 \times R \cong I_{out}^2 \times R = 2 A^2 \times 97.7 \text{ m}\Omega = 0.39 \text{ W}$$

(94)

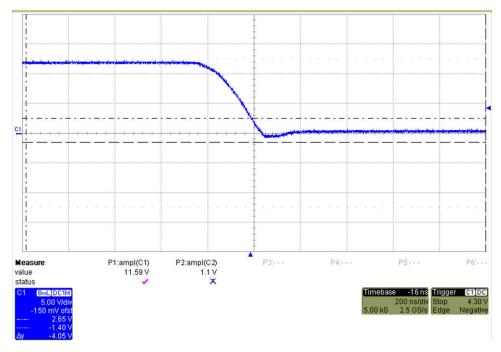

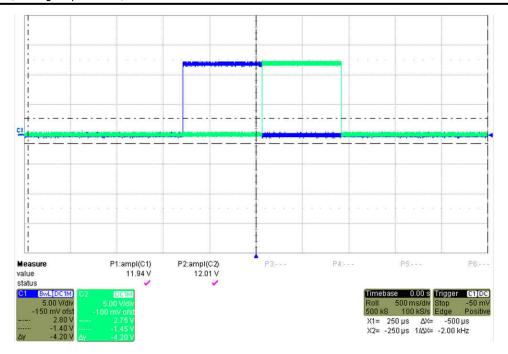

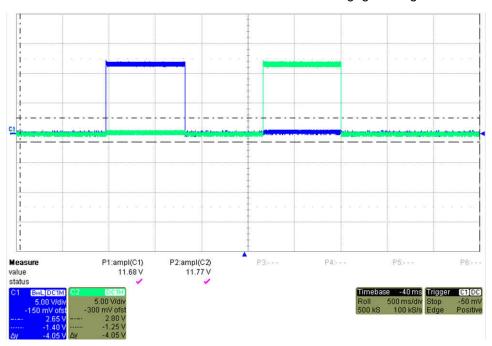

#### **Output Capacitor Selection**