# Phase-Noise Performance of the CDC7005 at UMTS and CDMA Frequencies

Loan Nguyen / Kal Mustafa

HPA / High-Speed Communications (HSC)

#### **ABSTRACT**

This application brief presents phase-noise data taken on Texas Instruments CDC7005 jitter cleaner and synchronizer PLL. The phase noise performance of CDC7005 depends on the phase noise of the reference clock, the voltage-controlled crystal oscillator (VCXO) clock, and the CDC7005 itself. This applications brief shows the phase noise performance of the CDC7005 clock synthesizer at the most popular Universal Mobile Telecommunications System (UMTS) and Code Division Multiple Access (CDMA) frequencies. It helps the user in choosing the right clocking solution for their particular applications. The test results reveal that the CDC7005 can provide clock outputs better than –145-dBc/Hz phase noises at 1-MHz offset from the carrier frequency with proper VCXO and loop bandwidth selection. Low phase noise is required for most base station applications such as UMTS and CDMA and its derivatives as well as many other jitter stringent applications.

#### Contents

| 1  | Introduction                                                |

|----|-------------------------------------------------------------|

| 2  | Test and Measurements Setup                                 |

| 3  | Summary and Conclusion                                      |

| 4  | Test Summary                                                |

| 5  | Acknowledgments13                                           |

| 6  | References                                                  |

|    | List of Figures                                             |

| 1  | Test Setup of the Phase-Noise Measurements                  |

| 2  | External Passive Loop Filter Circuit on the CDC7005 EVM     |

| 3  | Phase Noise of the CDC7005 at 30.72 MHz Driven by HP8664A   |

| 4  | Phase Noise of the HP8664A at 30.72 MHz                     |

| 5  | Phase Noise of the CDC7005 at 61.44 MHz Driven by HP8664A   |

| 6  | Phase Noise of the HP8664A at 61.44 MHz                     |

| 7  | Phase Noise of the CDC7005 at 76.8 MHz Driven by HP8664A    |

| 8  | Phase Noise of the HP8664A at 76.8 MHz                      |

| 9  | Phase Noise of the CDC7005 at 78.6432 MHz Driven by HP8664A |

| 10 | Phase Noise of the HP8664A at 78.6432 MHz                   |

Trademarks are the property of their respective owners.

| 11 | Phase Noise of the CDC7005 at 92.16 MHz Driven by HP8664A                 | . 8 |

|----|---------------------------------------------------------------------------|-----|

| 12 | Phase Noise of the HP8664A at 92.16 MHz                                   | . 8 |

| 13 | Phase Noise of the CDC7005 at 122.88 MHz Driven by HP8664A                | . 9 |

| 14 | Phase Noise of the HP8664A at 122.88 MHz                                  | . 9 |

| 15 | Phase Noise of the CDC7005 at 245.76 MHz Driven by HP8664A                | 10  |

| 16 | Phase Noise of the HP8664A at 245.76 MHz                                  | 10  |

| 17 | Phase Noise of the CDC7005 at 491.52 MHz Driven by HP8664A                | 11  |

| 18 | Phase Noise of the HP8664A at 491.52 MHz                                  | 11  |

| 19 | Closed-Loop Phase Noise of the CDC7005 at 61.44 MHz                       | 12  |

| 20 | Phase Noise of Toyocom 61.44 MHz VCXO                                     | 12  |

| 21 | Close-Loop Phase Noise Performance of CDC7005 With Toyocom 61.44-MHz VCXO | 13  |

#### 1 Introduction

Phase noise (PN) is the short-term instability caused by variation of frequency (phase) of a signal referenced to the carrier level and a function of the carrier offset (i.e., relative noise level within a 1-Hz bandwidth). Integration of PN over a given frequency band yields phase jitter RMS.

The CDC7005 is a low phase noise/low jitter clock synthesizer and jitter cleaner with five programmable LVPECL outputs. It requires either an external or internal low pass loop filter in addition to an external VCXO to complete the phase locked loop. By selecting VCXO and loop bandwidth, the device achieves the best performance at its outputs. This brief includes phase noise plots of the most common frequencies used in base station applications. In addition, the phase noise of the clock source feeding the CDC7005 is included for completeness.

# 2 Test and Measurements Setup

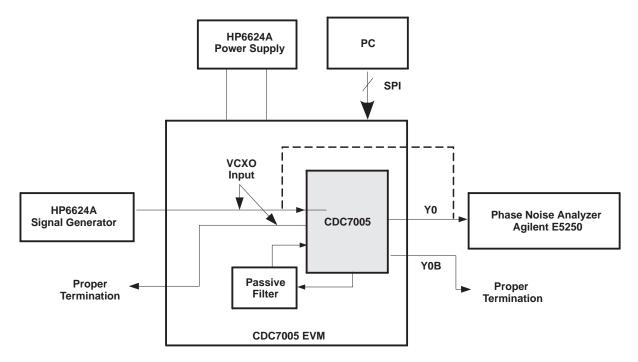

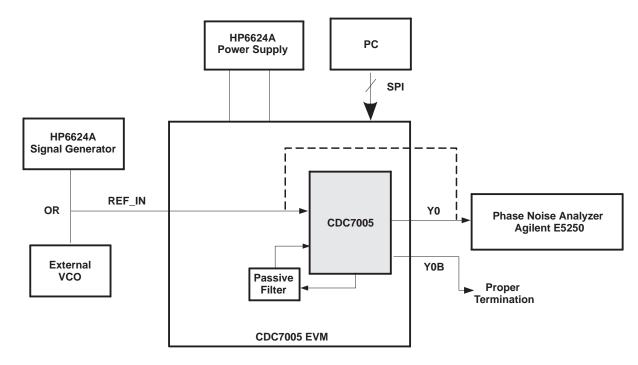

The block diagrams of the test setup are shown in Figure 1. An input reference clock from the HP8664A signal generator is fed into the Agilent E5250 and the phase noise of the source is measured (indicated by the dotted line). The same signal is then fed into one leg of the VCXO\_IN of the CDC7005 and the phase noise is measured through the Agilent E5250 analyzer (open-loop).

All measurements were taken at nominal 3.3-V power supply, room temperature, and open loop PLL. The HP8644 as a signal generator, the CDC7005 evaluation module (EVM) in 1x mode, and the Agilent E5250 phase noise test system were used. The test setup below was used for most the phase noise testing. The phase noise can be measured up to 40 MHz from the carrier frequency, although some measurements were taken up to 10 MHz or 1 MHz from the carrier depending upon the desired clock frequency.

Figure 1. Test Setup of the Phase-Noise Measurements

Figure 2. External Passive Loop Filter Circuit on the CDC7005 EVM

## 3 Summary and Conclusion

The CDC7005 PLL tracks the input reference signal up to the loop bandwidth, while it follows the VCO (here VCXO) phase noise floor at frequencies above the loop bandwidth. The VCXO phase noise performance is critical in achieving good phase noise performance and meeting stringent phase noise requirements in base station applications.

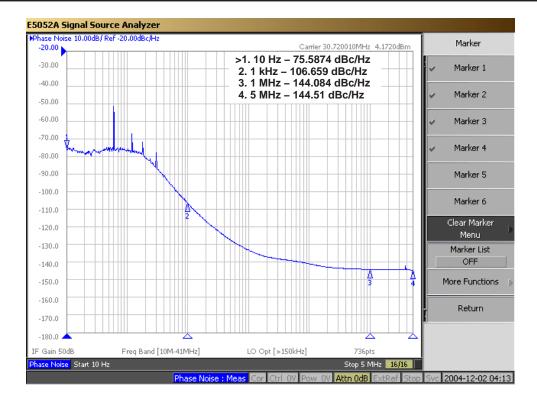

Figure 3. Phase Noise of the CDC7005 at 30.72 MHz Driven by HP8664A

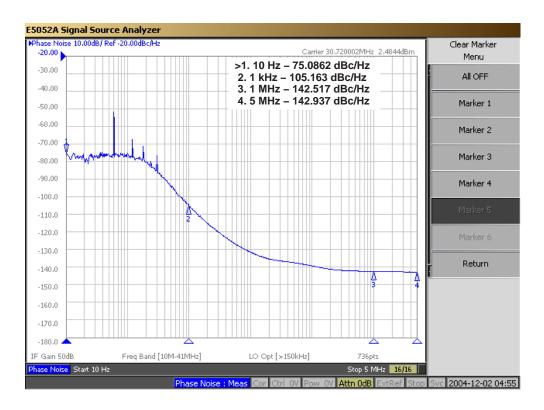

Figure 4. Phase Noise of the HP8664A at 30.72 MHz

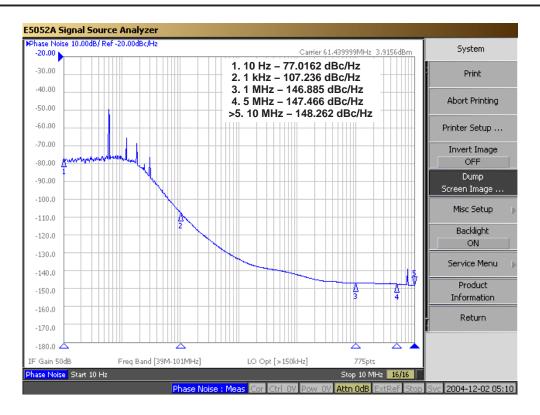

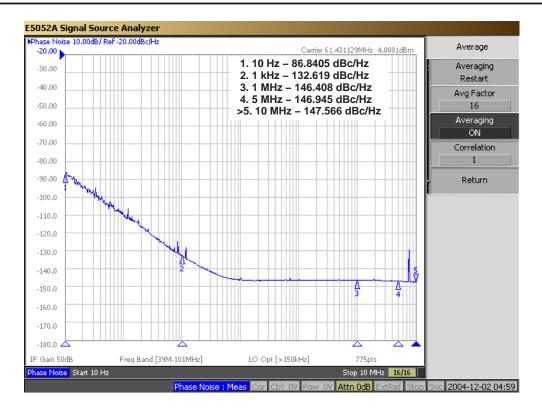

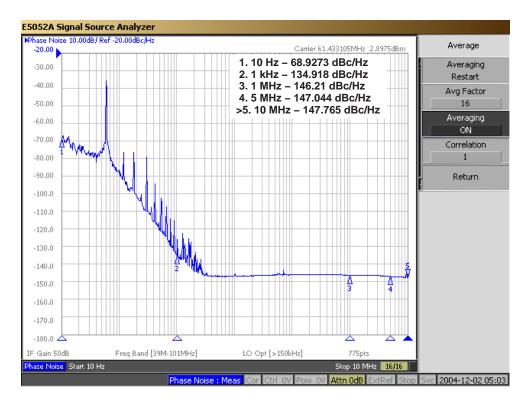

Figure 5. Phase Noise of the CDC7005 at 61.44 MHz Driven by HP8664A

Figure 6. Phase Noise of the HP8664A at 61.44 MHz

Figure 7. Phase Noise of the CDC7005 at 76.8 MHz Driven by HP8664A

Figure 8. Phase Noise of the HP8664A at 76.8 MHz

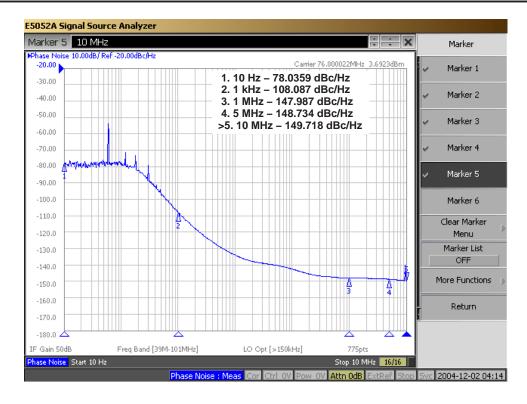

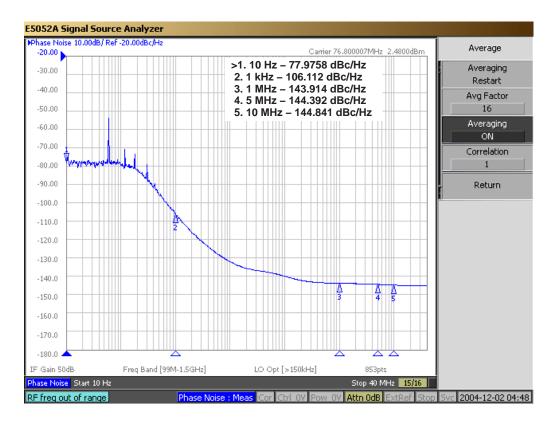

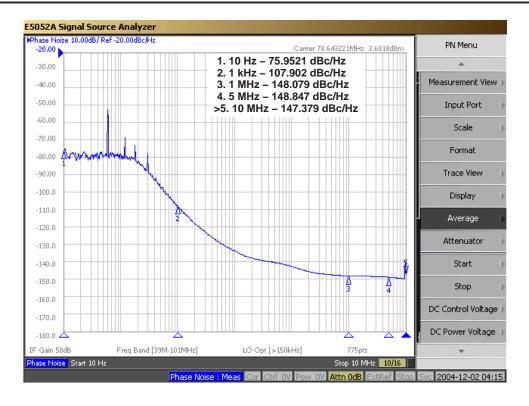

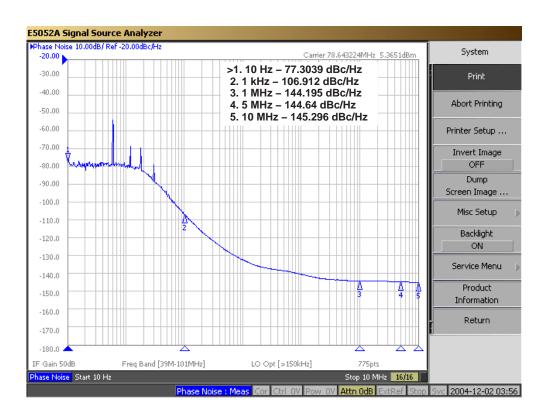

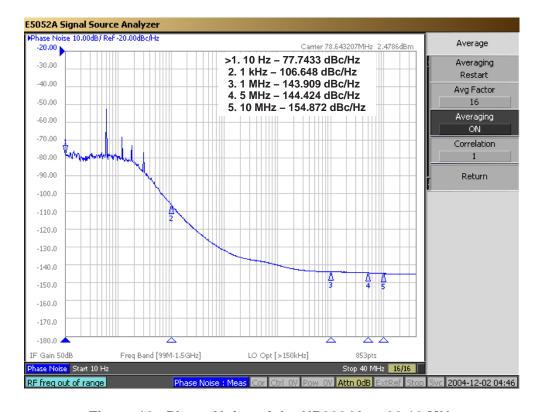

Figure 9. Phase Noise of the CDC7005 at 78.6432 MHz Driven by HP8664A

Figure 10. Phase Noise of the HP8664A at 78.6432 MHz

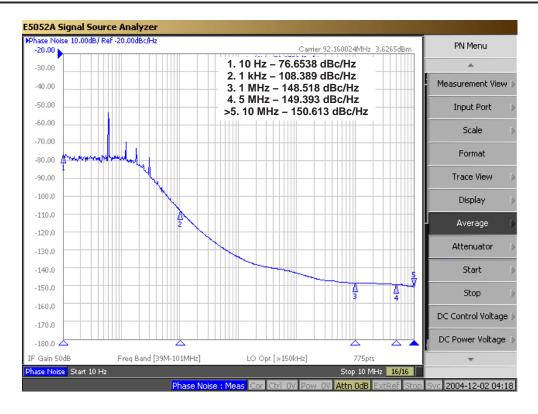

Figure 11. Phase Noise of the CDC7005 at 92.16 MHz Driven by HP8664A

Figure 12. Phase Noise of the HP8664A at 92.16 MHz

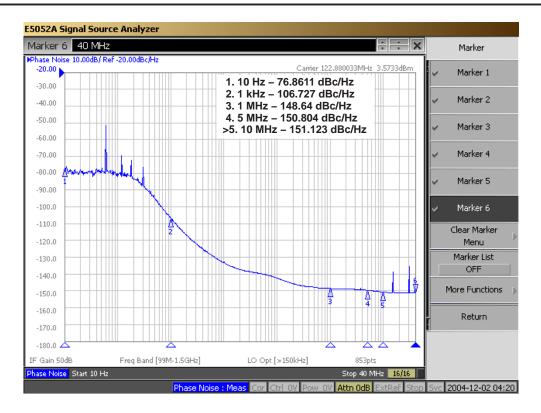

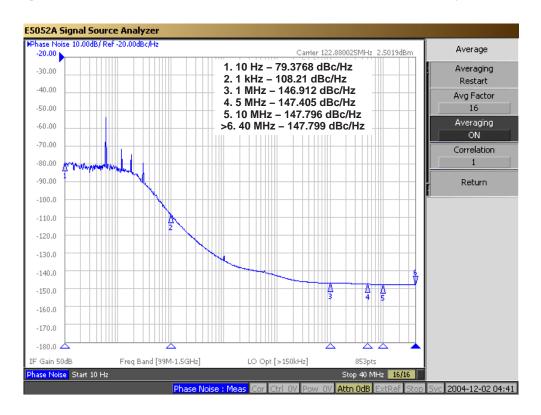

Figure 13. Phase Noise of the CDC7005 at 122.88 MHz Driven by HP8664A

Figure 14. Phase Noise of the HP8664A at 122.88 MHz

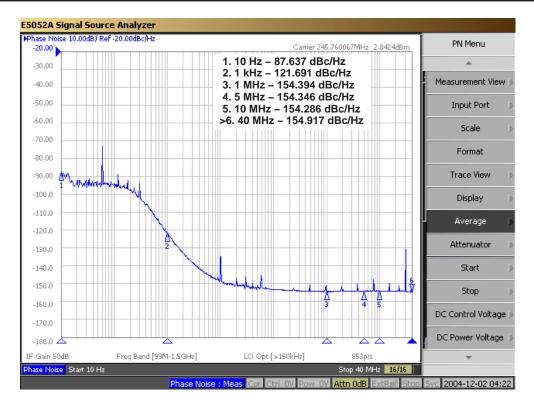

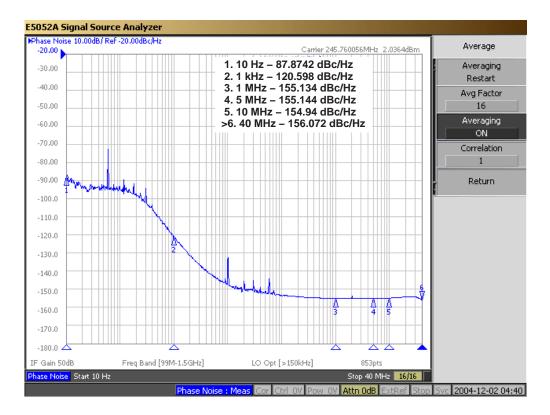

Figure 15. Phase Noise of the CDC7005 at 245.76 MHz Driven by HP8664A

Figure 16. Phase Noise of the HP8664A at 245.76 MHz

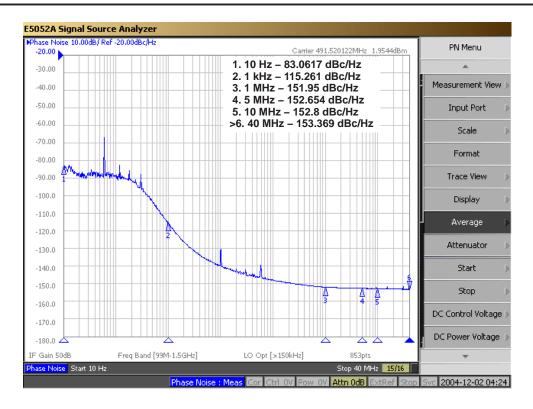

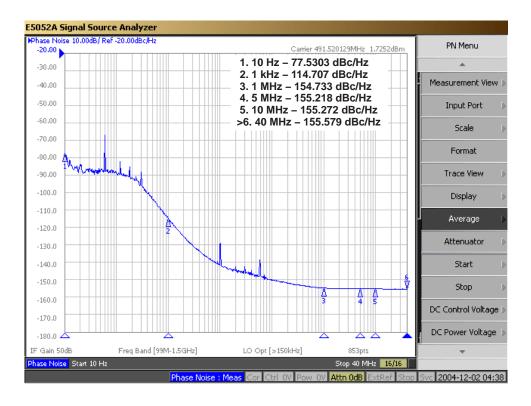

Figure 17. Phase Noise of the CDC7005 at 491.52 MHz Driven by HP8664A

Figure 18. Phase Noise of the HP8664A at 491.52 MHz

Figure 19. Closed-Loop Phase Noise of the CDC7005 at 61.44 MHz

Figure 20. Phase Noise of Toyocom 61.44 MHz VCXO

Figure 21. Close-Loop Phase Noise Performance of CDC7005 With Toyocom 61.44-MHz VCXO

From the data above, it is evident that a low phase noise clock output is easily attainable from the CDC7005, with the proper selection of differential or single-ended VCXO's.

## 4 Test Summary

PC

The test results reveal that the CDC7005 can provide clock outputs better than –145-dBc/Hz phase noises at 1-MHz offset from the carrier frequency. Low phase noise is required for most base station application such as UMTS and CDMA and its derivatives as well as many other jitter stringent applications.

## 5 Acknowledgments

The authors of this application brief would like to thank the following people for proving the necessary samples and equipments in conducting these tests:

- 1. Doyce Ramey, Texas Instruments Inc., RF Wireless group, dramey@ti.com

- 2. Paul Woodley, O&M Sales, Inc., Paul.Woodley@o-m-sales.com

- 3. Micky Kilpatrick, Agilent Technologies, micky kilpatrick@agilent.com

### 6 References

- 4. CDC7005 data sheet, Texas Instruments, SCAS685

- 5. CDC7005 EVM user's guide, Texas Instruments, SCAU005

- 6. Using the CDC70005 as a 1:5 PECL Buffer With Programmable Divider Ratio, Texas Instruments, http://focus.ti.com/lit/an/scaa060/scaa060.pdf

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| e               |

|-----------------|

| d               |

| trol            |

|                 |

| work            |

|                 |

|                 |

|                 |

|                 |

| d<br>trol<br>wo |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated