# Application Note Leveraging Edge Rate Accelerators with Auto-Sensing Level Shifters

Michael Ikwuyum, Ajith Narayanasetty, Sahil Garg

#### ABSTRACT

Level shifting one voltage signal level into another voltage signal level from a host or driver to a peripheral is not always straight forward. System engineers often select auto-sensing bidirectional voltage translators due to their perceived ease-of-use. In certain use cases, the driver and peripheral both can act as a driver, in which case the transmitter and receiver can both drive their data lines. A voltage translator needs to auto-sense the direction to send or receive the signals but also account for fast data transfer and good signal integrity. How does the voltage translator not only auto-sense the direction to send or receive the signals but also account for fast data transfer and good signal integrity? Auto-sensing devices must be designed with weaker drive strength to enable being overdriven by their hosts. Such small drive strength can impact signal integrity at higher speeds. As systems become increasingly sophisticated with more level shifters and more peripherals, there is an ever expanding need for increased data throughput and signal integrity. This is where one-shots (also known as *monostable multi-vibrators'* or *edge rate accelerators*), can help. This application note discusses the major contributors and challenges for auto-sensing level shifters at high speeds and how one-shots impact such challenges.

For replacing auto-sensing level shifters with more suitable recommendations dependent on application types, see *Do's and Don'ts for TXB and TXS Voltage Level-Shifters with Edge Rate Accelerators*.

**Note** All data collected for this application note correlates to the typical performance of One-Shots. Refer to individual device data sheets for specific recommendations.

#### **Table of Contents**

| 1 Introduction                                 | 2 |

|------------------------------------------------|---|

| 2 One-Shot Performance                         | 3 |

| 3 Design Considerations                        | 4 |

| 3.1 PCB Layout Design with the One-Shots       |   |

| 3.2 Effects of External Resistors on One-Shots | 4 |

| 3.3 Effects of Slow Inputs on the One-Shots    |   |

| 3.4 Effects of Speed and Loading on One-Shots  |   |

| 3.5 Effects of Temperature on One-Shots        |   |

| 4 Summary                                      | 7 |

| 5 References                                   |   |

#### List of Figures

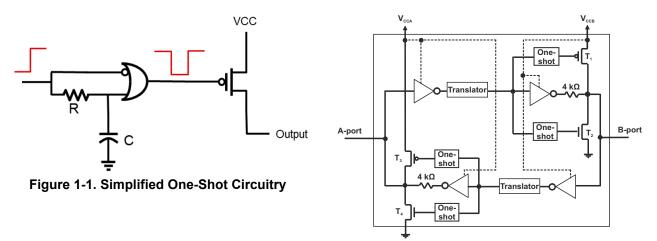

| Figure 1-1. Simplified One-Shot Circuitry                        | <mark>2</mark> |

|------------------------------------------------------------------|----------------|

| Figure 1-2. TXB Architecture                                     |                |

| Figure 1-3. TXS Architecture                                     | 3              |

| Figure 2-1. One-Shot Performance at Slower Speed                 | 4              |

| Figure 2-2. One-Shot Performance at the Data Sheet Max Data Rate | 4              |

| Figure 3-1. Impact of a Slow Input Rise Time, 11 ns/V            | 5              |

| Figure 3-2. Impact of a Slower Input Rise Time, 2.4 µS/V         | 5              |

| Figure 3-3. Impact of Loading on Rise and Fall Times             | 5              |

| Figure 3-4. Impact of Loading on the O.S.                        | 5              |

| Figure 3-5. 15 pF Load Above the Max Data Rate                   |                |

|                                                                  |                |

Leveraging Edge Rate Accelerators with Auto-Sensing Level Shifters

| Figure 3-6. 100 pF Load Above the Max Data Rate                                  | 5 |

|----------------------------------------------------------------------------------|---|

| Figure 3-7. 15 pF Load Below the Max Data Rate                                   |   |

| Figure 3-8. 100 pF Load Below the Max Data Rate                                  |   |

| Figure 3-9. Lumped Capacitance Impact at Max Data Rate                           | 6 |

| Figure 3-10. Reflections at Cold, Room and Hot Temp                              | 6 |

| Figure 3-11. Amplified One-shot Reflections                                      | 6 |

| Figure 3-12. Typical Temperature Impact on Ron                                   | 7 |

| Figure 3-13. Typical Temperature Impact on Pulse Width Duration For the One-Shot | 7 |

|                                                                                  |   |

#### Trademarks

All trademarks are the property of their respective owners.

#### 1 Introduction

Auto-Sensing level shifters are named so because their input(s) and output(s), can be used in applications to perform the same functionality to send and receive signals. The I/Os are designed with weaker drive strength than devices from other level shifting families, to be easily overdriven by the hosts. This makes auto-direction devices a requirement for bidirectional interfaces such as I<sup>2</sup>C, MDIO, Quad-SPI, etc.

One-shots (OS) are named so because their outputs will create a single pulse of a set time period for each input trigger. The most common input trigger method is a rising or falling edge. These circuits are also often referred to as edge rate accelerators because they produce an increased output drive strength for a short time, resulting in faster output transition rates over a device that does not include these circuits.

As part of the level shifter portfolio, TI offers *TXS and TXB Level Shifter Families* with one-shots. The one-shots are composed of a combination of logic with on-chip components. When the input of the device triggers, the one-shot circuit generates a pulse to the output MOSFET as shown in Table 1-1, bypassing the TXB's typical 4  $k\Omega$  output driver to produce a low-impedance output driver for a short time, improving the output's rise and fall time. This pulse width is a function of RC time constant and can also be impacted by additional or external RC components. It may also have variations with device-to-device or temperature.

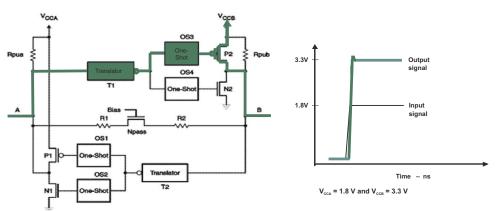

Figure 1-2. TXB Architecture

Figure 1-3. TXS Architecture

When the one-shot is triggered by an input, the output switches to an active state – *on-state* of the one-shot output for a set period of time and returns to its resting state – *off-state*, similar to *Figure 1-3*.

While the one-shot is active, the output resistance of the device is decreased. The low resistance path to  $V_{CCB}$  through the pFET (P2) will cause the output to rise towards  $V_{CCB}$  very quickly. Thereby, increasing the edge rate and maintaining DC drive for bidirectional I/Os.

After the one-shot expires, the internal pull-up of the TXS device drives the line high and maintains a steady state. The same is applicable with the internal buffer resistor of the TXB device.

Faster rising or falling input edges and the external load resistance and capacitance needs to be considered by ensuring < 70 pF to prevent damages to the device due to excessive current or power consumption. Section 3.3 and Table 1-1 further provides a general reference attributed to fast rising or falling inputs per lumped capacitance to avoid expiring the one-shot before the output reaches steady state. Similar to *Implications of Slow or Floating CMOS Inputs*, slower rising and falling inputs can also cause damage to the device due to excessive current / power consumption. For more guidelines using devices with one-shots, see Similar to *Do's and Don'ts For TXS and TXB Voltage Level Shifters with Edge Rate Accelerators*.

From using the standard 2.2 time constant, charge of ~86.5% transition times can be estimated (typically measured from 10% to 90%). Note that the typical pull-up resistance without the one-shot active is 10 k $\Omega$  and the typicall pull-up resistance with the one-shot active is 50  $\Omega$ . With typical load capacitance of 15 pF, the typical rise and fall times are compared below showing how the one-shots helps for faster rise/fall times. Section 2 further clarifies implications of slower rise/fall times for data throughput.

|                             | Without one-shot | With one-shot |

|-----------------------------|------------------|---------------|

| Rise or Fall time (2.2×R×C) | 330 ns           | 1.7 ns        |

#### 2 One-Shot Performance

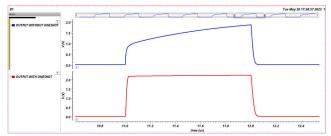

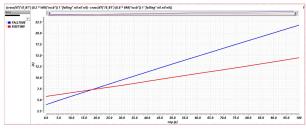

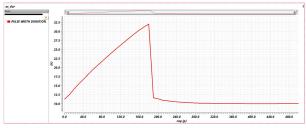

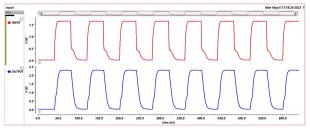

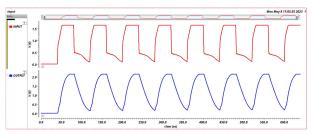

The one-shot performance in Figure 2-1 and Figure 2-2 shows the difference between the TXS / TXB device with and without the one-shot. Similar to Table 1-1, the figures highlight a faster rising edge with the one-shot as compared to the device without the one-shot. The device without the one-shot has a weaker drive with a higher output resistance, yielding a slow response. As the speed gets faster, its output level will be unable to reach the desired level. This highlights the advantage of the one-shot for bidirectional applications needing increased data throughput for better signal integrity.

Note

Refer to individual device data sheets for specific data rate recommendations.

510.0

Figure 2-1. One-Shot Performance at Slower Speed

## 3 Design Considerations

### 3.1 PCB Layout Design with the One-Shots

To help minimize noise with switching transients and further avoid false triggers from ringing / reflections while interacting with the one-shots, bypass capacitors should be used on both power supplies, V<sub>CCA</sub> and V<sub>CCB</sub>. Careful considerations should be made for short path bypass capacitors, as close as possible to both  $V_{CC}$ supplies and GND while designing printed circuit boards (PCB) with devices with one-shots.

2.0 1.75

0.5

0.25

360.0 390.0 420.0

Figure 2-2. One-Shot Performance at the Data

**Sheet Max Data Rate**

PCB signal trace-lengths must be kept short enough so that the round-trip delay of any reflection is less than the one-shot duration, typically 10ns to 30 ns. With minimal parasitic capacitance and inductance from shorter traces, reflections encounter low impedance at the source driver further avoiding false triggering of the one-shot for an abnormal output pulse width, output signal oscillations, or other adverse system-level effects.

The following equation for the board effective relative permittivity can be used to determine the maximum trace length to help remain within the design's stipulated delay:

Propagation Velocity, V= c/ $\sqrt{(\epsilon_r)}$ .

where c is the speed of light and the wavelength of the signal,  $\lambda = V / bandwidth$ .

For example, typical bandwidth for logic devices are at 300 MHz and the typical effective permittivity of a PCB  $\varepsilon_{r}$ , around 4.

Signal integrity issues may be observed with trace lengths >  $1/8^{th}$  of the signal's wavelength, ( $\lambda/8$ ).

Hence, V =  $3 \times 10^{8}$  (m/s)  $/\sqrt{4}$  =  $15 \times 10^{7}$  m/s

$\lambda = 15 \times 10^{7}$  (m/s) / 300×10<sup>6</sup> (Hz) = 0.5 m

And,  $\lambda/8 = 0.625$  m. For example, approximately 6 cm or approximately 2.5 inches.

### 3.2 Effects of External Resistors on One-Shots

As shown in Rise and Fall Time Estimates With or Without the One-Shots, additional resistors will impact the rise and fall times, and the overall data throughput. To further avoid divider networks, careful considerations should be taken while choosing external resistors as the devices are mostly designed with internal resistors placed by the I/O pins. If external pull-ups and pull-downs are used, their value as well as accurate timing and temperature coefficients should also be considered. For more information, see Effects of Pullup and Pulldown Resistors on TXS and TXB Devices application note.

### 3.3 Effects of Slow Inputs on the One-Shots

Careful considerations must be made to ensure I/Os have defined voltage levels, as slow inputs will impact the one-shot for false triggering. This can result in continuous signal oscillations for high and low. With the internal 10 k $\Omega$  pull-ups of the TXS0101/2/4E devices (TXS0108E has a 40 k $\Omega$  and 4 k $\Omega$  pull-up when driving low and high respectively), inputs can be left floating. For TXB devices with inactive drivers i.e with the internal 4 k $\Omega$  in high-impedance, all unused pins are recommended to be tied to GND with >= 100 k $\Omega$  pull-downs.

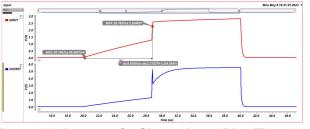

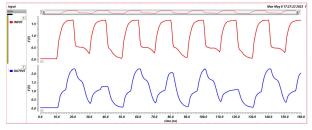

Slow inputs can also lead to false triggers as observed in Figure 3-1 and Figure 3-2, which can be amplified for signal oscillations.

Leveraging Edge Rate Accelerators with Auto-Sensing Level Shifters

Figure 3-1. Impact of a Slow Input Rise Time, 11 ns/V

Figure 3-2. Impact of a Slower Input Rise Time, 2.4 µS/V

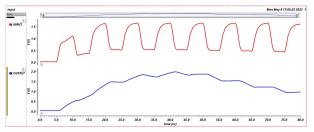

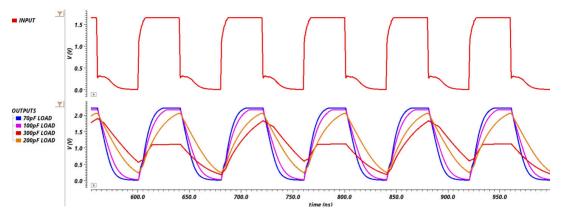

Figure 3-3 also show how additional loading can slow the rise and fall times. This slower rise and fall times from loading will have the potential to expire the one-shot's designed duration as observed in Figure 3-4, impacting overall signal integrity. See the data sheets for the recommended input transition rates. For more information, see the TXS and TXB level shifter families as shown in *Voltage Translators and Level Shifters*.

Figure 3-3. Impact of Loading on Rise and Fall Times

Figure 3-4. Impact of Loading on the O.S

#### 3.4 Effects of Speed and Loading on One-Shots

Figure 3-5. 15 pF Load Above the Max Data Rate

Figure 3-6. 100 pF Load Above the Max Data Rate

Figure 3-5 and Figure 3-6 show examples of the one-shot performing at varying loads with their impact. With faster data rates, the one-shot can time-out early. This will affect the signal not being pulled high enough for the desired output voltage levels.

Figure 3-7. 15 pF Load Below the Max Data Rate

Figure 3-8. 100 pF Load Below the Max Data Rate

Lower speeds are typically achievable with higher loads and vice-versa, as observed in Figure 3-7 and Figure 3-8. For optimal operation, lower loads should be considered for faster speed applications. Unless otherwise noted in the data sheets, >70pF at faster speeds above the recommendation will impact the one-shot designed duration which can cause false triggers for system failure.

Figure 3-9. Lumped Capacitance Impact at Max Data Rate

The one-shot works closely with RC, which significantly impacts the speed performance of the devices as the data rate is dependent on the RC circuitry. While strong pull-ups are not recommended for the TXB and TXS devices, careful considerations for lumped capacitive loading should be ensured per the data rate requirements, similar to the TXS or TXB data sheet recommendation. As shown, the one-shot can trigger for unwanted outputs and overall system failures. In addition to the loading, long traces and connectors will also add parasitic capacitance to the overall lumped capacitance.

### 3.5 Effects of Temperature on One-Shots

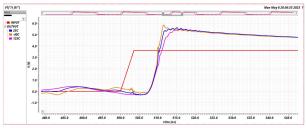

Poor design for temperature can lead to mismatched output impedance as depicted in Figure 3-10 showing how the impedance varies with temperature. We can see how the output impedance increases with temperatures. Careful consideration should be made for impedance matching to avoid amplifying the reflections. Such impedance mismatch will result in reflections which can be further amplified by the one-shot as oscillations to yield system failures similar to the Figure 3-11.

Figure 3-10. Reflections at Cold, Room and Hot Temp

Figure 3-11. Amplified One-shot Reflections

When the output impedance of the device decreases for faster data rates while the one-shot is activated, we see how key the overall output impedance is. Impedance mismatch can cause a voltage difference between the capacitance and the one-shot. If the one-shot is at an unwanted voltage, the one-shot can release the capacitance prior to being fully discharged, yielding to an expired one-shot for shorter pulse widths. Unless otherwise stated in the data sheets, note that the typical one-shot duration is designed for about 10 ns to 30 ns. Temperature and loading can significantly impact the output impedance and the one-shot duration as shown in Figure 3-12 and Figure 3-13.

Figure 3-12. Typical Temperature Impact on Ron Figu

Figure 3-13. Typical Temperature Impact on Pulse Width Duration For the One-Shot

Designing for impedance matching to avoid reflections should be considered as lower temperatures yield lower impedance and higher temperatures yield higher impedance. The application's voltage levels are also key as lower voltage nodes have the highest output impedance and higher voltage nodes have the lowest output impedance respectively, as observed with the R<sub>on</sub>. See the device's data sheet to ensure the system is designed to accommodate the overall output impedance of the device per the system's environment similar to the PCB layout design considerations.

### 4 Summary

The TXS and TXB level shifter families as shown in *Voltage Translators and Level Shifters* are designed with one-shots for a set duration of pulse width for optimal signal integrity, impacted by RC components. Therefore, intentional and careful considerations should be made when used with additional external components as majority of one-shot concerns are due to improper use of the devices, false triggering of the one-shots and poor layout design.

- 1. Consider short enough traces for round-trip delay reflections within the one-shot duration of 10-30 ns.

- Consider any tolerances of any additional RC components, similar to the data sheet recommendations. Consider using fast enough input edges per the input transition rate while avoiding floating inputs as stated in the data sheets.

- 3. Unless otherwise noted in the data sheets, makes sure <70 pF lumped capacitance designed for performance per the data sheet's recommended data rates.

- 4. Avoid timing-out the one-shot duration with additional parasitic capacitance as trace length and connectors yields additional capacitive loading.

- One-shot triggers when they detect rising or falling edges. Reflections and or ringing can cause false triggers. Ringing is also caused by capacitance and inductance of long cables and or traces and can also be amplified by unstable GND or V<sub>CC</sub> voltages.

- 6. Consider the impact on temperature per the output impedance, as mismatched impedance with PCB traces yield reflections that can be amplified by the one-shot as false edge triggers.

### **5** References

- 1. Texas Instruments, *Designing With the SN74LVC1G123 Monostable Multivibrator*, application note.

- 2. Texas Instruments, A Guide to Voltage Translation With TXS-Type Translators, application note.

- 3. Texas Instruments, A Guide to Voltage Translation With TXB-Type Translators, application note.

- 4. Texas Instruments, *Effects of Pullup and Pulldown Resistors on TXS and TXB Devices*, application note.

- 5. Texas Instruments, Implications of Slow or Floating CMOS Inputs, application note.

- 6. Texas Instruments, *Do's and Don'ts For TXS and TXB Voltage Level Shifters with Edge Rate Accelerators,* application note.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated