Texas Instruments Robotics System Learning Kit

# **Module 18**

Lecture: Serial Communication - UART

### **Serial Communication**

#### You will learn in this module

- Communication

- Encode

- Transmit

- Decode

- Serial: Universal Asynchronous Receiver Transmitter

- Interrupts

- Baud rate

- Performance measures

- Bandwidth

- Response time

### **Universal Asynchronous Receiver/Transmitter (UART)**

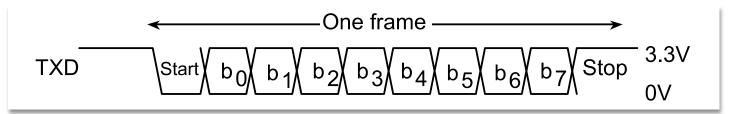

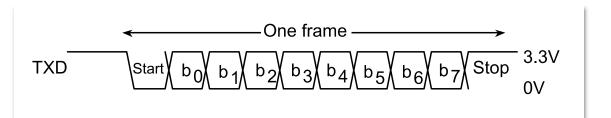

- Send/receive a frame

- 1 start (low), 5-8 data bits, 1 stop (high)

- Serial fashion, one bit every bit-time

- No clock is sent, asynchronous, timing derived from data

- Baud rate is total number of bits per unit time

- Baud rate = 1 / bit-time

- Both transmitter and receiver agree and know the baud rate

- Bandwidth is data or information per unit time

- Bandwidth = (data-bits / frame-bits) \* baud rate

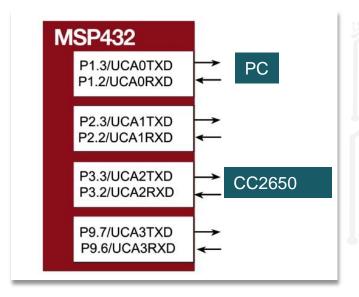

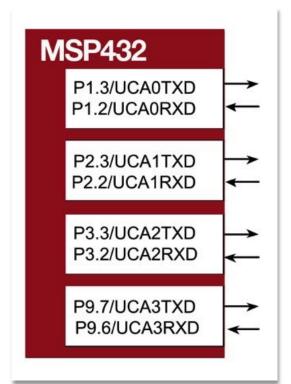

# **UART Port Selection**

| Pin  | PxSEL1=0, PxSEL0=1 |

|------|--------------------|

| P1.2 | UCA0RXD            |

| P1.3 | UCA0TXD            |

| P2.2 | UCA1RXD            |

| P2.3 | UCA1TXD            |

| P3.2 | UCA2RXD            |

| P3.3 | UCA2TXD            |

| P9.6 | UCA3RXD            |

| P9.7 | UCA3TXD            |

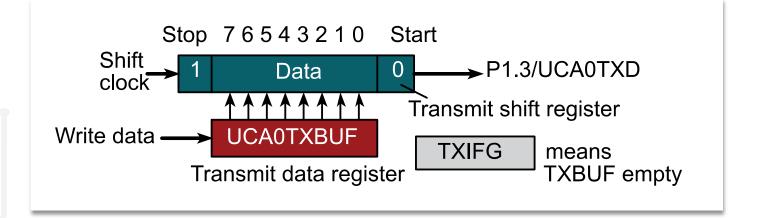

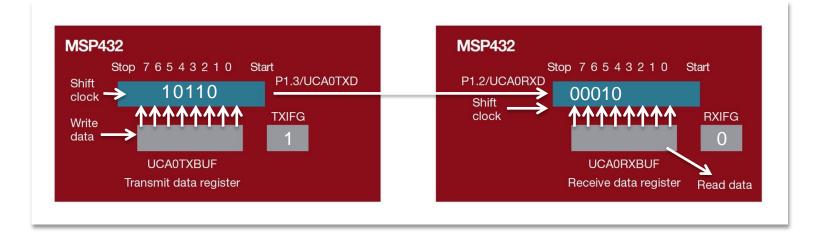

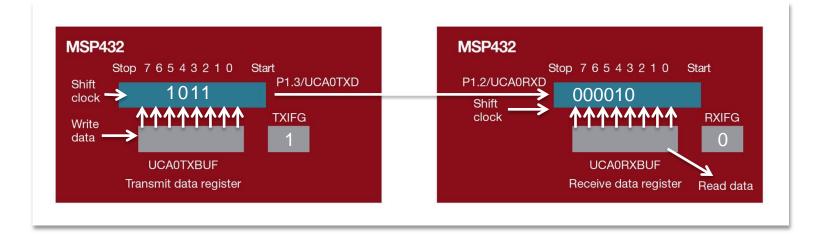

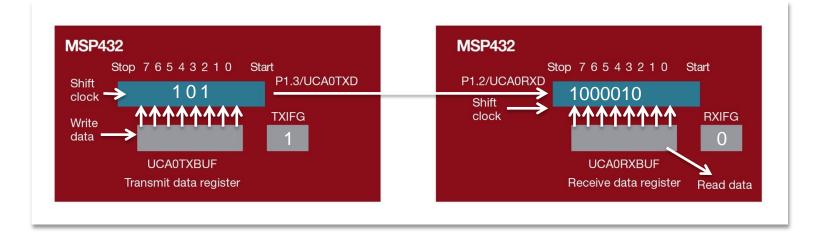

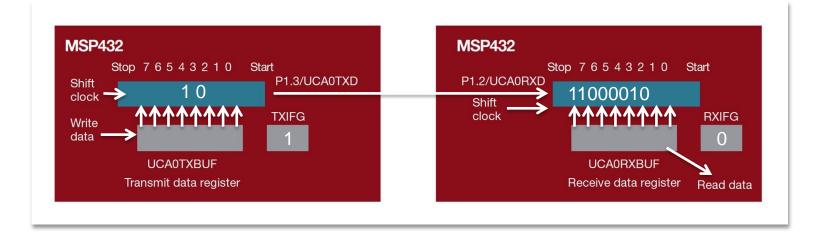

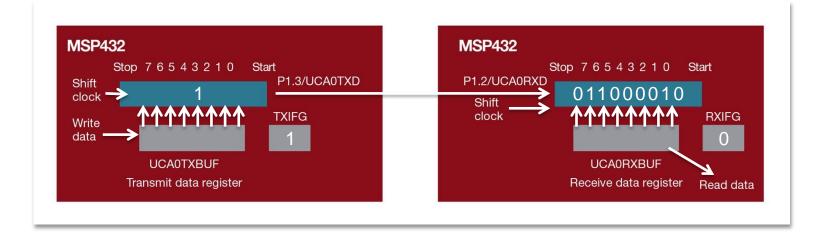

# **UART - Transmitter**

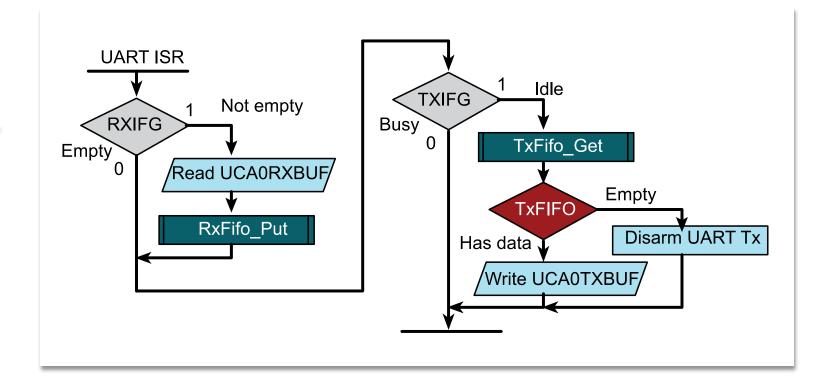

- Interrupt on TXIFG

- Data written to UCA0TXBUF

- Add start, stop bits

- Shift out at Baud Rate clock

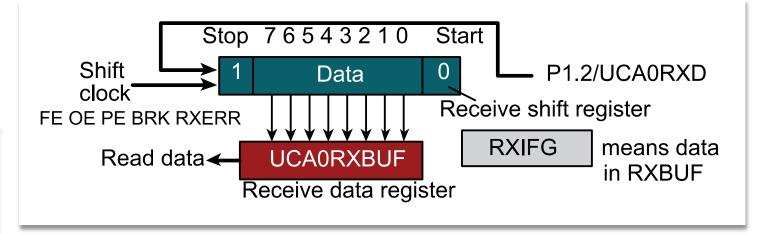

# **UART - Receiver**

- Start bit synchronization, shift in at baud rate

- Interrupt on RXIFG

- Read data from UCA0RXBUF

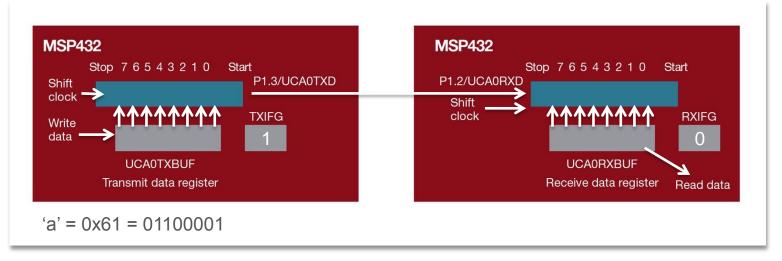

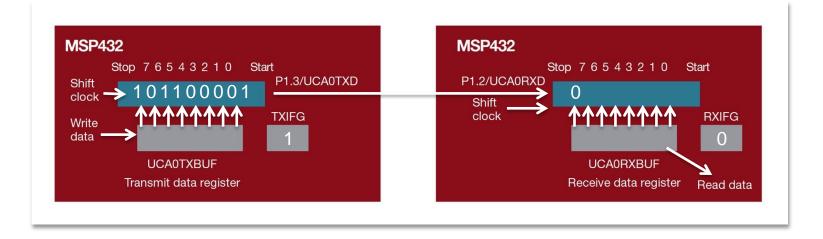

TXIFG in transmitter is 1

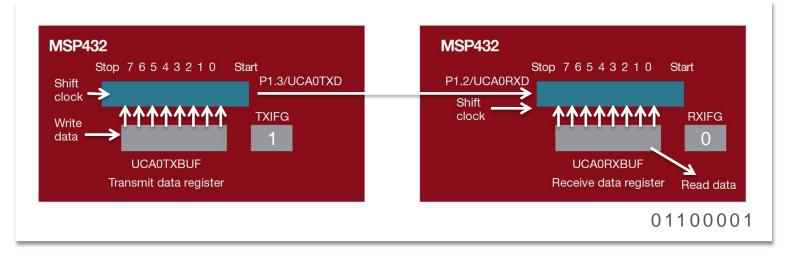

- Transmitter writes to UCA0TXBUF ('a' = 0x61 = 01100001)

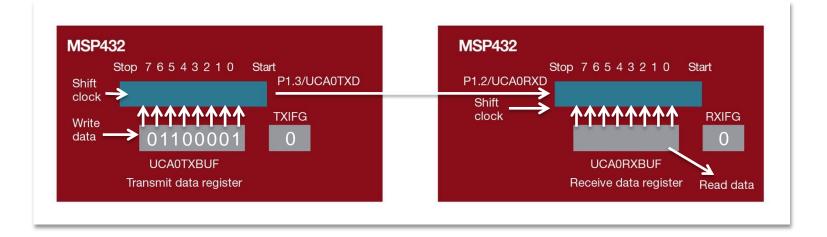

- TXIFG in transmitter becomes 0

- Data is moved from TXBUF to shift register

- Start bit and stop bit added

- TXIFG in transmitter becomes 1

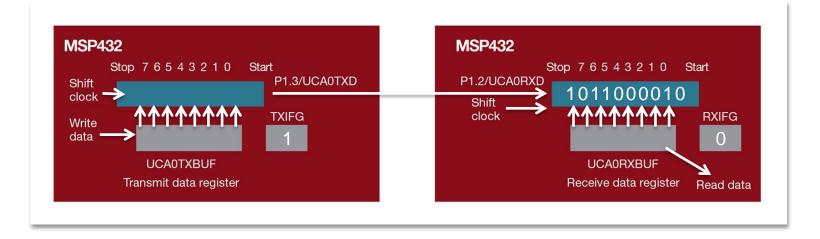

Start bit shifted

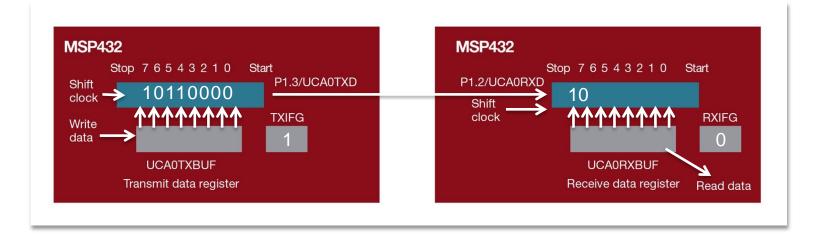

Data bit 0 shifted

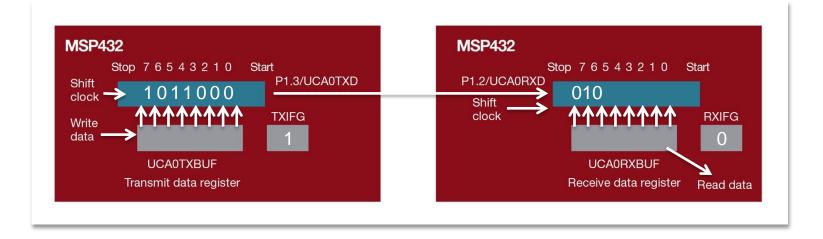

Data bit 1 shifted

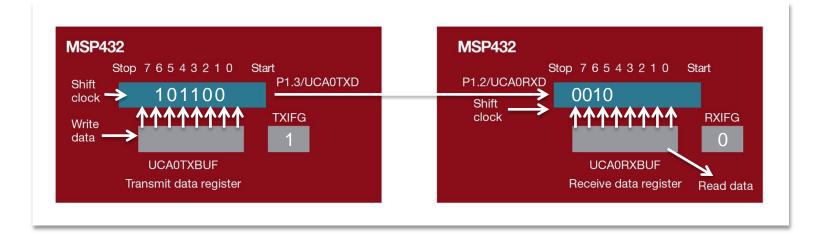

Data bit 2 shifted

Data bit 3 shifted

Data bit 4 shifted

Data bit 5 shifted

Data bit 6 shifted

Data bit 7 shifted

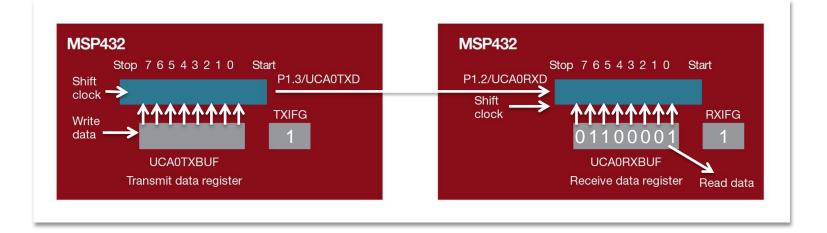

Stop bit shifted

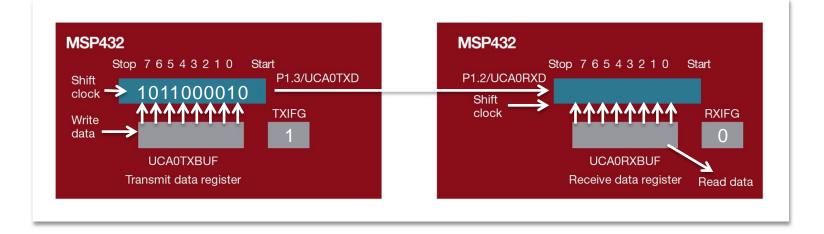

- Start bit and stop bit checked

- Data is moved from shift register to RXBUF

- RXIFG in receiver becomes 1

- Receiver reads from UCA0RXBUF ('a' = 0x61 = 01100001)

- RXIFG in transmitter becomes 0

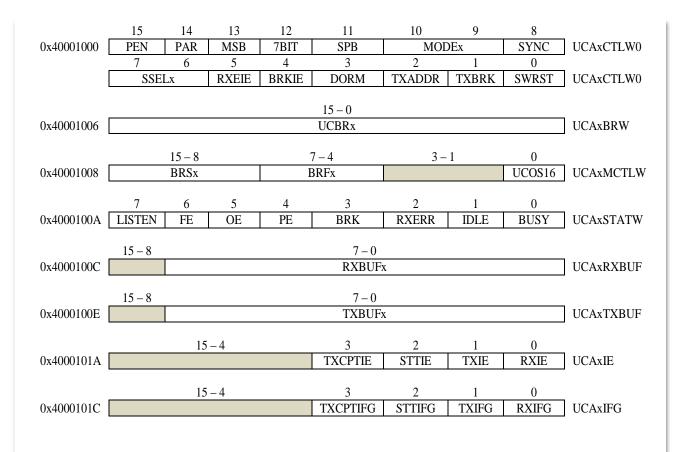

# **UART Registers**

# FIFO Usage

#### **Serial Communication**

- One bit at a time

- Asynchronous

- Interrupt-driven

- Baud rate

- Bandwidth

# **Module 18**

Lecture: Serial Communication - FIFO

# **Serial Communication**

#### You will learn in this module

- FIFO Queues

- Buffered I/O

- Little's Theorem

- Performance measures

- Bandwidth

- Response time

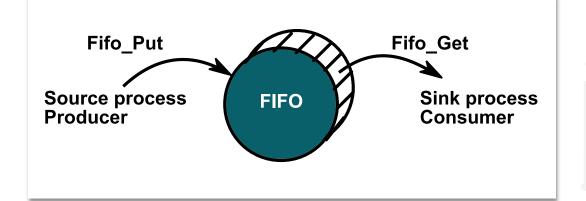

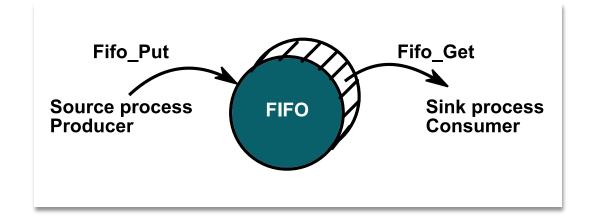

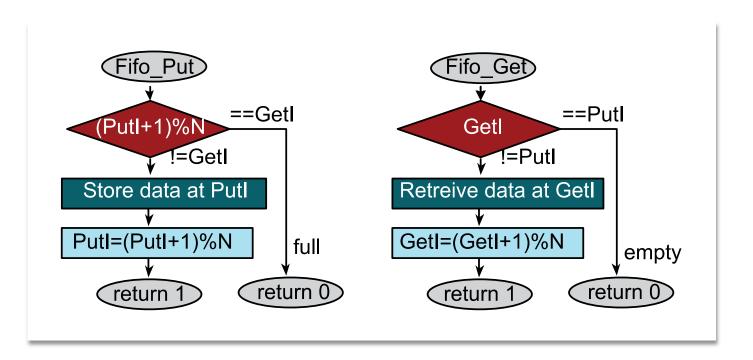

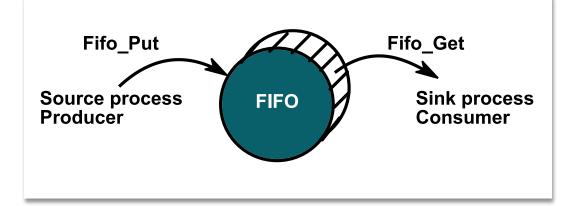

# First In First Out (FIFO) Queue

- Order preserving

- Producer puts on tail end

- Consumer gets from head end

- Buffer decouples producer & consumer

- Even out temporary mismatch in rates

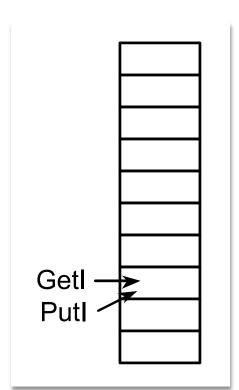

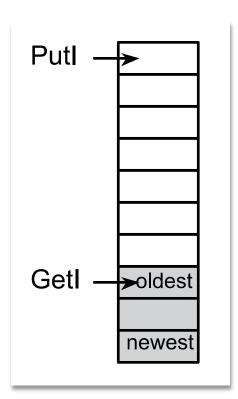

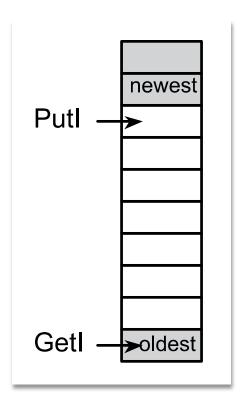

# **Empty FIFO**

- GetI points to oldest

- Putl points to empty place

- This FIFO has 10 spaces

- It can hold up to 9 data

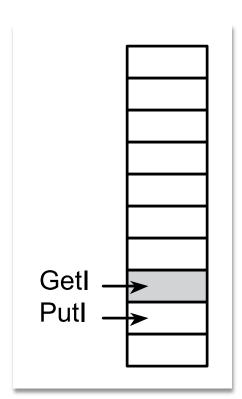

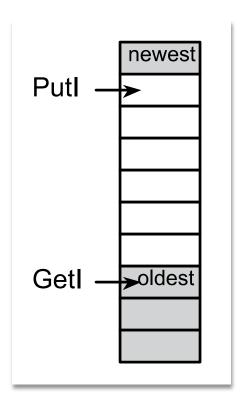

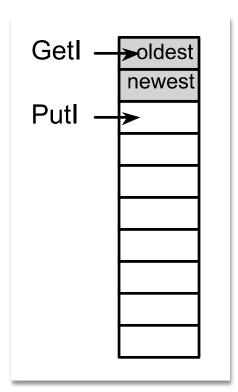

# **First Put**

- Store at Putl

- Increment Putl

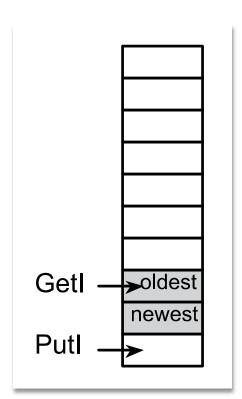

# **Second Put**

- Store at Putl

- Increment Putl

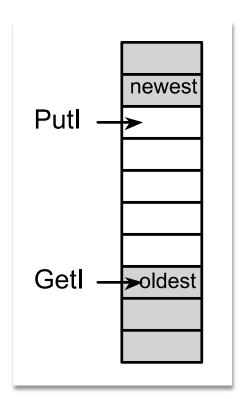

# **Third Put**

- Store at Putl

- Increment PutI (wrap)

# **Fourth Put**

- Store at Putl

- Increment Putl

- Store at Putl

- Increment Putl

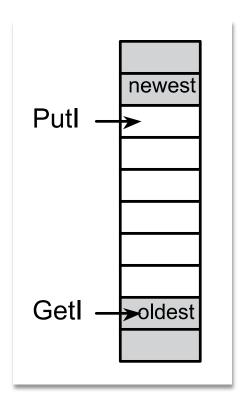

# **First Get**

- Read from GetI

- Increment Getl

# **Second Get**

- Read from Getl

- Increment Getl

# **Third Get**

- Read from Getl

- Increment GetI (wrap)

# **Fourth Get**

- Read from GetI

- Increment Getl

# ЛШ

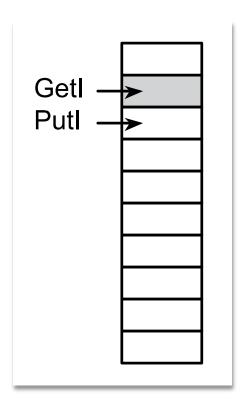

# **Fifth Get**

- GetI points to data to get

- Putl points to place to put

# **FIFO Implementation**

- GetI points to data to get

- Putl points to place to put

# ЛШ

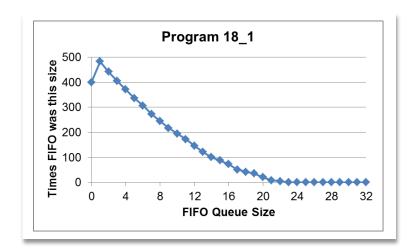

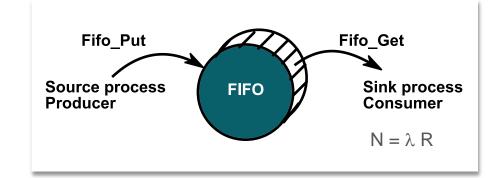

### Little's Theorem

- N be the average number of data packets in the queue (plus 1)

- Let  $\lambda$  be the average arrival rate in packets per second (pps)

- Let R be the average response time of a packet

- time waiting in the queue plus the

- time for the consumer to process the packet

- Little's Theorem  $N = \lambda R$

# **Summary**

#### FIFO queue

- Data flow

- Order preserving

- Full error on put

- Empty error on get

- Little's Theorem

# ti.com/rslk

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated