# LM331

AN-673 2-Way Multiplexed LCD Drive and Low Cost A/D-Converter Using V/F

Techniques with COP8 Microcontrollers

Literature Number: SNOA150

## 2-Way Multiplexed LCD Drive and Low Cost A/D Converter Using V/F Techniques with COP8 Microcontrollers

#### ABSTRACT

This application note is intended to show a general solution for implementing a low cost A/D and a 2-way multiplexed LCD drive using National Semiconductor's COP840C 8-bit microcontroller. The implementation is demonstrated by means of a digital personal scale. Details and function of the weight sensor itself are not covered in this note. Also the algorithms used to calculate the weight from the measured frequency are not included, as they are too specific and depend on the kind of sensor used.

## **Typical Applications**

- Weighing scales

- Sensors with voltage output

- Capacitive or resistive sensors

- All kinds of measuring equipment

- Automotive test and control systems

#### Features

- 2-way multiplexed LCD drive capability up to 30 segments (4 digit and 2 dot points)

- Precision frequency measurement

- Low current consumption

- Current saving HALT mode

- Additional computing power for application specific tasks

#### National Semiconductor Application Note 673 Volker Soffel April 1990

Itiplexed LCD Drive and Techniques with COP8

Microcontrollers

Low Cost A/D Converter

#### INTRODUCTION

Today's most popular digital scales all have the following characteristics:

They are battery powered and use a LCD to display the weight. Instead of using a discrete A/D-converter, in many cases a V/F converter is used, which converts an output voltage change of the weight sensor to a frequency change. This frequency is measured by a microcontroller and is used to calculate the weight. The advantages of a V/F over an A/D converter are multifold. Only one line from the V/F to the microcontroller is needed, whereas a parallel A/D needs at least 8 lines or even more (National also offers A/Ds with serial output). A V/F can be constructed very simply using National Semiconductor's low cost, precision voltage to frequency converters LM331 or LM331A. Other possibilities are using Op-amps or a 555-timer in astable mode.

## V/F-CONVERSION

## Hardware

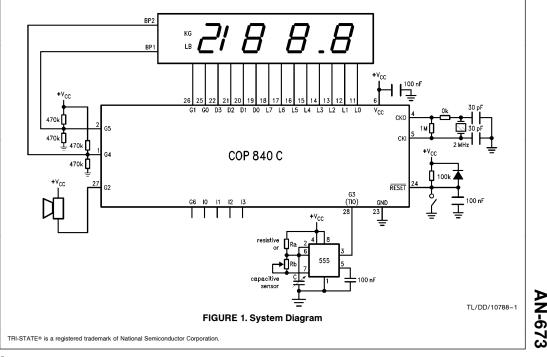

The basic configuration of the scale described in this application note is shown in *Figure 1*.

© 1995 National Semiconductor Corporation TL/DD10788

RRD-B30M75/Printed in U. S. A.

A capacitive or resistive sensor's weight related capacitance or resistance change is transformed by a 555 timer (in astable mode) to a change of frequency. The output frequency f is determined by the formula:

The output high time is given by:

t1 = 0.693\* (Ra + Rb) \*C

The output low time is given by:  $t2\,=\,0.693^*\,\textrm{Rb}^*\,\textrm{C}$

This frequency is measured using the COP800 16-bit timer in the "input capture" mode. After calculation, the weight is displayed on a 2-way multiplexed LCD. Using this configuration a complete scale can be built using only two ICs and a few external passive components.

For more information on V/F converters generally used with voltage output sensors, refer to the literature listed in the reference section.

#### **Frequency Measurement**

The COP 16-bit timer is ideally suited for precise frequency measurements with minimum software overhead. This timer has three programmable operating modes, of which the "input capture" mode is used for the frequency measurement. Allocated with the timer is a 16-bit "autoload/capture register". The G3-I/O-pin serves as the timer capture input (TIO). In the "input capture" mode the timer is decremented with the instruction cycle frequency (tc). Each positive going edge at TIO (also neg. edge programmable) causes the timer value to be copied automatically to the autoload/capture register without stopping the timer or destroying its

contents. The "timer pending" flag (TPND) in the PSW-register is set to indicate a capture has occurred, and if the timer-interrupt is enabled, an interrupt is generated. The frequency measurement routine listed below executes the following operations (refer to the RAM/register definition file listed at the beginning for symbolic names used in the routines):

The timer is preset with FFFF Hex and is started by setting the TRUN bit, after which the software checks the TPND-flag in a loop (timer interrupt is disabled). When the TPND flag is set the first time, the contents of the capture register is saved in RAM locations STALO and STAHI (start value). The TPND pending flag now must be reset by the software. Then, another 255 positive going edges are counted (equal to 255 pulses) before the capture register is saved in RAM locations ENDLO, ENDHI (end value). The shortest time period that can be measured depends on the number of instruction cycles needed to save the capture register, because with the next positive going edge on TIO the contents of the capture register is overwritten (worst case is 18 instruction cycles, which equals a max. frequency of 55.5 kHz at tc = 1  $\mu$ s).

The end-value is subtracted from the start-value and the result is restored in RAM locations STALO, STAHI. This value can then be used to calculate the time period of the frequency applied to TIO (G3) by multiplying it with the tc-time and dividing the result by the number of pulses measured (N = 255).

T = (startvalue - endvalue) \*tc/N

;THE FOLLOWING "INCLUDE FILE" IS USED ;AS PART OF THE DEFINITION- AND INITIALIZATION PHASE ; IN COP800 PROGRAMS. ;REGISTER NAMES, CONTROL BITS ETC ARE NAMED IN THE ; SAME WAY IN THE COP800 DATA-SHEETS. --- COP800 MEMORY MAPPED ---; ; \* PORT -, CONFIGURATION - AND CONTROL REGISTERS \* ; ; ; L-PORT DATA REGISTER PORTLD 0D0 = PORTLC 0D1 ; L-PORT CONFIGURATION TL/DD/10788-2

2

PORTLP 0D2 ; L-PORT INPUT REGISTER = PORTGD 0D4 ; G-PORT DATA REGISTER = PORTGC = 0D5 ; G-PORT CONFIGURATION ; G-PORT INPUT REGISTER 0D6 PORTGP = 0DC PORTD = ; D-PORT (OUTPUT) PORTI = 0D7 ; I-PORT (INPUT) SIOR 0E9 ; MWIRE SHIFT REGISTER = ; TIMER LOW-BYTE TMRLO = 0EA ; TIMER HIGH-BYTE ; T.-AUTO REG.LOW BYTE ; T.-AUTO REG.HIGH BYTE TMRHI = 0EB TAULO = 0EC TAUHI = 0ED 0ee CNTRL == ; CONTROL REGISTER PSW 0EF ; PSW-REGISTER = .FORM ; \* CONSTANT DECLARE \* ; ; --- CONTROL REGISTER BITS ---; S0 00 ; MICROWIRE CLOCK DIVIDE BY = --- BIT 0 ---; S1 01 MICROWIRE CLOCK DIVIDE BY = ; --- BIT 1 ---; ; EXTERNAL INTERRUPT EDGE 02 IEDG = ; POLARITY SELECT (0=RISING ; EDGE, 1=FALLING EDGE) ; ENABLE MICROWIRE FUNCTION MSEL 03 = --- SO AND SK ---; ; START/STOP THE TIM/COUNT. TRUN 04 = (1=RUN; 0=STOP); ; TIMER INPUT EDGE POL.SEL. TEDG 05 = ; (0=RIS. EDGE;1=FAL. EDGE) ; SELECTS THE CAPTURE MODE CSEL = 06 ; SELECTS THE TIMER MODE TSEL = 07 --- P S W REGISTER ---; GIE = 00 ; GLOBAL INTERRUPT ENABLE TL/DD/10788-3

01 ENT ; EXTERNAL INTERRUPT ENABLE = ; MICROWIRE BUSY SHIFTING BUSY = 02 IPND = 03 ; EXTERNAL INTERR. PENDING ENTI ; TIMER INTERRUPT ENABLE = 04 TPND = 05 ; TIMER INTERRUPT PENDING = ; CARRY FLAG C 06 ; HALF CARRY FLAG НC = 07 ;\*\*\*\* RAM-DEFINITIONS \*\*\*\*\* BCDLO = 000 ; CALCULATED WEIGHT IN BCD ;LOW BYTE BCDHI = 001 ;CALCULATED WEIGHT IN BCD ;HIGH BYTE MWBUF0 = 003 ;7SEGMENT DATA FOR LCD DISPL ;L-PORT = 004 MWBUF1 ;D-PORT = 005 ;G-PORT MWBUF2 = 006 ; OFFSET REGISTERS FOR = 007 ;7 SEGMENT CODE TABLE OFF1 OFF2 OFF3 = 008 ; = 009 ;START VALUE,LOW BYTE = 00A ;START VALUE,HIGH BYTE STALO STAHI ENDLO = 00B ;END VALUE LOW BYTE ENDHI = 00C ;END VALUE HIGH BYTE DIV0 = 00D ;DIVISOR FOR DINBI248 ROUTINE ;022.. 02F RESERVED FOR STACK WITH COP820 ;062..06F RESERVED FOR STACK WITH COP840 ;\*\*\*\* REGISTER DEFINITIONS \* \* \* \*  $\begin{array}{rcl} \text{COUNT} &=& 0 \text{F0} \\ \text{COUNT2} &=& 0 \text{F1} \end{array}$ COUNT3 = 0F2FLAG = 0FF;FLAG REGISTER ;\*\*\*\* BIT DEFINITIONS FLAG REGISTER \*\*\*\* POUND = 04; POUND=1: DISPLAY POUND SEGMENT ;POUND=0:DISPLAY kg SEGMENT ;\*\*\*\*\* G-PORT BIT DEFINITIONS \*\*\*\*\* BP1 = 05 ;BACKPLANE 1 TL/DD/10788-4

4

| ;TIME O        | F 255 PU                                | JLSES, USING                                                                                | TIMER INPUT CAPTURE MODE                                                                                                                                                                                                                                                                                    |               |

|----------------|-----------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| FMEAS:         | LD<br>LD<br>LD<br>LD                    | COUNT, #000<br>X, #TAULO<br>B, #TMRLO<br>[B+], #0FF<br>[B], #0FF<br>B, #CNTRL<br>[B+], #0D0 | <pre>;PERIOD TIME=<br/>;(START-ENDVALUE)*tc/255<br/>;DIFFERENCE START-ENDVALUE<br/>;IS STORED IN ENDLO,ENDHI<br/>;LOAD PULSE COUNTER (255 PULSES)<br/>;POINT TO AUTO REG. LOW B.<br/>;PRESET TIMER<br/>;REG. WITH FFFFh<br/>;CNTRL-REG.: TIMER CAPTURE<br/>;MODE,TIO POS. TRIGGERED,<br/>;START TIMER</pre> |               |

| L1:            | RBIT<br>IFBIT<br>JP                     | #TPND, [B]<br>#TPND, [B]<br>SSTORE                                                          | ;RESET TIMER PENDING FLAG                                                                                                                                                                                                                                                                                   |               |

| SSTORE:        | JP                                      | L1                                                                                          | ;STORE START VALUE                                                                                                                                                                                                                                                                                          |               |

|                | RBIT<br>LD                              | #TPND, [B]<br>A, [X+]                                                                       | ; LOAD TIMER CAPTURE REG.                                                                                                                                                                                                                                                                                   |               |

|                | X<br>LD                                 | A,STALO<br>A,[X-]                                                                           | ;LOW BYTE<br>;STORE IN RAM<br>;LOAD HIGH BYTE CAPTURE,<br>;POINT TO LOW BYTE CAPTURE                                                                                                                                                                                                                        |               |

|                | X<br>LD                                 | A,STAHI<br>B,#PSW                                                                           | STORE IN RAM                                                                                                                                                                                                                                                                                                |               |

| L256:<br>DCOU: | IFBIT<br>JP<br>JP<br>RBIT<br>DRSZ<br>JP | #TPND, [B]<br>DCOU<br>L256<br>#TPND, [B]<br>COUNT<br>L256                                   | ;RESET TIMER PENDING FLAG<br>;DECREMENT PULSE COUNTER<br>;COUNTER = 0 ?<br>;NO,LOOP 'TIL 255 PULSES<br>;HAVE BEEN MEASURED                                                                                                                                                                                  |               |

| ESTORE:        |                                         |                                                                                             | ;STORE END VALUE                                                                                                                                                                                                                                                                                            |               |

|                | LD<br>LD<br>LD<br>X                     | CNTRL,#00<br>B,#STALO<br>A,[X+]<br>A,[B]                                                    | ;STOP TIMER<br>;POINT TO START VALUE LOW BYTE<br>;LOAD END VALUE LOW BYTE<br>;LOAD ACCU WITH STARTVALUE LOW BYTE<br>;& STALO WITH END VALUE LOW BYTE                                                                                                                                                        | TL/DD/10788-5 |

|                | SC<br>SUBC                              | A,[B]                                                                                       | ;SUBTRACT ENDVALUE LOW BYTE                                                                                                                                                                                                                                                                                 |               |

|                | Х                                       | A,[B+]                                                                                      | ;FROM STARTVALUE LOW BYTE<br>;STORE RESULT IN STALO,                                                                                                                                                                                                                                                        |               |

|                | LD<br>X                                 | A,[X]<br>A,[B]                                                                              | ; POINT TO STAHI<br>;LOAD ACCU WITH ENDVALUE HIGH BYTE<br>;LOAD ACCU WITH STARTVALUE HIGH BYTE<br>;& STAHI WITH ENDVALUE HIGH BYTE                                                                                                                                                                          |               |

|                | SUBC                                    | A, [B]                                                                                      | ;SUBTRACT ENDVALUE HIGH BYTE FROM<br>;STARTVALUE HIGH BYTE                                                                                                                                                                                                                                                  |               |

|                | X<br>RET<br>.END                        | A,[B]                                                                                       | ;STORE RESULT IN STAHL                                                                                                                                                                                                                                                                                      | TL/DD/10788-6 |

## 2-WAY MULTIPLEXED LCD DRIVE

Today a wide variety of LCDs, ranging from static to multiplex rates of 1:64 are available on the market. The multiplex rate of a LCD can be determined by the number of its backplanes (segment-common plate). The higher the multiplex rate the more individual segments can be controlled using only one line. e.g. a static LCD only has one backplane; only one segment can be controlled with one line. A two-way multiplexed LCD has two backplanes and two segments can be controlled with one line, etc.

Common to all LCDs is the fact that the drive voltage applied to the backplane(s) and segments has to be alternating. DC-components higher than 100 mV can cause electrochemical reactions (refer to manufacturer's spec), which reduce reliability and lifetime of the display.

If the multiplex ratio of the LCD is N and the amount of available outputs is M, the number of segments that can be driven is:

#### S = (M - N) \* N

So the maximum number of a 2-way mux LCD's segments that can be driven with a COP800 in 28-pin package (if all outputs can be used to drive the LCD) is:

#### S = (18 - 2) \* 2 = 32

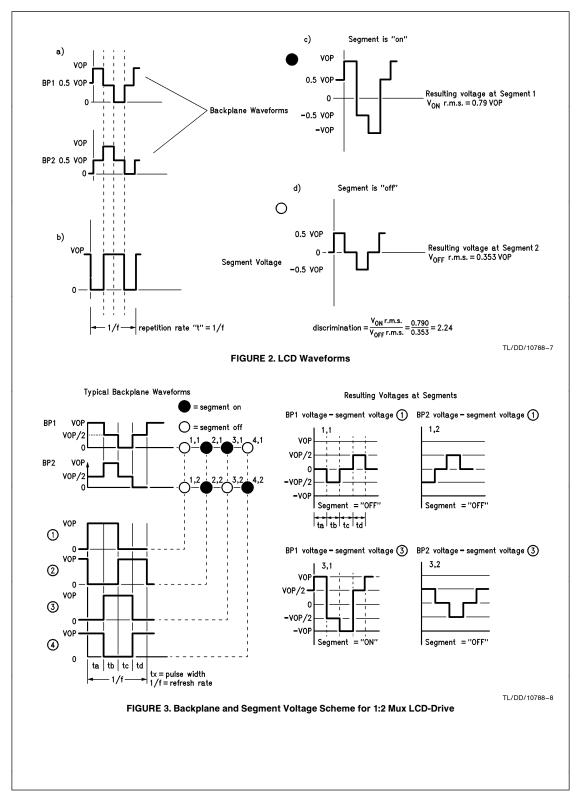

During one LCD refresh cycle tx (typical values for 1/tx = fx are in the range 30 Hz ... 60 Hz), three different voltages levels: Vop, 0.5\*Vop and 0V have to be generated. The "off" voltage across a segment is not 0V as with static LCDs and also the "on" voltage is not Vop, but only a fraction of it. The ratio of "on" to "off" r.m.s.-voltage (discrimination) is determined by the multiplex ratio and the number of voltage levels involved. The most desirable discrimination ratio is one that maximizes the ratio of V<sub>ON</sub> to V<sub>OFF</sub>, allowing the maximum voltage difference between activated and non-activated states. In general the maximum achievable ratio for any particular value of N is given by:

$(V_{ON}/V_{OFF})$  max = SQR ((SQR(N) + 1)/(SQR(N) - 1))

#### SQR = square root

Using this formula the maximum achievable discrimination ratio for a 2-way multiplex LCD is 2.41, however, it is also possible to order a customized display with a smaller ratio. For ease of operation, most LCD drivers use equal voltage steps (0V, 0.5 \*Vop, Vop). Thus a discrimination ratio of 2.24 is achieved. When using the COP800 to drive a 2-way multiplexed LCD the only external hardware required to achieve the three voltage steps are 4 equal resistors that form two voltage dividers—one for each backplane

(Figure 1). The procedure is to set G4 and G5 to "0" for 0V, to HI-Z (TRI-STATE®) for 0.5\*Vop and to "1" in order to establish Vop at the backplane electrodes.

With the COP800 each I/O pin can be set individually to TRI-STATE, "1" or "0", so this procedure can be implemented very easily.

The current consumption of typical LCDs is in the range of 3  $\mu$ A to 4  $\mu$ A (at Vop = 4.5V, refresh rate 60 Hz) per square centimeter of activated area. Thus the backplane and segment terminals can be treated as Hi-Z loads. At high refresh rates the LCD's current consumption increases dramatically, which is the reason why many LCD manufacturers recommend not using a refresh frequency higher than 60 Hz. **Timing Considerations**

#### Timing Considerations

As shown in *Figures 2* and *3*, one LCD refresh cycle tx is subdivided into four equally distant time sections ta, tb, tc and td during which the backplane and segment terminals have to be updated in order to switch a specific segment on or off. Considering a refresh frequency of 50 Hz (tx = 20 ms) ta, tb, tc and td are equal to 5 ms; a COP800 running from an external clock of 2 MHz has an internal instruction cycle time of 5  $\mu$ s and a typical current consumption of less than 350  $\mu$ A (at V<sub>CC</sub> = 3V and room temperature), thus meeting both the requirements of low current consumption and additional computing power between LCD refreshes.

The timing is done using the COP800's 16-bit timer in the PWM autoload mode. The timer and the assigned 16-bit autoload register are preset with proper values. By setting the TRUN-flag in the CNTRL-register the timer is decremented each instruction cycle. A flag (TPND) is set at underflow and the timer is automatically reloaded with the value stored in the autoload-register. Timer underflow can also be programmed to generate an interrupt.

#### Segment Control

Figure 2 shows the voltage-waveforms applied to the two backplane-electrodes (a) and the waveform at a segementelectrode (b), which is needed to switch segment A on and segment B off. The resulting voltage over the segments (c and d) is achieved by subtracting waveform (b) from BP1 (segment A) and waveform (b) from BP2 (segment B).

*Figure 3* shows the four different waveforms which must be generated to meet all possible combinations of two segments connected to the same driving terminal (off-off, on-off, off-on, on-on).

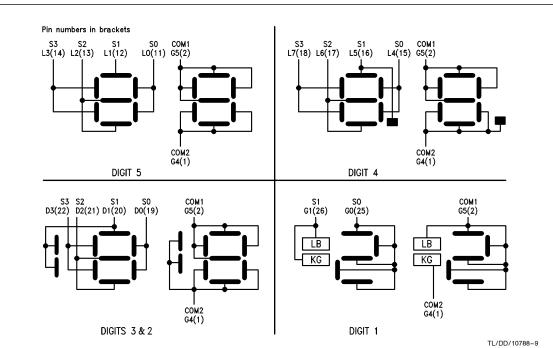

Figure 4 shows the internal segment and backplane connections for a typical 2-way mux LCD.

FIGURE 4. Customized LCD Display (Backplane and Segment Organization)

#### LCD Drive Subroutine

The LCD drive subroutine DISPL converts a 16-bit binary value to a 24-bit BCD-value for easier display data fetch. The drive subroutine itself is built up of a main routine doing the backplane refresh and 7 subroutines (SEG0, SEG1, SEG2, SEG3, SEGOUT, TTPND, DISPD). The subroutines SEG0 to SEG4 are used to get the LCD segment data from a look-up table in ROM for time phases ta, tb, tc and td respectively. Subroutine SEGOUT writes the segment data for each time phase to the corresponding output ports. One time phase takes 5 ms, giving a total refresh cycle time of 20 ms (50 Hz). The exact timing is done by using the COP800 16-bit timer in the PWM autoload mode. In that mode the timer is reloaded with the value stored in the autoload register on every timer underflow. At the same time the timer pending flag is set. The subroutine TTPND checks this flag in a loop. If the timer pending flag is set, this subroutine resets it and returns to the calling program. Thus a 5 ms time delay is created before the segment and backplane data for the next time phase is written to the output ports. Finally the subroutine DISPD switches off the LCD by setting the backplane and segment connections to "0". In this digital scale application a frequency measurement is made while the LCD is off. Then the weight is calculated from this frequency and is displayed for 10s. After this 10s the LCD is switched off again and the COP800 is programmed to enter the current saving HALT mode (I<sub>DD</sub> < 10  $\mu$ A). A new weight cycle on the digital scale is initiated by pressing a push button, which causes a reset of the microcontroller.

#### CONCLUSIONS

National Semiconductor's COP800 Microcontroller family is ideally suited for use with V/F converters and 2-way multiplexed LCDs, as they offer features, which are essential for these types of applications. The high resolution, 3-mode programmable 16-bit timer allows precise frequency measurement in the input capture mode with minimum software overhead. The timer's PWM autoreload mode offers an easy way to implement a precise timebase for the LCD refresh. The COP800's programmable I/O ports provide flexibility in driving 2-way multiplexed LCDs directly. The COP800 family, fabricated using M2CMOS technology, offers both low voltage (min  $V_{\rm CC}$  of 2.5V) and low current drain.

#### REFERENCES

- 1. National Semiconductor, "Linear Databook 2, Rev. 1" LM331, LM331A datasheets pages 3-285 ff.

- National Semiconductor, "Linear Applications Databook, 1986", "Versatile monolithic V/Fs can compute as well as convert with high accuracy", pages 1213 ff.

- National Semiconductor, "Microcontrollers Databook, Rev. 1", COP820C/COP840C datasheets pages 2–7 ff.

- U. Tietze, Ch. Schenk, "Halbleiter-Schaltungstechnik" 8.Auflage 1986, Springer Verlag, ISBN 0-387-16720-X, "Funktionsgeneratoren mit steuerbarer Frequenz", pages 465 ff, "Multivibratoren", pages 183 ff.

- 5. Lucid Displays, "LCD design guide", English Electric Valve Company Ltd., Chelmsford, Essex, Great Britain.

| APPENDIX—Softwar                                                                                                                                                         | e Routines                                                                                                                                               |                    |                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|

| ;LOOKUP TABL                                                                                                                                                             | E FOR CUSTOMIZED                                                                                                                                         | 2-WAY MULIPLEX LCD |                |

| . = X'200<br>;TIMEPHASE T<br>.BYTE 004<br>.BYTE 008<br>.BYTE 008<br>.BYTE 008<br>.BYTE 002<br>.BYTE 001<br>.BYTE 001<br>.BYTE 001<br>.BYTE 000<br>.BYTE 000<br>.BYTE 000 | a 7 SEGMENT DATA<br>;"0" AND ".0"<br>;"1" AND ".1"<br>;"2" AND ".2"<br>;"3" AND ".3"<br>;"4" AND ".4"<br>;"5" AND ".5"<br>;"6" AND ".6"<br>;"7" AND ".7" |                    |                |

| ;SPECIAL SEG<br>.BYTE 001<br>.BYTE 000<br>.BYTE 003<br>.BYTE 002                                                                                                         | MENTS TIMPHASE Ta<br>;"LB"<br>;"LB 2"<br>;"KG"<br>;"KG 2"                                                                                                |                    |                |

| . = .+ 1                                                                                                                                                                 | b 7 SEGMENT DATA<br>;"0"<br>;"1"<br>;"2"<br>;"3"<br>;"4"                                                                                                 |                    | TL/DD/10788-10 |

|         | . BYTE<br>. BYTE | 002<br>00A<br>00F<br>000<br>001<br>008<br>00C<br>008<br>00C<br>008<br>000<br>00C<br>000<br>00C<br>000<br>008<br>00D | ; "8"<br>; "9"<br>; ".0"<br>; ".1"<br>; ".2"<br>; ".3"<br>; ".4"<br>; ".5"<br>; ".6"<br>; ".7"<br>; ".8"<br>; ".9"                                                                                      |                |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|         | .LOCAL                                                                                                                                             |                                                                                                                     |                                                                                                                                                                                                         |                |

| TTPND:  | LD                                                                                                                                                 | B,#PSW                                                                                                              |                                                                                                                                                                                                         |                |

| \$LOOP: | IFBIT<br>JP<br>JP                                                                                                                                  | #TPND,[H<br>\$END<br>\$LOOP                                                                                         | 3]                                                                                                                                                                                                      |                |

| \$END:  | RBIT<br>LD<br>RET<br>.LOCAL                                                                                                                        | #TPND,[E<br>B,#PORTC                                                                                                |                                                                                                                                                                                                         |                |

|         | . = .+1<br>;TIMEPH<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE                              | ASE TC 7<br>00B<br>001<br>007<br>00D<br>00E<br>00E<br>003<br>00F<br>00F<br>00F                                      | SEGMENT DATA<br>;"0" AND ".0"<br>;"1" AND ".1"<br>;"2" AND ".2"<br>;"3" AND ".3"<br>;"4" AND ".4"<br>;"5" AND ".5"<br>;"6" AND ".5"<br>;"6" AND ".6"<br>;"7" AND ".7"<br>;"8" AND ".8"<br>;"9" AND ".9" |                |

| COPY:   |                                                                                                                                                    |                                                                                                                     | ;COPY 2BYTES POINTED TO<br>;BY B AND B+1 TO RAM<br>;POINTED TO BY X AND X+1                                                                                                                             |                |

|         | LD<br>X<br>LD<br>X<br>RET<br>.LOCAL                                                                                                                | A, [B+]<br>A, [X+]<br>A, [B+]<br>A, [X+]                                                                            |                                                                                                                                                                                                         |                |

|         |                                                                                                                                                    |                                                                                                                     |                                                                                                                                                                                                         | TL/DD/10788-11 |

|         |                                                                                                                                                    |                                                                                                                     |                                                                                                                                                                                                         |                |

|         |                                                                                                                                                    |                                                                                                                     |                                                                                                                                                                                                         |                |

;TIMEPHASE Td 7 SEGMENT DATA ;"0" .BYTE 00D ;"1" 001 .BYTE ;"2" .BYTE 00C ;"3" .BYTE 005 ;"4" 001 .BYTE ;"5" .BYTE 005 ;"6" .BYTE 00D ;"7" .BYTE 001 ;"8" .BYTE 00D ;"9" 005 .BYTE ;" " .BYTE 000 ;".0" .BYTE 00F ;".1" .BYTE 003 ;".2" ;".3" .BYTE 00E .BYTE 007 ;".4" .BYTE 003 .BYTE 007 ;".5" ;".6" .BYTE 00F ;".7" 003 .BYTE ;".8" .BYTE 00F ;".9" 007 .BYTE .BYTE 002 ;". " ;SPECIAL SEGMENTS TIMEPHASE Tb .BYTE 003 ;"LB" .BYTE 003 ;"LB 2 " 001 001 ;"KG" ;"KG 2" .BYTE .BYTE ;"LB" ;"LB 2" ;"KG" ;"KC ;SPECIAL SEGMENTS TIMPHASE TC .BYTE 002 .BYTE 003 .BYTE 000 ;"KG 2" .BYTE 001 ;SPECIAL SEGMENTS TIMEPHASE Td ;"LB" ;"LB 2" .BYTE 000 000 .BYTE ; "KG" .BYTE 002 ;"KG 2" .BYTE 002 .END ;DISPL: ; INPUT PARAMETER: COUNT2 = RAM REGISTER, WHICH CONTAINS ; THE DISPLAY TIME IN SEC. ;EXAMPLE COUNT2= 1-> DISPLAY TIME IS 1SEC. ;LCD DRIVE ROUTINE FOR CUSTOMIZED 2 WAY MULTIPLEX ;LCD TL/DD/10788-12 ; ROUTINE CONVERTS BCD DATA STORED IN RAM LOCATIONS ;BCDLO, BCDHI INTO LCD OUTPUT DATA STORED AT ;MWBUF0 = LPORT DATA ;MWBUF1 = DPORT DATA ;MWBUF2 = G-PORT DATA (G0,G1 ONLY, OTHER BITS STAY UNCHANGED) ;SUBROUTINES INCLUDED: ;SEG0: GETS LCD SEGMENT DATA FOR TIMEPHASE TA ;SEG1: GETS LCD SEGMENT DATA FOR TIMEPHASE TB ;SEG2: GETS LCD SEGMENT DATA FOR TIMEPHASE TC ;SEG3: GETS LCD SEGMENT DATA FOR TIMEPHASE TD ; DISPD: SWITCHES THE DISPLAY OFF AND CONFIGURES G-, L- AND D-PORTS ;TTPND: CHECKS TIMER PENDING FLAG (REFRESH RATE GENERATION) ;SEGOUT: OUTPUTS LCD SEGMENT AND BACKPLANE DATA ;SUBROUTINES SEG0... SEG1 MUST FOLLOW DIRECTLY AFTER LOOK-UP ;TABLE, BECAUSE OF THE USE OF THE LAID-INSTRUCTION .LOCAL SEG0: LDB, #OFF1 ; POINT TO OFFSET 1 REG. [B+],#000 LD[B+],#000 LD LD A,#00B \$TWO: IFBIT #05, BCDHI ;WEIGHT >= 200 POUNDS? ;YES DISPLAY DIGIT5 ("2") INCA \$POUND: IFBIT #POUND, FLAG JP \$LPORT A,#002 ADD \$LPORT: Х A,[B] X, #BCDLO LD LD B,#MWBUF0 A,[X] LD AND A,#00F ;ELIMINATE DIGIT1 BITS ADD A,OFF2 ;GET DIGIT1 DATA LAID Х ;SAVE DIGIT1 DATA A,[B] ; IN MWBUF0 LD A,[X+] ;ELIMINATE DIGIT1 BITS AND A,#0F0 SWAP А ;ALWAYS DISPLAY DECIMAL POINT ADD A,OFF1 LAID ;GET DIGIT1 DATA SWAP А OR A,[B] ;STORE DIGIT1 AND Х A, [B+] ; DIGIT2 DATA IN MWBUF0 TL/DD/10788-13

| \$DPORT:           | LD<br>IFBIT<br>JP<br>AND<br>ADD | A,[X]<br>#04,BCD<br>\$ADD1<br>A,#00F<br>A,OFF2     | HI<br>;DISPLAY NO LEADING ZERO                             |                |

|--------------------|---------------------------------|----------------------------------------------------|------------------------------------------------------------|----------------|

| \$ADD1:            | JP<br>AND                       | \$GET<br>A,#00F                                    |                                                            |                |

| \$GET:             | ADD                             | A, OFF1                                            | ;DISPLAY "1" (DIGIT4)                                      |                |

| <b>A O D O D T</b> | LAID<br>X                       | A,[B+]                                             | ;GET DIGIT3 DATA<br>;STORE DIGIT3 DATA IN<br>;MWBUF1       |                |

| \$GPORT:           | LD<br>LAID                      | A,OFF3                                             | ;GET DIGIT5 ("2") AND SPECIAL                              |                |

| 0001               | OR<br>X<br>RET                  | A,#0FC<br>A,[B]                                    | ;SEGMENT DATA<br>;SET BITS 27 TO 1<br>;SAVE DATA IN MWBUF2 |                |

| SEG1:              | LD<br>LD<br>LD<br>JP            | B,#OFF1<br>[B+],#03<br>[B+],#03<br>A,#056<br>\$TWO | 1B<br>10                                                   |                |

| SEG2:              | LD<br>LD<br>LD<br>JP            | B,#OFF1<br>[B+],#03<br>[B+],#03<br>A,#05A<br>\$TWO |                                                            |                |

| SEG3:              | LD<br>LD<br>LD<br>JP<br>.LOCAL  | B,#OFF1<br>[B+],#0<br>[B+],#0<br>A,#05E<br>\$TWO   | 4B<br>40                                                   |                |

| DISPL:             | IFBIT<br>JP<br>JD               | #POUND, H<br>MULT2                                 | FLAG                                                       |                |

| MULT2:             | JP<br>LD<br>LD                  | LDT<br>B,#BUF12<br>[B+],#22                        |                                                            | TL/DD/10788-14 |

|                    |                                 |                                                    |                                                            |                |

|        | LD<br>JSR<br>LD<br>JSR<br>LD<br>LD<br>JSR                     | X,#STALO<br>MULBI168<br>B,#BUF12LC<br>COPY<br>STAHI+1,#C<br>DIV0,#10<br>DIVBI248     |                                                                                                     |                |

|--------|---------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|

| LDT:   | JSR<br>LD                                                     | BINBCD16<br>COUNT,#50                                                                | ;CONVERT BINARY TO BCD WEIGHT<br>;REPEAT DISPLAY LOOP 50 TIMES<br>;(=1 SEC DISPLAY TIME)            |                |

|        | LD<br>LD<br>LD<br>LD<br>LD                                    | [B+] <b>,</b> #003                                                                   | ;LOAD TIMER WITH 1000(03E8h)<br>;(=50 Hz LCD REFRESH AT tc=5us)<br>;LOAD AUTOREG. WITH 1000         |                |

|        | LD                                                            |                                                                                      | ;CNTRL-REG.:"TIMER WITH AUTO-<br>;LOAD"- MODE,START TIMER                                           |                |

| DISP1: | LD                                                            | [B+],#010                                                                            | ;PSW-REG.:RESET TPND FLAG                                                                           |                |

|        | JSR                                                           | SEG0                                                                                 | ;GET 7-SEGM. DATA FOR REFRESH<br>;TIMEPHASE Ta                                                      |                |

| TP0:   | JSR                                                           | TTPND                                                                                | ;TEST TIMER PENDING FLAG<br>;BACKPLANE REFRESH Ta                                                   |                |

|        | SBIT<br>LD<br>RBIT<br>SBIT<br>LD<br>RBIT<br>JSR<br>JSR<br>JSR | <pre>#BP1, [B] A, [B+] #BP2, [B] #BP1, [B] A, [B-] #BP2, [B] SEGOUT SEG1 TTPND</pre> | ; POINT TO G-CONFIGREG.<br>; POINT TO G-DATA REG.<br>; SEGMENT DATA OUT<br>; GET 7-SEG. DATA FOR Tb |                |

| TP1:   | SBIT                                                          | #BP2,[B]                                                                             |                                                                                                     |                |

|        | LD<br>RBIT<br>SBIT                                            | #BP2,[B]<br>#BP1,[B]<br>#BP2,[B]                                                     | ;POINT TO G-CONFREG.                                                                                |                |

|        | LD<br>RBIT                                                    | A,[B-]<br>#BP1,[B]                                                                   | ;POINT TO G-DATA REG.                                                                               |                |

|        | JSR<br>JSR<br>JSR                                             | SEGOUT<br>SEG2<br>TTPND                                                              | ;GET 7-SEGM. DATA FOR TC                                                                            |                |

| TP2:   | RBIT<br>LD<br>RBIT                                            | #BP1,[B]<br>A,[B+]<br>#BP2,[B]                                                       | ;POINT TO G-CONFIGREG.                                                                              |                |

|        | SBIT<br>LD<br>RBIT<br>JSR                                     | #BP1,[B]<br>A,[B-]<br>#BP2,[B]<br>SEGOUT                                             | ;POINT TO G-DATA-REG.                                                                               |                |

|        |                                                               |                                                                                      |                                                                                                     | TL/DD/10788-15 |

|        |                                                               |                                                                                      |                                                                                                     |                |

|        |                                                               |                                                                                      |                                                                                                     |                |

|        |                                                               |                                                                                      |                                                                                                     |                |

|   |         | TOD                                               | 0000                                                               |                                                                         |                |

|---|---------|---------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|

|   |         | JSR<br>JSR                                        | SEG3<br>TTPND                                                      |                                                                         |                |

|   | TP3:    | RBIT<br>RBIT<br>LD<br>RBIT<br>SBIT<br>JSR<br>DRSZ | <pre>#BP1,[B] #BP2,[B] A,[B+] #BP1,[B] #BP2,[B] SEGOUT COUNT</pre> |                                                                         |                |

|   |         | JP<br>LD                                          | DISP1<br>COUNT,#50                                                 |                                                                         |                |

|   |         | DRSZ<br>JP<br>JSR                                 | COUNT2<br>DISP1<br>DISPD                                           | ;10SEC OVER?<br>;NO, DISPLAY WEIGHT                                     |                |

|   |         | RET                                               | DISPD                                                              | ;YES ROUTINE FINISHED                                                   |                |

|   | DISPD:  |                                                   |                                                                    | ;SWITCH DISPLAY OFF                                                     |                |

|   |         | LD<br>LD                                          | B,#PORTLD<br>[B+],#000                                             | ;OUTPUT 0 TO L PORT                                                     |                |

|   |         | LD<br>LD                                          | [B+],#0FF<br>B,#PORTGD                                             | ;L-PORT = OUTPUT PORT                                                   |                |

|   |         | LD<br>LD                                          | [B+],#000<br>[B+],#037                                             |                                                                         |                |

|   |         | LD<br>RET                                         | PORTD,#000                                                         | ) ;OUTPUT 0 TO D-PORT                                                   |                |

|   | SEGOUT: |                                                   |                                                                    |                                                                         |                |

|   |         | LD<br>LD<br>X                                     | B,#MWBUF0<br>A,[B+]<br>A,PORTLD                                    | ;POINT TO MWBUF1<br>;OUTPUT 7 SEG. DATA IN                              |                |

|   |         | LD                                                | A,[B+]                                                             | ;MWBUF0 TO L-PORT<br>;POINT TO MWBUF2                                   |                |

|   |         | X<br>LD                                           | A, PORTD<br>X, #PORTGD                                             | ;OUTPUT MWBUF1 TO D-PORT                                                |                |

|   |         | LD<br>AND                                         | A, [X]<br>A, [B]                                                   | ;AND MWBUF2 WITH PORTGD                                                 |                |

|   |         | Х                                                 | A,[B]                                                              | ;LEAVE BITS 27 UNCHANGED<br>;STORE RESULT (A')IN                        |                |

|   |         | AND                                               | A,#003                                                             | ;MWBUF2,LOAD A WITH<br>;ORIGINAL MWBUF2 VALUE<br>;AND 007 WITH ORIGINAL |                |

|   |         | AND                                               | A,#003                                                             | ;MWBUF2 (A''),SET BITS 0,1 TO<br>;CORRECT VALUE                         |                |

|   |         | OR                                                | A,[B]                                                              | ;OR A' WITH A'', RESTORE ORIGINAL<br>;G2G7 BITS                         |                |

|   |         | X<br>RET                                          | A,[X]                                                              | ;OUTPUT RESULT TO G-PORT                                                |                |

|   |         |                                                   |                                                                    |                                                                         | TL/DD/10788-16 |

|   |         |                                                   |                                                                    |                                                                         |                |

|   |         |                                                   |                                                                    |                                                                         |                |

|   |         |                                                   |                                                                    |                                                                         |                |

|   |         |                                                   |                                                                    |                                                                         |                |

| 1 |         |                                                   |                                                                    |                                                                         |                |

;16 BIT BINARY TO BCD CONVERSION ;THE MEMORY ASSIGNMENTS ARE AS FOLLOWS: ;BINLO: RAM ADRESS BINARY LOW BYTE ;BCDLO: RAM ADRESS BCD LOW BYTE ;COUNT: RAM ADRESS SHIFT COUNTER (0F0...0FB,0FF) ; BCD NUMBER IN BCDLO, BCDLO+1, BCDLO+2 ; MEMORY ADRESS M(BINLO+1) M(BINLO) BINARY HB ;DATA BINARY LOW BYTE ; ; MEMORY ADRESS M(BCDLO+2) M(BCDLO+1) M(BCDLO) ;DATA BCD HB BCD BCD LOW BYTE ; BINLO = STALO .LOCAL \$BCDT = (BCDLO + 3) & OF\$BINT = (BINLO + 2) & OF BINBCD: COUNT, #16 ;LOAD CONTROL REGISTER WITH LD;NUMBER OF LEFTSHIFTS TO ;EXECUTE LD B, #BCDLO ;LOAD BCD-NUMBER LOWEST BYTE ;ADRESS ;CLEAR BCD RAM-REGISTERS \$CBCD: LD [B+],#00 IFBNE #\$BCDT JP \$CBCD ;LEFTSHIFT BINARY NUMBER \$LSH: LD B, #BINLO RC \$LSHFT: LD A,[B] A,[B] ADC ; IF MSB IS SET, SET CARRY Х A,[B+] IFBNE #\$BINT JP \$LSHFT B, #BCDLO LD\$BCDADD: LDA,[B] ;ADD CORRECTION FACTOR A,#066 ADD ADC A, [B] ;LEFTSHIFT BCD NUMBER ; (BCD=2\*\*WEIGHT OF ;BINARY BIT (=CARRY BIT)) DCOR ; DECIMAL CORRECT ADDITION А A, [B+] Х IFBNE #\$BCDT TL/DD/10788-17 JP \$BCDADD DRSZ COUNT ;DECREMENT SHIFT COUNTER JP \$LSH RET .LOCAL TL/DD/10788-18

```

;BINARY DIVIDE 24BIT BY 8BIT (Q=Y/Z)

;YL: LOW BYTE RAM ADRESS DIVIDEND

;ZL: LOW BYTE RAM ADRESS DIVISOR

;CNTR: RAM ADRESS SHIFT COUNTER (0F0...0FB,0FF)

;QUOTIENT AT RAM LOCATIONS YL..YL+2

;REMAINDER AT YL+3

;QUOTIENT IS ALL '1'S IF DIVIDE BY ZERO, REMAINDER

; THEN CONTAINS YL

; THE MEMORY ASSIGNMENTS ARE AS FOLLOWS:

;

M(YH+1) M(YH)

M(YL+1) = M(YL)

;

Y (HIGH BYTE) Y Y (LOW BYTE)

0

;

___

---

_____

;

M(ZL)

;

Ζ

;

;

;ROUTINE NEEDS 1.21ms FOR EXECUTION AT tc=1us

ΖL

= DIVO

= STALO

= COUNT

YL.

CNTR

.LOCAL

$YH

= YL+2

$BTY

= ($YH&00F)+2 ;PARAMETER FOR "IFBNE"-INSTR.

DIVBI248:

CNTR, #018 ; INITIALIZE SHIFT COUNTER

LD

B,#$YH+1 ;FOR 24 COUNTS

[B],#000 ;PUT 0 IN M(YH+1)

LD

LD

X,#$YH+1

LD

$LSHFT:

LD

B, #YL ; LEFT SHIFT DIVIDEND

RC

$LUP:

LD

A,[B]

ADC

A,[B]

A, [B+]

Х

IFBNE

#$BTY

JP

$LUP

LD

B,#ZL

IFC

JP

$SUBT

$TSUBT:

;SUBTRACT AND TEST

SC

;SUBTRACT Z FROM M(YH+1,YH+2)

LD

A,[X]

SUBC

A,[B]

IFNC

JP

$TEST

TL/DD/10788-19

```

\$SUBT: ;SUBTRACT Z FROM M(YH+1, YH+2) LDA,[X] SUBC A,[B] Х A,[X] LD B,#YL SBIT #0,[B] \$TEST: CNTR ;24 SHIFTS EXECUTED? \$LSHFT ;NO, LEFT SHIFT DIVIDEND DRSZ CNTR JP RET .LOCAL ; BINARY MULTIPLIES A 16BIT VALUE (X1) ;WITH A 8BIT VALUE (X2): M = X1 + X2;X1L: RAM ADRESS X1 LOW BYTE ;X2L: RAM ADRESS X2 ;COUNT RAM ADRESS SHIFT COUNTER ;M IS STORED AT RAM ADRESSES X2L...X2L+2 ;THE MEMORY ASSIGNMENTS ARE AS FOLLOWS: ;MEMORY M(X2L+2) M(X2L+1) M(X2L) ;DATA 0 0 X2 ;-----; MEMORY M(X1L+1) M(X1L) X1 (LOW BYTE) X1(H.B.) ;DATA ;THE EXECUTION TIME FOR THE ROUTINE AT tc=lus IS 240us ; .LOCAL MULBI168: COUNT, #9 ; PRESET SHIFT COUNTER LD[B+],#00 ;PRESET X2L+1,X2L+2 WITH '0' LD[B]**,**#00 LDRC \$LOOP: A,[B] ;RIGHT SHIFT LDRRCA Х A,[B-] A,[B] LD RRCA Х A,[B-] LD A,[B] RRCA Х A,[B+] TL/DD/10788-20

| \$TEST: | LD<br>IFNC<br>JP<br>RC<br>LD<br>LD<br>ADC<br>X<br>LD<br>ADC<br>X | A, [B+]<br>\$TEST<br>A, [B-]<br>A, [X+]<br>A, [B]<br>A, [B+]<br>A, [X-]<br>A, [B]<br>A, [B] | ; INCREMENT B POINTER<br>; MOST SIGN. BIT OF X2 SET?<br>; NO, TEST SHIFT COUNTER<br>; YES, RESET CARRY<br>; POINT TO 2nd HIGHEST BYTE<br>; OF RESULT<br>; DO WEIGHTED ADD |                |

|---------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Ŷ1E51.  | DRSZ<br>JP<br>RET<br>.LOCAL<br>.END                              | COUNT<br>\$LOOP                                                                             | ;8 RIGHT SHIFTS EXECUTED?<br>;NO,SHIFT<br>;YES,MULIPLICATION FINISHED                                                                                                     | TL/DD/10788-21 |

|         |                                                                  |                                                                                             |                                                                                                                                                                           |                |

|         |                                                                  |                                                                                             |                                                                                                                                                                           |                |

|         |                                                                  |                                                                                             |                                                                                                                                                                           |                |

|         |                                                                  |                                                                                             |                                                                                                                                                                           |                |

|         |                                                                  |                                                                                             |                                                                                                                                                                           |                |

|         |                                                                  |                                                                                             |                                                                                                                                                                           |                |

Γ

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

|  | R | National Semiconductor<br>Corporation<br>2900 Semiconductor Drive<br>P.O. Box 58090<br>Santa Clara, CA 95052-8090<br>Tei: 1(800) 272-9959<br>TWX: (910) 339-9240 | National Semiconductor<br>GmbH<br>Livry-Gargan-Str. 10<br>D-82256 Fürstenfeldbruck<br>Germany<br>Tel: (81-41) 35-0<br>Telex: 527649<br>Fax: (81-41) 35-1 | National Semiconductor<br>Japan Ltd.<br>Sumitomo Chemical<br>Engineering Center<br>Bidg. 7F<br>1-7-1, Nakase, Mihama-Ku<br>Chiba-City, Nakase, Mihama-Ku<br>Chiba-City, Cita Prefecture 261<br>Tel: (043) 239-2500<br>Fax: (043) 299-2500 | National Semiconductor<br>Hong Kong Ltd.<br>13th Floor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsui, Kowloon<br>Hong Kong<br>Tei: (852) 2737-1600<br>Fax: (852) 2736-9960 | National Semiconductores           Do Brazil Ltda.           Rue Deputado Lacorda Franco           120-34           Sao Paulo-SP           Brazil 0416-000           Tel: (55-11) 212-5066           Telex: 391-1131931 NSBR BR           Fax: (55-11) 212-1181 | National Semiconductor<br>(Australia) Pty, Ltd.<br>Buisiness Park Drive<br>Monash Business Park<br>Nottinghill, Melbourne<br>Victoria 3168 Australia<br>Tel: (3) 558-9999<br>Fax: (3) 558-9998 |

|--|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

## **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated