# Flexible Timing Configuration with IO-Link Master Frame Handler

# Thomas Schneider

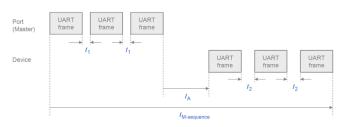

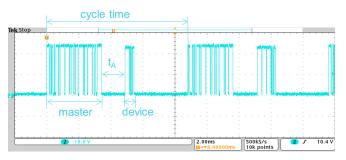

IO-Link is a serial, bi-directional, point-to-point protocol and interface standard for sensors and actuators in factory automation applications. An IO-Link system consists of an IO-Link master and IO-Link devices, including sensors, actuators, RFID readers, I/O modules, and so forth. The IO-Link master enables data exchange with IO-Link devices from different manufacturers. These interactions of the master and its devices are characterized by several time constraints that apply to the UART frame and the master and device message transmission times. Communication between a master port and its associated device takes place in a fixed schedule called the M-sequence time. Figure 1 demonstrates the timings of an M-sequence consisting of a master port message and a device message. The device needs to respond to the master within the response time of the device  $t_{A}$  and not exceeding the maximum UART frame transmission delay t<sub>2</sub>.

Figure 1. IO-Link Timing

Usually a frame handler is used to execute most of the low level communication tasks to decrease the load on the processor of the IO-Link master. Often, this frame handler is implemented already in a semiconductor device together with the PHY. As the frame handler implementation is fixed in this case in hardware, this makes it inflexible to react on the different timing behaviors of the IO-Link devices from different manufacturers. According to the IO-Link specification, the time  $t_A$  needs to be less than 10  $T_{Bit}$  and  $t_2$  needs to be less than 3  $T_{Bit}$ , where  $T_{BIT} = 1 / (transmission)$ rate). For example, this might be violated if an inductive coupler device is between the master and the device communication line and adding some delay to the communication. A frame handler with fixed timing limits might not be able to continue with the IO-Link communication in this case. TI's solution to implement the frame handler in software using the programmable real time unit and industrial communications subsystem (PRU-ICSS) of the Sitara<sup>™</sup> processor family makes it much more flexible

# TEXAS INSTRUMENTS

to react on the different timing behaviors. This flexible timing configuration makes it possible to also communicate in these special use cases. Not only can the time  $t_A$  and  $t_2$  be adjusted during run-time, but also the delay time while establishing Master port communication  $T_{DMT}$  can be adjusted as needed.

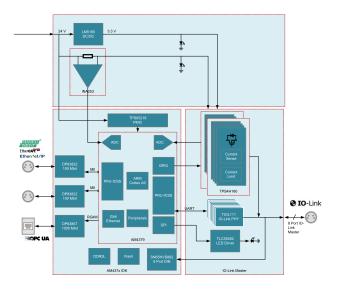

Figure 2 shows the block diagram of an 8 Port IO-Link Master Reference Design (TIDA-010016) where the frame handler is implemented in software using the PRU.

## Figure 2. TIDA-010016 Block Diagram

## Implementation

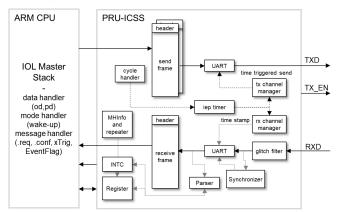

For the IO-Link master frame handler implementation with a flexible timing configuration, one of TI's Sitara processors with the integrated PRU-ICSS has been used. The PRU-ICSS is a specialized sub-processor within some of TI's Sitara processors. It is designed to complete most instructions in a single cycle and offers deterministic behavior of those. This PRU-based frame handler enables a very flexible way of timing and time synchronization and is almost free of jitter. It replaces hardware UARTs by a software implementation and eliminates the need for external processing hardware. With one PRU up to 8 IO-Link master ports can be realized. As one ICSS module of the Sitara processor consists out of two PRUs, up to 16 IO-Link master ports can be realized with one ICSS module. All ports support independent cycle time from 400 µs up to 132 ms in 100 µs steps. At 400 µs, a maximum payload of eight bytes is supported. The double send buffer

www.ti.com

minimizes  $t_{idle}$  time and offloads the host timing. Synchronous start of selected channels is supported without any jitter and latency between the channels. Figure 3 shows the IO-Link master PRU frame handler. The often available second ICSS module on the Sitara processor can be used to process something else, like real-time Ethernet.

#### Figure 3. IO-Link Master – PRU Frame Handler

Sitara processor:

The IO-Link master PRU frame handler driver is part of the RTOS Processor SDK for Sitara AM437x and AMIC120 PROCESSOR-SDK-RTOS-AM437X. The driver supports the following major functionalities:

- Standard APIs to initialize, de-initialize, and control the common Software IP driver

- Configuration and control of the PRU frame handler firmware to handle the messages transferred between the IO-Link master and device

- Timer and interrupt driven IO-Link communication between IO-Link master and device to meet the timing requirement of IO-Link master protocol

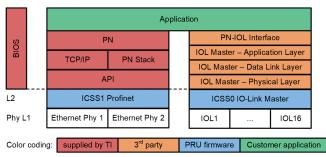

In addition, a sample IO-Link master stack interface layer is provided in the IO-Link master demo application to provide an interface between the IO-Link master stack and the driver. Figure 4 shows an IO-Link master integration example with Profinet. ICSS0 is used for IO-Link and ICSS1 is used for Profinet.

#### Figure 4. PRU-ICSS IO-Link Master Project Example

#### **Test Results**

For test purposes, an inductive coupler device is used. Inductive coupler devices are placed between an IO-Link master and an IO-Link device to transfer power and IO-Link data contactlessly across an air gap, adding some delay to the response time  $t_A$  of the IO-Link device. In the test case, an IO-Link device with a transmission rate of 38.4 kbit/s (COM2) is used. Figure 5 shows the measured response time  $t_A$  which is 57 T<sub>BIT</sub>.

Figure 5. Measured Response Time t<sub>A</sub> of the IO-Link Device

A standard IO-Link master frame handler implementation in hardware is not be able to communicate with an IO-Link device with a response time of 57  $T_{BIT}$  as it is not flexible enough to adjust the timing. Only the flexible timing configuration with the IO-Link master frame handler implemented in software using the PRU makes it possible to still communicate with IO-Link devices in these special use cases.

#### **Table 1. Alternative Device Recommendations**

| DEVICE  | OPTIMIZED<br>PARAMETERS                      | PERFORMANCE<br>TRADE-OFF                    |

|---------|----------------------------------------------|---------------------------------------------|

| AM4x    | ARM Cortex-A9 Up to<br>1000 MHz; 2x PRU-ICSS |                                             |

| AMIC120 | 2x PRU-ICSS                                  | ARM Cortex-A9 Up to<br>300 MHz              |

| AMIC110 |                                              | ARM Cortex-A9 Up to<br>300 MHz; 1x PRU-ICSS |

#### References

Texas Instruments, Sitara AM4x Processors

Texas Instruments, 8 Port IO-Link Master Reference Design (TIDA-010016)

IO-Link, IO-Link Interface and System Specification

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated