# TMS320C6414, TMS320C6415, and TMS320C6416 Digital Signal Processors Silicon Errata

Silicon Revisions 1.0, 1.01, 1.02, 1.03, 1.1, 2.0

SPRZ011T October 2001 Revised August 2007

Copyright © 2007, Texas Instruments Incorporated

#### **REVISION HISTORY**

This silicon errata revision history highlights the technical changes made to the SPRZ011S revision to make it an SPRZ011T revision.

**Scope:** Applicable updates to the C64x device family, specifically relating to the C6414/C6415/C6416 devices, have been incorporated. TMS320C6414/C6415/C6416 silicon revision 2.0 updates have been incorporated.

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                            |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 16             | Silicon Revision 2.0 Known Design Exceptions to Functional Specifications section:<br>Added Advisory 2.0.5 – "PCI Reads May Get Ahead of PCI Writes When PCI Exceeds the Transfer Request Limit (C6415/C6416<br>Only)" |  |

## Contonte

| 1 | Introduction     |                                                                                                                                                                    |

|---|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                  | Development-Support Tool Nomenclature                                                                                                                              |

|   |                  | entification                                                                                                                                                       |

|   |                  |                                                                                                                                                                    |

| 2 |                  | 2.0 Known Design Exceptions to Functional Specifications and Usage Notes                                                                                           |

|   | •                | s for Silicon Revision 2.0                                                                                                                                         |

|   | TCP/VCP: T       | Bit in HPIC Register is Writable by CPU       10         CP/VCP Memory Address Range Must be Accessed Using Only Doublewords       10         4x Devices)       10 |

|   |                  | 10 d CLKOUT4/6                                                                                                                                                     |

|   |                  | Incorrect Update of the L1P Tag RAMs (All C64x Devices)                                                                                                            |

|   |                  | sion 2.0 Known Design Exceptions to Functional Specifications                                                                                                      |

|   | Advisory 2.0.1   | L2 Cache: Accesses to Mapped L2 RAM Update L2 LRU Information                                                                                                      |

|   | Advisory 2.0.2   | L2 Cache: L2 Controller Incorrectly Updates LRU for Accesses in L2 Cache                                                                                           |

|   | Advisory 2.0.3   | EMIF: PDT Transfers Fail When Acessing the Same SDRAM Page as Non-PDT<br>Transfers                                                                                 |

|   | Advisory 2.0.4   | PCI: Slave Reads With a Long Latency Can Return Bad Data (C6415/C6416 Only) 15                                                                                     |

|   | Advisory 2.0.5   | PCI Reads May Get Ahead of PCI Writes When PCI Exceeds the Transfer                                                                                                |

|   | ,                | Request Limit (C6415/C6416 Only) 16                                                                                                                                |

| 3 |                  | 1.1 Known Design Exceptions to Functional Specifications and Usage Notes                                                                                           |

|   | 3.1 Usage Note   | s for Silicon Revision 1.1                                                                                                                                         |

|   | 3.2 Silicon Revi | sion 1.1 Known Design Exceptions to Functional Specifications                                                                                                      |

|   | Advisory 1.1.1   | EMIF: CLKOUT6 may not be CPU/6 During Reset 17                                                                                                                     |

|   | Advisory 1.1.2   | PCI: Slave Writes With Null Data Phases Can Lock Up PCI (C6415/C6416 Only) 17                                                                                      |

|   | Advisory 1.1.3   | PCI: Slave Writes Can Corrupt Data (C6415/C6416 Only) 18                                                                                                           |

|   | Advisory 1.1.4   | PCI: Slave Reads Without Any Byte Enables Issue Target Abort (C6415/C6416 Only) 18                                                                                 |

|   | Advisory 1.1.5   | PCI: Master Transaction Following an Abort Can Erroneously Set MASTEROK<br>(C6415/C6416 Only)                                                                      |

|   | Advisory 1.1.6   | PCI: An Abort Received During a Master Read Can Lock Up PCI (C6415/C6416 Only) 19                                                                                  |

|   | Advisory 1.1.7   | PCI: Do Not Write a "1" to the Cache Line Size Register (C6415/C6416 Only) 19                                                                                      |

|   | Advisory 1.1.8   | HPI: Simultaneous Host and CPU Writes to HPIC Register Conflict                                                                                                    |

|   | Advisory 1.1.9   | EMU: Emulation Prone to Failure Under Certain Situations                                                                                                           |

|   | Advisory 1.1.10  | EMU: Driver-Induced HSRTDX Data Corruption                                                                                                                         |

|   | Advisory 1.1.11  | EMU: Data Corruption with RTDX and Real-Time Emulation Memory Read                                                                                                 |

|   | Advisory 1.1.12  | PLL: PLL May Fail to Oscillate on Startup                                                                                                                          |

|   | Advisory 1.1.13  | PCI: PCI Power Management Sticky Bits Always "1" (C6415/C6416 Only) 24                                                                                             |

|   | Advisory 1.1.14  | EMIF: Data Corruption can Occur in SDRAM When HOLD Feature is Used                                                                                                 |

|   | Advisory 1.1.15  | EMIF: PDT Write Transfers Fail When PDTWL Equals 3                                                                                                                 |

|   | Advisory 1.1.16  | PLL: PLL May Stop Oscillating if I/O Supply Falls Out of Specification                                                                                             |

|   | -                |                                                                                                                                                                    |

| 4 | Silicon Revision 1 | .03 Known Design Exceptions to Functional Specifications and Usage Notes                             | 26 |

|---|--------------------|------------------------------------------------------------------------------------------------------|----|

|   | •                  | for Silicon Revision 1.03                                                                            |    |

|   |                    | Does not Stop During Emulation Halt                                                                  |    |

|   | -                  | Specification Change for ARDY Sampling Moving Forward for Silicon Revision 1.1                       |    |

|   | Advisory 1.03.1    | EMIF: BECLKIN Must Be Provided During Reset                                                          |    |

|   | Advisory 1.03.2    | EMIF: BUSREQ Signal is Deasserted for 1 Cycle Under Certain Scenario                                 |    |

|   | Advisory 1.03.3    | EMIF: PDT Feature is not Functional                                                                  |    |

|   | Advisory 1.03.4    | L2: All Odd MAR Reads Return Incorrect Data                                                          |    |

|   | Advisory 1.03.5    | L1D: Overlapping/Adjacent Accesses Cause Bank Conflict Stalls                                        |    |

|   | Advisory 1.03.6    | DMA: DMA Can Be Locked Out of L2                                                                     |    |

|   | Advisory 1.03.7    | UTOPIA: Utopia Does Not Drive RxCLAV/TxCLAV Low Before Hi-Z (C6415/C6416 Only)                       | 29 |

|   | Advisory 1.03.10   | L1D: Write Hits Stall When Write Miss Buffer is not Empty                                            |    |

|   | Advisory 1.03.11   | HPI: Reading HPIA or HPIC After Reading HPID With Postincrement Fails                                | 30 |

|   | Advisory 1.03.12   | EMIF: Asynchronous Mode Does Not Work With Hold Values Other Than 1                                  | 30 |

|   | Advisory 1.03.13   | TCP: TCP is Not Functional for Certain Frame Sizes and Code Rates (C6416 Only)                       | 31 |

|   | Advisory 1.03.14   | EMIF: Asynchronous Write Followed by Read Can Occur With No CE Deassertion                           | 32 |

|   | Advisory 1.03.15   | EMIF: CE Not Asserted Correctly Under Certain Scenario in Synchronous Mode                           | 32 |

|   | Advisory 1.03.16   | EDMA: Transfer Completion Code Not Set for Large Transfers                                           | 32 |

|   | Advisory 1.03.17   | TCP: Frame Sizes Larger Than 20730 Cause Error (C6416 Only)                                          | 33 |

|   | Advisory 1.03.18   | VCP: Output Pointer is Incorrect (C6416 Only)                                                        | 33 |

|   | Advisory 1.03.19   | TCP: TCP Does Not Generate EDMA Event With SUM = 01 (C6416 Only)                                     | 33 |

|   | Advisory 1.03.20   | UTOPIA Does Not Regenerate EDMA Events as Specified (C6415/C6416 Only)                               | 34 |

|   | Advisory 1.03.21   | PCI: Idle Cycles are Required Between Slave Reads (C6415/C6416 Only)                                 | 34 |

|   | Advisory 1.03.23   | EMU: Device May Not Operate Properly Without an Active TCK                                           | 35 |

|   | Advisory 1.03.24   | CACHE: L2 Does Not Clean or Flush the Cache on Every Invocation                                      | 35 |

|   | Advisory 1.03.26   | JTAG: JTAG Does Not Function in Heterogeneous Environments                                           | 35 |

|   | Advisory 1.03.27   | EMU: Advanced Emulation Features are Not Functional                                                  | 36 |

|   | Advisory 1.03.28   | HPI: Host HPIA Writes can Block CPU HPIC Writes                                                      | 36 |

|   | Advisory 1.03.29   | PCI: PCI Burst Lengths Limited to 16 Words (C6415/C6416 Only)                                        | 36 |

|   | Advisory 1.03.30   | TCP: SNR Stopping Criteria Nonfunctional for Small Frames (C6416 Only)                               | 37 |

|   | Advisory 1.03.31   | VCP: Normalization Error in SM Max/Min (C6416 Only)                                                  | 37 |

|   | Advisory 1.03.32   | VCP: Sliding Windows Boundaries (C6416 Only)                                                         | 37 |

|   | Advisory 1.03.33   | TCP/VCP: Using Concurrent/Different Priority Levels can Corrupt Data (C6416 Only)                    | 37 |

|   | Advisory 1.03.34   | PCI Speed: PCI Does not Operate Correctly Unless CPU is Running 8 Times Faster<br>(C6415/C6416 Only) |    |

|   | Advisory 1.03.35   | EMU: Interrupts Received While Halted may not Execute Correctly                                      |    |

|   | Advisory 1.03.36   | EMU: Interrupts Received Near Software Breakpoints may Falsely Trigger the<br>Breakpoint             |    |

|   | Advisory 1.03.37   | PCI: Non-Word PCI Accesses in Big-Endian Mode Corrupt Data (C6415/C6416 Only)                        |    |

|   | Advisory 1.03.38   | VCP: SYMX/R Bits Set to a Value of Less Than 2 Can Cause Error (C6416 Only)                          |    |

|   | Auvisory 1.03.30   | Vor . Or where Dies Set to a value of Less than 2 Can Cause Lifter (Co4 to Oflig)                    | 29 |

| 5 | Silicon Revisions | 1.0, 1.01, and 1.02 Known Design Exceptions to Functional Specifications     | 40 |

|---|-------------------|------------------------------------------------------------------------------|----|

|   | Advisory 1.0.7    | EMIF: CLKOUT6 is Not Functional                                              | 40 |

|   | Advisory 1.0.13   | PCI: PCI is Not Functional When DSP is in Big-Endian Mode (C6415/C6416 Only) | 40 |

|   | Advisory 1.0.18   | RESET: Asserting RESET Does Not Wake Up CPU From PD3 Mode                    | 40 |

|   | Advisory 1.0.19   | RESET: Improper Reset May Damage the Device                                  | 41 |

|   | Advisory 1.0.26   | PD1 Does Not Gate Off CPU Clock                                              | 42 |

#### 1 Introduction

This document describes the known exceptions to the functional specifications for the TMS320C6414, TMS320C6415, and TMS320C6416 digital signal processors. [See the *TMS320C6414, TMS320C6415, TMS320C6416 Fixed-Point Digital Signal Processors* data sheet (literature number SPRS146).] Throughout this document, TMS320C64x and C64x refer to TMS320C6414, TMS320C6415, and TMS320C6416.

For additional information, see the latest version of the *TMS320C6000 DSP Peripherals Overview Reference Guide* (literature number SPRU190).

The advisory numbers in this document are not sequential. Some advisory numbers have been moved to the next revision and others have been removed and documented in the user's guide. When items are moved or deleted, the remaining numbers remain the same and are not resequenced.

This document also contains "Usage Notes". Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 1.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all TMS320<sup>™</sup> DSP devices and support tools. Each TMS320<sup>™</sup> DSP commercial family member has one of three prefixes: TMX, TMP, or TMS. Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- **TMS** Fully qualified production device

Support tool development evolutionary flow:

**TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

TMS320 is a trademark of Texas Instruments. All trademarks are the property of their respective owners.

**TMDS** Fully qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

#### 1.2 Revision Identification

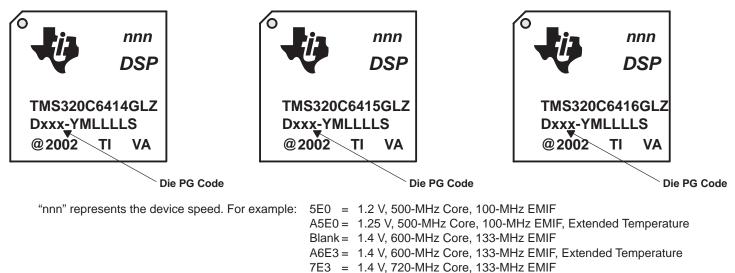

The device revision can be determined by the Die PG code marked on the top of the package. The location of the Die PG code for the GLZ package is shown in Figure 1. Figure 1 shows some examples of the types of C6414, C6415, and C6416 package symbolization.

NOTE: Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" or "TMP" at the beginning of the device name.

#### Figure 1. Example, Die PG Codes for TMS320C6414, TMS320C6415, and TMS320C6416 (GLZ)

Silicon revision is identified by a code on the chip. The code is of the format Dxxx-YMLLLLS or Cxxx-YMLLLLS, etc. If xxx is 101, then the silicon is revision 1.01; if xxx is 102, then the silicon is revision 1.02, etc.

| Die PG Code<br>(xxx) | Silicon Revision | Comments                                                                                                 |

|----------------------|------------------|----------------------------------------------------------------------------------------------------------|

| 10                   | 1.0              | TMS320C6414, TMS320C6415, and TMS320C6416                                                                |

| 101                  | 1.01             | TMS320C6414, TMS320C6415, and TMS320C6416 Silicon Revision 1.01 is functionally the same as Revision 1.0 |

| 102                  | 1.02             | TMS320C6414, TMS320C6415, and TMS320C6416 Silicon Revision 1.02 is functionally the same as Revision 1.0 |

| 103                  | 1.03             | TMS32C6414C, TMS32C6415C, and TMS32C6416C                                                                |

| 11                   | 1.1              | TMS32C6414D, TMS32C6415D, and TMS32C6416D                                                                |

| 20                   | 2.0              | TMS32C6414E, TMS32C6415E, and TMS32C6416E                                                                |

| Table 1 | I. Die | PG | Codes |

|---------|--------|----|-------|

|---------|--------|----|-------|

## 2 Silicon Revision 2.0 Known Design Exceptions to Functional Specifications and Usage Notes

#### 2.1 Usage Notes for Silicon Revision 2.0

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### HPI: HWOB Bit in HPIC Register is Writable by CPU

On silicon revision 2.0 and earlier, the HWOB bit in the HPIC register is writable by the CPU, even though it should be writable by the Host only. Writing the incorrect value to the HPIC register will corrupt any data passed through the HPI.

When performing HPIC writes via the CPU, be sure to write the correct value into the HWOB bit.

## TCP/VCP: TCP/VCP Memory Address Range Must be Accessed Using Only Doublewords (All C64x Devices)

On silicon revision 2.0 and earlier, the TCP/VCP memory address range (0x5000 0000 to 0x5FFF FFFF) must always be accessed by doubleword requests. Even if the C64x device does not support the TCP/VCP peripherals or if the TCP/VCP coprocessors are not enabled, this memory address range must *always* be accessed via doublewords. A request of any other size will cause the chip to hang. Users should be especially careful when using Code Composer Studio <sup>™</sup> Integrated Development Environment (IDE), because Code Composer Studio requests memory data using word-sized accesses. Do not attempt to view this memory map region (0x5000 0000 to 0x5FFF FFFF) in a Code Composer Studio window. (Note: this region can be disabled in the Code Composer Studio memory map to prevent accidental access.)

For all TMS320C64x<sup>™</sup> DSP devices, always access the memory address range 0x5000 0000 to 0x5FFF FFFF via doublewords.

#### EMIFA: Dead CLKOUT4/6

On silicon revision 2.0 and earlier, there is a usage condition concerning EMIFA which can affect the functionality of CLKOUT4 and CLKOUT6.

The EMIFA Global Control register (GBLCTL) controls the logic that outputs the internal CPU/4 or CPU/6 clocks to the CLKOUT4 and CLKOUT6 pins. The GBLCTL is registered with the AECLKIN clock; therefore, without a valid EMIF clock, it is possible to have unknown values in the GBLCTL register. Furthermore, without a valid EMIF clock, the EMIFA GBLCTL will not be reset to its default value.

To avoid a dead CLKOUT4 and/or CLKOUT6, a valid clock must be provided to EMIFA at all times. This can be implemented externally using AECLKIN or by setting the BEA[17:16] pins (EMIFA\_CLK\_SEL bits) to select the internal CPU/4 or CPU/6.

Code Composer Studio and TMS320C64x are trademarks of Texas Instruments.

#### L1P Cache: Incorrect Update of the L1P Tag RAMs (All C64x Devices)

On C6414/C6415/C6416 silicon revision 2.0 and earlier, when the CPU is executing non-cacheable code from external memory and there is snoop activity from L2 to L1P occurring at the same time, an incorrect update to the L1P Tag RAM can occur.

Snoop activity from L2 to L1P can be generated two ways:

- 1. EDMA/QDMA activity to L2

- 2. Block cache invalidates initiated in L2

When there is a non-cacheable L1P fetch that is returned from L2 to L1P, **and** there is a snoop from L2 in the very next cycle, then the snoop tag read interferes with the tag/status RAM write for the non-cacheable data. This interference causes the tag RAMs to be incorrectly updated with the tag for that line, rather than discarding the write to the tags. When the NEXT access to that non-cacheable line in L2 occurs, the L1P incorrectly registers this as a hit and transfers data from the L1P rather than the desired external data.

To avoid an incorrect update of the L1P tag RAMs, do the following as best practice:

- 1. While executing code from non-cacheable space, *do not* perform either EDMA/QDMA transfers to L2 *or* block cache invalidates initiated in L2

- 2. Mark program code as cacheable as soon as possible.

#### 2.2 Silicon Revision 2.0 Known Design Exceptions to Functional Specifications

For the C6414/C6415/C6416 device there is **no** current plan to have any further *major* silicon updates; therefore, all silicon revision 2.0 known design exceptions to functional specifications identified will be how the device functionally operates and will **not** be changed/corrected.

| L2 Cache: Accesses to Mapped L2 RAM Update L2 LRU Information                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CPU accesses to L2 RAM addresses incorrectly cause updates to the "Least-Recently Used" (LRU) state information in the L2 cache. This may cause an increased number of L2 cache misses in some systems.                                                                                                                                                                                                                                                                                                       |

| The L2 cache implements a 4-way set-associative cache. The cache uses the (LRU) information to determine what "way" within each set is least recently used. When the CPU accesses data in L2 cache, the L2 controller determines what "way" holds the data in that set, and marks that "way" as most-recent. When allocating a new line in the cache, the L2 controller evicts the line in the set from the least-recently used "way" under the assumption that more-recently accessed data is more relevant. |

| When the CPU accesses data in L2 SRAM, either via program fetches or data accesses, the L2 cache is incorrectly updated by the L2 controller. The L2 controller updates the LRU as if the access was to "way 0" in the cache. This causes the LRU history to <i>not</i> reflect the actual sequence of accesses to L2 cache. As a result, the L2 may not choose the actual least-recently used line during an eviction.                                                                                       |

| Only CPU accesses to L2 RAM cause this update to LRU information in L2 cache. DMA accesses to L2 RAM <i>do not</i> trigger updates to the L2 LRU information.                                                                                                                                                                                                                                                                                                                                                 |

| Perform one of the following three workarounds:                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>Choose an L2 cache size that fits your cached working set. The advisory primarily impacts programs that are significantly larger than the L2 cache size.</li> </ul>                                                                                                                                                                                                                                                                                                                                  |

| • Explicitly remove cached contents from L2 when finished with them. The L2 cache allocates "invalid" lines within each set before consulting the LRU. Programs may do this using "block invalidate" or "block writeback-invalidate" commands in the L2 cache.                                                                                                                                                                                                                                                |

| • Lay out buffers in L2 RAM so they <i>do not</i> conflict with buffers or code held in L2 cache. L2 RAM addresses map onto L2 sets in the same manner as external memory addresses.                                                                                                                                                                                                                                                                                                                          |

| For more detailed information on the organization and manipulation of the L2 cache, see the <i>TMS320C64x DSP Two-Level Internal Memory Reference Guide</i> (literature number SPRU610).                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Advisory 2.0.2                                                                                                | L2 Cache: L2 Controller Incorrectly Updates LRU for Accesses in L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:                                                                                         | 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Details:                                                                                                      | The L2 cache implements a 4-way set-associative cache. The cache uses the "Least-Recently Used" (LRU) information to determine what "way" within each set is least recently used. When the CPU accesses data in L2 cache, the L2 controller determines what "way" holds the data in that set, and marks that "way" as most-recent. When allocating a new line in the cache, the L2 controller evicts the line in the set from the least-recently used "way" under the assumption that more-recently accessed data is more relevant. |

|                                                                                                               | For this advisory, CPU accesses which hit L2 cache <i>do not</i> correctly update the LRU information for the set accessed. Instead of storing the LRU information back to the set being accessed, the L2 controller stores the information to 3 adjacent sets.                                                                                                                                                                                                                                                                     |

|                                                                                                               | LRU information is stored in groups of 4 sets. The 3 adjacent sets affected by the current set are defined as follows:                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                               | • Group 1 contains sets 0, 1, 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                               | • Group 2 contains sets 4, 5, 6, 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                               | • Etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| For example, during an access to set 5, the L2 controller incorrectly stores the information to sets 4, 6, 7. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                               | As a result of this issue, repeated misses to the same set with no intervening accesses to adjacent sets will allocate from the same "way". This can make the L2 cache appear to "thrash". A series of misses to consecutive sets in L2 cache may appear to allocate with reduced associativity; that is, L2 could appear to behave as a 2-way or direct-mapped cache.                                                                                                                                                              |

| Workaround:                                                                                                   | Perform one of the following three workarounds:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                               | <ul> <li>Choose an L2 cache size that fits your cached working set. The advisory primarily impacts programs that are significantly larger than the L2 cache size.</li> </ul>                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                               | • Explicitly remove cached contents from L2 when finished with them. The L2 cache allocates "invalid" lines within each set before consulting the LRU. Programs may do this using "block invalidate" or "block writeback-invalidate" commands in the L2 cache.                                                                                                                                                                                                                                                                      |

|                                                                                                               | <ul> <li>Offset external buffers that are accessed as part of the same working set so that<br/>accesses to the buffers are at least 4 L2 sets apart (512 bytes). This will prevent the<br/>buffers from "thrashing" each other in L2 cache.</li> </ul>                                                                                                                                                                                                                                                                              |

|                                                                                                               | For more detailed information on the organization and manipulation of the L2 cache, see the <i>TMS320C64x DSP Two-Level Internal Memory Reference Guide</i> (literature number SPRU610).                                                                                                                                                                                                                                                                                                                                            |

| Advisory 2.0.3        | EMIF: PDT Transfers Fail When Acessing the Same SDRAM Page as Non-PDT Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | fected: 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Details:              | When PDT and non-PDT transfers occur to the same SDRAM page, PDTA, PDT, and PDTDIR may not be driven to their appropriate state. The incorrect behavior of these signals can result in PDT data corruption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Workaround:           | Place all PDT transfers, whether reads or writes, in a memory range that is an aliased version of the physical SDRAM. For example, if SDRAM is in CE0 and is 128 Mbytes (MB) in depth, then the functional addressable space is 0x8000 0000 through 0x87FF FFFF and all normal CPU and non-PDT DMA transfers should access this memory range. The "aliased" view of the SDRAM is at address 0x8800 0000 through 0x8FFF FFFF and must be used for all PDT transfers. Similarly, if SDRAM is 64 MB in depth, the functional addressable view is 0x8000 0000 through 0x83FF FFFF and the "aliased" view is 0x8400 0000 through 0x87FF FFFF. The aliased view accesses the same underlying physical address as the functional view. |  |  |

|                       | The address space for the "aliased" view can be created by bit-wise ORing the "logical address" (functional address) in use as follows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                       | • For 128 MB, OR with 0x0800 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                       | • For 64 MB, OR with 0x0400 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                       | • For 32 MB, OR with 0x0200 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                       | • For 16 MB, OR with 0x0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                       | This workaround is ONLY applicable if the CE space has less than or equal to 128 MB of SDRAM connected to it. If a CE space is full (maximum addressable space is 256 MB), then that CE space cannot support PDT transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| PCI: Slave Reads With a Long Latency Can Return Bad Data (C6415/C6416 Only)                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| When an external master attempts to read memory from the DSP, it is issued a "Retry". The PCI will then go prefetch a FIFO's worth (32 words) of data. If this data takes an exceptional long time to fetch (approximately 32K PCI cycles, ~1 ms @ 33-MHz PCI), the PCI port can mishandle the return data and "delete" the first word of a PCI frame. The data returned to th master is address-shifted by one 32-bit word. For example, if {0,1,2,3,4,} is expected and {1,2,3,4,5} is returned. |  |  |

| Data will only take that long to fetch if the access is to a very slow external memory, or there are large, slow DMAs using the same priority queue as PCI (which, by default, is medium). For performance reasons, the separation of DMA traffic is recommended.                                                                                                                                                                                                                                  |  |  |

| For more detailed information on the EDMA peripheral, EDMA performance, and EDMA performance data, see the following reference guide and application notes:                                                                                                                                                                                                                                                                                                                                        |  |  |

| • TMS320C6000 DSP Enhanced Direct Memory Access (EDMA) Controller Reference<br>Guide (literature number SPRU234)                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| • TMS320C64x EDMA Architecture Application Report (literature number SPRA994)                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| <ul> <li>TMS320C6000 EDMA IO Scheduling and Performance Application Report (literature number SPRAA00)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| <ul> <li>TMS320C64x EDMA Performance Data Application Report (literature number SPRAA02)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PCI slave reads that start in less than 32K PCI cycles will not return bad data.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Do not use PCI to directly read from exceptionally slow external memories.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Do not put any other DMA activity on the same priority level as PCI.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| If system considerations force a user to put other DMA activity on PCI's level, put only DMA traffic that will complete within the 32K PCI clock cycle limit.                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Advisory 2.0.5        | PCI Reads May Get Ahead of PCI Writes When PCI Exceeds the Transfer Request Limit<br>(C6415/C6416 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details:              | When the PCI port exceeds its allocation of EDMA Transfer Requests (TRs), it can re–order read and write memory transactions. This can cause PCI slave reads to return "stale" data.                                                                                                                                                                                                                                                                                                                                                             |

|                       | When the PCI port reaches its limit for the number of outstanding TRs, it must wait for previously issued TRs to complete. While the PCI port is waiting, any pending write data and/or read requests will be held pending in internal buffers. When a TR allocation is available, any pending read requests are serviced before any pending write data, regardless of the order in which the write data and read request were received. This can potentially allow the read request to get ahead of the write data, and return "stale" results. |

| Workaround:           | TI recommends that good EDMA resource allocation be used to prevent the problem. For detailed information on EDMA resource allocation, refer to the <i>TMS320C64x EDMA Architecture Application Report</i> (literature number SPRA994).                                                                                                                                                                                                                                                                                                          |

|                       | The following guidelines can help prevent PCI from running out of available TRs:                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | <ul> <li>Do not place large or slow transfers on EDMA priority levels at or above the PCI's<br/>priority level.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       | • Increase PCI's TR allocation limit. For detailed information, refer to the <i>TMS320C6000 DSP Peripheral Component Interconnect (PCI) Reference Guide</i> (literature number SPRU581).                                                                                                                                                                                                                                                                                                                                                         |

|                       | The following guidelines can ensure correct read data:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                       | • Do not read any of the previous 32 words written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Write 32 words of "dummy" data after writing "real" data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 3 Silicon Revision 1.1 Known Design Exceptions to Functional Specifications and Usage Notes

#### 3.1 Usage Notes for Silicon Revision 1.1

All usage notes for silicon revision 1.1 still apply and have been moved up to the Usage Notes for Silicon Revision 2.0 section of this document.

#### 3.2 Silicon Revision 1.1 Known Design Exceptions to Functional Specifications

| Advisory 1.1.1        | EMIF: CLKOUT6 may not be CPU/6 During Reset                                                                                                                                                                                                                                                                                             |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1.1 and earlier                                                                                                                                                                                                                                                                                                                         |

| Details:              | At power up, before the rising edge of RESET, there is a chance that CLKOUT6 will not be CPU/6. When this happens, the CLKOUT6 will be CPU/2 until the rising edge of RESET. Once the first rising edge of RESET is detected, CLKOUT6 will remain CPU/6 until power is removed from the device. (Internal reference number DSPvd03612). |

| Workaround:           | If correct CLKOUT6 is important to the system at all times, two resets can be performed on the DSP. The first will ensure a correct CLKOUT6 and the second can then be used for system reset activities.                                                                                                                                |

| Advisory 1.1.2        | PCI: Slave Writes With Null Data Phases Can Lock Up PCI (C6415/C6416 Only)                                                                                                                                                                                                                                                              |

| Revision(s) Affected: | 1.1 and earlier                                                                                                                                                                                                                                                                                                                         |

| Details: | When performing slave writes to the DSP, the PCI port is susceptible to lockup if a word is     |

|----------|-------------------------------------------------------------------------------------------------|

|          | written without any byte enables asserted. The PCI port will always disconnect a transfer when  |

|          | it detects a null data phase. If this null data phase coincides with a particular internal FIFO |

|          | state, then the PCI port will also disconnect all future accesses. (Internal reference number   |

|          | DSPvd03620).                                                                                    |

|          |                                                                                                 |

**Workaround**: When transferring data using slave writes to the DSP, ensure at least one byte is enabled in every data phase.

| Advisory 1.1.3        | PCI: Slave Writes Can Corrupt Data (C6415/C6416 Only)                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | 1.1 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Details:              | When performing slave writes to the DSP through the PCI port, it is possible for the data to be corrupted. If the end of the PCI frame coincides with a particular internal FIFO state, then the last word of the burst will overwrite the first word of the burst. The location in memory where the last word should have gone is left unmodified. Only slave writes that burst longer than four words are affected. (Internal reference number DSPvd03632). |  |  |

| Workaround:           | To completely avoid the data corruption, do not perform burst lengths of more than four words or adhere to all of the following guidelines:                                                                                                                                                                                                                                                                                                                   |  |  |

|                       | 1. Limit the PCI burst lengths to 9 words or less                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                       | <ol> <li>Operate the DSP at an 18.0 or 14.8 CPU-to-PCI clock frequency ratio only<br/>(e.g., 600-MHz or 490-MHz CPU for 33-MHz PCI)</li> </ol>                                                                                                                                                                                                                                                                                                                |  |  |

|                       | 3. Move the PCI to EDMA priority 0 and move all other EDMA requestors to other queues                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                       | 4. Perform slave writes to L2 SRAM destinations only                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                       | 5. Set EDMA_WEIGHT register in the L2 controller to x0000 0002                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                       | Following these guidelines ensures that the PCI peripheral and the EDMA servicing logic never align their signals in a way that causes the problematic FIFO state. In cases where the burst length size cannot be controlled, following all guidelines except #1 will minimize the chance of the data corruption.                                                                                                                                             |  |  |

| Advisory 1.1.4        | PCI: Slave Reads Without Any Byte Enables Issue Target Abort (C6415/C6416 Only)                                                                                                                                                                                                                     |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1.1 and earlier                                                                                                                                                                                                                                                                                     |

| Details:              | A slave read transaction that does not assert any byte enables during a data phase will cause<br>the PCI port to respond with a target abort. If a simple master attempts to repeat this<br>transaction until successful, the system will be deadlocked. (Internal reference number<br>DSPvd03632). |

| Workaround:           | When doing PCI Slave Reads to the DSP, ensure that at least one byte lane is enabled during every data phase.                                                                                                                                                                                       |

| Advisory 1.1.5        | PCI: Master Transaction Following an Abort Can Erroneously Set MASTEROK<br>(C6415/C6416 Only)                                                                                                                                                                                                               |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | 1.1 and earlier                                                                                                                                                                                                                                                                                             |  |  |

| Details:              | If an abort of any kind is received (Master abort, Target abort, or writing "0" to the START bits) and is followed by a master transaction, then the master transaction can set the MASTEROK interrupt bit (PCIIS.6) before the transfer has actually completed. (Internal Reference number DSPvd03633).    |  |  |

| Workaround:           | When processing a MASTEROK interrupt, check the START bits to ensure the transaction has actually completed.                                                                                                                                                                                                |  |  |

| Advisory 1.1.6        | PCI: An Abort Received During a Master Read Can Lock Up PCI (C6415/C6416 Only)                                                                                                                                                                                                                              |  |  |

| Revision(s) Affected: | 1.1 and earlier                                                                                                                                                                                                                                                                                             |  |  |

| Details:              | If an abort of any kind is received (Master abort, Target abort, or writing "0" to the START bits) while performing a master read, then the PCI port can be put into a state where no further transactions are possible. The PCI port disconnects all transactions. (Internal reference number DSPvd03434). |  |  |

| Workaround:           | If this PCI lock-up occurs, reset and reconfigure the PCI port.                                                                                                                                                                                                                                             |  |  |

| Advisory 1.1.7        | PCI: Do Not Write a "1" to the Cache Line Size Register (C6415/C6416 Only)                                                                                                                                                                                                                                  |  |  |

| Revision(s) Affected: | 1.1 and earlier                                                                                                                                                                                                                                                                                             |  |  |

| Details:              | If the Cache Line Size Configuration register contains the value of "1", the PCI port will not function correctly.                                                                                                                                                                                          |  |  |

| Workaround:           | Do not write a "1" to the Cache Line Size Configuration register.                                                                                                                                                                                                                                           |  |  |