# Technical Article Layout Matters: Solving Pinout Assignment Issues for DC/DC Converters in WCSP Packages

Eric Yao

The miniaturization trend in consumer electronics has taken hold for good. Consumers are demanding smaller electronics with better features: more flash capacity in solid-state drives, faster smartphones, more integrated communication modules, etc. To achieve this, engineers must look for increasingly power dense solutions. One challenge associated with achieving a high-power-density solution is finding small DC/DC converters with compact external components. When it comes to size, DC/DC converters in wafer chip-scale packages (WCSPs) are smaller than standard quad flat no-lead (QFN) or small-outline transistor (SOT) packages. WCSPs have also lower height than QFN or SOT packages, which can help engineers design not only smaller equipment but also one with a lower profile.

### The Trouble with Logic Signal Pins

Although DC/DC converters in WCSP have the size advantage, the pinout assignment of a typical WCSP might prevent engineers from choosing this package. Often, some logic signal pins (like the EN pin or the SDA and SCL pins of the I<sup>2</sup>C interface) sit in the middle of the package because other pins with higher priorities in silicon layout (like VIN, AVIN, AGND, PGND and the output sense pins) must connect to the signal traces directly. Because external components should be placed as close to these pins as possible, engineers have to insert small vias for the pins in the middle of the package to achieve proper signal routing during printed circuit board (PCB) layout.

In order to fit in more features (which equals more pins) in one device, engineers increasingly opt for a smaller WCSP pin pitch. While the 0.5-mm or 0.4-mm pitch was used in old devices, nowadays the 0.35-mm pitch is being adopted by many new devices in the market. Once the WCSP pin pitch is 0.35 mm, traditional PCB manufacturing prevents engineers from placing vias in the middle of the package. To address this issue, engineers have to either do away with vias altogether or use an advanced PCB assembly technology, which raises the cost of the overall solution. As a result, engineers have to choose between a larger solution size or a less competitive product.

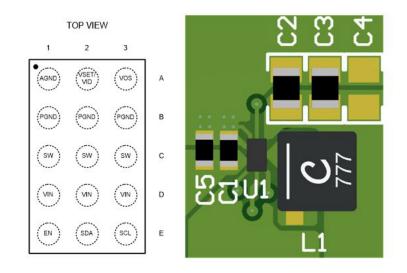

To address this problem, engineers should consider the pinout assignment when choosing the right buck converters in WSPC for their solutions. TI's TPS62866 is a 6-A synchronous step-down converter which measures only 1.05x1.75x0.5-mm in WCSP. For the same current level buck converters in QFN, the typical package size is 3x3x1-mm. Figure 1 shows the pinout assignment and typical PCB layout of the TPS62866.

1

#### Figure 1. Pinout of the TPS62866 With a Typical PCB Layout

The absence of logic pins in the middle of the integrated circuit means that engineers don't need special vias for PCB routing, even though the pin pitch is 0.35 mm. Such assignment makes it also possible to place all signal traces around the device for direct routing, further saving board space and allowing engineers to shrink the overall power supply solution, leaving more room for the features that consumers crave.

A reasonable pinout assignment is an important feature for DC/DC converters in WCSP packages. The TPS62866 provides a good pinout assignment and implements many features including I<sup>2</sup>C interface in a 1.05x1.75x0.5-mm, 0.35-mm pitch WCSP.

#### Additional Resources

- Read this application note to learn more about the die size BGA (DSBGA) wafer level chip scale package (WLCSP).

- Explore different methods of output-voltage adjustment for DC/DC converters.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated