# What You Need to Know about Transimpedance Amplifiers – Part 1

#### Samir Cherian

Transimpedance amplifiers (TIAs) act as front-end amplifiers for optical sensors such as photodiodes, converting the sensor's output current to a voltage. TIAs are conceptually simple: a feedback resistor ( $R_F$ ) across an operational amplifier (op amp) converts the current (I) to a voltage ( $V_{OUT}$ ) using Ohm's law,  $V_{OUT} = I \times R_F$ . In this series of blog posts, I will show you how to compensate a TIA and optimize its noise performance. For a quantitative analysis of a TIA's key parameters, such as bandwidth, stability and noise, please see the application note, ""Transimpedance Considerations for High-Speed Amplifiers."

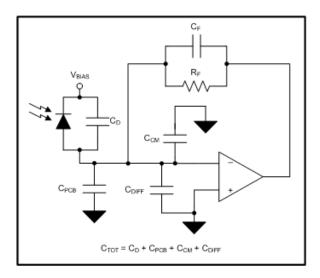

In a physical circuit, parasitic capacitances interact with the feedback resistor to create unwanted poles and zeros in the amplifier's loop-gain response. The most common sources of parasitic input and feedback capacitances are the photodiode capacitance ( $C_D$ ), the op amp's common-mode ( $C_{CM}$ ) and differential input capacitance ( $C_{DIFF}$ ), and the circuit-board capacitance ( $C_{PCB}$ ). The feedback resistor,  $R_F$  is not ideal and has a parasitic shunt capacitance that may be as large as 0.2pF. In high-speed TIA applications, these parasitic capacitances interact with each other and  $R_F$  to create a response that is not ideal. In this blog post, I will illustrate how to compensate a TIA.

Figure 1 shows a complete TIA circuit with parasitic-input and feedback-capacitance sources.

Figure 1. TIA Circuit Including Parasitic Capacitances

Three key factors determine the bandwidth of a TIA:

- Total input capacitance (C<sub>TOT</sub>).

- Desired transimpedance gain set by R<sub>F</sub>.

- The op amp's gain-bandwidth product (GBP): the higher the gain bandwidth, the higher the resulting closed-loop transimpedance bandwidth.

These three factors are interrelated: for a particular op amp, targeting the gain will set the maximum bandwidth; conversely, targeting the bandwidth will set the maximum gain.

### Single-pole Amplifier with No Parasitics

The first step of this analysis assumes an op amp with a single pole in the  $A_{OL}$  response and the specifications shown in Table 1.

**Table 1. TIA Specifications**

| Op amp open | -loop gain at DC, AoL(DC)     | 120dB    |

|-------------|-------------------------------|----------|

|             | Op amp GBP                    | 1GHz     |

| Feed        | lback resistor R <sub>F</sub> | 159.15kΩ |

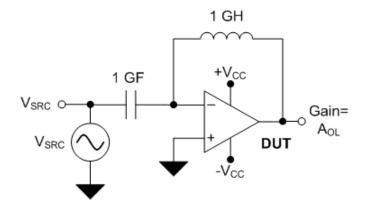

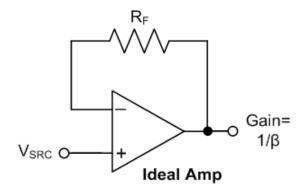

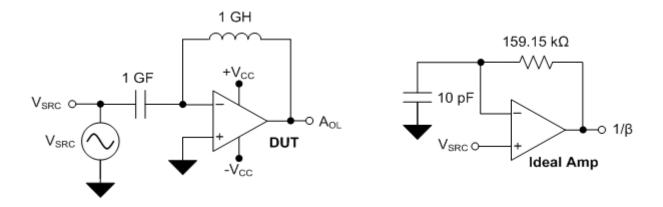

An amplifier's closed-loop stability is related to its phase margin,  $\Phi_M$ , which is determined by the loop-gain response defined as  $A_{OL} \times \beta$ , where  $\beta$  is the inverse of the noise gain. Figure 2 and Figure 3 show the TINA-TI<sup>TM</sup> circuits to determine the op amp's  $A_{OL}$  and noise gain, respectively. Figure 2 configures the device under test (DUT) in an open-loop configuration to derive its  $A_{OL}$ . Figure 3 uses an ideal op amp with the desired  $R_F$ ,  $C_F$  and  $C_{TOT}$  around it to extract the noise gain,  $1/\beta$ . Figure 3 excludes parasitic elements  $C_F$  and  $C_{TOT}$  – for now.

Figure 2. DUT Configuration to Determine aoL

Figure 3. Ideal Amplifier Configuration to Determine Noise Gain (1/B)

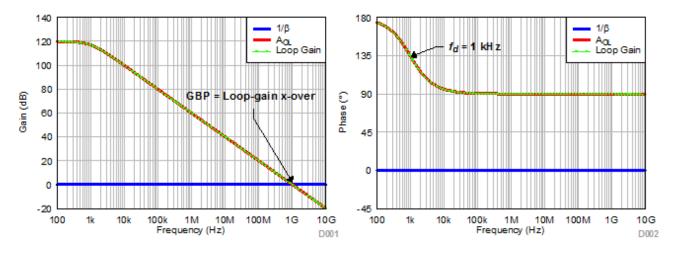

Figure 4 shows the simulated magnitude and phase of loop gain,  $A_{OL}$  and  $1/\beta$ . Since  $1/\beta$  is purely resistive, its response is flat across frequency. The loop gain is  $A_{OL}(dB) + \beta(dB) = A_{OL}(dB)$ , since the amplifier is in a unity-gain configuration as shown in Figure 3. The  $A_{OL}$  and loop-gain curves thus lie on top of each other, as shown in Figure 4. Since this is a single-pole system, the total phase shift due to the  $A_{OL}$  pole at  $f_d$  is 90°. The resulting  $\Phi_M$  is thus  $180^\circ$ - $90^\circ = 90^\circ$ , and the TIA is unconditionally stable.

Figure 4. Simulated Loop Gain, aoL And 1/B for an Ideal Case

### Effect of Input Capacitance (C<sub>TOT</sub>)

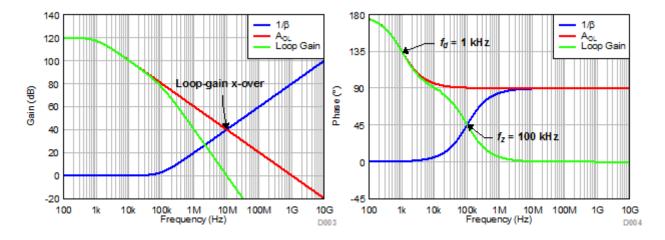

Let's analyze the effect of capacitance at the amplifier's inputs on loop-gain response. I'll assume a total effective input capacitance,  $C_{TOT}$ , of 10pF. The combination of  $C_{TOT}$  and  $R_F$  will create a zero in the 1/ $\beta$  curve at a frequency of  $f_z$  = 1/(2 $\pi R_F C_{TOT}$ ) = 100kHz. Figure 5 and Figure 6 show the circuit and resulting frequency response. The  $A_{OL}$  and 1/ $\beta$  curves intersect at 10MHz – the geometric mean of  $f_z$  (100kHz) and the GBP (1GHz). A zero in the 1/ $\beta$  curve becomes a pole in the  $\beta$  curve. The resulting loop gain will have a two-pole response, as shown in Figure 6.

The zero causes the magnitude of  $1/\beta$  to increase at 20dB/decade and intersect the  $A_{OL}$  curve at a 40dB/decade rate of closure (ROC), resulting in potential instability. The dominant  $A_{OL}$  pole at 1kHz results in a 90° phase shift in the loop gain. The zero frequency,  $f_z$ , at 100kHz adds another 90° phase shift. Its effect is complete by 1MHz. Since the loop-gain crossover occurs at only 10MHz, the total phase shift from  $f_d$  and  $f_z$  will be 180°, resulting in  $\Phi_M = 0$ ° and indicating that the TIA circuit is unstable.

Figure 5. Simulation Circuit Including a 10pF Input Capacitor

Figure 6. Simulated Loop Gain, a<sub>OL</sub> And (1/B) When Including the Effects of Input Capacitance

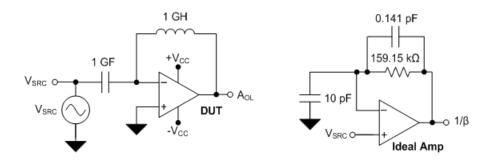

## Effect of Feedback Capacitance (C<sub>F</sub>)

To recover the phase loss due to  $f_z$ , insert a pole,  $f_{p1}$ , into the 1/ $\beta$  response by adding capacitor  $C_F$  in parallel with  $R_F$ .  $f_{p1}$  is located at 1/(2 $\pi R_F C_F$ ). To get a maximally flat, closed-loop Butterworth response ( $\Phi_M$  = 64°), calculate  $C_F$  using Equation Figure 7:

$$C_{F} = \frac{1}{2\pi(0.707)R_{F}f_{-2dR}}$$

(1)

## Figure 7. (1)

where f<sub>-3dB</sub> is the closed-loop bandwidth shown in Equation Figure 8:

$$f_{-3dB} = \sqrt{\frac{GBP}{2\pi R_F C_{TOT}}}$$

(2)

## Figure 7. (2)

The calculated  $C_F = 0.14pF$  and  $f_{-3dB} = 10MHz$ .  $f_z$  is located at ≈7MHz. The feedback capacitor includes the parasitic capacitances from the printed circuit board and  $R_F$ . In order to minimize  $C_{PCB}$ , remove the ground and power planes beneath the feedback trace between the amplifier's inverting input and output pin. Using resistors with small form factors, such as 0201 and 0402 reduces parasitic capacitance caused by the feedback components. Figure 9 and Figure 10 show the circuit and resulting frequency response.

Figure 7. Simulation Circuit, Including a 0.14pF Feedback Capacitor

Figure 8. Simulated Loop Gain, a<sub>OL</sub> And 1/B When Including the Effects of Input and Feedback Capacitance

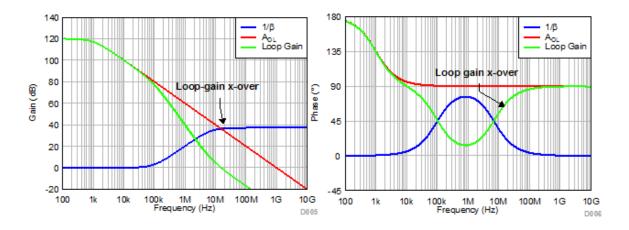

Using Bode-plot theory, Table 2 summarizes the points of inflection in the loop-gain response.

Table 2. Effect of Poles and Zeros on the Loop-gain Magnitude and Phase

| Cause                                                      | Effect on magnitude                                                                                                    | Effect on phase                                                                                                                             |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| A <sub>OL</sub> dominant<br>pole, f <sub>d</sub> =<br>1kHz | The magnitude decreases at -20dB/dec starting at 1kHz                                                                  | Starting at 180°, the phase decreases at -45°/dec from 100Hz-10kHz                                                                          |  |

| 1/β zero at fz<br>= 100kHz                                 | Combined with the effect of f <sub>d</sub> , the magnitude decreases at -40dB/dec starting at 100kHz                   | Starting at 90°, the phase decreases at -45°/dec from 10kHz-1MHz                                                                            |  |

| 1/β pole at f <sub>p1</sub><br>= 7MHz                      | Combined with the previous two effects,<br>the slope of the loop-gain magnitude<br>reduces from -40dB/dec to -20dB/dec | Starting at 700kHz, the phase increases at $45^{\circ}$ /dec and starts to recover the $\Phi_{\text{M}}$ . Its effect continues till 70MHz. |  |

The 1/β curve reaches a maximum value of

$$20log_{10}(1+\frac{10p\,F}{0.14pF}) \approx 37dB$$

. For a Butterworth response,  $1/\beta$

$$\frac{\text{GBP}}{\left(\text{C}_{\text{TOT}}/\text{C}_{\text{F}}\right)} \approx 14\text{MHz}$$

intersects AOI near its maximum value at a frequency

.  $f_d$  and  $f_z$  create a total phase

$$tan^{-1}\left(\frac{14MHz}{7MHz}\right) = 63.5^{\circ}$$

shift of 180°. The phase reclaimed by f<sub>p1</sub> is

, which is very close to the simulated 65°.

When designing a TIA, you must know the photodiode's capacitance, as this is usually fixed by the application. Given the photodiode capacitance, the next step is to select the correct amplifier for the application.

Choosing the right amplifier requires an understanding of the relationship between an amplifier's GBP, the desired transimpedance gain and closed-loop bandwidth, and the input and feedback capacitances. You can find an Excel calculator incorporating the equations and theory described in this post here. If you are designing a TIA, be sure to check the calculator out. It will save you a lot of time and manual calculations.

#### **Additional Resources**

- Download the application report, "Transimpedance Considerations for High-Speed Amplifiers," for a quantitative derivation of Equations Figure 7 and Figure 8 in this post.

- Get online support in the TI E2E™ Community Amplifier forums.

- Browse more than 40 training videos on op-amp topics like noise, bandwidth and stability.

- Learn more about selecting the correct amplifier in the application note, "Transimpedance Amplifiers (TIA): Choosing the Best Amplifier for the Job."

- Search TI high-speed op amps and find technical resources.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated