# Technical Article Selecting ESR for Linear Regulator Stability

Tim Reyes

Output stability is a key concern for any power-supply design. Given the simple nature of linear regulators (most of which have only three pins), it can be easy to forget its importance. While many techniques exist to ensure a stable output, the easiest and most cost-effective solution is to add or use the equivalent series resistance (ESR) of the output capacitor.

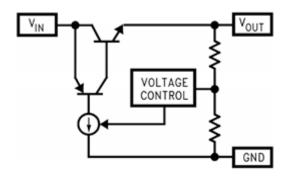

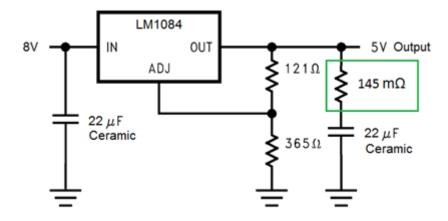

For demonstration purposes, let's use the LM1084 low dropout positive regulator with a 5V output. The LM1084 is capable of providing 5A of current to the load, which is useful when large current spikes may be present. It is also a quasi-LDO, meaning that the pass transistor is a single NPN transistor driven by a PNP transistor, as shown in Figure 1. Because of its internal structure, quasi-LDOs generally need some amount of ESR at the output capacitor to ensure stability.

Figure 1. Quasi-LDO Simplified Internal Schematic

Generally, the ESR of tantalum and electrolytic capacitors is enough to provide stability, but as designs become more space-constrained, ceramic capacitors are preferable due to their smaller size. Since ceramic capacitors have virtually no ESR, adding an external resistor in series mimics the behavior. In this blog, I'll use the LM1084 to demonstrate how to estimate the optimal ESR value at the output and test its effectiveness in the lab.

#### Methods for Testing Stability

One traditional method when testing for stability is to use a frequency response network analyzer, which injects a small sinusoidal signal into the feedback loop and measures the gain and phase response across frequency. It requires breaking the feedback loop, so you generally cannot test fixed-output regulators with the feedback loop built into the integrated circuit (IC). This method is more tedious to set up, requires extra lab equipment, and can result in errors if you don't take the proper precautions.

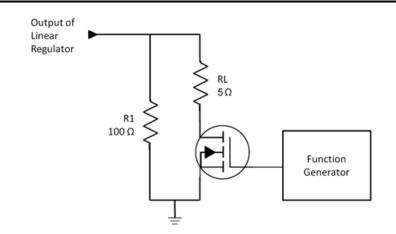

A simpler method is to perform a load-transient test and observe the ringing at the output. Figure 2 shows an example setup that can provide a 50mA to 1A load transient with a 5V regulator output. The function generator provides a square wave to the gate of the N-channel FET. When the N-channel FET is driven, the total load resistance is effectively  $5\Omega$ . When the NFET is not driven, the load resistance is  $100\Omega$ , which is just enough resistance to satisfy the minimum load requirement.

1

Figure 2. Load-transient Test Setup

### **Observing the Output Ringing**

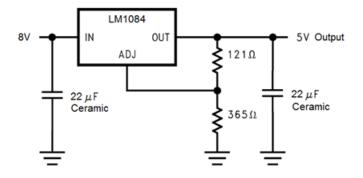

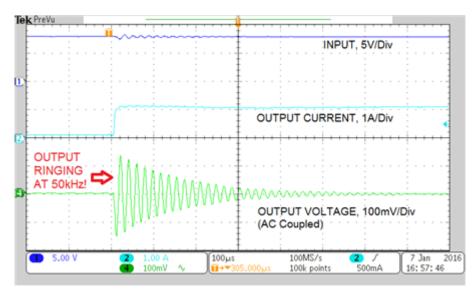

The ringing at the output during a load transient can help determine if the regulator is stable. Figure 3 shows the schematic of the LM1084 with a ceramic output capacitor and no external ESR added. Figure 4 shows its load-transient response. As shown in Figure 4, there is an excessive amount of ringing, which you can damp by adding some ESR to the output capacitor. But how much ESR should you add?

Figure 3. LM1084 Schematic – No ESR

Figure 4. Load-transient Response – No ESR

#### Calculating the ESR Value

You can determine the appropriate ESR value with Equation 1:

$$ESR(minimum) = \frac{1}{2^* \pi f_{oscillation} * C_{out}}$$

(1)

This equation will give you a minimum ESR that provides a zero at the output ringing, or oscillation, frequency. During a load-transient test, the output ringing frequency gives you a clue that the 0db crossing point is near that frequency, and therefore needs a bit of phase boost to dampen the output response. Providing a zero at that frequency will provide the phase boost you need. Let's do a calculation using the examples in Figure 3 and Figure 4.

The oscillation frequency in Figure 4 is about 50kHz and the output ceramic capacitor is  $22\mu$ F. Plugging those numbers into Equation 1 gives you a minimum ESR value of  $145m\Omega$ :

$$ESR(minimum) = \frac{1}{2^*\pi^*(50 \text{ kHz})^*(22\mu\text{F})} = 145\text{m}\Omega$$

(2)

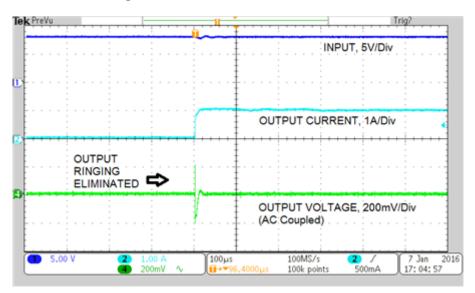

Now let's see the effect of adding  $145m\Omega$  of ESR to the output response during a load transient. Figure 5 shows the schematic with ESR added, while Figure 6 shows its load-transient response. Although the ringing was eliminated, the side effect is that the effective output capacitance diminishes with the addition of ESR, and the capacitor becomes just a bit more resistive. This means that the initial output dip is larger.

Figure 5. LM1084 Schematic – with ESR

In summary, you can dampen the output ringing produced by linear regulators by simply adding an external resistor, which is especially useful when designing with ceramic capacitors. The calculation is simple and requires minimal equipment to test and verify stability.

#### **Additional Resources**

- Read the "ESR, Stability, and the LDO Regulator" application note to understand why higher ESR capacitors are necessary, how to choose them, and how to determine whether or not the regulator is stable.

- Download the "Linear Regulators: Theory of Operation and Compensation" application note that discusses the operation and compensation of linear regulators.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated