## Technical Article Gate Drive Transformer vs. High/low Side Driver: a Detailed Implementation

Wei Zhang

My previous blog post discussed isolation requirements in a typical power-supply system and two popular gate driver implementation methods: a gate drive transformer and a high-/low-side gate driver. A high-/low-side driver, such as the 600V UCC27714, can save over 50% in PCB layout area and much more on component volume.

In this post, I will discuss more details about the actual implementation of the two methods, including their strengths and weaknesses.

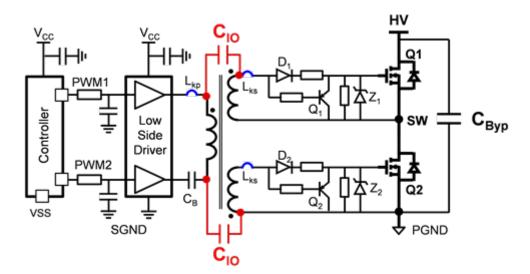

Figure 1 shows the actual implementation of a gate-drive transformer for a half-bridge MOSFET configuration. The additional components (compared to Figure 2a in my previous blog post) are necessary in order to have a clean and solid gate-drive signal on the MOSFETs. These additional components are:

- C<sub>B</sub>: a blocking capacitor to prevent gate drive transformer saturation.

- D<sub>1</sub>, D<sub>2</sub>: to prevent symmetrical negative-voltage bias and save gate drive loss.

- Q1, Q2: low-voltage P-MOSs or PNP transistor to enhance gate drive turnoff performance.

- Z<sub>1</sub>, Z<sub>2</sub>: Zener diodes to help protect the gate/source of the power MOSFET from overvoltage.

Obviously, additional components definitely increase gate drive transformer design complexity. Leakage inductances also hurt the performance of the gate drive transformer, including reduced peak gate drive current and large overshoot (caused by leakage inductance and MOSFET junction capacitances). Practically speaking,, increasing the peak-drive current necessitates increasing the core size and winding-wire thickness to facilitate higher driving speeds; the corresponding effect will be higher overshoot, however, since the leakage inductance stores higher energy. Bifilar winding of the gate-drive transformer could be helpful to minimize leakage inductance; however, the trade-off is increased primary-to-secondary winding coupled leakage capacitance,  $C_{IO}$ .  $C_{IO}$  is the one of the major parasitics that limits common-mode transient immunity (CMTI) performance (see my blog post, "48V systems: Driving power MOSFETS efficiently and robustly" for an explanation). In summary, it is really difficult to do a better trade-off given the above-mentioned factors.

1

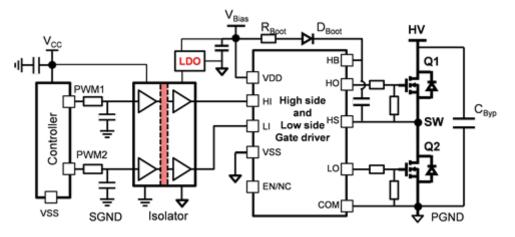

Figure 2 shows the actual implementation of the high-side and low-side gate-driver solution with digital isolator. Compared to Figure 2b in my last post, I added only a few major components:  $R_{Boot}$  and a 5V LDO, used to provide a power interface between  $V_{Bias}$ , 10 to 20V, and the isolator secondary side, which requires a 3 to 5V low voltage/power supply.

Because there is no transformer leakage inductance-related issue compared to a gate drive transformer, you can achieve better trade-offs among gate drive current, overshoot, CMTI, etc.

Figure 2. Actual Implementation of High-side and Low-side Gate Driver

Table 1 compares the two methods. The high-/low-side gate driver does "win" from the perspective of having fewer auxiliary components, small parasitic inductances/ $C_{IO}$ , smaller overshoot and PCB size, and flexible peak gate drive current. Concerning isolated bias power, as I mentioned before, the high-/low-side gate driver could take advantage of the existing offline isolated power-supply subsystem.

|                       | Gate-drive transformer   | High-/low-side gate<br>driver |

|-----------------------|--------------------------|-------------------------------|

| Isolated bias power   | No                       | Yes                           |

| Auxiliary components  | Many                     | Few                           |

| Parasitic inductances | Large                    | Small                         |

| CIO                   | High (≥10pF)             | Very low (<1pF)               |

| Overshoot (LLK)       | High                     | Low                           |

| PCB size              | Bulky                    | Very small                    |

| Peak drive current    | Limited (size trade-off) | Up to 10A                     |

Table 1. Comparison between Gate Drive Transformer and High-/Low-side Gate Driver

Stay tuned for the next installment of this series, when I will discuss the dynamic performance of each method.

## **Additional Resources**

2

- Catch up with part one: Gate drive transformer vs. high/low side driver: Which way to go for power supply design?

- Check out TI's new high-speed, 600V high-side low-side gate driver with 4A peak output.

- Design using the UCC27714

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated