Test Report: PMP23209

# Highly-Integrated, 12-V, 100-mA, Dual-Output, Isolated Bias Supply Reference Design

# **Description**

This reference design generates two isolated +12-V rails at 100 mA each from a 12-V<sub>DC</sub> input voltage. The design is optimized for a small footprint by employing a primary resonant LLC topology with a single UCC25800 driver and a transformer with functional insulation.

Top of Board (Angled)

#### **Features**

- Small size with simplified LLC design

- · High efficiency: 85% at full load

- Dual output for high-side (HS) and low-side (LS) drivers

- Employs small and low-cost transformer

#### **Applications**

- GaN, IGBT and SiC gate transformer driver bias supply

- Automotive onboard charger (OBC)

- Automotive DC/DC converter

- Automotive traction inverter and motor control

Top of Board

Applications www.

**Bottom of Board**

www.ti.com Design Information

# 1 Design Information

## 1.1 Voltage and Current Specifications

**Table 1-1. Voltage and Current Requirements**

| Parameter                                | Specifications |  |  |  |

|------------------------------------------|----------------|--|--|--|

| V <sub>IN</sub>                          | 12 V           |  |  |  |

| V <sub>OUT</sub> HS, V <sub>OUT</sub> LS | 12 V ±10%      |  |  |  |

| I <sub>OUT</sub> LS, I <sub>OUT</sub> HS | 100 mA         |  |  |  |

#### 1.2 Dimensions

The dimensions of the board are 32 mm  $\times$  27 mm  $\times$  6.5 mm.

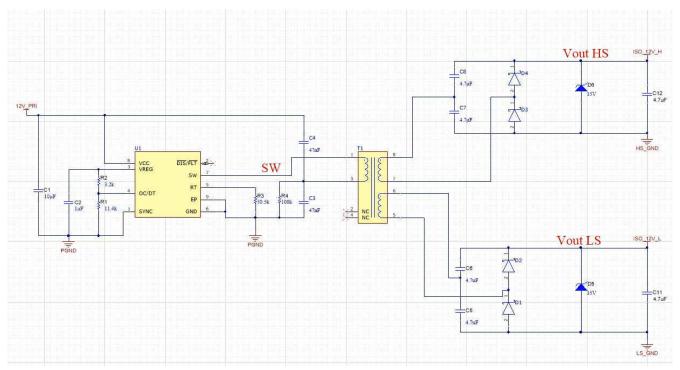

# 1.3 System Schematic

The following image illustrates the simplified schematic.

Figure 1-1. PMP23209 Schematic

# 2 Testing and Results

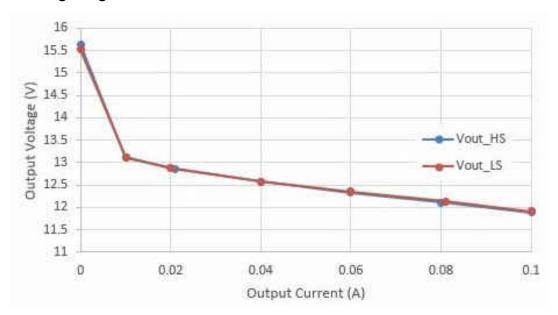

#### 2.1 Output Voltage Regulation

Figure 2-1. Open Loop Output Voltage vs Output Current

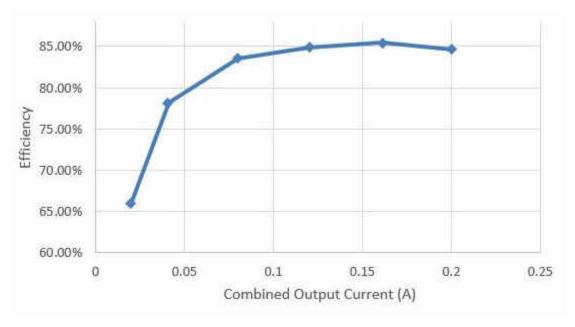

## 2.2 Efficiency Graphs

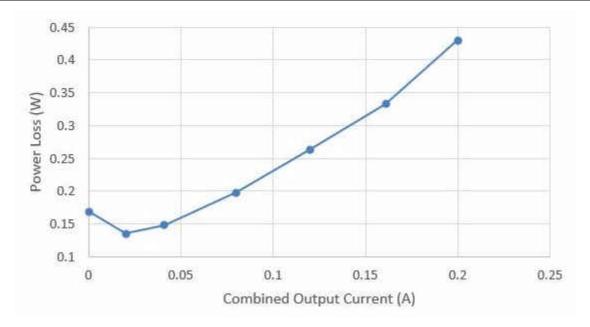

Efficiency and power loss are shown in the following figures.

Figure 2-2. Efficiency – HS and LS Rail Current Split Evenly

www.ti.com Testing and Results

Figure 2-3. Power Loss – HS and LS Rail Current Split Evenly

# 2.3 Efficiency Data

Efficiency data is shown in the following table.

| V <sub>IN</sub> (V) | I <sub>IN</sub> (A) | V <sub>OUT_HS</sub> (V) | I <sub>OUT_HS</sub> (A) | V <sub>OUT_LS</sub> (V) | I <sub>OUT_LS</sub> (A) | P <sub>IN</sub> (W) | P <sub>OUT</sub> (W) | P <sub>loss</sub> (W) | Efficiency |

|---------------------|---------------------|-------------------------|-------------------------|-------------------------|-------------------------|---------------------|----------------------|-----------------------|------------|

| 12.06               | 0.014               | 15.64                   | 0                       | 15.52                   | 0                       | 0.16884             | 0                    | 0.16884               | 0.00%      |

| 12.05               | 0.033               | 13.11                   | 0.010                   | 13.12                   | 0.010                   | 0.39765             | 0.2623               | 0.13535               | 65.96%     |

| 12.05               | 0.056               | 12.86                   | 0.021                   | 12.87                   | 0.020                   | 0.6748              | 0.52746              | 0.14734               | 78.17%     |

| 12.04               | 0.1                 | 12.58                   | 0.040                   | 12.58                   | 0.040                   | 1.204               | 1.0064               | 0.1976                | 83.59%     |

| 12.03               | 0.145               | 12.33                   | 0.060                   | 12.35                   | 0.060                   | 1.74435             | 1.4808               | 0.26355               | 84.89%     |

| 12.02               | 0.19                | 12.11                   | 0.080                   | 12.13                   | 0.081                   | 2.2838              | 1.95133              | 0.33247               | 85.44%     |

| 12.01               | 0.234               | 11.89                   | 0.100                   | 11.91                   | 0.100                   | 2.81034             | 2.38                 | 0.43034               | 84.69%     |

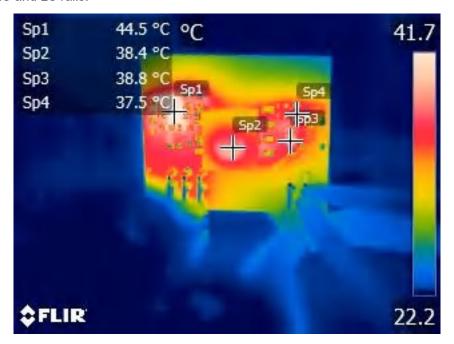

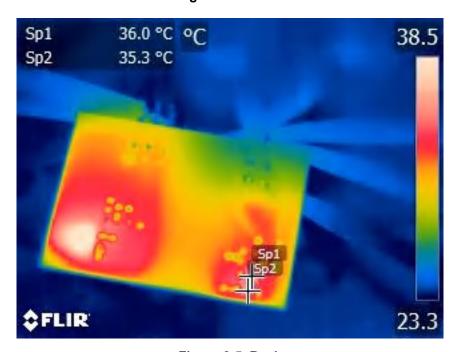

#### 2.4 Thermal Images

All images were captured with the DUT at 25°C ambient, after a 30-minute warm up. The output was loaded with 100 mA on both HS and LS rails.

Figure 2-4. Front

Figure 2-5. Back

www.ti.com Waveforms

# 3 Waveforms

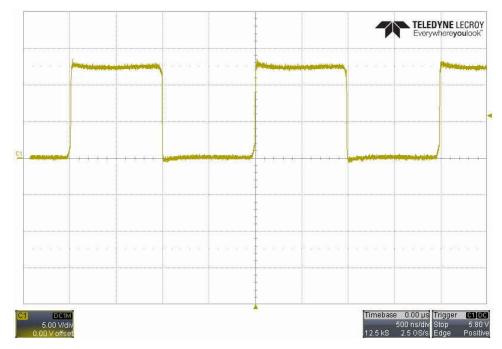

# 3.1 Switching

The following waveform is the switch node at 12-V input, and 100 mA on both HS and LS rails.

Figure 3-1. Switch Node: 12-V Input, 100 mA on Both HS and LS Rails

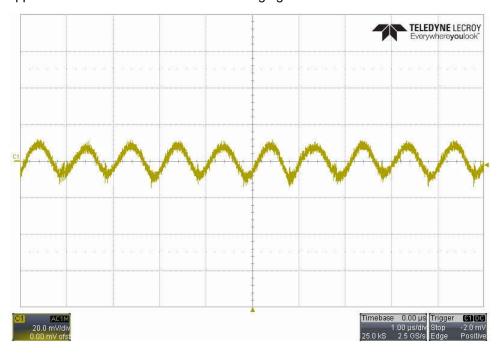

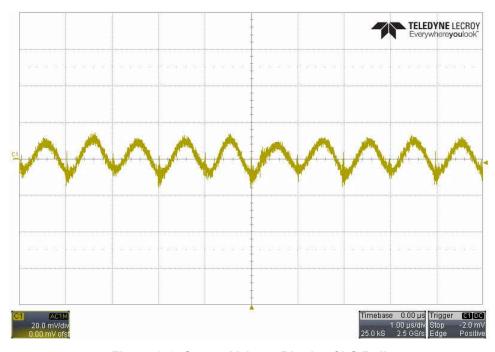

## 3.2 Output Voltage Ripple

Output voltage ripple waveforms are shown in the following figures.

Figure 3-2. Output Voltage Ripple of HS Rail

Figure 3-3. Output Voltage Ripple of LS Rail

8

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated