## TI Precision Designs: Reference Design Level Translation: Dual to Single Supply Amp, ±15V to 5V

# 🔱 Texas Instruments

### **TI Precision Designs**

TI Precision Designs are analog solutions created by TI's analog experts. Reference Designs offer the theory, component selection, and simulation of useful circuits. Circuit modifications that help to meet alternate design goals are also discussed.

### **Design Resources**

| Design Archive  |

|-----------------|

|                 |

| <u>TINA-TI™</u> |

| <u>OPA140</u>   |

| OPA188          |

| OPA827          |

| OPA211          |

| OPA376          |

| OPA313          |

| OPA333          |

| OPA350          |

All Design files SPICE Simulator Product Folder Product Folder Product Folder Product Folder Product Folder Product Folder Product Folder

## **Circuit Description**

Translating a +/-15V signal to a single supply 5V signal for use with an ADC is a common circuit requirement. This Dual Supply to Single Supply Amplifier translates a  $\pm$ 15V signal to a 0V to 5V signal. The output of this design will not be outside of 0-5V regardless of power supply sequencing or other transient conditions.

Ask The Analog Experts WEBENCH® Design Center TI Precision Designs Library

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments

#### 1 Design Summary

The design requirements are as follows:

- Supply Voltage: ±15 V, and +5V

- Input: ±10 V (linear range), ±15 V safe range

- Output: 0.2V to 4.8V

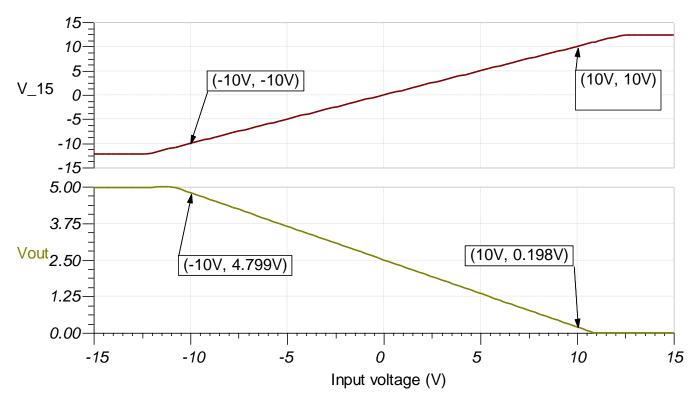

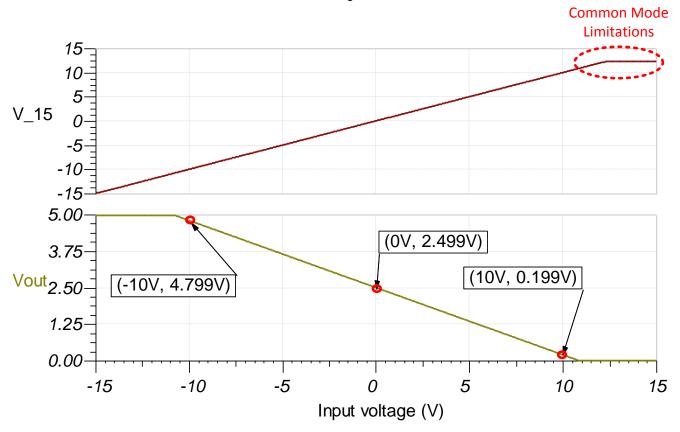

The design goals and performance are summarized in Table 1. Figure 1 depicts the measured transfer function of the design.

## Table 1. Comparison of Design Goals, Simulation, and Measured Performance

|                  | Goal | Simulated |

|------------------|------|-----------|

| Zero Scale Error | 0.5% | 0.196%    |

| Full-Scale Error | 0.5% | 0.32%     |

**Figure 1: Measured Transfer Function**

#### 2 Theory of Operation

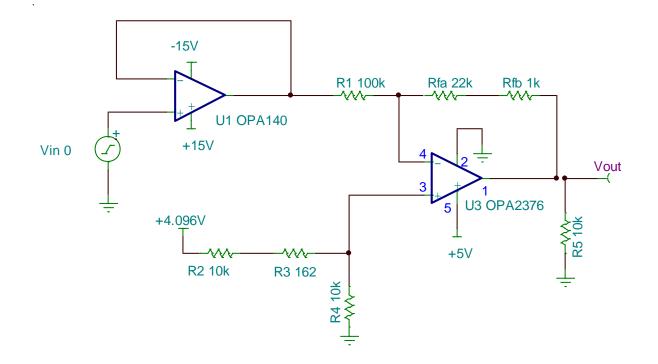

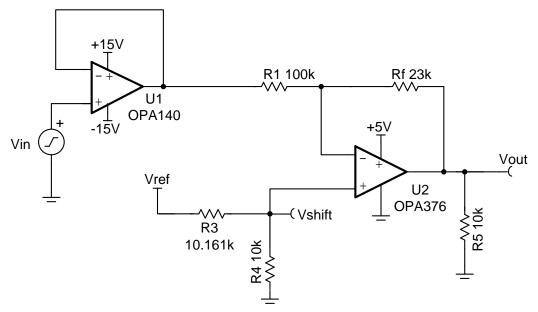

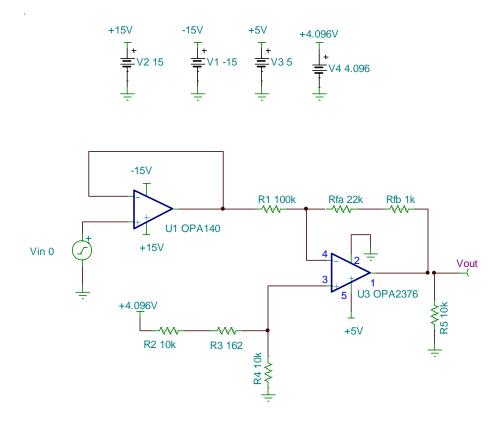

Figure 2 shows the full schematic for the design. The first stage (U1) is a  $\pm 15V$  amplifier with a  $\pm 10V$  linear output swing. In this example the first stage is shown as a buffer but other  $\pm 15V$  configurations can be used. For example an instrumentation amplifier with  $\pm 15V$  supplies could be used. The second stage translates the output of the first stage from  $\pm 15V$  to single supply 5V to be compatible with ADC inputs. The resistors in the second stage are scaled to attenuate the output from the first stage. A dc voltage (Vshift) is applied to the non-inverting input to shift the polarity of the signal to single supply. Table 2. Input to Output ScalingTable 2 shows the input to output scaling for the design in Figure 1.

Figure 2: Complete Circuit Schematic

|                  | Goal | Simulated |

|------------------|------|-----------|

| Zero-Scale Input | -10V | 0.2V      |

| Midscale Input   | 0    | 2.5V      |

| Full-Scale Input | +10V | 4.8V      |

Table 2. Input to Output Scaling

<u>/</u>->

#### 2.1 Design of Level Translation Amplifier

The transfer function for the circuit in Figure 2 is given in Equation (1). The equation can be derived using superposition. The first term (-Rf/R1) is derived by grounding the non-inverting input and considering the amplifier as an inverting amplifier. It controls the attenuation of the level translation amplifier. The second term (Rf/R1 + 1) is derived by grounding the inverting path, and considering the amplifier as a non-inverting amplifier. This term adds an offset to shift the signal from dual supply to single supply.

$$V_{\text{out}} = -\left(\frac{R_f}{R_1}\right)V_{\text{in}} + \left(\frac{R_f}{R_1} + 1\right)V_{\text{shift}}$$

<sup>(1)</sup>

The first step in the design procedure is to choose resistors that set the gain of the amplifier. The gain of the amplifier is the change in output divided by the change in input signal (Equation (2)). The gain is also given by Equation (3). Using Equation (2) and Equation (3) and selecting an arbitrary value for R1 it is possible to solve for Rf. Note that  $100k\Omega$  was selected for R1 to minimize loading of the amplifiers. A smaller value could be used to minimize noise. Equation (6) gives the solution for Rf and Equation (7) shows how the resistor can be created using two standard value resistors. Table 3 lists standard resistor values for your reference.

$$\frac{\Delta V_{\text{out}}}{\Delta V_{\text{in}}} = \frac{(V_{\text{out\_full}} - V_{\text{out\_zero}})}{(V_{\text{in\_full}} - V_{\text{in\_zero}})} = \frac{(4.8V - 0.2V)}{(10V - (-10V))} = 0.23$$

(2)

Where

V<sub>out full</sub> = Maximum linear output voltage.

V<sub>out zero</sub> = Minimum linear output voltage.

$V_{in\_full}$  = Maximum linear input. This input will produce  $V_{out\_zero.}$  Remember the amp is inverting.  $V_{in\_zero}$  = Maximum linear input. This input will produce  $V_{out\_full.}$  Remember the amp is inverting.

$$\frac{\Delta V_{\text{out}}}{\Delta V_{\text{in}}} = \frac{R_{\text{f}}}{R_{1}} \tag{3}$$

$$R_f = 0.23R_1 \tag{4}$$

Let

$$R_1 = 100 k\Omega$$

(5)

$$R_{f} = 0.23R_{1} = 23k\Omega \tag{6}$$

$$R_f = 22k\Omega + 1k\Omega$$

(for standard resistor values, Rfa & Rfb) (7)

The second step of the design procedure is to determine the voltage applied to the non-inverting input (Vshift) that will offset the signal from  $\pm 10V$  to single supply 5V. An easy way to do this is to consider the midscale signal (Vin = 0V). When Vin is 0V the transfer function from Equation (1) reduces to Equation (8).

$$V_{out} = \left(\frac{R_f}{R_1} + 1\right) V_{shift} \text{ for } V_{in} = 0V$$

(8)

$$V_{\rm shift} = \frac{V_{\rm out}}{\left(\frac{R_{\rm f}}{R_{\rm 1}} + 1\right)} = \frac{2.5V}{1.23} = 2.033V \tag{9}$$

The final step of the design procedure is to select values for the voltage divider to achieve the appropriate shift voltage. Equation (10) shows the relationship between Vref and Vshift. Vref is a reference output voltage. In this example, 4.096V is used as the reference voltage but any reference will work as long as Vref is greater than Vshift. The resistors (R2, R3, and R4) form a voltage divider. Two resistors were used (R2 and R3) to facilitate a more accurate resistor ratio using standard values. Equations (12), (13), and (14) show the math behind selecting the voltage divider resistors. Table 3 gives the standard resistor values.

$$V_{\text{shift}} = V_{\text{ref}} \frac{R_4}{(R_2 + R_2) + R_4}$$

(10)

$$\frac{V_{\text{shift}}}{V_{\text{ref}}} = \frac{2.033V}{4.096V} = \frac{R_4}{(R_2 + R_3) + R_4}$$

(11)

$$(R_2 + R_3) = 1.0161R_4 \tag{12}$$

Let

$$R_4 = 10k\Omega$$

,  $(R_2 + R_3) = 10.161k\Omega$  (13)

$R_2 = 10.0 k\Omega$  and  $R_3 = 161 \Omega$  (choose closest values from Table)

|      | Standard 1% Resistor Table |      |      |      |      |      |      |      |      |      |      |

|------|----------------------------|------|------|------|------|------|------|------|------|------|------|

| 10   | 10.2                       | 10.5 | 10.7 | 11   | 11.3 | 11.5 | 11.8 | 12.1 | 12.4 | 12.7 | 13   |

| 13.3 | 13.7                       | 14   | 14.3 | 14.7 | 15   | 15.4 | 15.8 | 16.2 | 16.5 | 16.9 | 17.4 |

| 17.8 | 18.2                       | 18.7 | 19.1 | 19.6 | 20   | 20.5 | 21   | 21.5 | 22.1 | 22.6 | 23.2 |

| 23.7 | 24.3                       | 24.9 | 25.5 | 26.1 | 26.7 | 27.4 | 28   | 28.7 | 29.4 | 30.1 | 30.9 |

| 31.6 | 32.4                       | 33.2 | 34   | 34.8 | 35.7 | 36.5 | 37.4 | 38.3 | 39.2 | 40.2 | 41.2 |

| 42.2 | 43.2                       | 44.2 | 45.3 | 46.4 | 47.5 | 48.7 | 49.9 | 51.1 | 52.3 | 53.6 | 54.9 |

| 56.2 | 57.6                       | 59   | 60.4 | 61.9 | 63.4 | 64.9 | 66.5 | 68.1 | 69.8 | 71.5 | 73.2 |

| 75   | 76.8                       | 78.7 | 80.6 | 82.5 | 84.5 | 86.6 | 88.7 | 90.9 | 93.1 | 95.3 | 97.6 |

Table 3: Standard Resistor Table

5

(10)

(14)

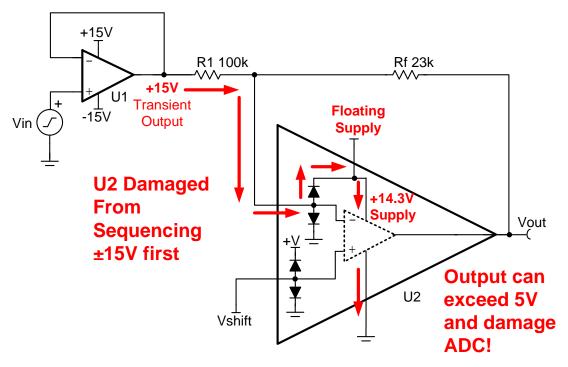

#### 2.2 Power Sequencing

This circuit is typically used to translate a  $\pm 15V$  signal to a single supply voltage that can be accepted by an ADC. A key goal of this type of circuit is to prevent the output from exceeding the input range of a single-supply ADC (0V to 5V in this example). Driving a 5V ADC or a 5V amplifier with a 15V signal will normally damage the ADC. Problems with this type circuit normally happen during power supply sequencing. The load resistance and the transient voltage suppressors prevent this design from outputting a transient signal outside of the ADC safe range.

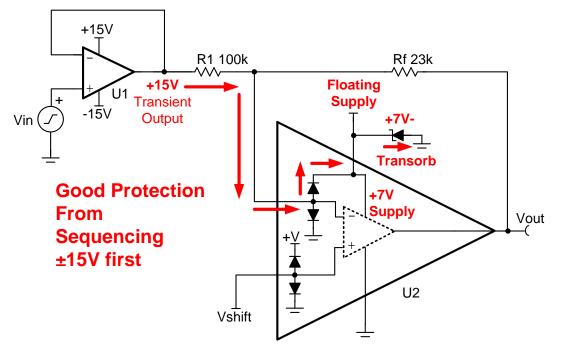

Figure 3 illustrates what can happen if you do not take any precautions to protect against power supply sequencing issues. In this example the  $\pm 15V$  supplies turn on first and the 5V supply is floating. Assuming the output of U1 is at 15V, current will flow through R1 and the input ESD diode on U2 which will raise the power supply of U2 to 14.3V. The absolute maximum voltage on U2 is 7V, so the device is damaged.

Figure 3: Damage: No Protection for Supply Sequencing

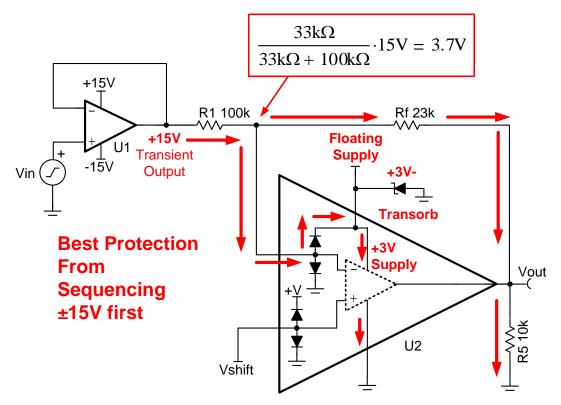

Figure 4 illustrates a circuit that uses a transient voltage suppressor (transorb) to prevent damage caused by power supply sequencing issues. A transorb operates like a zener diode but is optimized for fast response and capable of dissipating large energy transients for short times. In this example the  $\pm 15V$  supplies turn on first and the 5V supply is floating. Assuming the output of U1 is at 15V, current will flow through R1 and the input ESD diode on U2 which will raise the power supply of U2 until the transorb turns on. The transorb will limit the supply voltage to 7V which is within the absolute maximum voltage rating for U2, so the device is not damaged.

Figure 4: Good protection from Power Supply Sequencing Issues

7

Figure 5 illustrates a circuit that uses an output load as well as a transorb to prevent damage caused by power supply sequencing issues. The transorb acts as a secondary protection in this example. The primary protection is provided by the load resistor. In this example the ±15V supplies turn on first and the 5V supply is floating. The load resistor provides a path to ground for the output of U1. By considering the resistors R1, Rf, and R5 as a voltage divider you can calculate the voltage on U2's inverting input to be 3.7V. The 3.7V on the inverting input of U2 will cause current flow through the input ESD structure causing the power supply of U2 to rise to 3V. The 3V supply is well within the absolute maximum operating rating of U2. The 3V supply with not turn on the transorb. In this example, the transorb acts as a secondary protection for large transients. Thus, this circuit configuration offers two forms of protection from sequencing and general transients.

Figure 5: Best Protection from Power Supply Sequencing Issues

#### 3 Component Selection

#### 3.1 Op Amp Buffer Selection

The buffer could be any  $\pm 15V$  amplifier in need of level translation. In this example the OPA140 was selected for excellent dc precision, and good ac performance at an excellent price point. Other options are given in the modifications section (Section 5).

#### 3.2 Op Amp Level Translation Selection

The level translation amplifier (U2) was selected for excellent dc precision, and good ac performance at an excellent price point. In this example the OPA376 was selected for excellent dc precision, and good ac performance at an excellent price point. Other options are given in the modifications section (Section 5).

#### 3.3 Transient Voltage Suppressor Selection

The goal of the Transient Voltage Suppressor (TVS) is to keep the supply voltage lower than the op amps absolute maximum voltage rating (7V). Table 4 shows an example of a typical TVS specification. It is important to keep the "working peak voltage" equal to or greater than the supply voltage (5V in this example). The breakdown voltage should be less than the absolute maximum voltage. In this case the minimum breakdown voltage is 6V and the absolute maximum is 7V. Finally, pay attention to the leakage current. In some cases these diodes can have high leakage. In this example the leakage is 5µA which is small compared to the normal quiescent currents of the circuit.

|                                                         |                 |                  | CDSOD323-   |             |             |             |             |             |             |         |              |   |             |   |    |

|---------------------------------------------------------|-----------------|------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---------|--------------|---|-------------|---|----|

| Parameter                                               | Symbol          | Uni-<br>T03      | Bi-<br>T03C | Uni-<br>T05 | Bi-<br>T05C | Uni-<br>T08 | Bi-<br>T08C | Uni-<br>T12 | Bi-<br>T12C | Unit    |              |   |             |   |    |

| Minimum Breakdown Voltage @ 1 mA                        | V <sub>BR</sub> | 4.0              |             | 6.0         |             | 8.5         |             | 13.3        |             | V       |              |   |             |   |    |

| Working Peak Voltage                                    | V <sub>WM</sub> | 3.3              |             | 5.0         |             | 8.0         |             | 12.0        |             | V       |              |   |             |   |    |

| Maximum Clamping Voltage @ Ip = 1 A                     | V <sub>C</sub>  | 7.0              |             | 9.8         |             | 13.4        |             | 19.0        |             | V       |              |   |             |   |    |

| Typical Clamping Voltage<br>@ 8/20 μs @ Ι <sub>ΡΡ</sub> | V <sub>C</sub>  | 19.0 V<br>@ 20 A |             |             |             |             |             |             | 3 V<br>17 A |         | .5 V<br>17 A |   | 3 V<br>11 A | V |    |

| Maximum Leakage Current @ V <sub>WM</sub>               | ID              | 5                |             | 5           |             | 5           |             | 5 5         |             | 5 5 2 1 |              | 2 |             | 1 | μA |

| Typical Capacitance @ 0 V, 1 MHz                        | CJ              |                  |             |             | (           | 3           |             |             |             | pF      |              |   |             |   |    |

#### Table 4: Selecting the Transient Voltage Suppressor

### 3.4 Passive Component Selection

The resistor tolerance and drift are the primary cause of full-scale and zero-scale error in this design. In this example, 0.1% 20ppm/C resistors are used to achieve highest accuracy for a reasonable cost target. Typical 0.1% 20ppm/C resistors cost \$0.05 USD. Thus, the total cost of resistors is about \$0.35 where as the cost of the active components is \$2.2 USD. Choosing resistors that are more accurate than 0.1% generally costs significantly more and reduces availability. In some cases this design uses two resistors in series to achieve an accurate transfer function where standard values are not available.

9

## 4 Simulation

The TINA-TI<sup>TM</sup> schematic shown in Figure 6 includes the circuit values obtained in the design process.

Figure 6: TINA-TI<sup>™</sup> Schematic

### 4.1 Transfer Function

The result of the dc transfer function is shown in Figure 6.

Figure 7: Simulated Transfer Function

11

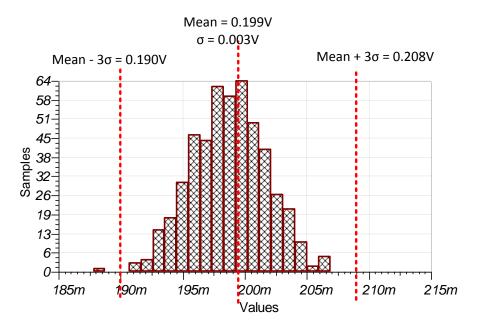

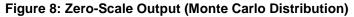

## 4.2 Monte Carlo Analysis Full-Scale & and Zero-Scale Error

Figure 8 and Figure 9 show the results of a Monte Carlo analysis for the Zero-Scale Output and the Full-Scale Output. This error is dominated by resistor tolerance. In this example the tolerance was set to 0.1%.

Figure 9: Full-Scale Output (Monte Carlo Distribution)

Equations (16) and (15) illustrate the calculation for zero-scale error and full-scale error using the statistical results from the simulation. Since the mean value in the distribution was approximately equal to the targeted performance the error is taken as plus or minus three standard deviations ( $\pm 3\sigma$ ). Based on probability theory, 99.7% of all devices should be within these error bands. This analysis only looks at resistor variation, because in this case resistor variation will be the dominant error source.

Zero Scale Error (%) =

$$\frac{\pm 3\sigma}{(V_{out\_full} - V_{out\_zero})} = \frac{\pm 0.009V}{(4.8V - 0.2V)} * 100\% = 0.196\%$$

of full scale (15)

Full Scale Error (%) =

$$\frac{\pm 3\sigma}{(V_{out\_full} - V_{out\_zero})} = \frac{\pm 0.015V}{(4.8V - 0.2V)} * 100\% = 0.32\%$$

of full scale (16)

#### 4.3 Simulated Results Summary

Table 5 summarizes the simulated performance of the design.

#### **Table 5: Summary of Simulated Results**

|                  | Goal | Simulated |

|------------------|------|-----------|

| Zero-Scale Error | 0.5% | 0.196%    |

| Full-Scale Error | 0.5% | 0.32%     |

#### 5 **Modifications**

The method described Section 2.1 can be used for different supply voltages and different reference voltages. For example, the same method could be used to translate a ±15V amplifier to a single supply 3V amplifier. Also, any reference voltage can be used. Different amplifiers can be selected based on your requirements. Table 6 and Table 7 provide examples of different amplifiers that can be used to achieve different design objectives.

| Output<br>Amplifier | Design Objective                   | Vos<br>uV | Vos Drift<br>uV/degC | lq<br>uA | Voltage<br>Noise<br>nV/√Hz | GBW<br>MHz | SR<br>V/uS | Approx.<br>Price<br>US\$ / 1ku |

|---------------------|------------------------------------|-----------|----------------------|----------|----------------------------|------------|------------|--------------------------------|

| OPA140              | Wide Band, Low Noise, DC Precision | 30        | 0.35                 | 1800     | 8                          | 11         | 20         | 1.55                           |

| OPA188              | DC Precision, Low Noise, Low Iq    | 6         | 0.03                 | 450      | 8.8                        | 2          | 0.8        | 0.8                            |

| OPA827              | Wide Band, Low Noise, DC Precision | 75        | 0.1                  | 4800     | 4                          | 22         | 28         | 3.75                           |

| OPA211              | Wide Band, Low Noise, DC Precision | 30        | 0.35                 | 3600     | 1.1                        | 80         | 27         | 3.45                           |

#### Table 6. Brief Comparison of ±15V Supply Amplifiers

| Table 7. Brief Comparison of 5V Supply Amplifiers |                                    |           |                      |          |                            |           |            |                                |

|---------------------------------------------------|------------------------------------|-----------|----------------------|----------|----------------------------|-----------|------------|--------------------------------|

| Output<br>Amplifier                               | Design Objective                   | Vos<br>uV | Vos Drift<br>uV/degC | lq<br>uA | Voltage<br>Noise<br>nV/√Hz | BW<br>MHz | SR<br>V/uS | Approx.<br>Price<br>US\$ / 1ku |

| OPA376                                            | Wide Band, Low Noise, DC Precision | 5         | 0.26                 | 760      | 7.5                        | 5.5       | 2          | 0.65                           |

| OPA313                                            | Low Noise, Low Iq                  | 500       | 2                    | 50       | 25                         | 1         | 0.5        | 0.3                            |

| OPA333                                            | DC Precision, Low Iq               | 2         | 0.02                 | 17       | 50                         | 350       | 0.16       | 0.95                           |

| OPA350                                            | Wide Band, Low Noise, DC Precision | 150       | 4                    | 5200     | 7                          | 38        | 22         | 1.15                           |

### .....

#### 6 About the Author

Arthur Kay is an applications engineering manager at TI where he specializes in the support of amplifiers, references, and mixed signal devices. Arthur focuses a good deal on industrial applications such as bridge sensor signal conditioning. Arthur has published a book and an article series on amplifier noise. Arthur received his MSEE from Georgia Institute of Technology, and BSEE from Cleveland State University.

#### 7 Acknowledgements & References

#### 7.1 Acknowledgements

The author wishes to acknowledge Collin Wells, Tim Green, and Marek Lis for technical contributions to this design.

#### 7.2 References

1. Rfcafe.com, Standard Resistor Table: <u>http://www.rfcafe.com/references/electrical/resistor-values.htm</u>

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated