# UCC24630 Secondary-Side Synchronous Rectifier Controller Diode Replacement Demonstration Board PMP11216

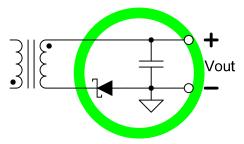

This test report demonstrates the efficiency improvements gained by synchronous rectification compared with diode rectification in 5V to 24V flyback output circuits. Results shown are for demonstration purposes only and thermal performance is not guaranteed. Maximum reverse blocking voltage, including spikes, must be less than 100V peak using the MOSFET specified. Higher voltage applications can be used if the MOSFET is replaced with a properly rated device. The illustration shown is for the existing diode anode connected to GND (refer to Figure 1). Use with any other diode connection arrangement would require a different IC bias arrangement.

Figure 1. Diode that was replaced w located such that its anode is connected to GND; otherwise, additional circuitry would have been required.

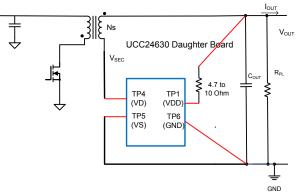

To install the demonstration board on an existing design, the board was connected in parallel with the existing diode. This is recommended until proper SR timing is verified. Once correct SR operation is verified, the diode can be removed. Tthe VS pin of the board was connected to the anode pad of the host circuit, and the VD pin of the board was connected to the cathode pad of the host circuit. The VCC terminal was connected to the output, and the GND terminal was connected to the converter output ground with a short piece of wire. Connecting VCC and GND at a low noise connection, such as across a filter capacitor (refer to Figure 2) is recommended to reduce noise.

Figure 2. Demonstration card connection to existing circuit shown

# PHOTO OF THE PROTOTYPE:

Figure 3. Front image of tested board

Figure 4. Back image of tested board

The reference design board allowed for an alternate D-Pak MOSFET package to be mounted on the back side to increase the thermal dissipation capability of the board for a higher-power applications. Forced airflow from a fan could also help extend the power level to be evaluated. The board was designed to test either the D-Pak (Q2) or SON package (Q1).

## **Detailed Component Selection**

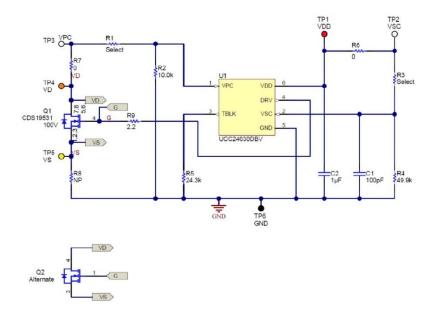

Figure 5 PMP11216 Schematic

The resistor dividers for the SR VDS sense and the Vout sense were determined for the application.

The resistor value of  $24.3k\Omega$  on the TBLK pin should be confirmed is correct for the application. The SR Demonstration Board is pre-programmed for a VPC Blanking Time of 340ns with R5=24.3k $\Omega$ .

The blanking time was determined based on the converter minimum primary on time of 470ns. The blanking time should be selected to be 120ns shorter than the minimum primary on time.

Determining the values for R1, R3, and R5 is a simple process.

Determine R1 value based on operating range of SR VDS voltage and Vout.

$\label{eq:VPC_divider: Calculate R1 Value} \begin{array}{l} \text{VPC divider: Calculate R1 Value}. \ \text{R2 is set at 10k Ohm.} \\ \text{*}V_{\text{IN(min)}} \text{ is bulk capacitor minimum} \\ \text{*}V_{\text{OUT(min)}} \text{ is output min operating voltage} \\ \text{*}V_{\text{VPC}\_\text{EN}} \text{ is 0.44V} \\ \text{*}N_{\text{PS}} \text{ is transformer primary to secondary turns ratio.} \end{array}$

$$R1 = \frac{\left[\left(\frac{V_{IN(\min)}}{N_{PS}} + V_{OUT(\min)}\right) - V_{VPC} - EN \times 1.1\right] \times R2}{V_{VPC} - EN \times 1.1}$$

### **Detailed Component Selection (continued)**

VSC divider: Calculate R3 Value. R4 is set at 49.9K.

Calculated R3 value results in 10% margin SR on time for initial power up (early turn off). \*RatioVPC\_VSC is 4.15

$$R3 = \left[ \left( \frac{\frac{R1 + R2}{R2}}{\frac{R1}{Ratio \, vPc \, vsc \, \times \, 1.1}} \right) - 1 \right] \times R4$$

TBLK resistor value: Confirm R5 value of 24.3K. Set tVPC\_BLK to be ~100ns less than expected converter minimum primary on time.

$$R5 = \frac{tv_{PC-BLK} - 100ns}{18\,pF}$$

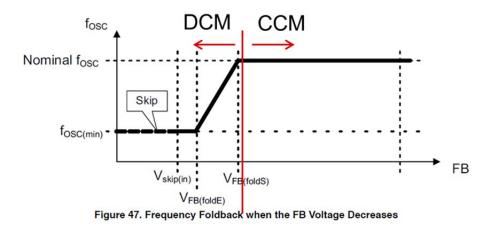

### **Use in CCM Operation**

The UCC24630 SR controller is compatible with flyback converters operating in CCM with primary controllers that are fixed frequency at high load conditions. For the CCM dead time control reliable operation, the converter should be operating in fixed frequency mode at any line and load condition that results in CCM operation. Refer to typical primary controller control law below.

Figure 6. Typical Fixed Frequency Controller Control Law

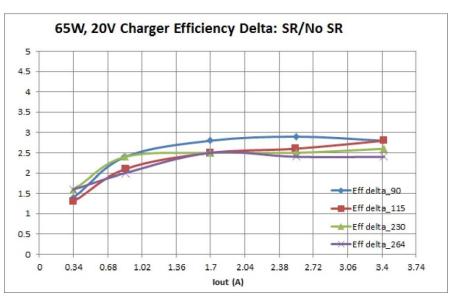

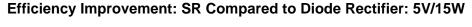

Efficiency Improvement: SR Compared to Diode Rectifier: 20V/65W

Figure 7. Efficiency improvement with SR over line and 10% to 100% load.

PMP11216 SR Daughter card with CSD19531 MOSFET Vs SSP5P10, schottky rectifier diode.

PMP11216 SR Daughter card with CSD18503 MOSFET Vs B540C-13 schottky rectifier diode.

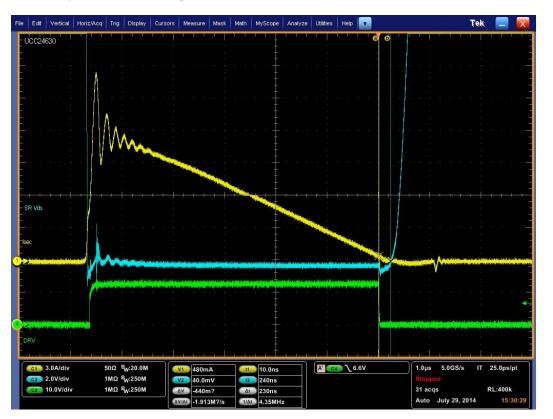

#### Typical SR Timing in 20V/65W Converter at Full Load

Figure 9. SR VDS, Isec, and SR Gate Drive at 115V, Full Load

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated