# PMP10117RevC Test Results

| 1 |                 | St                              | tartup                                                     | 2  |  |

|---|-----------------|---------------------------------|------------------------------------------------------------|----|--|

| 2 |                 | Sh                              | hutdown                                                    | 2  |  |

| 3 |                 | Ef                              | fficiency                                                  | 3  |  |

| 4 | Load Regulation |                                 |                                                            |    |  |

| 5 | Ripple Voltage  |                                 |                                                            |    |  |

| 6 |                 | Control Loop Frequency Response |                                                            |    |  |

| 7 |                 | Load Transients                 |                                                            |    |  |

| 8 |                 | M                               | liscellaneous Waveforms                                    | 8  |  |

|   | 8.              | 1                               | Switch node (LS-FET Q1)                                    | 8  |  |

|   | 8.              | 2                               | Gate Q1 (LS-FET)                                           | 9  |  |

|   | 8.              | 3                               | Drain-Source Voltage of the High Side MOSFET               | 10 |  |

|   | 8.              | 4                               | Gate Q2 High Side MOSFET (gate-switchnode)                 | 11 |  |

| 9 |                 | Th                              | hermal Image                                               | 12 |  |

| 1 | 0               |                                 | Appendix, added input filter to attenuate reflected ripple | 13 |  |

Topology: Device: Buck

TPS40170 "deep impact"

All measurements have been performed at 48V input voltage and 9A output if not otherwise mentioned;

RevC: added input filter w/ WE 8070 series, # 744.334.0150, 1.5uH / 4.4milliOhms, 16.5Arms / 18.5Asat, 18.4 x 7.9 x 7.2mm

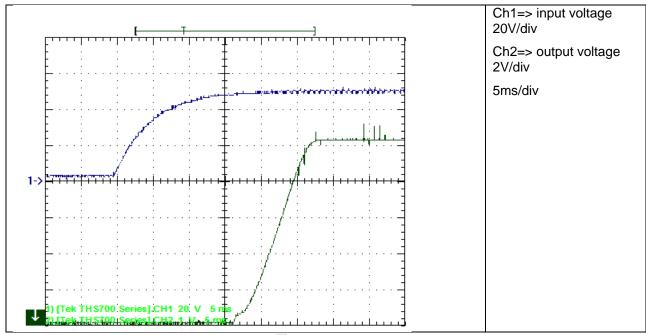

### 1 Startup

The startup waveform is shown in the Figure 1. The input voltage was set at 48V, with 9A load at the output. (Power supply 6554A was switched on)

#### Figure 1

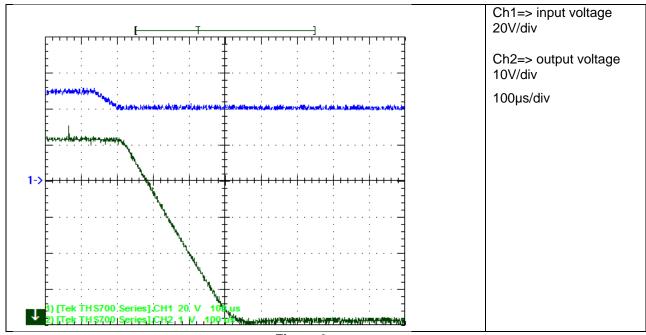

#### 2 Shutdown

The shutdown waveform is shown in the **Error! Reference source not found.**. The input voltage was set at 48V, with 9A load on the output. (Power Supply was disconnected)

Figure 2

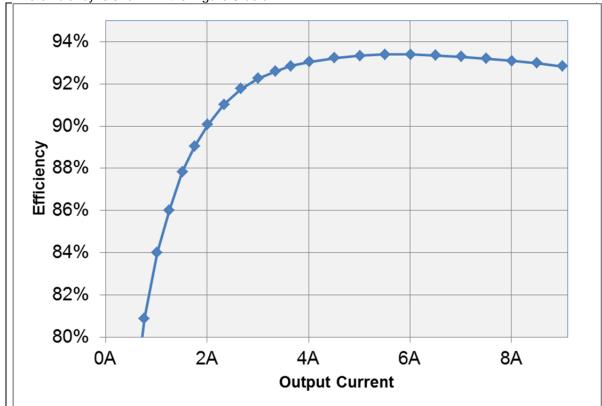

# 3 Efficiency

Figure 3

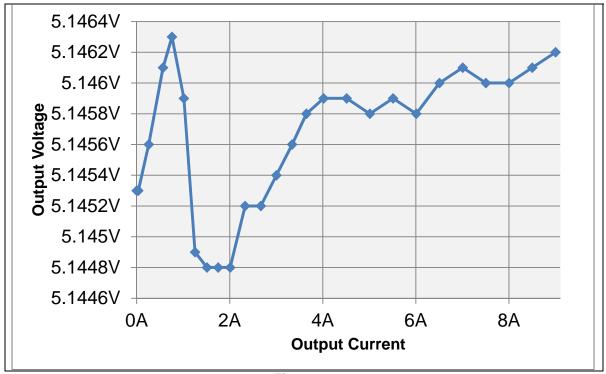

### 4 Load Regulation

The load regulation is shown in the Figure 4 below, regulation <2mV

Figure 4

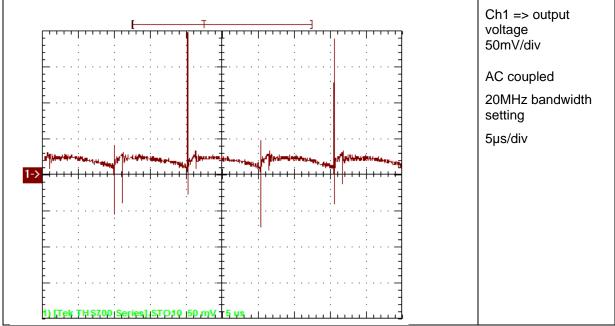

## 5 Ripple Voltage

The output ripple voltage is shown in Figure 5.

Figure 5

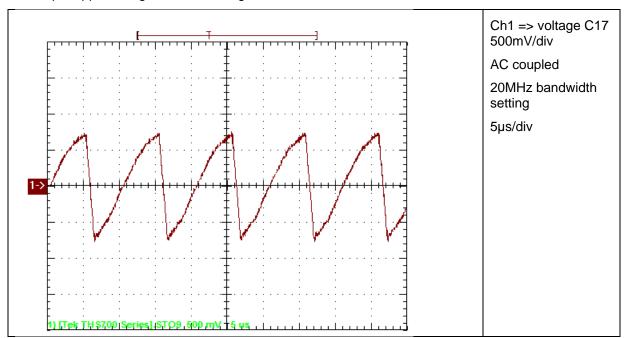

The input ripple voltage is shown in Figure 6.

Figure 6

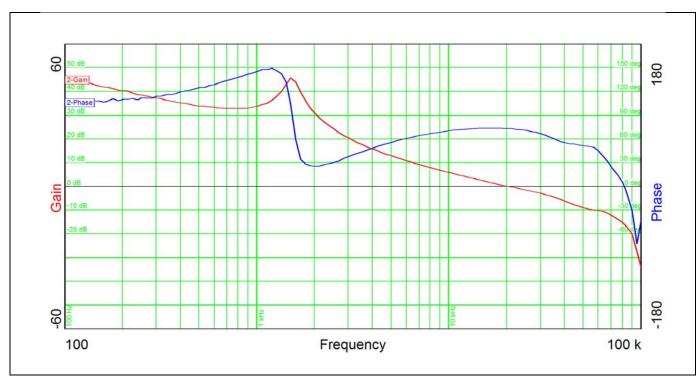

# 6 Control Loop Frequency Response

Figure 7 shows the loop response with 9A load (6060B).

Figure 7

Table 1 summarizes the results from Figure 7

| Bandwidth (kHz)  | 20.4  |

|------------------|-------|

| Phasemargin      | 73°   |

| slope            |       |

| (20dB/decade)    | -0.96 |

|                  |       |

| gain margin (dB) | -16   |

| slope            |       |

| (20dB/decade)    | -3.7  |

| freq (kHz)       | 81.7  |

Table 1

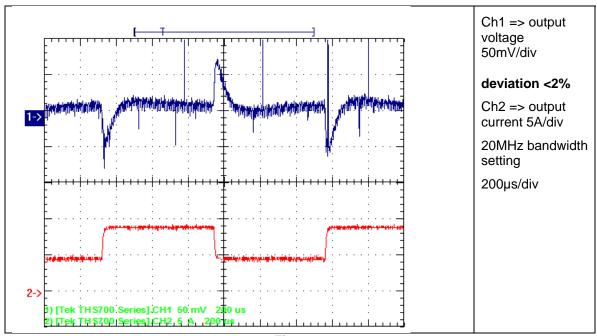

#### 7 Load Transients

The Figure 8 shows the response to load transients. The load is switching from 4.5A to 9A.with 800Hz frequency (6060B load).

Figure 8

### 8 Miscellaneous Waveforms

### 8.1 Switch node (LS-FET Q1)

With input voltage set to 48V and 9A lout results in the waveform shown in Figure 9

Figure 9

### 8.2 Gate Q1 (LS-FET)

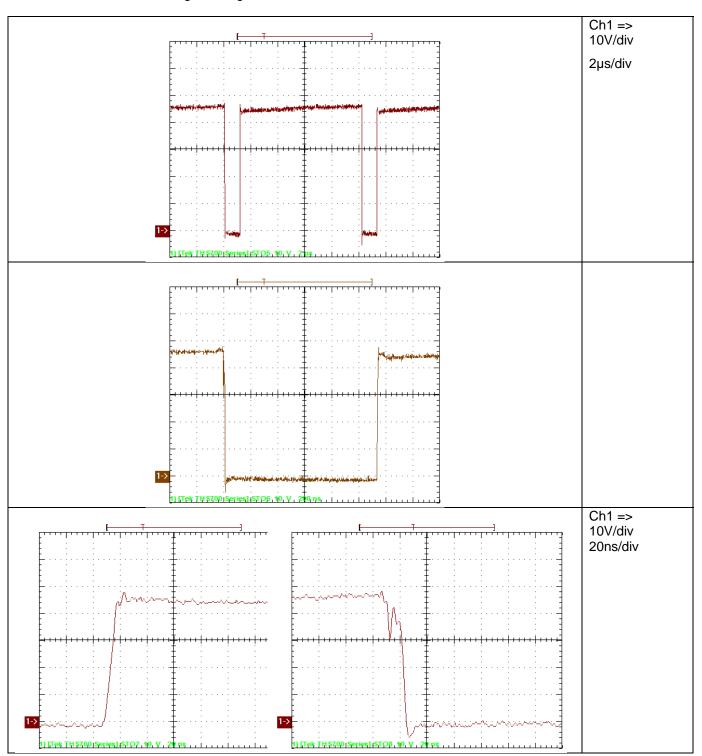

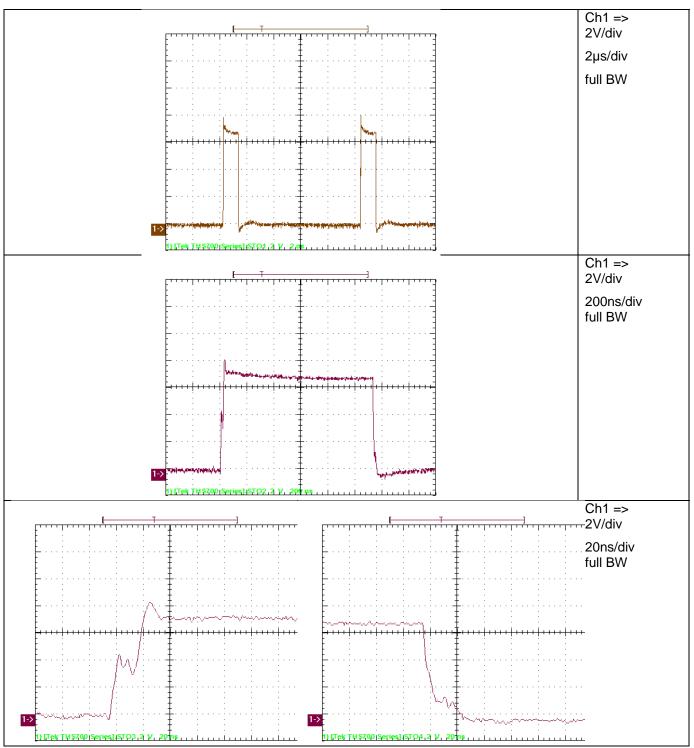

Figure 10 shows the waveform across gate Q1 to GND

Figure 10

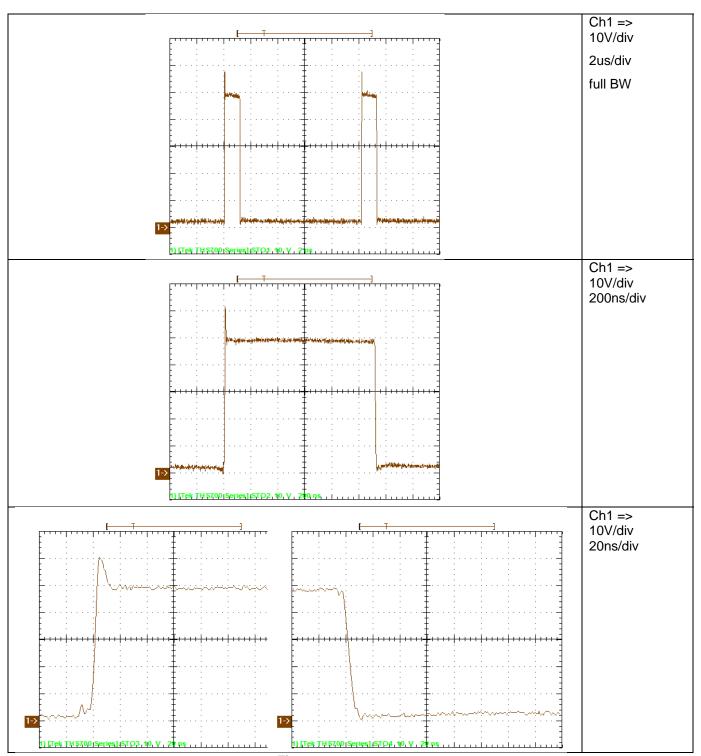

#### 8.3 Drain-Source Voltage of the High Side MOSFET

Measured with reference to VIN and waveform is displayed inverted. The waveform is shown in Figure 11, gate vs. switchnode:

Figure 11

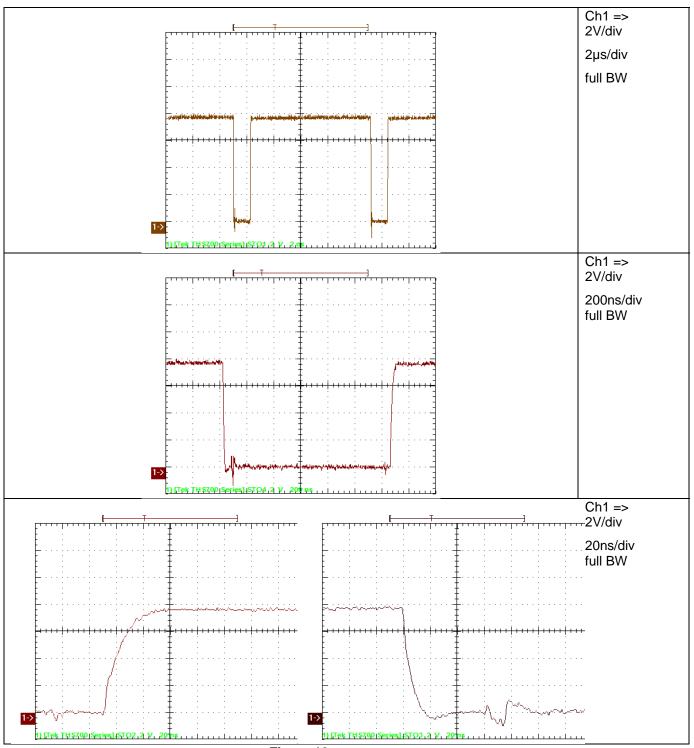

### 8.4 Gate Q2 High Side MOSFET (gate-switchnode)

With input voltage set to 48V and 9A lout results in the waveform shown in Figure 12

Figure 12

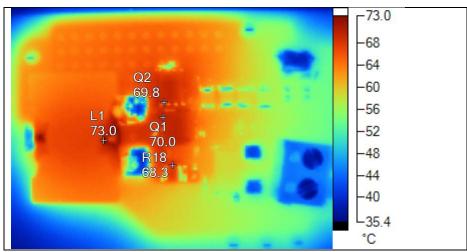

# 9 Thermal Image

Figure 13 shows the thermal image at 48V input and 9A output (30 mins full load)

Figure 13

| Name | Temperature |  |  |  |

|------|-------------|--|--|--|

| L1   | 73.0°C      |  |  |  |

| Q2   | 69.8°C      |  |  |  |

| Q1   | 70.0°C      |  |  |  |

| R18  | 68.3°C      |  |  |  |

Table 2

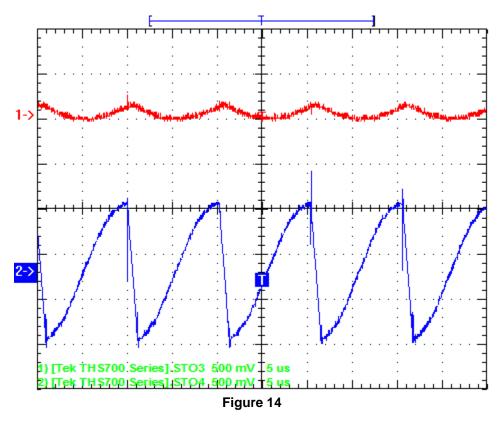

### 10 Appendix, added input filter to attenuate reflected ripple

#### **Revision C:**

In Revision C inductor 74433401050 from Wuerth Electronic is chosen as input filter inductor L2. Figure 14 shows the input ripple voltage across C20 (Channel 1) and C11-C15 (Channel 2). The ripple voltage across C20 is reduced by a factor of 10.

Attenuation roughly -20dB (1.5Vpp vs. 150mVpp) and far less RF content

Current consumption with and without L2 is as follows; estimated power losses 3Arms^2 x 5milliOhms around 45mW, measured 86mW:

|                 | Without L2 | With L2  |

|-----------------|------------|----------|

| V <sub>in</sub> | 48.001 V   | 47.993 V |

| l <sub>in</sub> | 1.0359 A   | 1.0377 A |

| $I_{out}$       | 8.995 A    | 8.992 A  |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated