# TI Designs 1-kW, Compact, 97.5% Efficiency, Digital PFC for AC/DC PSUs With eMeter Reference Design

# Texas Instruments

# **TI Designs**

The TIDA-00707 is a 1-kW, compact (100-mmx80mm) power factor correction (PFC) circuit designed for telecom, server, and industrial power supplies. This reference design is a continuous conduction mode (CCM) boost converter, implemented using a UCD3138A Digital Power Supply controller with all protections built-in. Hardware is designed and tested to pass conducted emissions, surge, and EFT (as per EN55014) requirements.

Key highlights of this reference design:

- Provides a ready platform of front-end PFC to address various power supplies up to 1 kW

- Improves overall system performance with lower bus ripple, lower bus capacitance, lower RMS currents, and front-end protections

- Meets stringent current THD and power factor norms

- Protects for output overcurrent, overvoltage, and undervoltage conditions

#### **Design Resources**

| TIDA-00707 | Design Folder  |

|------------|----------------|

| UCD3138A   | Product Folder |

| UCC28881   | Product Folder |

| UCC27517A  | Product Folder |

| TLV704     | Product Folder |

| OPA2376    | Product Folder |

| ISO7321C   | Product Folder |

All trademarks are the property of their respective owners.

# **Design Features**

- Wide Operating Input Range: 195-V to 270-V AC

- Designed to Drive Wide Range of Downstream DC/DC Converters and Inverter-Fed Motors up to 1 kW

- High Power Factor > 0.99 and < 5% THD From Medium-to-Full Load (50% to 100%); Meets Current THD Regulations as per IEC 61000-3-2

- High Efficiency of > 97% at Full Load Over Entire Operating Voltage Range

- No Need for External Cooling up to 55°C Ambient Operation for Loads ≤ 900 W

- Communicates Input Power Consumption Information of the Unit Precisely for all Load Conditions

- Built-in 12-V/3-W Supply for Housekeeping Power Needs

- PMBUS and Isolated UART for Communication

- Meets the Requirements of Conducted Emissions Standard – EN55011 Class A, EFT Norm IEC6000-4-4, and Surge Norm IEC61000-4-5

- PFC Converter Designed With a Small PCB Form Factor (100 mm × 82 mm)

# **Featured Applications**

- Telecom Rectifiers

- Server and Industrial Power Supplies

- Online UPS

- Power Storage Banks

- Motor Drives

1-kW, Compact, 97.5% Efficiency, Digital PFC for AC/DC PSUs With eMeter

Copyright © 2016, Texas Instruments Incorporated

Reference Design

#### Key System Specifications

2

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### 1 **Key System Specifications**

| PARAMETER                                     | TEST CONDITIONS                                   | MIN              | NOM                          | MAX        | UNIT |

|-----------------------------------------------|---------------------------------------------------|------------------|------------------------------|------------|------|

| INPUT CONDITIONS                              | L                                                 |                  |                              | 1          |      |

| Input voltage (V <sub>INAC</sub> )            |                                                   | 195              | 230                          | 270        | VAC  |

| Frequency (f <sub>LINE</sub> )                |                                                   | 47               | 50                           | 63         | Hz   |

| No load power (P <sub>NL</sub> )              | $V_{INAC} = 230 \text{ V}, I_{OUT} = 0 \text{ A}$ | _                | 2.2                          | _          | W    |

| OUTPUT CONDITIONS                             |                                                   |                  |                              |            |      |

| Output voltage                                |                                                   | _                | 390                          | _          | V    |

| Output current                                |                                                   | _                | _                            | 2.56       | А    |

| Line regulation                               |                                                   | _                | _                            | 0.5        | %    |

| Load regulation                               |                                                   | _                | _                            | 0.5        | %    |

| Output voltage ripple                         | Peak to peak                                      | _                | 20                           | _          | V    |

| Output power (P <sub>o</sub> )                |                                                   | _                | 1000                         | 1000       | W    |

| SYSTEM CHARACTERIS                            | STICS                                             |                  |                              |            |      |

| Efficiency (η)                                | $V_{IN} = V_{NOM}$ and full load                  | _                | 97                           | _          | %    |

|                                               | Output overcurrent                                | _                | _                            | _          | —    |

| Protections                                   | Output overvoltage                                | _                | _                            | _          | —    |

| Protections                                   | Output undervoltage                               | _                | _                            | _          | —    |

|                                               | Open-loop detection                               | _                | _                            | _          | —    |

| Operating ambient                             | Open frame                                        | -10              | 25                           | 55         | °C   |

|                                               | Power line harmonics                              | As per EN5       | 5011 / EN5                   | 5022 Class | A    |

|                                               | Conducted emissions                               | As per IEC       | As per IEC 61000-3-2 Class A |            |      |

| Standards and norms                           | EFT                                               | As per IEC-      | As per IEC-61000-4-4         |            |      |

|                                               | Surge                                             | As per IEC-      | 61000-4-5                    |            |      |

| Board form factor<br>(FR4 material, 2 layers) | Length × Breadth × Height                         | 100 × 80 × 40 mr |                              |            |      |

#### **Table 1. Key System Specifications**

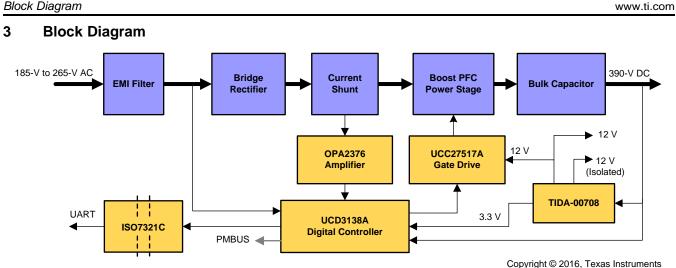

#### 2 System Description

The power supplies for telecom, server, and industrial systems convert AC line power to isolated constant DC voltage of –48 V in telecom systems, 12 V in server systems, and 24 V in industrial systems. These high-power systems typically range from 1 to 5 kW. These power supplies need a front-end power factor correction circuit to shape the input current of the power supply and to meet the power factor and current THD norms such as IEC61000-2-3.

A power factor correction (PFC) circuit shapes the input current of the power supply to be in phase with the mains voltage and aids to maximize the real power drawn from the mains. In addition, a PFC front-end offers several benefits:

- Reduces RMS input current A power circuit with a 230-V/5-A rating is limited to about 575 W of available power with a PF of 0.5. Increasing the PF to 0.99 will double the deliverable power to 1138 W, allowing higher-power loads to be operated.

- Facilitates power supply holdup

The active PFC circuit maintains a fixed intermediate DC bus voltage that is independent of the input voltage, so the energy stored in the system does not decrease as the input voltage decreases. This allows the use of smaller, less expensive bulk capacitors.

- Improves efficiency of downstream converters The PFC reduces the dynamic voltage range applied to the downstream inverters and converters, reducing voltage ratings of rectifiers results in lower forward drops, and increasing operating duty cycle results in lower current in switches.

- Increases the efficiency of the power distribution system A lower RMS current reduces distribution wiring losses.

- Reduces the VA rating of standby power generators and stresses on neutral conductors Reducing harmonics eliminates the risk of triplen harmonics (the third and multiples thereof) that can add up to dangerous levels in the neutral conductor of Y-connected 3-phase systems.

This reference design is a boost power factor converter implemented by using the UCD3138A as the PFC controller for telecom, sever, and industrial systems that demand a PFC up to 1 kW. The design provides a ready platform of active front-end to operate downstream DC/DC converters or inverters operating on Hi-line AC voltage range from 195-V to 270-V AC.

Telecom, server, and industrial power supplies require high efficiency over their entire operating voltage range and wide load variations from 50% to 100% load. This design demonstrates a high-performance power factor stage in a small form factor (165 mm × 95 mm), operating from 195-V to 270-V AC, and delivers up to 1 kW of continuous power output at an efficiency of greater than 97%. The design also provides precise information on power consumption of the end equipment from the AC input line, which can be used for energy calculations and control the load for power optimization on need basis. The EMI filter at the front end of the circuit is designed to meet EN55011 class-A conducted emission levels.

The design uses a 5-W housekeeping power supply board (TIDA-00708), which is designed to meet the auxiliary needs of a general power supply. It supports an input voltage range from 100-V to 450-V DC and provides a 3.5-V DC (1.5-W) and 12-V DC (2.5-W) non-isolated outputs. In addition, a 12-V DC (1-W) isolated output is also provided to support downstream auxiliary power needs. The features of the power supply board include easily pluggable, compact size (LXBXH), high efficiency, low no-load power consumption, and low cost. Find more details of this power supply in the design guide of the power supply, TIDA-00708 (TIDUBK7).

This TI Design meets the key challenges of telecom, server, and industrial power supplies to provide safe and reliable power with all protections built in while delivering high performance with low power consumption and a low bill-of-material (BOM) cost.

3

System Description

Incorporated

Figure 1. Block Diagram of 1-kW PFC Regulator

#### 3.1 Highlighted Products and Key Advantages

The following highlighted products are used in this reference design. Key features for selecting the devices for this reference design are revealed in the following sections. Find more details of the highlighted devices in their respective product datasheets.

#### 3.1.1 UCD3138A—Digital Power Supply Controller

To implement high performance and a small form factor PFC design at 1-kW power, the UCD3138A is the preferred controller as it offers a series of benefits to address the next generation needs of low THD norms and provides a digital interface for health monitoring and controls.

The UCD3138A is a fully programmable, power-optimized digital controller solution that offers the benefits of a simple design to speed up time to market while maintaining ample ability to develop high-performing and well-differentiated power supply solutions. The device is built to include a configurable digital state machine, optimized to meet the performance requirements of telecom and server isolated power applications, along with a general purpose microcontroller. The controller features optimized digital hardware for implementing a number of cutting edge power management functions such as burst mode, ideal diode emulation, mode switching, synchronous rectification, and reduced quiescent current draw in the controller. In summary, the UCD3138A addresses all key concerns such as high efficiency across the entire operating range, high degree of flexibility for various control schemes and topologies, high integration for increased power density, high reliability, and lowest overall system cost.

Other key features include:

- Digital control of up to three independent feedback loops

- Up to 16-MHz error analog-to-digital converter (EADC)

- Up to eight high-resolution digital pulse width modulated (DPWM) outputs

- Fully programmable, high-performance, 31.25 MHz, 32-bit ARM7TDMI-S processor

- 14-channel, 12-bit, 267-ksps general purpose ADC with integrated filters

- Communication peripherals (I2C/PMBus, UART)

- Configurable PWM edge movement

- Configurable feedback control

- Configurable modulation methods

- Fast, automatic, and smooth mode switching

- High efficiency and light load management

- Soft start and stop with and without pre-bias

- Fast input voltage feed forward hardware

- Rich fault protection options

- Internal temperature sensor

- Timer capture with selectable input pins

- Up to five additional general purpose timers

- Built-in watchdog: BOD and POR

- Operating temperature: -40°C to 125°C

# 3.1.2 UCC27517A—Low-Side Gate Driver

Lower switching losses are necessary to achieve high efficiency. The switching losses of a MOSFET are a function of drive current that needs to pass quickly through the Miller Plateau Region of the power-MOSFET's switching transition. A high-current gate driver placed closely to FET helps achieve faster turn on and turn off by effectively charging and discharging voltage across its gate-to-drain parasitic capacitor (CGD), thus reducing switching losses effectively.

The UCC27517A is a simple, low-cost, low-side gate-driver device that offers superior replacement of standard NPN and PNP discrete solutions with peak-source and a sink current of 4 A. The device is a single-channel, high-speed gate driver and has symmetrical drive with negative input voltage handling (-5 V) ability. The UCC27517A operates over a wide VDD range of 4.5 to 18 V and wide temperature range of  $-40^{\circ}$ C to  $140^{\circ}$ C.

Other key features include:

- Fast propagation delays (13 ns typical)

- Outputs held low during VDD UVLO (ensures glitch-free operation at power up and power down)

- Hysteretic-logic thresholds for high-noise immunity

- · Output held low when input pins are floating

- 5-pin DBV (SOT-23) package helps to optimize the space

# 3.1.3 TLV70433—700-V Lowest Quiescent Current Off-Line Switcher

To optimize no load power loss and meet the control circuit power needs, the low dropout (LDO) linear regulator TLV70433 is selected. The TLV70433 operates over a wide input voltage range of 2.5 to 24 V and provides 2% typical accuracy. The device is stable with an effective capacitance of 0.47  $\mu$ F. It is an ideal solution for always on systems that require very little idle state power dissipation.

Other key features include:

- Current output up to 150 mA

- Low power  $I_Q = 3.2 \ \mu A$

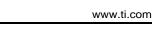

# 3.1.4 OPA2376—High-Speed, Single-Supply, Rail-to-Rail Operational Amplifier

An operational amplifier (op amp) strengthens signals to accommodate the measurement range of the UCD3138 for current sensing feedback. The op amp should have sufficient bandwidth and rail-to-rail operation for exact detection of current sense feedback. The OPA2376 is a perfect fit, as it is a low-noise, rail-to-rail swing, high-speed op amp. These features make it ideal for driving sampling ADCs used for control loops. In addition, the amplifier's wide operating temperature range and wide common-mode range ensures device performance in the most demanding environments.

Other key features include:

- Rail-to-rail input and output

- Wide bandwidth: 5.5 MHz

- Low offset voltage: 5 μV

- Low noise: 7.5 nV/ $\sqrt{Hz}$

- Single-supply operation: 2.2 to 5.5 V

- High CMRR

Block Diagram

6

#### 3.1.5 ISO7321C—Low-Power, Dual-Channel 1/1 Digital Isolator With Fail-Safe High

For a dual-channel isolator with an isolated communication interface, the ISO7321C is the preferred choice, as it provides up to 3000  $V_{RMS}$  for 1 minute per UL 1577. The device is capable of operating up to 25 Mbps and has an integrated glitch filter to aid in low-frequency operation. In fail-safe condition, the ISO7321C output defaults to high level.

Other key features include:

- Low power consumption, typ I<sub>cc</sub> per channel at 1 Mbps: 1 mA (3.3-V supply) ٠

- Qualified for •

- IEC 61000-4-2 Level 3 ESD at 6 kV

- IEC61000-4-4 Level 4 EFT at 4-kV power, 4-kV I/O

- IEC 61000-4-5 Level 4 Surge at 6 kV (air), 8 kV (oil)

- Wide temperature range: -40°C to 125°C •

#### 4 System Design Theory

This reference design is a 1-kW boost power factor converter, operating in CCM and implemented using the UCD3138A Digital Power Supply controller. The design is specifically tailored for telecom, server, and industrial power supplies. This serves as a superior alternative to existing analog control based PFC circuits used to meet the power harmonic norms. This design is intended to operate at country specific line voltages between 195-V to 265-V AC. Under full load conditions, the system has greater than 97% efficiency over the wide input operating voltage range from 195-V to 270-V AC. The TIDA-00707 includes several protections embedded into this design, which includes output overvoltage protection and output short-circuit protection. In addition, the design provides precise information of the power consumption of the unit.

The main focus of this design is a low EMI, high efficiency, high power factor, and protected DC power rail for targeted applications.

### 4.1 PFC Regulator Operating Mode

The PFC shapes the input current of the power supply to maximize the real power available from the mains. The PFC must also comply with low harmonic (low THD) regulatory requirements such as IEC61000-3-2. Currently, two modes of operation have been widely used for PFC implementations: CCM and critical conduction mode (CrM). For higher power circuits, the topology of choice is the boost converter operating in CCM and with average current mode control. For lower power applications, the CrM boost topology is typically used.

For high power levels such as 1 kW, CCM operation is preferred as it has a lower peak and RMS currents. Lower peak currents significantly reduce the stress in power MOSFET, diode, and inductor. In addition, the filtering is easier as the current is more continuous through the boost inductor. Finally, the switching frequency remains constant for the CCM operation, so the boost inductor design and EMI filter designs are easier.

### 4.2 PFC Circuit Component Design

The UCD3138A is configured for fixed frequency in CCM and requires minimal external components for high-wattage PFC regulator implementation. The design process and component selection for this design are illustrated in the following sections.

#### 4.2.1 Design Goal Parameters

Table 2 shows the design goal parameters for this design. These parameters are used in further calculations when selecting components.

|                   | PARAMETER             | MIN | TYP        | MAX  | UNIT |

|-------------------|-----------------------|-----|------------|------|------|

| INPUT             |                       |     |            |      |      |

| V <sub>IN</sub>   | Input voltage         | 195 |            | 270  | VAC  |

| f <sub>LINE</sub> | Input frequency       | 47  |            | 63   | Hz   |

| OUTPUT            |                       | •   | . <u>.</u> | -j   | -    |

| V <sub>OUT</sub>  | Output voltage        |     | 390        |      | VDC  |

| P <sub>OUT</sub>  | Output power          |     |            | 1000 | W    |

|                   | Line regulation       |     |            | 5%   |      |

|                   | Load regulation       |     |            | 5%   |      |

| PF                | Targeted power factor |     | 0.99       |      |      |

| η                 | Targeted efficiency   |     | 96%        |      |      |

| Table 2. | Design | Goal | Parameters  |

|----------|--------|------|-------------|

|          | Design | ooui | i urumeters |

7

System Design Theory

#### 4.2.2 Current Calculations

The input fuse, bridge rectifier, and input capacitor are selected based upon the input current calculations. First, determine the maximum average output current,  $I_{OUT(max)}$ :

$$I_{OUT(max)} = \frac{P_{OUT(max)}}{V_{OUT}} = \frac{1000 \text{ W}}{390 \text{ V}} = 2.56 \text{ A}$$

(1)

The maximum input RMS line current  $(I_{IN\_RMS(max)})$  is calculated using the parameters from Table 2 and the initial assumptions of efficiency and power factor:

$$I_{IN\_RMS(max)} = \frac{P_{OUT(max)}}{\eta \times V_{IN(min)} \times PF} = \frac{1000 \text{ W}}{0.96 \times 195 \text{ V} \times 0.99} = 5.40 \text{ A}$$

(2)

The maximum input current  $(I_{IN(max)})$  and the maximum average input current  $(I_{IN\_AVG(max)})$  can be determined based upon the calculated RMS value and assuming the waveform is sinusoidal:

$$I_{IN(max)} = \sqrt{2} \times I_{IN\_RMS(max)} = \sqrt{2} \times 5.40 \text{ A} = 7.63 \text{ A}$$

(3)

$$I_{IN\_AVG(max)} = \frac{2}{\pi} \times I_{IN(max)} = \frac{2}{\pi} \times 7.63 \text{ A} = 4.86 \text{ A}$$

(4)

#### 4.2.3 Bridge Rectifier

The maximum input AC voltage is 270-V AC, so the DC voltage can reach voltage levels of up to 385-V DC. Considering a safety factor of 30%, select a component with voltage rating greater than 500-V DC. The input bridge rectifier must have an average current capability that exceeds the input average current ( $I_{IN_{AVG(max)}}$ ). A higher current bridge rectifier is recommended to optimize the power loss due diode forward voltage drop.

This design uses a 1000-V, 15-A diode GBJ1508 for input rectification. The forward voltage drop of bridge rectifier diode,  $V_{F BRIDGE} = 0.85$  V.

The power loss in the input bridge ( $P_{BRIDGE}$ ) can be calculated as:  $P_{BRIDGE} = 2 \times V_{F\_BRIDGE} \times I_{IN\_AVG(max)} = 2 \times 0.85 \text{ V} \times 4.86 \text{ A} = 8.26 \text{ W}$

#### (5)

#### 4.2.4 Inductor Ripple Current

8

The TIDA-00707 is designed to operate in CCM. If the chosen inductor allows a relatively high-ripple current, the converter will be forced to operate in discontinuous mode (DCM) at light loads and at the higher input voltage range. High-inductor ripple currents have an impact on the boundary of CCM and DCM and results in higher light-load THD. This also affects the choices for the input capacitor, current sense resistor ( $R_{SENSE}$ ), and internal compensation values tuned in software of the UCD3138A. Allowing an inductor ripple current ( $\Delta I_{RIPPLE}$ ) of 20% or less results in CCM operation over the majority of the operating range; however, this requires a boost inductor that has a higher inductance value, and the inductor itself will be physically large. In this design, the inductor is sized to have 30% peak–to-peak ripple current to optimize performance with size and cost. The focus of the design minimizes space with the understanding that the converter operates in DCM at the higher input voltages and light loads but is optimized well for a nominal input voltage of 230-V AC at full load.

#### 4.2.5 Input Capacitor

Select the input capacitor based on the input ripple current and an acceptable high frequency input voltage ripple. Allowing an inductor ripple current ( $\Delta I_{RIPPLE}$ ) of 30% and a high frequency voltage ripple factor ( $\Delta V_{RIPPLE_IN}$ ) of 2%, the maximum input capacitor value ( $C_{IN}$ ) is calculated by first determining the input ripple current ( $I_{RIPPLE}$ ) and the input voltage ripple,  $V_{IN\_RIPPLE}$ :

$$I_{\text{RIPPLE}} = \Delta I_{\text{RIPPLE}} \times I_{\text{IN}(\text{max})} = 0.3 \times (7.63 \text{ A}) = 2.289 \text{ A}$$

(6)

$$V_{\text{IN}_{\text{RIPPLE}}} = \Delta V_{\text{RIPPLE}_{\text{IN}}} \times V_{\text{IN}_{\text{RECTIFIED}(\text{min})}} = 0.02 \times \left(\sqrt{2} \times 195 \text{ V}\right) = 5.52 \text{ V}$$

(7)

The recommended value for the input X-capacitor can now be calculated as:

$$C_{IN} = \frac{I_{RIPPLE}}{8 \times 140 \text{ kHz} \times 5.52 \text{ V}} = \frac{2.289 \text{ A}}{8 \times 140 \text{ kHz} \times 5.52 \text{ V}} = 0.37 \text{ }\mu\text{F}$$

(8)

A standard value 0.68- $\mu F$  X2 film capacitor is used , taking into consideration the conducted EMI performance.

#### 4.2.6 Boost Inductor

Based upon the allowable inductor ripple current discussed in Section 4.2.4, the boost inductor ( $L_{BST}$ ) is selected after determining the maximum inductor peak current,  $I_{L_{PEAK}}$ :

$$I_{L}PEAK(max) = I_{IN(max)} + \frac{I_{RIPPLE}}{2} = 7.63 \text{ A} + \frac{2.289}{2} = 8.775 \text{ A}$$

(9)

The minimum value of the boost inductor is calculated based upon the acceptable ripple current ( $I_{RIPPLE}$ ) at a worst case duty cycle of 0.5:

$$L_{BST(min)} \ge \frac{V_{OUT} \times D \times (1-D)}{f_{SW} \times I_{RIPPLE}} \ge \frac{390 \text{ V} \times 0.5 \times (1-0.5)}{(140 \text{ kHz} \times 2.289 \text{ A})} \ge 304 \text{ }\mu\text{H}$$

$$(10)$$

The actual value of the boost inductor used is  $L_{BST} = 327 \ \mu H$ .

The duty cycle of operation is a function of the rectified input voltage and will continuously change over the half line cycle. The duty cycle ( $DUTY_{(max)}$ ) can be calculated at the peak of minimum input voltage:

$$DUTY_{(max)} = \frac{V_{OUT} - V_{IN}_{RECTIFIED(min)}}{V_{OUT}} = \frac{390 \ V - (1.414 \times 195 \ V)}{390 \ V} = 0.293$$

(11)

### 4.2.7 Boost Diode

The output diode must have a blocking voltage that exceeds the output overvoltage of the converter and average current same as  $I_{OUT(max)}$ . The diode is generally an ultra-fast recovery diode or a silicon carbide Schottky diode.

For high wattages such as 1 kW, using a silicon carbide Schottky diode, although more expensive, eliminates the reverse recovery losses and results in less power dissipation. The C3D04060A, 600-V/7.5-A SiC diode is selected as the output diode.

$$P_{\text{DIODE}} = V_{\text{F}_{125\text{C}}} \times I_{\text{OUT}(\text{max})} + 0.5 \times f_{\text{SW}} \times V_{\text{OUT}} \times Q_{\text{RR}}$$

The estimated power loss with the SiC diode is  $V_{F_{-125C}} = 1.25$  V;  $Q_{RR} = 0$ .

$$P_{DIODE} = 1.25 \text{ V} \times 2.56 \text{ A} + 0.5 \times 100 \text{ kHz} \times 390 \text{ V} \times 0nC = 3.20 \text{ W}$$

In case an ultra-fast diode is preferred (over a silicon carbide Schottky diode), the BYV29FX-600, a 600-V/9-A diode, is the best choice for this design. The diode losses with ultra-fast diodes are estimated based upon the forward voltage drop ( $V_F$ ) at 125°C and the reverse recovery charge ( $Q_{RR}$ ) of the diode:

$$P_{DIODE} = 1.5 \text{ V} \times 2.56 \text{ A} + 0.5 \times 100 \text{ kHz} \times 390 \text{ V} \times 13 \text{ nC} = 4.09 \text{ W}$$

(12)

System Design Theory

**FEXAS**

*TRUMENTS*

(16)

#### 4.2.8 Switching Element

The MOSFET switch is driven by a UCC27517A gate driver for which VCC bias voltages are limited to (no more than) 12 V from the bias supply. An external gate drive resistor is recommended to limit the rise time and to dampen any ringing caused by the parasitic inductances and capacitances of the gate drive circuit; this will also help in meeting any EMI requirements of the converter. This design uses a 5.0- $\Omega$  resistor; the final value of any design is dependent upon the parasitic elements associated with the layout of the design. To facilitate a fast turnoff, a standard 100-V, 1-A Schottky diode or switching diode is placed antiparallel with the gate drive resistor. A 10-k $\Omega$  resistor is placed between the gate of the MOSFET and ground to discharge the gate capacitance and protect from inadvertent dV/dt triggered turn on.

The drain-to-source RMS current (I<sub>DS RMS</sub>) through switching FET is calculated as

$$I_{DS\_RMS} = \frac{P_{OUT(max)}}{V_{IN\_RECTIFIED(min)}} \times \sqrt{2 - \frac{16 \times V_{IN\_RECTIFIED(min)}}{3 \times \pi \times V_{OUT}}}$$

(13)

$$I_{DS_RMS} = \frac{1000 \text{ W}}{275 \text{ V}} \times \sqrt{2 - \left(\frac{16 \times 275 \text{ V}}{3 \times \pi \times 390 \text{ V}}\right)} = 3.24 \text{ A}$$

The maximum voltage across the FET is the maximum output boost voltage (that is, 420 V), which is the overvoltage set point of the PFC converter to shut down the output. Considering a derating of 30%, the voltage rating of the MOSFET must be greater than 550-V DC.

IPP60R190P6 MOSFET of 600 V and 25 A at 25°C / 12 A at 100°C is selected for the current design.

The conduction losses of the switch MOSFET in this design are estimated using the R<sub>DS(on)</sub> at 125°C, found in the device datasheet, and the calculated drain-to-source RMS current, I<sub>DS RMS</sub>:

$$P_{\text{COND}} = I_{\text{DS}_{\text{RMS}}}^2 \times R_{\text{DS(on)}} = 3.24 \text{ A}^2 \times (0.37 \Omega) = 3.884 \text{ W}$$

(14)

The switching losses are estimated using the rise time, t<sub>r</sub>, and fall time, t<sub>r</sub>, of the MOSFET gate and the output capacitance losses, Coss:

$$P_{SW} = f_{SW} \left[ 0.5 \times V_{OUT} \times I_{IN(max)} \times (t_r + t_f) + 0.5 \times C_{OSS} \times V_{OUT}^2 \right]$$

$$P_{SW} = 100 \text{ kHz} \times \left[ 0.5 \times 390 \text{ V} \times 7.63 \text{ A} \times (12 \text{ ns} + 9 \text{ ns}) + 0.5 \times 61 \text{ pF} \times 390 \text{ V}^2 \right] = 3.588 \text{ W}$$

(15)

Total FET losses:

$P_{COND} + P_{SW} = 3.884 + 3.588 = 7.472 W$

An appropriately sized single heat sink is used for the MOSFET, boost diode, and bridge rectifier.

#### 4.2.9 Sense Resistor

Selecting a current sense resistor is based on two key parameters:

- Optimizing the power loss in the circuit

- Requiring gain and bandwidth of the op amp used to amplify the current sense signal

For current sensing feedback, the OPA2376 op amp strengthens the signals and accommodates the signal range within the measurement range of the UCD3138. In the UCD3138, the ADC used from current sensing has the measurement range of -0 to 1.6 V and has the analog comparator range of 0 to 2.5 V. To have the best signal-to-noise ratio and maximum input signal corresponding to an overcurrent condition,  $R_{\text{SENSE}}$  selected is 0.008  $\Omega$ .

For the signal conditioning, each input signal must follow the subsequent guidelines to limit the amplified signal within the range of ADC previously mentioned. The maximum op amp gain is defined by

$$K_{I} \leq \frac{1.6 \text{ V}}{I_{IN(max)} \times 1.2 \times R_{SENSE}}$$

(17)

In equation 17, a factor of 20% is taken for the overcurrent limit.

$$K_{1} \leq \frac{1.6 \text{ V}}{7.63 \times 1.2 \times 0.008} = 21.84$$

A gain of 21.1 is set using resistors R24 and R26 across the current sense amplifier, U3, as shown in Figure 2.

Figure 2. Amplifier Circuit for Current Sense Signal

Calculate the power dissipated across the sense resistor, P<sub>RSENSE</sub>:  $P_{RSENSE} = I_{IN\_RMS(max)}^2 \times R_{SENSE} = 5.40 \text{ A}^2 \times 0.008 = 0.233 \text{ W}$

(18)

#### 4.2.10 **Output Capacitor**

The output capacitor, C<sub>OUT</sub>, is sized to meet holdup requirements of the converter or the output ripple. In this design, the sizes of the output capacitors are based on a voltage ripple of less than 3% of the output DC voltage.

$$C_{OUT(min)} \ge \frac{I_{OUT}}{\pi \times 2 \times 2 \times f_{LINE(min)} \times V_{RIPPLE}}$$

(19)

Where  $V_{RIPPLE} = 0.03 \times 390 V$  (assuming 3 % voltage ripple).

$$C_{OUT(min)} \geq \frac{2.56}{\pi \times 2 \times 2 \times 57 \times 0.03 \times 390} = 305 \, \mu F$$

The actual capacitor used is 440 µF.

The required ripple current rating at twice the line frequency is equal to:

$$I_{\text{COUT}_2\text{fline}} = \frac{I_{\text{OUT}(\text{max})}}{\sqrt{2}} = \frac{2.56 \text{ A}}{\sqrt{2}} = 1.81 \text{ A}$$

(20)

There is a high-frequency ripple current through the output capacitor:

$$I_{COUT\_HF} = I_{OUT(max)} \times \sqrt{\frac{16 \times V_{OUT}}{3 \times \pi \times V_{IN\_RECTIFIED(min)}}} - 1.5$$

$$I_{COUT\_HF} = 2.56 \text{ A} \times \sqrt{\frac{16 \times 390 \text{ V}}{3 \times \pi \times 1.414 \times 195 \text{ V}}} - 1.5 = 2.43 \text{ A}$$

(21)

The total ripple current in the output capacitor is the combination of both, and the output capacitor must be selected accordingly:

$$I_{\text{COUT}_RMS(\text{total})} = \sqrt{\left(I_{\text{COUT}_2 \text{fline}}\right)^2 + \left(I_{\text{COUT}_HF}\right)^2} = \sqrt{\left(1.81\right)^2 + \left(2.43\right)^2} = 3.03 \text{ A}$$

(22)

#### 4.2.11 Output Voltage Set Point

For low power dissipation and minimal contribution to the voltage set point, 600 k $\Omega$  is used for the top voltage feedback divider resistor, R<sub>FB1</sub>. Multiple resistors in series are used due to the maximum allowable voltage across each resistor.

For each input signal to the UCD3138, its magnitude must accommodate the measurement range of the device. In the UCD3138, the ADC measurement range is 0 to 2.5 V. To have the best signal-to-noise ratio, the input signal must be as large as possible. For this reason, the signal conditioning for each input signal must follow these guidelines:

For V<sub>OUT</sub>, the voltage divider:

$$K_{VOUT} \le \frac{2.5 V}{V_{OUT(max)}}$$

When the maximum output voltage V<sub>OUT(max)</sub> is 420-V DC, including the overvoltage protection set at 415-V DC:

$$K_{VOUT} \le \frac{2.5\,V}{420\,V} = 0.00595$$

Considering these constraints on the gain, the bottom divider resistor, R<sub>FB2</sub>, is selected to meet the feedback voltage of 2.0 V at  $V_{OUT}$  of 390 V.

$$R_{FB2} = \frac{V_{REF} \times R_{FB1}}{V_{OUT} - V_{REF}} = \frac{2.0 \text{ V}}{390 \text{ V}} \times R_{FB1} = 3.07 \text{ k}\Omega$$

A standard value 3.16-kΩ resistor is selected for R<sub>FB2</sub>. A 0.1-μF capacitor is added across RFB2 to filter out noise.

12 1-kW, Compact, 97.5% Efficiency, Digital PFC for AC/DC PSUs With eMeter Reference Design Copyright © 2016, Texas Instruments Incorporated

www.ti.com

(23)

## 4.3 Bias Power

An auxiliary housekeeping power supply is needed to power the UCD3138A control circuit, UCC27517A gate driver, and inrush current limiting bypass relay. In addition, external cooling is required when the converter is operated at power  $\geq$  900 W. To address each of these needs, an add-on auxiliary power supply board (TIDA-00708) of 5 W is used. This board is based on a Flyback design using the high voltage off-line switcher UCC28881. The TIDA-00708 provides a 3.3-V and two 12-V isolated outputs. For more details, see the TIDA-00708 design guide (TIDUBK7).

System Design Theory

Note that the auxiliary power supply TIDA-00708 is already mounted in the TIDA-00707 design and hence is an integral part of TIDA-00707.

| DEVICE              | VOLTAGE (V) | MAX CURRENT (mA) |

|---------------------|-------------|------------------|

| UCD3138A controller | 3.3         | 100              |

| Relay               | 12          | 35               |

| Gate driver         | 12          | 35               |

| Fan (optional)      | 12          | 75               |

#### Table 3. Expected Auxiliary Power Consumption for Different Devices

# 4.4 Designing the Firmware on UCD3138A Controller for Single-Phase PFC

The UCD3138 digital power supply controller has multiple peripherals inside the device, which have been specifically optimized to enhance the performance of PFC circuit.

A step-by-step guide for the design of the UCD3138A firmware required for the TIDA-00707 PFC is explained in the PMP10804 test results (TIDUAY4). This document covers the hardware interface, voltage loop and current loop implementation, system protection, firmware structure, internal state machines, and other advanced features. A graphical user interface (GUI) and a guide for tuning the coefficients of a PFC system are also presented in the guide.

#### 5 **Getting Started Firmware**

This section details the necessary equipment, test setup, and procedure instructions to program the TIDA-00707 board with the provided software.

#### 5.1 Programming the UCD3138A

The design needs the following equipment and necessary files to program the device:

- PMBus to USB Interface Adapter Kit (HPA172) Accessories include:

- USB interface adapter

- USB cable (5-pin B mini male to Type A male)

- Ribbon cable (Socket to socket, 10 pins, 2 headers, polarized) \_

- Four male-to-female interface wires to connect USB interface adapter to connecter J7 on TIDA-00707 control card

Figure 3. USB Adapter (HPA172) Outlook

- GUI installations file "TI-Fusion-Digital-Power-Designer-2.0.16.exe" or later version

- Firmware file • UCD3138\_PFC.x0 file, located in the software package folder path \TIDA-00707\_1.0\Debug

- PC operating system ٠ Microsoft® Windows XP®, or Vista®, or Windows 7®.

#### 5.1.1 GUI Setup

- To use the GUI:

- 1. Find installation file.

The GUI installation file is "TI-Fusion-Digital-Power-Designer-Version-2.0.16.exe" or later version.

- Install the file. Double click and launch the .exe file to start the installation. Click "Next" all the way through. When presented, click "I accept the agreement" after reading it. Then click "Install".

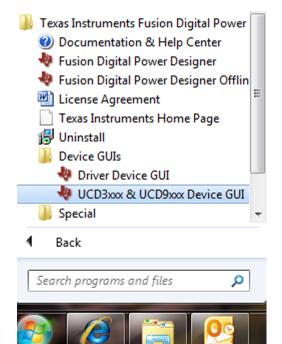

- Launch UCD3138 GUI. After the installation, click "Finish" to exit setup; then click "Exit Program". The GUI for the TIDA-00707 board can be launched through the following steps:

- (a) Click the Windows "Start" button.

- (b) Click "All Programs".

- (c) Click "Texas Instruments Fusion Digital Power Designer".

- (d) Click "Device GUIs".

- (e) Click "UCD3xxx & UCD9xxx Device GUI".

Figure 4. GUI Launch Path

Getting Started Firmware

#### Getting Started Firmware

#### 5.1.2 Hardware Setup

#### 5.1.2.1 Setup Overview

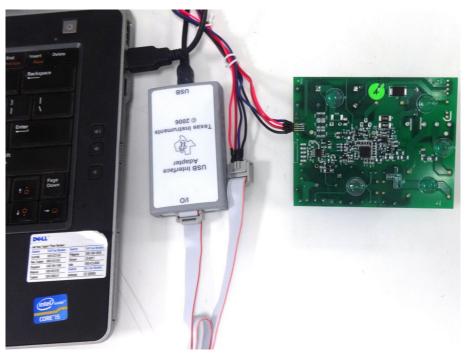

Figure 5 shows the connection between the TIDA-00707 and the PC computer through a USB interface adapter (HPA172).

Figure 5. TIDA-00707 Setup for Programing UCD3138A

**NOTE:** In Figure 5, pin numbers connected on the board are 1 to 4 from top to bottom, respectively.

#### 5.1.2.2 USB Adaptor Connection

1. Use four jumper cables (male on one end and female on the other end) to connect the connector J7 of the "TIDA00707 board" and the connector of USB interface adapter (HPA172). The connection details are shown in Table 4.

| PIN NUMBER ON THE CONNECTOR OF<br>HPA172 (FROM) | PIN NUMBER ON CONNECTOR J7 OF<br>TIDA-00707 BOARD (TO) |

|-------------------------------------------------|--------------------------------------------------------|

| 5                                               | 1                                                      |

| 6                                               | 4                                                      |

| 9                                               | 2                                                      |

| 10                                              | 3                                                      |

#### Table 4. Connections Between J7 and USB Interface Adapter for Programming

- 2. Connect the mini connector of the USB cable to the USB interface adapter and connect the other end to the USB port of the PC.

- 3. The LED on HPA172 should be illuminated. If not, unplug the USB cable and reconnect. If the LED is still not illuminated, change with a new HPA172 USB adapter. If the LED is illuminated, proceed to the next step.

#### 5.1.3 Procedure

- 1. Launch the GUI by the steps described in Section 5.1.1. Wait until the window shown in Figure 6 appears.

- Click "Scan Device in ROM Mode", then wait and check Figure 6 on its "Log" and confirm "Found ROM v2 IC v3 UCD31xx". If "Found ROM" is not shown, click "Device ID", then click "Command Program to jump to ROM (sendByte0xD9)", and then click "Scan Device in ROM Mode" again. If the device is found, proceed to the next step.

| 🕹 UCD3XXX / UCD9XXX Device GUI                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Settings                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Status                                                                                                                                                                                                                                                                                        | Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Attached:       ROM UCD3138A Rev2         Last ROM Found:       IC Info:       UCD3138A Rev2         ROM Info:       ROM v2 IC v3         Package ID:       64-pin         Last Program Found:       Address:         Address:          DEVICE_ID:          MFR_MODEL:          MFR_REVISION: | Scan Device in ROM Mode         Scan for Device in Program Mode:       DEVICE_ID_DEVICE_CODE_IC_DEVICE_ID_PMBUS_REVISION         When a device is found, dump additional PMBus commands         Command ROM to execute its program (SendByte_0xF0 to Address 11)         Command Program to jump to ROM (SendByte_0xF0 to Address 11)         Command Program to jump to ROM (SendByte_0xD9)         Flash       Checksums] SMBus/I2C [Debug  Utilities [Trim] Multi-image         Emware Download       Download firmware to data/program/boot flash       Set PFlash: 0 v 0xFF_0xAA         Dump Flash File       Displays the contents of a flash file       Set DFlash: 0xFF_0xAA         Export Flash       Reads program and/or data flash from the device to a file         Compare Flash Files       Compares two flash file contents         Full Export Tool       Reads program and/or data flash from the device         Elash Test Tool       Erases, writes a pattern, and then verifies that the pattern is present         X0 to Hex Tool       Converts a Tektronix Extended X0 to Intel Hex or S-Record |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Log Timestamp Message 11:06:48.322 Looking for device in ROM mode at address 11d 11:06:48.322 Reading ROM version                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11:06:48.462     Found ROM v2 IC v3 - UCD3138A Rev2       Copy Log     Clear Log       Fusion Digital Power Designer v2.0.16 [2015-01-19]     Texas Inst                                                                                                                                      | Display all SMBus/I2C activity in log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 6. OK Indication (Found ROM)

#### Getting Started Firmware

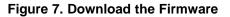

- 3. On the GUI is shown as in Figure 6, click Firmware Download, then a new window appears, as in Figure 7. In this new window:

- (a) Check "Download data flash". If the "DO NOT write program checksum" radio button is chosen as shown in Figure 7, the firmware will not be executed once the PFC is powered up. Click "Command ROM to execute its program" to execute the program.

If the "Write program checksum" radio button is chosen, the firmware will be executed automatically once the PFC is powered up.

- (b) Click "Select file" and find "UCD3138\_PFC.x0", which is located in the software package folder path \TIDA-00707\_1.0\Debug, and click "Download".

- (c) After downloading the program, click "Close" to close the window shown in Figure 7.

| 👆 Fusion Digital Powe                                                                                                                                                                        | r Firmware Download Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _ 🗆 🔀                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                                                                                                                                              | s built-in firmware download tool if you need to download/reset data flash but want to keep your current PMBus configuration.<br>JI, this tool does not require that the device have firmware loaded or be able to execute its program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         |

| Firmware File: C:\Users\<br>Data flash mode:<br>Download data flash<br>(mass erases first)<br>Download partial<br>Start page 0 ÷<br>Final page 63 ÷<br>Erase data flash<br>Boot support Help | a0270670\Documents\UCD3138A\control card\SV601149A_Control_Card_Test_Program_V2.x0         Program flash checksum write mode (power up mode): <ul> <li>DO NOT write program checksum (Stay in ROM)</li> <li>Select this option for experimental mmware or if you need to be able to perform low-level debugging via the ROM. When the UCD3XXX is powered on, it will stay in ROM mode.</li> <li>WRITE program checksum (Automatically execute Select this option for production devices. When the device is powered on, it will execute its program flash.</li> <li>Validate with checksum 0x 0</li> <li>PASS THRU whatever program checksum is in the firmware This option GUI "File&gt;Export" tool PFlash + DFlash output or the UCD3XXX Device GUI's "Export Flash" output.</li> </ul> | Select File<br>Download |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

# 6 Getting Started Hardware

This section details the necessary equipment, test setup, and procedure instructions for the TIDA-00707 board testing and validation.

## 6.1 Test Conditions

For input, the power supply source ( $V_{IN}$ ) must range from 195-V to 270-V AC. Set the input current limit of input AC source to 7.5 A.

For output, use an electronic variable load or a variable resistive load, which must be rated for  $\ge$  400 V and must vary the load current from 0 mA to 3 A.

# 6.2 Test Equipment Required for Board Validation

- Isolated AC source

- Single-phase power analyzer

- Digital oscilloscope

- Multimeters

- Electronic or resistive load

### 6.3 Test Procedure

- 1. Connect input terminals of the reference board to the AC power source.

- Connect output terminals to the electronic load, maintaining correct polarity. VDC and ground pins of the output are provided as test points. These test points can be removed to make proper soldered connections for loading the converter for testing.

- 3. Set and maintain a minimum load of about 10 mA.

- 4. Increase gradually the input voltage from 0 V to turn on voltage of 195-V AC.

- 5. Start the load to draw current from the output terminals of the PFC.

- 6. Observe startup conditions for smooth switching waveforms.

- 7. For a power of ≥ 900 W, an external fan can be used for cooling. A low-wattage, high LFM fan such as 612NMLE is recommended with a 12-V output provided at connector J3. Ensure that the fan is rated for 12-V operation and power ≤ 0.75 W.

- 8. Connect the fan at connector J3, maintaining correct polarity.

- 9. If a low-wattage fan is not available, a cooling fan can be powered from an external DC lab power supply.

#### 7 Test Results

The test results are divided in multiple sections that cover the steady state performance, functional performance waveforms and test data, transient performance waveforms, thermal measurements, conducted emission measurements, and Surge and EFT measurements.

### 7.1 Performance Data

#### 7.1.1 Efficiency and Regulation With Load Variation

Table 5 shows the data at a 230-V AC input:

| V <sub>INAC</sub> (V) | I <sub>INAC</sub> (A) | PF   | P <sub>INAC</sub> (W) | і <sub>тно</sub> (%) | V <sub>OUT</sub> (V) | I <sub>оυт</sub> (А) | Р <sub>оит</sub> (W) | EFF (%) | % REG |

|-----------------------|-----------------------|------|-----------------------|----------------------|----------------------|----------------------|----------------------|---------|-------|

| 230                   | 0.23                  | 0.80 | 41.5                  | 13.59                | 390.8                | 0.10                 | 37.1                 | 89.4    | 0.07  |

| 230                   | 0.37                  | 0.94 | 79.6                  | 12.90                | 390.7                | 0.19                 | 74.6                 | 93.7    | 0.04  |

| 230                   | 0.70                  | 0.97 | 156.2                 | 12.12                | 390.7                | 0.38                 | 149.2                | 95.6    | 0.04  |

| 230                   | 1.03                  | 0.99 | 233.4                 | 9.50                 | 391.0                | 0.58                 | 224.8                | 96.3    | 0.12  |

| 230                   | 1.36                  | 0.99 | 309.7                 | 7.00                 | 390.9                | 0.77                 | 299.4                | 96.7    | 0.10  |

| 230                   | 1.69                  | 0.99 | 386.6                 | 2.96                 | 390.9                | 0.96                 | 374.5                | 96.9    | 0.10  |

| 230                   | 2.02                  | 1.00 | 462.7                 | 2.30                 | 390.8                | 1.15                 | 449.0                | 97.0    | 0.07  |

| 230                   | 2.35                  | 1.00 | 539.4                 | 2.00                 | 390.8                | 1.34                 | 524.1                | 97.2    | 0.07  |

| 230                   | 2.68                  | 1.00 | 615.7                 | 1.99                 | 390.8                | 1.53                 | 598.7                | 97.2    | 0.07  |

| 230                   | 3.02                  | 1.00 | 694.0                 | 1.85                 | 390.7                | 1.73                 | 674.7                | 97.2    | 0.04  |

| 230                   | 3.35                  | 1.00 | 770.2                 | 1.72                 | 390.5                | 1.92                 | 748.2                | 97.1    | -0.01 |

| 230                   | 3.68                  | 1.00 | 847.1                 | 1.58                 | 390.4                | 2.11                 | 822.2                | 97.1    | -0.03 |

| 230                   | 4.01                  | 1.00 | 923.0                 | 1.41                 | 390.1                | 2.30                 | 895.7                | 97.0    | -0.11 |

| 230                   | 4.20                  | 1.00 | 997.1                 | 1.43                 | 390.0                | 2.48                 | 967.2                | 97.0    | -0.15 |

| 230                   | 4.50                  | 1.00 | 1034.0                | 1.40                 | 390.0                | 2.57                 | 1002.6               | 97.0    | -0.16 |

Table 5. Efficiency and Regulation With Load Variation

#### 7.1.2 Standby Power

The standby power was noted at multiple AC input voltages with a constant negligible load on the output DC bus. The results are tabulated in Table 6:

| V <sub>INAC</sub> (VAC) | ENERGY INPUT AFTER<br>3 MIN (mWh) | V <sub>оит</sub> (V) | I <sub>оит</sub> (А) | Р <sub>оит</sub> (W) | NO LOAD INPUT<br>POWER (W) |

|-------------------------|-----------------------------------|----------------------|----------------------|----------------------|----------------------------|

| 195                     | 113.0                             | 392                  | 0.0                  | 0.0                  | 2.26                       |

| 230                     | 106.0                             | 392                  | 0.0                  | 0.0                  | 2.12                       |

| 270                     | 96.0                              | 392                  | 0.0                  | 0.0                  | 1.92                       |

#### **Table 6. No Load Power Consumption**

No load power is contributed by three main branches:

- Resistors used input AC voltage sensing

- Resistors used for output DC bus voltage sensing

- Power consumed by controller and relay

The power consumed by AC input and DC output sensing resistors is ~0.55 W, and this can be decreased by increasing the resistor values.

# 7.2 Performance Curves

# 7.2.1 Efficiency and Power Factor With Load and Line Variation

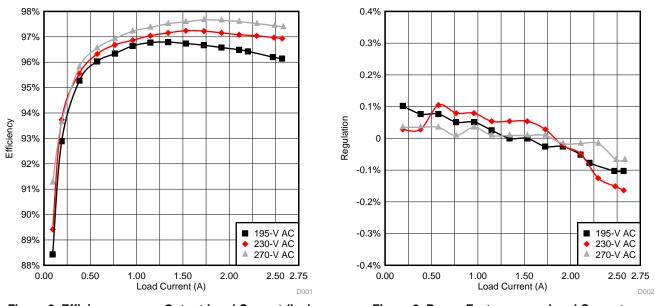

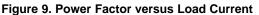

Figure 8 and Figure 9 show the measured efficiency and power factor in the system with AC input voltage variation.

Figure 8. Efficiency versus Output Load Current (Iout)

### 7.2.2 Input THD With Load and Line Regulation

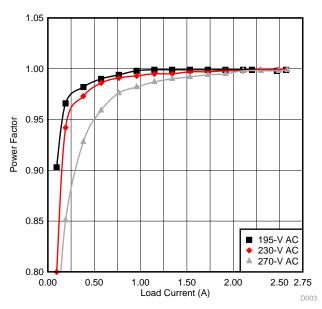

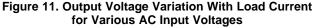

Figure 10 shows the measured input THD of the system with AC input voltage variation. Figure 11 shows the measured load regulation of the output with AC input voltage variation.

Test Results

#### 7.3 Functional Waveforms

#### 7.3.1 Switching Node Waveforms

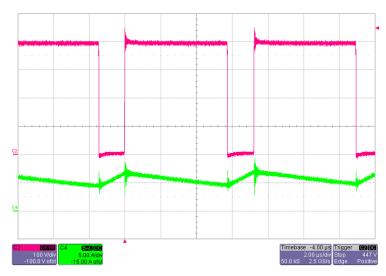

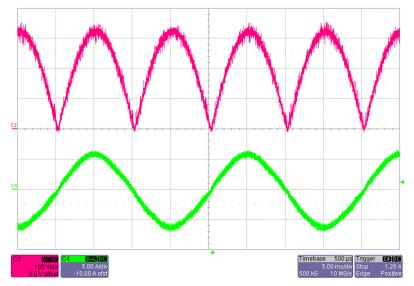

The waveform at switching node (SW) was observed along with the PFC inductor current for 230-V AC under full load (2.31 A) conditions.

**NOTE:** Red trace: Drain voltage, 100 V/div; Green trace: PFC inductor current, 5 A/div

Figure 12. SW Node Waveform and MOSFET Current at  $V_{INAC}$  = 230-V AC, Full Load

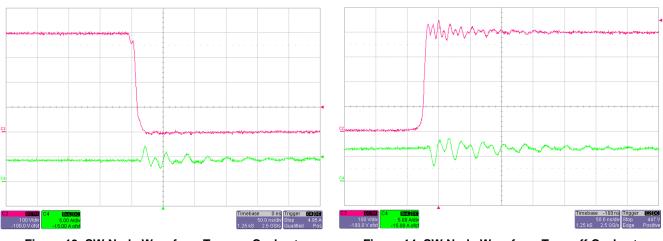

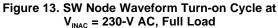

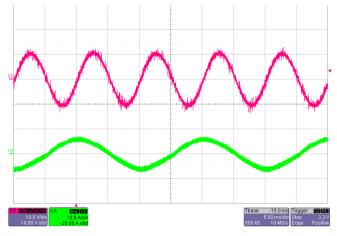

NOTE: Red trace: Drain voltage, 100 V/div; Green trace: Drain current, 5 A/div

Figure 14. SW Node Waveform Turn-off Cycle at  $V_{INAC}$  = 230-V AC, Full Load

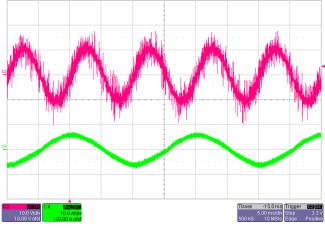

#### 7.3.2 Input Voltage and Current Waveform

Figure 15 shows the input current waveform at 230-V AC with full load conditions.

Figure 15. Input Voltage and Input Current at  $V_{INAC}$  = 230-V AC, Full Load

# 7.3.3 Inrush Current Waveform

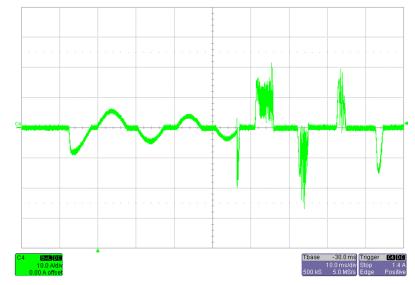

Inrush current drawn by the system is observed and recorded at a maximum input voltage of 230-V AC.

Figure 16. Output Voltage and Input Inrush Current at V<sub>INAC</sub> = 230 V, Full Load

Test Results

www.ti.com

### 7.3.4 Output Ripple

A ripple observed at the 390-V DC output is loaded to 2.56 A at 230-V AC.

Figure 17. Output Voltage Ripple at  $V_{INAC}$  = 230 V, Full Load

Figure 18. Output Voltage Ripple at V<sub>INAC</sub> = 230 V, Full Load, Only 50-Hz Component

additub

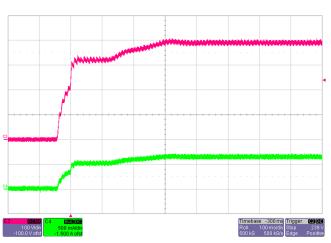

### 7.3.5 Turn-On Characteristics

The 390-V output turn on at full load (2.31 A) was recorded at 230-V AC.

Figure 20. Output Turn-on Waveform at V<sub>INAC</sub> = 230 V With Full Load of 2.56 A

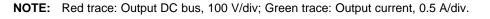

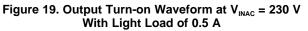

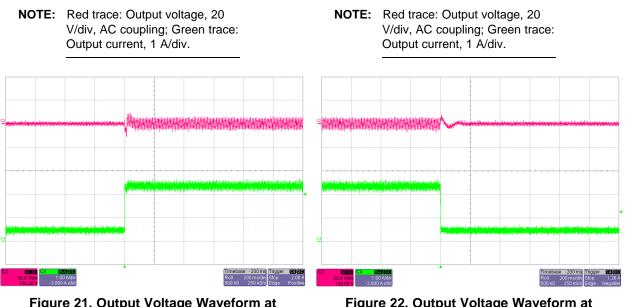

# 7.4 Transient Waveforms

#### 7.4.1 Transient Load Response

Load transient performance is observed with the load switched at a 0.2-m wire length. The output load is switched using electronic load.

$V_{IN}$  = 230-V AC, load transient from 0.5 to 2.56 A and vice-versa performance at a 390-V output.

Figure 21. Output Voltage Waveform at V<sub>INAC</sub> = 230 V, Load Transient From 0.5 to 2.56 A Figure 22. Output Voltage Waveform at  $V_{INAC}$  = 230 V, Load Transient From 2.56 to 0.5 A

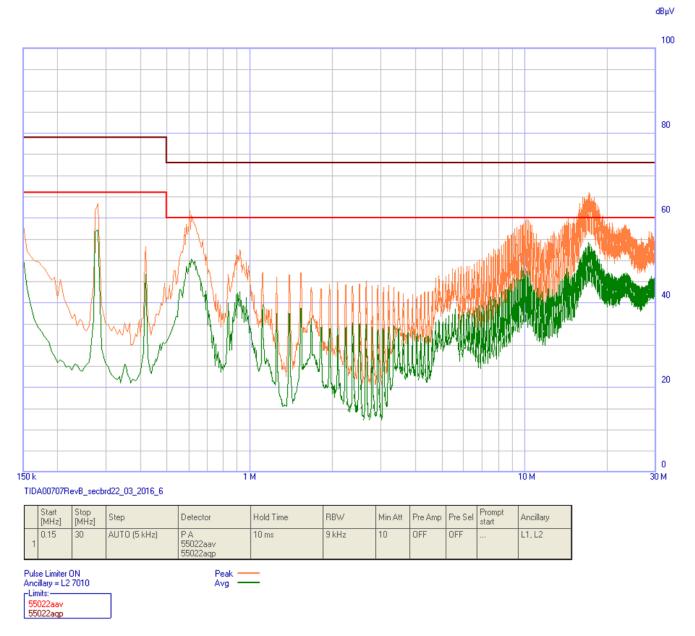

#### 7.5 Conducted Emissions

Generally, conducted emissions increase at full load. This operating point is chosen for measuring conducted EMI.

#### 7.5.1 With Resistive Load at Output

The 230-V AC input, 2.56-A resistive load is connected to the PSU with short leads. The conducted emissions in a pre-compliance test setup were compared against EN55011 class-A limits and found to meet them satisfactorily.

# 7.6 Surge and Fast Transients Tests

Surge and EFT testing is done on the boards as per EN55014. The test condition and test results are tabulated in Table 7.

| BASIC STANDARD                               | PORT     | IEC 61000-6-2/EN 50082-2<br>REQUIREMENTS <sup>(1)</sup> | PERFORMANCE<br>CRITERION REQUIRED | TEST RESULT                                        |

|----------------------------------------------|----------|---------------------------------------------------------|-----------------------------------|----------------------------------------------------|

| IEC/EN 61000-4-4:<br>Fast transients (burst) | AC input | ±2 kV, 5 kHz                                            | B <sup>(2)</sup>                  | Passed with performance criterion $A^{(3)}$        |

| IEC/EN 61000-4-5:<br>Surge                   | AC input | ±4 kV line to earth<br>±2 kV line to line               | B <sup>(2)</sup>                  | Passed with performance criterion A <sup>(3)</sup> |

#### Table 7. Surge and EFT Test Results

Test Results

(1) Immunity standard for industrial environments

<sup>(2)</sup> Temporary loss of function or degradation of performance which ceases after the disturbance ceases

<sup>(3)</sup> Normal performance within limits specified by the design or manufacturer

#### Design Files

### 8 Design Files

#### 8.1 Schematics

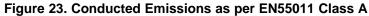

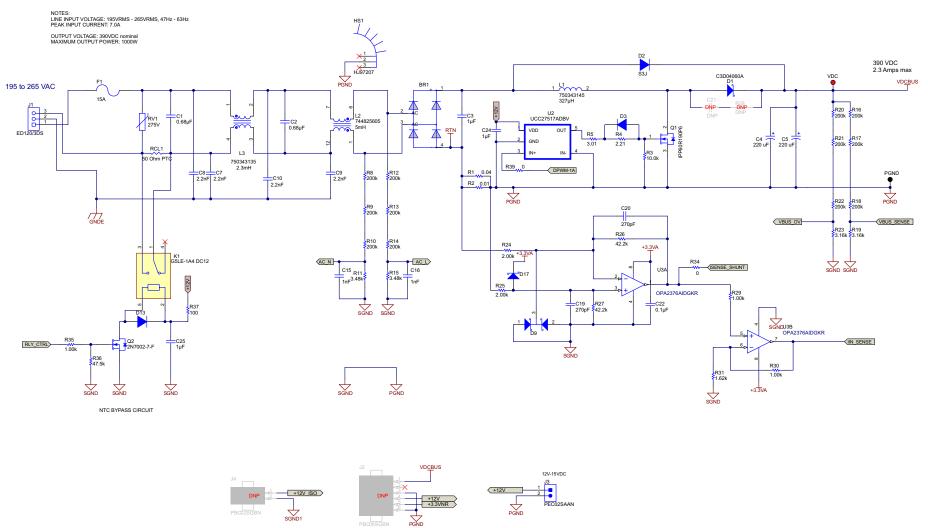

To download the schematics, see the design files at TIDA-00707.

Copyright © 2016, Texas Instruments Incorporated

## Figure 24. Power Stage, Current and Voltage Sensing Schematic

Copyright © 2016, Texas Instruments Incorporated

# Figure 25. Controller and Communication Interface Schematic

Design Files

#### 8.2 **Bill of Materials**

www.ti.com

To download the bill of materials (BOM), see the design files at TIDA-00707.

#### 8.3 PCB Layout Recommendations

A careful PCB layout is critical in a high-current fast-switching circuit to provide appropriate device operation and design robustness. As with all switching power supplies, pay attention to detail in the layout to save time in troubleshooting later on.

#### 8.3.1 **Power Stage Specific Guidelines**

Follow these key guidelines to route the power stage components:

- Minimize the loop area and trace length of the power path circuits, which contain high frequency • switching currents. This will help reduce EMI and improve the converter's overall performance.

- Keep the switch node as short as possible. A short and optimal trace width helps to reduce induced ringing caused by parasitic inductance.

- Keep traces with high dV/dt potential and high di/dt capability away from or shielded from sensitive signal traces with adequate clearance and ground shielding.

- Keep power ground and control ground separate for each power supply stage. Tie them together (if they are electrically connected) in one point near DC input return or output return of the given stage.

- When multiple capacitors are used in parallel for current sharing, the layout should be symmetrical across both capacitor leads. If the layout is not identical, the capacitor with the lower series trace impedance will see higher peak currents and become hotter (i2R).

- Tie the heat sinks of all the power switching components to their respective power grounds.

- Place protection devices such as TVS, snubbers, capacitors, or diodes physically close to the device they are intended to protect, and route with short traces to reduce inductance.

- Choose the width of PCB traces based on an acceptable temperature rise at the rated current as per IPC2152 as well as acceptable DC and AC impedances. The traces should withstand the fault currents (such as short circuit current) before electronic protection devices, such as fuses or circuit breakers, are activated.

- Determine the distances between various traces of the circuit according to the requirements of applicable standards. For this design, the UL 60950-1 safety standard is followed to maintain the creepage and clearance from live line to neutral line and to safety ground, as defined in the Tables 2K through 2N of this standard.

- Adapt the thermal management to fit the end-equipment requirements.

#### 8.3.2 UCD3138A Controller Specific Guidelines

The UCD3138A is a highly integrated controller with a large number of mixed signals. Follow these key guidelines to route the controller components and signal circuits:

• To reduce noise coupling and prevent chip malfunction, group each pin, select good components, have appropriate connections to each pin, and place well on the PCB.

Design Files

- To avoid chip malfunction, group all digital circuitry and analog circuitry, place digital circuitry close to each other, place analog circuitry close to each other and make trace connections among them.

- Locate all controller support components at specific signal pins close to their connection pin. Connect the other end of the component to the AGND or DGND, respectively, with shortest trace length.

- Find detailed recommendations of each pin connection and its associated component in the UCD3138A data manual (SLUSC66).

- Reference grounds AGND or DGND for the device can be common ground SGND (signal ground) or separate grounds. In either case, these grounds must be a copper plane or island. If there are separate AGND or DGND planes, tie them together close to the chip.

- Make the trace routing for the voltage sensing and current sensing circuit components to the device as short as possible to reduce parasitic effects on the current limit and current and voltage monitoring accuracy. These traces must not have any coupling to switching signals on the board.

- Connect the SGND plane to high current ground (main power ground) at a single point that is at the negative terminal of DC IO capacitor, respectively.

#### 8.3.3 Gate Driver Specific Guidelines

Follow these key guidelines to route the high-frequency high-current gate driver:

- Locate the driver device as close as possible to the power device to minimize the length of high current traces between the output pins of gate drive and the gate of the power device.

- Locate the VDD bypass capacitors between VDD and GND as close as possible to the driver with minimal trace length to improve the noise filtering. These capacitors support high-peak current being drawn from VDD.

- Minimize the turn-on and turn-off current-loop paths (driver device, power MOSFET, and VDD bypass capacitor) as much as possible to keep the stray inductance to a minimum.

- Minimize noise coupling with star point grounding from one current loop to another. Connect the driver GND to the other circuit nodes such as the power switch source or the PWM controller ground at one single point. The connected paths must be as short as possible to reduce inductance and be as wide as possible to reduce resistance.

#### 8.3.4 Layout Prints

To download the layer plots, see the design files at TIDA-00707.

Design Files

### 8.4 Altium Project

To download the Altium project files, see the design files at TIDA-00707.

#### 8.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00707.

### 8.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00707.

### 9 Software Files

To download the software files, see the design files at TIDA-00707.

### 10 References

- 1. Texas Instruments, *High Power Factor and High Efficiency—You Can Have Both*, Unitrode Power Supply Design, Seminar 1800 (SLUP282)

- 2. Texas Instruments, A Design Review of a Full-Featured 350-W Offline Power Converter, PMP5568 Test Results (TIDU186)

- 3. Texas Instruments, *Snubber Circuits: Theory, Design and Applications*, Seminar 900, Topic 2 (SLUP100)

- 4. Texas Instruments, *Safety Considerations in Power Supply Design*, Unitrode Power Supply Design Seminar, Topic 1 (SLUP224)

- 5. Texas Instruments, Understanding Noise-Spreading Techniques and their Effects in Switch-Mode Power Applications, Unitrode Power Supply Design Seminar, SEM1800, Topic-2 (PDF)

- 6. Texas Instruments, *Designing a UCD3138 Controlled Interleaved PFC*, UCD3138 Application Report (SLUA712)

- 7. Texas Instruments, *Designing a UCD3138 Controlled Bridgeless PFC*, UCD3138 Application Report (SLUA713)

- 8. Texas Instruments, UCD3138 Digital Power Peripherals Programmer's Manual (SLUU995)

- 9. Texas Instruments, *PFC THD Reduction and Efficiency Improvement by ZVS or Valley Switching*, PFC Application Report (SLUA644)

- 10. Texas Instruments, *Low-cost solution for measuring input power and RMS current*, Technical Brief (SLYT545)

- 11. Texas Instruments, AC cycle skipping improves PFC light-load efficiency, Technical Brief (SLYT585)

### 11 Terminology

SLYZ022 — TI Glossary: This glossary lists and explains terms, acronyms, and definitions.

Specific terms used in the document:

- PWM— Pulse width modulation

- FETs, MOSFETs-Metal-oxide-semiconductor field-effect transistor

- IGBT- Insulated gate bipolar transistor

- ESD— Electrostatic discharge

- RMS— Root mean square

### 12 About the Authors

**LATIF AMEER BABU** is a Systems Architect at Texas Instruments, where he is responsible for developing reference design solutions for the industrial segment. Latif brings to this role his extensive experience in power electronics, high frequency DC-DC converter, and analog circuit design. Latif earned his master of technology in power electronics and power systems from Indian Institute of Technology, Mumbai; IN. Latif is a member of the Institute of Electrical and Electronics Engineers (IEEE) and has one US patent.

**BOSHENG SUN** is a Systems Engineer at Texas Instruments where he is responsible for systems solution, firmware design and collateral development for TI's high voltage power controller products. Bosheng earned a B.S. degree from Tsinghua University, China in 1995, and an M.S. degree from Cleveland State University, Ohio in 2003, both in electrical engineering. Bosheng has three US patents.