# **BQ76905**

# Technical Reference Manual

Literature Number: SLUUCI8 NOVEMBER 2023

# **Table of Contents**

| Read This First                                          | 7               |

|----------------------------------------------------------|-----------------|

| About This Manual                                        |                 |

| Battery Notational Conventions                           | 7               |

| Trademarks                                               | 7               |

| Glossary                                                 | 7               |

| 1 Introduction                                           | 9               |

| 2 Device Description                                     | 11              |

| 2.1 Overview                                             | 11              |

| 2.2 Functional Block Diagram                             | 11              |

| 3 Device Configuration                                   | 13              |

| 3.1 Direct Commands and Subcommands                      | 13              |

| 3.2 Configuration Using OTP or Registers                 | 14              |

| 3.3 Data Formats                                         | 14              |

| 3.3.1 Unsigned Integer                                   | 14              |

| 3.3.2 Integer                                            | 14              |

| 3.3.3 Hex                                                |                 |

| 4 Device Security                                        | 17              |

| 5 Measurement Subsystem                                  | 19              |

| 5.1 Voltage Measurement                                  | 19              |

| 5.1.1 Voltage Measurement Schedule                       | 19              |

| 5.1.2 Unused VC Cell Input Pins                          | 22              |

| 5.1.3 General Purpose ADCIN Functionality                | 23              |

| 5.2 Coulomb Counter and Digital Filters                  | 23              |

| 5.3 Internal Temperature Measurement                     | 26              |

| 5.4 Thermistor Temperature Measurement                   | 27              |

| 5.5 Measurement Calibration                              | <mark>27</mark> |

| 6 Protection Subsystem                                   | 33              |

| 6.1 Protections Overview                                 | 33              |

| 6.2 Protection FET Drivers                               | 35              |

| 6.3 Cell Overvoltage Protection                          | 36              |

| 6.4 Cell Undervoltage Protection                         | 37              |

| 6.5 Short Circuit in Discharge Protection                | 38              |

| 6.6 Overcurrent in Charge Protection                     | 40              |

| 6.7 Overcurrent in Discharge 1 and 2 Protections         | 40              |

| 6.8 Current Protection Latch                             | 42              |

| 6.9 CHG Detector                                         | 42              |

| 6.10 Overtemperature in Charge Protection                | 43              |

| 6.11 Overtemperature in Discharge Protection             |                 |

| 6.12 Internal Overtemperature Protection                 | 44              |

| 6.13 Undertemperature in Charge Protection               | 45              |

| 6.14 Undertemperature in Discharge Protection            | 46              |

| 6.15 Host Watchdog Protection                            | 47              |

| 6.16 Cell Open Wire Detection                            | 47              |

| 6.17 Voltage Reference Measurement Diagnostic Protection | 48              |

| 6.18 VSS Measurement Diagnostic Protection               | 48              |

| 6.19 REGOUT Diagnostic Protection                        |                 |

| 6.20 LFO Oscillator Integrity Diagnostic Protection      |                 |

| 6.21 Internal Factory Trim Diagnostic Protection         | 49              |

| 7 Device Status and Controls.                            | 51              |

Table of Contents www.ti.com

| 7.1 0x00 Control Status() and 0x12 Battery Status() Commands |     |

|--------------------------------------------------------------|-----|

| 7.2 LDOs                                                     |     |

|                                                              |     |

| 7.4 TS Pin Operation                                         |     |

| 7.5 Programmable Timer                                       |     |

| 8 Operational Modes                                          |     |

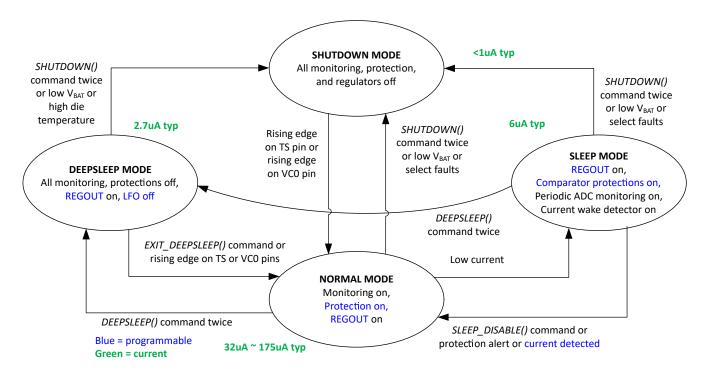

| 8.1 Overview of Operational Modes                            |     |

| 8.2 NORMAL Mode                                              |     |

| 8.3 SLEEP Mode                                               |     |

| 8.4 DEEPSLEEP Mode                                           |     |

| 8.5 SHUTDOWN Mode                                            |     |

| 8.6 CONFIG UPDATE Mode                                       |     |

| 9 I <sup>2</sup> C Serial Communications                     |     |

| 9.1 I <sup>2</sup> C Serial Communications Interface         |     |

| 10 Cell Balancing.                                           |     |

| 10.1 Cell Balancing                                          |     |

| 11 Commands and Subcommands                                  |     |

| 11.1 Direct Commands                                         |     |

| 11.2 Bit field Definitions for Direct Commands               | 72  |

| 11.2.1 Safety Alert A Register                               |     |

| 11.2.2 Safety Status A Register                              |     |

| 11.2.3 Safety Alert B Register                               |     |

| 11.2.4 Safety Status B Register                              |     |

| 11.2.5 Battery Status Register                               |     |

| 11.2.6 Alarm Status Register                                 | 76  |

| 11.2.7 Alarm Raw Status Register                             | 78  |

| 11.2.8 Alarm Enable Register                                 | 79  |

| 11.2.9 FET CONTROL Register                                  |     |

| 11.2.10 REGOUT CONTROL Register                              |     |

| 11.2.11 DSG FET Driver PWM Control Register                  |     |

| 11.2.12 CHG FET Driver PWM Control Register                  |     |

| 11.3 Command-only Subcommands                                |     |

| 11.4 Subcommands with Data                                   |     |

| 11.5 Bit field Definitions for Subcommands                   |     |

| 11.5.1 DEVICE NUMBER Register                                |     |

| 11.5.2 FW VERSION Register                                   |     |

| 11.5.3 HW VERSION Register                                   |     |

| 11.5.4 SECURITY KEYS Register                                |     |

| 11.5.5 CB ACTIVE CELLS Register                              |     |

| 11.5.7 PROT RECOVERY Register                                |     |

| 12 Data Memory                                               |     |

| 12.1 Calibration.                                            |     |

| 12.1.1 Calibration:Voltage                                   |     |

| 12.1.2 Calibration: Current.                                 |     |

| 12.1.3 Calibration:Temperature                               |     |

| 12.2 Settings                                                |     |

| 12.2.1 Settings:Configuration                                |     |

| 12.2.2 Settings:Cell Balancing                               |     |

| 12.2.3 Settings:Protection                                   |     |

| 12.3 Protections.                                            |     |

| 12.3.1 Protections:Cell Voltage                              |     |

| 12.3.2 Protections: Current                                  |     |

| 12.3.3 Protections:Temperature                               |     |

| 12.4 Power                                                   |     |

| 12.4.1 Power:Sleep                                           |     |

| 12.4.2 Power:Shutdown                                        |     |

| 12.5 Security                                                |     |

| 12.5.1 Security:Settings                                     |     |

| 12.6 Data Memory Summary                                     | 115 |

www.ti.com Table of Contents

Table of Contents www.ti.com

This page intentionally left blank.

#### **About This Manual**

This technical reference manual (TRM) discusses the modules and peripherals of the BQ76905 device, and how each is used to build a complete battery pack monitor and protection solution. For details on the hardware device features and electrical specifications, see the BQ76905 2-Series to 5-Series High Accuracy Battery Monitor and Protector for Li-Ion, Li-Polymer, LiFePO<sub>4</sub> (LFP), and LTO Battery Packs.

# **Battery Notational Conventions**

The following notation is used if commands, subcommands, and data memory values are mentioned within a text block:

- Commands and subcommands: italics with parentheses and no breaking spaces; for example, Battery Status()

- Data memory: italics, bold, and breaking spaces; for example, Power Config

- Register bits and flags: italics and brackets; for example, [SCD]

- Data memory bits: italics and bold; for example, [FET EN]

- · Modes and states: ALL CAPITALS; for example, DEEPSLEEP

#### **Trademarks**

All trademarks are the property of their respective owners.

# Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

Read This First www.ti.com

This page intentionally left blank.

# Chapter 1 Introduction

The Texas Instruments BQ76905 provides a highly integrated, high accuracy battery monitor and protector for 2-series to 5-series Li-lon, Li-Polymer, and LiFePO<sub>4</sub> battery packs. Each device includes a high accuracy monitoring system, a highly configurable protection subsystem, and support for host controlled cell balancing. Integration includes low-side protection NFET drivers, a programmable LDO for external system use, and an I<sup>2</sup>C host communication interface supporting up to 400-kHz operation with optional CRC. Device features include:

- Battery monitoring capability for 2-series to 5-series cells

- Integrated low-side drivers for NFET protection with optional autonomous recovery

- · Extensive protection suite including voltage, temperature, current, and internal diagnostics

- 16-bit delta-sigma voltage ADC

- High accuracy cell voltage measurement of 5 mV (typical)

- Dedicated 16 / 24-bit delta-sigma coulomb counter ADC

- High-accuracy current measurement with low input offset error

- Wide-range current applications (±200 mV measurement range across sense resistor)

- 48-bit accumulated charge integrator with timer

- · Host-controlled cell balancing

- Multiple power modes (typical battery pack operating range conditions)

- NORMAL mode: 30 μA to 180 μA

- SLEEP mode: 10 μA

DEEPSLEEP mode: 5 μA

SHUTDOWN Mode: 1 μA

- High voltage tolerance of 45 V on cell connect and select additional pins

- · Support for temperature sensing using internal sensor and external thermistor

- Integrated one-time-programmable (OTP) memory for device settings, programmed by TI

- 400-kHz I<sup>2</sup>C serial communications with optional CRC support

- Programmable LDO for external system usage

*Introduction* www.ti.com

This page intentionally left blank.

#### 2.1 Overview

The BQ76905 product is a highly integrated, accurate battery monitor and protector for 2-series to 5-series Li-lon, Li-Polymer, LiFePO<sub>4</sub> (LFO), and LTO battery packs. A high accuracy voltage, current, and temperature measurement provides data for host-based algorithms and control. A feature-rich and highly configurable protection subsystem provides a wide set of protections which can be triggered and recovered completely autonomously by the device or under full control of a host processor. Integrated FET drivers drive low-side charge and discharge protection NFETs. A programmable LDO is included for external system use, with voltage programmable to 1.8 V, 2.5 V, 3.0 V, 3.3 V, or 5.0 V, capable of providing up to 20 mA.

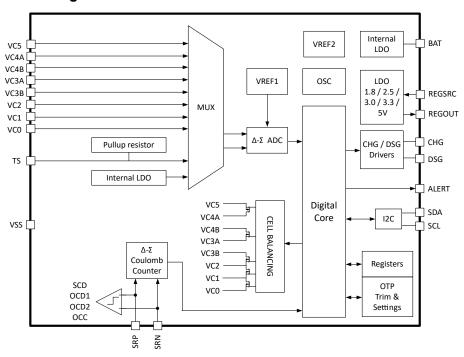

The BQ76905 device includes one-time-programmable (OTP) memory which TI programs to configure default device operation settings, for systems where a host processor is not available to configure the device. A 400-kHz I<sup>2</sup>C communication interface and ALERT interrupt output enable communication with a host processor. The device includes support for one external thermistor as well as an internal die temperature measurement. Figure 2-1 shows the BQ76905 block diagram.

## 2.2 Functional Block Diagram

Figure 2-1. BQ76905 Block Diagram

Device Description www.ti.com

This page intentionally left blank.

#### 3.1 Direct Commands and Subcommands

The BQ76905 device includes support for direct commands and subcommands. The direct commands are accessed using a 7-bit command address that is sent from a host through the device serial communications interface and either triggers an action, or provides a data value to be written to the device, or instructs the device to report data back to the host. Subcommands are additional commands that are accessed indirectly using the 7-bit command address space and provide the capability for block data transfers.

When a subcommand is initiated, a 16-bit subcommand address is first written to the 7-bit command addresses 0x3E (lower byte) and 0x3F (upper byte). The device initially assumes a read-back of data is needed and auto-populates existing data into the 32-byte transfer buffer (which uses 7-bit command addresses 0x40–0x5F), and writes the checksum for this data into address 0x60. If the host instead intends to write data into the device, the host overwrites the new data into the transfer buffer, a checksum for the data into address 0x60, and the data length into address 0x61.

As soon as address 0x61 is written, the device checks the checksum written into 0x60 with the data written into 0x40-0x5F, and if this is correct, it proceeds to transfer the data from the transfer buffer into the device's memory. The checksum is the 8-bit modulo-256 sum of the subcommand bytes (0x3E and 0x3F) and the bytes used in the transfer buffer, then the result is bitwise inverted. The verification cannot take place until the data length is written, so the device realizes how many bytes in the transfer buffer are included. The data length must be written last, after the checksum has been written (they do not need to be written together as a word).. The data length includes the two bytes in 0x3E and 0x3F, the two bytes in 0x60 and 0x61, and the length of data in the transfer buffer. Therefore, if the entire 32-byte transfer buffer is used, the data length is 0x24.

When the data length in 0x61 is read, the device automatically increments the address presently in 0x3E and 0x3F by 0x0020, and populates the transfer buffer with new readback data. This allows large portions of data memory to be read by continuous reading of the address space 0x40 to 0x61. If the host attempts to read the transfer buffer data starting at 0x40 while the device is still loading the data into the transfer buffer, the device clock stretches the I2C read transaction until the data is available.

Some subcommands are only used to initiate an action and do not involve sending or receiving data. In these cases, the host can simply write the subcommand into 0x3E and 0x3F, it is not necessary to write the length and checksum or any further data. Note that if an auto-incremented address corresponds to a subcommand that does not involve data, the auto-incrementing does not cause that subcommand to be initiated.

The commands supported in the device are described in Commands and Subcommands. Single-byte commands are direct commands, while two-byte commands are subcommands. Data formats are described in Data Formats.

The most efficient approach to read the data from a subcommand (to minimize bus traffic) is shown below:

- Write lower byte of subcommand to 0x3E.

- 2. Write upper byte of subcommand to 0x3F.

- 3. Read back the subcommand from 0x3E and 0x3F, which echoes back the subcommand address sent in steps 1 and 2 (or the auto-incremented address from step 6).

- 4. Read buffer starting at 0x40 for the expected length (reading the full 32 bytes is also acceptable).

- 5. Read the checksum at 0x60 and verify it matches the data read over the length specified by the subcommand.

Device Configuration www.ti.com

6. If auto-incrementing is desired, read the data length at 0x61, at which point the device increments the address in 0x3E and 0x3F by 32 and repopulate the buffer with the next 32 bytes of data, then go to step 2.

#### Note

0x61 provides the length of the buffer data plus 4 (that is, length of the buffer data plus the length of 0x3E and 0x3F plus the length of 0x60 and 0x61).

The checksum is calculated over 0x3E, 0x3F, and the length of buffer data specified by the subcommand, it does not include the checksum or length in 0x60 and 0x61.

Write command or subcommand bits denoted RSVD\_0 only as a "0". Write bits denoted RSVD\_1 only as a "1".

# 3.2 Configuration Using OTP or Registers

The BQ76905 device includes Data Memory registers with values stored in digital logic, as well as one-time programmable (OTP) memory, which holds device trim information and default settings for registers. At initial power-up or after a reset, the device loads the OTP settings into registers, which are used by the device logic during operation. The device can also perform a reset on demand if the 0x0012 RESET() subcommand is sent.

The OTP memory is written by TI during device manufacturing and cannot be modified by the customer. A customized OTP configuration can be developed and programmed into a custom device by TI, depending on business terms. For example, with the appropriate OTP configuration the device can power up, load settings from OTP, and operate autonomously without needing host processor support. If interested in this option, please contact TI for further discussion.

For other cases, a host processor generally initializes registers after power up or reset, but registers need to be re-initialized after each power cycle or reset of the device. Register values are preserved while the device is in NORMAL, SLEEP, or DEEPSLEEP modes. If the device enters SHUTDOWN mode or a reset occurs, all register memory is cleared, and the device returns to the default parameters when powered again. Even if TI has provided a device with a customized OTP, the customer can still modify register values in system after power-up, in case a different setting is required.

The OTP memory also includes a digital signature, which is stored in OTP. When the device is first powered or after a reset, it reads the OTP settings and check that the signature matches that stored, to provide robustness against bit errors in reading or corruption of the memory. If a signature error is detected, the device enters SHUTDOWN mode.

#### 3.3 Data Formats

0

#### 3.3.1 Unsigned Integer

Unsigned integers are stored without changes as 1-byte, 2-byte, or 4-byte values in little endian byte order.

U1 MSB 0 1 U2 U2 **MSB** LSB 0 2 3 1 U4 L U4 H U4 L U4 H LSB **MSB** LSB **MSB**

#### 3.3.2 Integer

Integer values are stored in 2's-complement format in 1-byte, 2-byte, or 4-byte values in little endian byte order.

www.ti.com Device Configuration

0

| <b>I</b> 1 |  |

|------------|--|

| MSB        |  |

0 1

| 12  | 12  |

|-----|-----|

| LSB | MSB |

0 1 2 3

| 14 L | 14 L | 14 H | 14 H |

|------|------|------|------|

| LSB  | MSB  | LSB  | MSB  |

# 3.3.3 Hex

Bit register definitions are stored in unsigned integer format.

Device Configuration www.ti.com

This page intentionally left blank.

The BQ76905 device includes two security modes: SEALED and FULLACCESS, which can be used to limit the ability to view or change settings.

In SEALED mode, most data and status can be read using commands and subcommands, but only selected settings can be changed. Data memory settings cannot be read or changed directly.

FULLACCESS mode includes SEALED mode functionality, adds the ability to execute additional subcommands, and provides capability to read and modify all device settings.

Selected settings in the device can be modified while the device is in operation through supported commands and subcommands, but in order to modify all settings, the device must enter CONFIG\_UPDATE mode, which stops device operation while settings are being updated. After the update is completed, device operation is restarted using the new settings. CONFIG\_UPDATE mode is only available in FULLACCESS mode.

The BQ76905 device implements a key-access scheme to move from SEALED to FULLACCESS mode. A unique set of keys must be sent to the device through the subcommand address (0x3E and 0x3F). The keys must be sent consecutively to 0x3E and 0x3F, with no other data written between the keys. Do not set the two keys to identical values, and it is recommended to not use keys which are identical to subcommand addresses. When in SEALED mode, the 0x12 Battery Status()[SEC1, SEC0] bits are set to [1, 1]. When the FULLACCESS keys are correctly received by the device, the bits are set to [0, 1]. The state [0, 0] is not valid and only indicates that the state has not yet been loaded. The state [1, 0] is also not valid.

The FULLACCESS keys are stored in data memory in **Security:Full Access Key Step 1** and **Security:Keys:Full Access Key Step 2**. The access keys are changed during operation using the *0x0035 SECURITY\_KEYS()* subcommand. This subcommand enables a R/W of the 2 key words (4 bytes). Each word is sent in little endian order using this subcommand.

When using the codes by writing them to 0x3E and 0x3F, they must be sent in little endian order; therefore, if 0x1234 and 0x5678 are written as the FULLACCESS codes to 0x0035 SECURITY\_KEYS(), then to unseal requires writing 0x34 and 0x12 to 0x3E and 0x3F, followed by writing 0x78 and 0x56 to 0x3E and 0x3F. The two codes must be written within 5 s of each other to succeed.

To read the keys (only available in FULLACCESS mode, assume for example the keys are 0x1234 0x5678):

- 1. Write 0x35 and 0x00 to 0x3E and 0x3F

- 2. Read back 4 bytes from the transfer buffer at 0x40–0x43 (for example, 0x34 0x12 0x78 0x56).

To write the keys (only available in FULLACCESS mode):

- Write 0x35 and 0x00 to 0x3E and 0x3F.

- 2. Write the data in little endian format to the transfer buffer at 0x40–0x43 (for example, 0x34 0x12 0x78 0x56).

- 3. Write the checksum to 0x60. The checksum is calculated by inverting the modulo-256 sum of the data and command bytes (for example, 0xB6).

- 4. Write the length of 0x08 to 0x61. The length includes the command, data, checksum, and length bytes.

To set the device into SEALED mode when initially powering up, the **Security:Security Settings[SEAL]** configuration bit must be programmed into OTP. During operation, a device in FULLACCESS mode can be put into SEALED mode by sending the *0x0030 SEAL()* subcommand.

Device Security www.ti.com

The BQ76905 device includes additional means to limit further modification of device settings. If the **Security:Security Settings[LOCK\_CFG]** configuration bit is set, the data memory settings can no longer be modified when the device exits CONFIG\_UPDATE mode. If the **Security:Security Settings[PERM\_SEAL]** bit is set, the device cannot be unsealed after it has been sealed. If these bits are not set in OTP, the settings are lost on a full reset and the device is again able to unseal and modify data memory.

# Measurement Subsystem

## 5.1 Voltage Measurement

The BQ76905 device integrates a voltage ADC which is multiplexed between measurements of cell voltages, an internal temperature sensor, the TS pin, and also performs measurements of the voltage at the VC5 pin, the internal 1.8-V LDO (REG18) voltage, and the VSS rail (for diagnostic purposes). The BQ76905 device supports measurement of individual differential cell voltages in a series configuration, ranging from 2 series cells to 5 series cells. Each cell voltage measurement is a differential measurement of the voltage between two adjacent cell input pins, such as VC1-VC0, VC2-VC1, and so forth. The cell voltage measurements are processed based on trim corrections, and then reported in 16-bit resolution using units of 1 mV. The cell voltage measurements can support a recommended voltage range from -0.2 V to 5.5 V. The voltage ADC saturates at a level of 5 × VREF1 (approximately 5.98 V) when measuring cell voltages, although for best performance it is recommended to stay at a maximum input of 5.5 V.

The 16-bit cell and VC5 (Stack), VSS pin, and REG18 voltage measurements are available by using the commands listed below.

| Command       | Name                    | Unit             |

|---------------|-------------------------|------------------|

| 0x14 and 0x15 | Cell 1 Voltage          | mV               |

| 0x16 and 0x17 | Cell 2 Voltage          | mV               |

| 0x18 and 0x19 | Cell 3 Voltage          | mV               |

| 0x1A and 0x1B | Cell 4 Voltage          | mV               |

| 0x1C and 0x1D | Cell 5 Voltage          | mV               |

| 0x22 and 0x23 | REG18 Voltage           | 16-bit ADC codes |

| 0x24 and 0x25 | VSS Voltage             | 16-bit ADC codes |

| 0x26 and 0x27 | Stack (VC5 pin) voltage | 1 mV (unsigned)  |

| 0x28 and 0x29 | Int Temperature         | °C               |

| 0x2A and 0x2B | TS Measurement          | 16-bit ADC codes |

Table 5-1. Commands to Read 16-Bit Voltage Measurements

#### **5.1.1 Voltage Measurement Schedule**

#### Overview

The voltage ADC and associated mux operates on a measurement loop in order to implement all its required measurements. The schedule is different in NORMAL versus SLEEP mode (there are no measurements in DEEPSLEEP or SHUTDOWN modes).

#### **NORMAL Mode Scheduling**

The measurement loop in NORMAL mode consists of a fast ADSCAN loop, which consists of up to 6 separate measurement slots. The width of the measurement slots is independently programmable based on the category of measurement - cell voltage measurement vs other measurements. By programming the width of the slot, the effective resolution of the ADC conversion changes with it. The slot width is programmable as 366  $\mu$ s (fastest but lowest resolution), 732  $\mu$ s, 1.46 ms, or 2.93 ms (slowest but highest resolution). The schedule of

conversions while in NORMAL mode is described in the tables below. If a device is configured to use fewer than the maximum number of supported series cells (such as the device being used in a 3s system), the schedule is shortened accordingly. This results in the number of slots in an ADSCAN in NORMAL mode being (number of cells used) + 1.

Table 5-2. NORMAL Mode Voltage ADC ADSCAN Measurement Loop (setup for a 5s configuration)

| Slot Number | Selected Input |

|-------------|----------------|

| 0           | Cell-1 Voltage |

| 1           | Cell-2 Voltage |

| 2           | Cell-3 Voltage |

| 3           | Cell-4 Voltage |

| 4           | Cell-5 Voltage |

| 5           | Shared Slot    |

Table 5-3. NORMAL Mode Voltage ADC ADSCAN Measurement Loop (setup for a 2s configuration)

| Slot Number | Selected Input |

|-------------|----------------|

| 0           | Cell-1 Voltage |

| 1           | Cell-2 Voltage |

| 2           | Shared Slot    |

The additional measurements that are less speed critical use the Shared Slot, which rotates through a series of five less frequent measurements. The completion of one full rotation through all five of these less frequent measurements (one per ADSCAN loop) is termed a FULLSCAN loop. The items measured in the FULLSCAN using the Shared Slot are shown in the table below. This schedule uses 5 ADSCANs to complete one FULLSCAN to provide updated data for all less frequent measurements. The timing of a FULLSCAN loop depends on the timing of the ADSCAN loop and can range from approximately 5.5 ms to approximately 88 ms (and longer based on the *LOOP\_SLOW* settings described below).

Table 5-4. NORMAL Mode Voltage Schedule - FULLSCAN Shared Slot Usage

| Shared Slot Usage    | Description                                                                                                                                                                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TS                   | Measurement of TS pin voltage, which can be configured in thermistor mode (with internal pullup enabled and using internal 1.8-V LDO as reference) or general purpose ADCIN mode (with internal pullup disabled and using bandgap reference) |

| Internal Temperature | Measurement of delta-VBE                                                                                                                                                                                                                     |

| Stack                | Top of stack voltage (VC5 pin) vs VSS, using resistive divider only switched on during measurement.                                                                                                                                          |

| VREF                 | Measurement of the internal REG18 LDO voltage                                                                                                                                                                                                |

| VSS                  | Measurement of the VSS pin voltage                                                                                                                                                                                                           |

The measurement of the internal REG18 LDO voltage (which is set based on VREF2) provides an output code given by REG18 × 32768 × 2 / 5 / VREF1, which results in a nominal value of 19228.

The BQ76905 also includes an option to slow the measurement loop if active power dissipation is more important than speed of data availability. The loop can be slowed by up to 8x in NORMAL mode using the **Settings:Configuration:Power Config[LOOP\_SLOW[1:0]]** bits, which cause the voltage ADC to insert idle slots to effectively slow the average conversion speed and thus reduces the device's average power dissipation. See below for how these bits control the schedule. The idle slots are inserted in a contiguous group at the end of each active ADSCAN, not interleaved between each active conversion slot, to ensure that cell voltage measurements are taken as closely together as possible. The **LOOP\_SLOW** setting does not affect the schedule during SLEEP mode.

www.ti.com Measurement Subsystem

#### Table 5-5. LOOP\_SLOW Speed Control

| LOOP_SLOW[1] | LOOP_SLOW[0] | Loop Speed                                                                  |

|--------------|--------------|-----------------------------------------------------------------------------|

| 0            | 0            | Loop runs at full speed                                                     |

| 0            | 1            | Loop runs at half speed (one idle slot included for each active slot)       |

| 1            | 0            | Loop runs at quarter speed (three idle slots included for each active slot) |

| 1            | 1            | Loop runs at eighth speed (seven idle slots included for each active slot)  |

#### **SLEEP Mode Scheduling**

When the device is in SLEEP mode, measurements are only taken in a burst every **Power:Sleep:Voltage Time** interval. Between these bursts, the ADC remains idle, to save power. When the timer expires, the device takes all measurements in a long burst. These are implemented as shown in the table below. When fewer than 5 cells are being used, the unused cell voltage slots are removed. This results in the SLEEP schedule length in slots = 5 + (number of cells used).

Table 5-6. SLEEP Mode Measurement Schedule (all 5 cells used)

| Slot | Description                      |

|------|----------------------------------|

| 0    | Cell-1 Voltage                   |

| 1    | Cell-2 Voltage                   |

| 2    | Cell-3 Voltage                   |

| 3    | Cell-4 Voltage                   |

| 4    | Cell-5 Voltage                   |

| 5    | TS pin measurement               |

| 6    | Internal Temperature measurement |

| 7    | Stack measurement                |

| 8    | REG18 measurement                |

| 9    | VSS measurement                  |

When a burst measurement is complete, the device sets the ADSCAN and FULLSCAN bits in *Alarm Raw Status()* momentarily.

When the device exits SLEEP mode (whether through current detection or command or a protection), it immediately runs a SLEEP mode burst measurement to collect updated data, then begins the NORMAL mode schedule. If a burst measurement is already in progress when the exit is triggered, that burst is completed and then the device begins the NORMAL mode schedule.

#### Startup Mode Scheduling

When the device first boots from SHUTDOWN or exits DEEPSLEEP or CONFIG\_UPDATE modes, a special fast startup schedule is used, which is similar to the SLEEP mode schedule, but with fixed OSR settings, as shown below. This schedule results in approximately 6 ms ADC conversion time, in addition to the time required for the REG18 LDO to power up from SHUTDOWN. The device then transitions to evaluating the protections, so the FETs can be enabled as quickly as possible. This measurement loop and evaluation completion trigger the INITCOMP bit in *Alarm Raw Status()*. If the host intends to manually enable the FET drivers, it can monitor this signal to determine when the startup data is available for reading.

Table 5-7. Startup Mode Measurement Schedule (5s version)

| Slot | Description    | ADC OSR |

|------|----------------|---------|

| 0    | Cell-1 Voltage | 96      |

| 1    | Cell-2 Voltage | 96      |

| 2    | Cell-3 Voltage | 96      |

| 3    | Cell-4 Voltage | 96      |

Table 5-7. Startup Mode Measurement Schedule (5s version) (continued)

| Slot | Description                      | ADC OSR |

|------|----------------------------------|---------|

| 4    | Cell-5 Voltage                   | 96      |

| 5    | TS pin measurement               | 384     |

| 6    | Internal Temperature measurement | 384     |

| 7    | Stack measurement                | 96      |

| 8    | REG18 measurement                | 96      |

| 9    | VSS measurement                  | 96      |

If the device has been configured for a fewer number of cells being used (such as configured for use with only 2 cells being used), the startup sequence is shortened by skipping unused cell measurements. If the device is powering from SHUTDOWN mode, it determines the cell configuration based on the settings read in from OTP. If the device is exiting DEEPSLEEP or CONFIG\_UPDATE mode, it uses the cell configuration information previously loaded, either from OTP at power up or modified by the host.

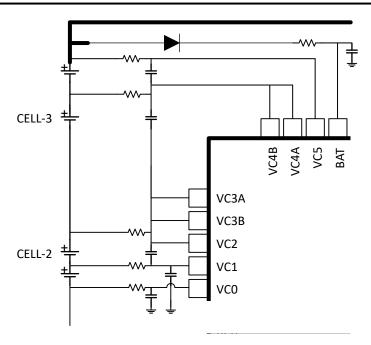

# 5.1.2 Unused VC Cell Input Pins

If the BQ76905 device is used in a system with fewer than 5 series cells, specific cells must be used for connection to real cells, as shown in Table 5-8. Short out the unused cell inputs on the circuit board. The device only measures and reports those cells designated as real cells. For example, if only two cells are used (which requires cell-1 connected between VC1 - VC0, and cell-2 connected between VC5 - VC4A), the 0x12 Cell 1 Voltage() command reports the lower cell voltage, while the 0x14 Cell 2 Voltage() command reports the upper cell voltage.

Table 5-8. Cell Usage

| Number of Cell Used (Vcell Mode setting) | Cell Connections                                    | Shorted Cells                                         |

|------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|

| 0, 1, or ≥ 5                             | VC5–VC4A, VC4B–VC3A, VC3B–VC2, VC2–<br>VC1, VC1–VC0 | VC4A–VC4B, VC3A–VC3B                                  |

| 4                                        | VC5–VC4A, VC4B–VC3A, VC2–VC1, VC1–<br>VC0           | VC4A–VC4B, VC3A–VC3B, VC3B–VC2                        |

| 3                                        | VC5–VC4A, VC2–VC1, VC1–VC0                          | VC4A–VC4B, VC4B–VC3A, VC3A–VC3B,<br>VC3B–VC2          |

| 2                                        | VC5-VC4A, VC1-VC0                                   | VC4A–VC4B, VC4B–VC3A, VC3A–VC3B,<br>VC3B–VC2, VC2–VC1 |

#### Note

It is important that the differential input for each cell input not fall below -0.3 V (the Absolute Maximum data sheet limit), with the recommended minimum voltage of -0.2 V. Therefore, it is important that the I·R voltage drop across the interconnect resistance does not cause a violation of this requirement.

Short the unused cell input pins to adjacent cell input pins, as shown in Figure 5-1.

It is also important to note that the range of voltages supported by the different VC pins differs depending on the pin. For example, pins VC5, VC4A, and VC4B can only support measurements if their pin voltage is greater than or equal to 2 V. Thus if implementing a 2s system using the top and bottom cell input pins, the upper cell voltage is not measured correctly if the lower cell voltage drops below 2 V, because then VC4A is below 2 V.

www.ti.com Measurement Subsystem

Figure 5-1. Connecting an Unused Cell Input Pin

The **Settings:Configuration:Vcell Mode** data memory setting is used to specify which cell inputs are used for actual cells. The device uses this information to disable cell voltage protections associated with inputs which are not used. Voltage measurements are reported in 16-bit format (in units of mV) only for inputs used for real cells.

#### 5.1.3 General Purpose ADCIN Functionality

The TS pin on the BQ76905 device can be used for general purpose ADC input (ADCIN) measurement, if not being used for temperature measurement of a thermistor. When used for ADCIN functionality, the internal VREF1 reference is used by the ADC, and the input range of the ADC is limited to 1.8 V. The digital full-scale range of the ADC is effectively 1.6667 × VREF1, which is approximately 2 V during normal operation.

The **Settings:Configuration:DA Config[TSMODE]** data memory bit controls whether the TS pin is used for a thermistor or as a general purpose ADC input. The resulting measurement of the TS pin is available using the TS Measurement() command in units of 16-bit ADC counts. The LSB size of the ADC counts is given by VREF1  $\times$  5 / 3 / 32768  $\cong$  61  $\mu$ V.

## 5.2 Coulomb Counter and Digital Filters

The BQ76905 device monitors pack current using a low-side sense resistor that connects to the SRP and SRN pins through an external RC filter, which must be connected such that a charging current creates a positive voltage on SRP relative to SRN. The device supports a wide range of sense resistor values, such as 1 m $\Omega$  or below. The differential voltage between SRP and SRN is digitized by a dedicated integrated coulomb counter ADC, which can digitize voltages over a ±200 mV range. The pins can also support higher positive voltages relative to VSS, which can occur during overcurrent or short circuit in discharge conditions, without damage to the device, although the current is not accurately digitized in this case.

#### **Current Measurement Data**

The coulomb counter provides two digital outputs, one of which uses the CC2 digital filter, which generates a 24-bit raw output. The timing and resolution of the CC2 output is programmable, with the output rate also affecting the resolution of the conversion. The effective resolution (defined as the resolution such that the data exhibits 1-sigma variation with  $\pm 1$  LSB) of the coulomb counter conversions increases with longer conversion time. The conversion time options when the coulomb counter is in full power mode are 366  $\mu$ s (which results in 13-bit effective resolution), 732  $\mu$ s (14-bit effective resolution), 1.46 ms (15-bit effective resolution), or 2.93 ms (16-bit

effective resolution). This conversion time is set using the **Settings:Configuration:DA Config[IADCSPEED1:0]** configuration bits. In addition, the coulomb counter supports a low power mode, which operates at a 16 times slower rate than the settings listed above, with similar resolution performance at each setting, but with supply current reduced by approximately  $55 \, \mu A$ .

This 24-bit CC2 value is reported in the 0x36 Raw Current() command. This command provides 24 bits of data in the LSBs, which is sign-extended to generate the upper 8 bits of the 32-bit field. While this data provides additional resolution for current measurement if desired,there can be considerable noise in the lower bits, so the data might need further filtering by the host before use. The 32-bit current data has an LSB value of approximately VREF2 /  $(5 \times 2^{23}) \cong 1.227$  V /  $(5 \times 2^{23}) \cong 29$  nV. Note that the data provided by the 0x36 Raw Current() command is not processed for offset or gain correction.

The 24-bit raw coulomb counter output is further processed, with the result reported in 16-bit format by the 0x3A Current() command in units of 16-bit userA. The processing consists of first subtracting an offset value (Calibration:Current:Curr Offset) from the 24-bit raw ADC result, then multiplying that result by a gain factor (Calibration:Current:Curr Calibration:Current:Curr Calibration:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Current:Cur

If a different sense resistor value is used, the host can modify the value of *Calibration:Current:Curr Gain* to adjust the units of the *0x3A Current()* command, depending on the range of currents expected in the system. Thus the units of each LSB are termed "userA" based on the gain setting. Since the *0x3A Current()* command reports signed 16-bit data, units of mA would only allow reporting of currents between -32768 mA and +32767 mA. If larger currents are expected, then the gain can be adjusted to set the LSB userA to a different value, such as 10 mA or 100 mA, which then allows reporting of currents between -327.68 A and +327.67 A (if userA = 10 mA) or between -3276.8 A and +3276.7 A (if userA = 100 mA).

The device also reports a 16-bit current which is measured primarily for charge integration purposes in 0x3C CC1 Current(), with units adjustable in similar fashion as the 0x3A Current(). In this case, the raw data is 16-bit, so the processing consists of first subtracting an offset value (Calibration:Current:CC1 Current:CC1 Current:C

The 0x3C CC1 Current() only operates in NORMAL mode, and generates a sample every 250 ms when the coulomb counter is in full power mode, or every 4 seconds in low power mode (as determined by the **Settings:Configuration:DA Config[CCMODE1:0]** setting). The 0x3C CC1 Current() is used to decide when the device enters SLEEP mode and for accumulated charge integration.

#### **Body Diode Protection**

The BQ76905 supports both series and parallel FET configurations. When the CHG and DSG FETs are in series, current can flow through the body diode of a disabled FET when the other FET is enabled. In this configuration, body diode protection is used to turn the disabled FET on when current above a threshold is detected to be flowing through that FET. When the system has separate DSG and CHG paths and parallel FETs, body diode protection is not needed and can be disabled by clearing the **Settings:Configuration:FET Options[SFET]** configuration bit.

The body diode protection is implemented in most cases using the digitized current data from the coulomb counter. Except for special cases, the device compares the absolute value of *0x3A Current()* to the body diode protection threshold given by **Settings:Protection:Body Diode Threshold**. If one FET is disabled and one is

www.ti.com Measurement Subsystem

enabled, and the absolute value of 0x3A Current() exceeds the threshold, and [SFET] = 0x1, then the disabled FET is enabled.

If **Settings:Configuration:DA Config[CCMODE1:0]** = 0x3, then the body diode protection instead uses the wake detector signal to decide whether or not to enable the disabled FET. This means the device uses the wake detector threshold for the body diode protection in these cases, so **Settings:Protection:Body Diode Threshold** is not used.

In order to avoid rapid cycling of a FET driver when the current is near the threshold, the FET enabled by body diode protection is not disabled again due to unneeded body diode protection until after a hysteresis time of approximately 240 ms has passed since the FET was initially enabled. This hysteresis does not apply if a protection fault occurs and the device is configured to disable the FET, or if a command to manually disable the FET is sent. In these cases the FET turns off immediately without observing the hysteresis.

#### **Current Measurement Schedule**

The schedule for current measurements depends on programmable settings as well as the operating mode of the device (such as whether the device is in SLEEP mode versus NORMAL mode). This programmability, which uses the **Settings:Configuration:DA Config[CCMODE1:0]**, allows the power dissipation of the device to be reduced if fast current measurements are not required in the system.

Table 5-9. Coulomb Counter Mode Control (Settings:Configuration:DA Config[CCMODE1:0])

| CCMODE[1] | CCMODE[0] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | 0         | NORMAL mode: Coulomb counter runs continuously, independent of the <i>LOOP_SLOW</i> or <i>CB_LOOP_SLOW</i> setting.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |           | SLEEP mode: Coulomb counter runs continuously while the voltage ADC is running in SLEEP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |           | during a burst measurement. It stops at the conclusion of the CC2 measurement underway when the burst measurement completes.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |           | Startup mode (at initial powerup from SHUTDOWN or exit of DEEPSLEEP or CONFIG_UPDATE mode):                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |           | Coulomb counter runs continuously while the voltage ADC is running during the Startup Sequence. It stops at the conclusion of the CC2 measurement underway when the Startup Sequence completes.                                                                                                                                                                                                                                                                                                                                                                  |

|           |           | 0x3C CC1 Current() and accumulated charge and time integration are updated in NORMAL mode but not in SLEEP mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |           | Body diode protection uses the coulomb counter CC2 digitized current data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0         | 1         | NORMAL mode: Coulomb counter runs continuously if <i>LOOP_SLOW</i> or <i>CB_LOOP_SLOW</i> is set to the fastest setting. When these parameters are modified to slower settings, the device inserts 1, 3, or 7 idle slots between each current measurement slot, thereby reducing the average output rate of the current measurements.  SLEEP mode: Coulomb counter runs continuously while the voltage ADC is running in SLEEP mode during a burst measurement. It stops at the conclusion of the CC2 measurement underway when the burst measurement completes. |

|           |           | Startup mode (at initial powerup from SHUTDOWN or exit of DEEPSLEEP or CONFIG_UPDATE mode):  Coulomb counter runs continuously while the voltage ADC is running during the Startup Sequence. It stops at the conclusion of the CC2 measurement underway when the Startup Sequence completes.                                                                                                                                                                                                                                                                     |

|           |           | Ox3C CC1 Current() and accumulated charge and time integration are only updated when in NORMAL and not using a mode that inserts idle slots into the voltage measurement schedule. These are not updated in SLEEP mode.  Body diode protection uses the coulomb counter CC2 digitized current data.                                                                                                                                                                                                                                                              |

Table 5-9. Coulomb Counter Mode Control (Settings:Configuration:DA Config[CCMODE1:0]) (continued)

| CCMODE[1] | CCMODE[0] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | 0         | NORMAL mode: Coulomb counter runs continuously in low power mode (CC1 and CC2 measurements take 16x longer versus in regular full power mode)  SLEEP mode: Coulomb counter takes one CC2 measurement at the beginning of each burst measurement using low power mode.  Startup mode (at initial powerup from SHUTDOWN or exit of DEEPSLEEP): Coulomb counter takes one CC2 measurement using low power mode at the beginning of the Startup Sequence.  0x3C CC1 Current() and accumulated charge and time integration are only updated with this setting while in NORMAL mode, they are not updated in SLEEP mode. The 0x3C CC1 Current() and charge integration is updated every approximately 4 seconds in NORMAL mode using this setting, due to the slower clock rate. The charge integration scales the CC1 Current appropriately when accumulating, to maintain the same units of userA-seconds.  Body diode protection uses the coulomb counter CC2 digitized current data. |

| 1         | 1         | Coulomb counter is powered down and does not operate at all. This provides a low power mode if current measurement is not needed. <i>0x3C CC1 Current()</i> and accumulated charge and time integration are not available in this mode.  In this mode, body diode protection is based on the wake comparator detection threshold, which also serves as the detector to enter/exit SLEEP mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### **Charge Integration**

When the *0x3C CC1 Current()* is operating, it is integrated to calculate the accumulated passed charge, with the integrated charge available as a signed 48-bit value from the *0x0004 PASSQ()* subcommand. The first 32-bits contains the 32 LSBs of the accumulated charge in units of userA-seconds, and the next 32-bits contain the upper 16 bits of the 48-bit result sign-extended to fill the 32-bit field. In addition, a timer value with units of 250 ms is available in a 32-bit value from the subcommand, which counts the time the device is in NORMAL mode since the integrator was reset. Neither the time nor the charge integration operate in SLEEP, DEEPSLEEP, or SHUTDOWN modes, only in NORMAL mode and based on the setting of *Settings:Configuration:DA Config[CCMODE1:0]*. The integrator and timer is reset by sending the *0x0005 RESET\_PASSQ()* subcommand. These are also reset upon entering CONFIG\_UPDATE mode. When the coulomb counter is in low power mode, it only generates a CC1 current output every 4 seconds, so the charge and time integration is also updated at these intervals. The integration of *0x3C CC1 Current()* is scaled accordingly when in low power mode, to provide accumulated charge using the same units of userA-seconds as in full power mode.

Table 5-10. Accumulated Charge and Time (from PASSQ() subcommand)

| Subcommand<br>Address | Rytes within Block Name |                                                                                      | Units                                                                                           |

|-----------------------|-------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                       | 0 - 3                   | Accumulated charge lower 32-bits (little-<br>endian)                                 | Lower 32 bits of signed 48-bit result, with the full 48-bit field having units of userA-seconds |

| 0x0004                | 4 - 7                   | Accumulated charge upper 16-bits sign-<br>extended to a 32-bit field (little-endian) | Upper bits of signed 48-bit result, with the full 48-bit field having units of userA-seconds    |

|                       | 8 - 11                  | Accumulated Time (little-endian)                                                     | 32-bit unsigned integer in units of 250 ms                                                      |

# **5.3 Internal Temperature Measurement**

The BQ76905 device integrates the capability to measure its internal die temperature by digitizing the difference between two internal transistor base-emitter voltages. This voltage difference is measured periodically as part of the measurement loop and is processed to provide a temperature value using the *0x28 Int Temperature()* command in units of °C. This resulting value is used by several protections and decisions within the device, such as the Internal Overtemperature Protection, internal overtemperature shutdown (based on *Power:Shutdown:Shutdown Temperature*, and cell balancing (based on *Settings:Cell Balancing:Max Internal Temp*).

26

www.ti.com Measurement Subsystem

The calculation of temperature is performed as follows using the *Calibration:Temperature:Int Temp Offset* and *Calibration:Temperature:Int Temp Gain* configuration parameters:

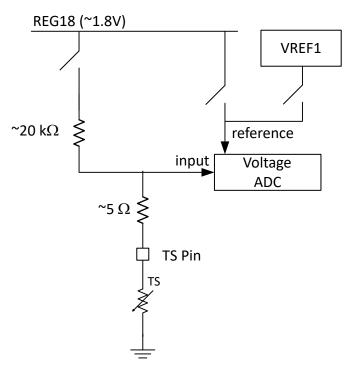

#### **5.4 Thermistor Temperature Measurement**

The BQ76905 device includes an on-chip temperature measurement and can also support measurement of an external thermistor on the TS pin. The device includes an internal trimmed  $20\text{-k}\Omega$  pullup resistor to bias the thermistor during measurement. The TS pin can be selected for thermistor measurement or general purpose ADCIN measurement using the **Settings:Configuration:DA Config[TSMODE]** data memory setting.

When the pin is selected for thermistor measurement, the internal pullup resistor is used to bias the pin during the measurement. In order to provide a high precision result, the device uses the same 1.8 V internal LDO voltage for the ADC reference as is used for biasing the thermistor pullup resistor, thereby implementing a ratiometric measurement that removes the error contribution from the LDO voltage level. Because the pullup resistor is only enabled during the pin measurement, it is recommended to limit the capacitance at this node to less than 4 nF to reduce the effect of incomplete settling when the pullup resistor is biased.

If the pin is selected for general purpose ADCIN measurement, the pullup resistor is not enabled during measurement, and the ADC uses VREF1 for its reference when measuring the pin.

The data is reported using the *TS Measurement()* command, in units of 16-bit ADC counts. The full-scale digital value reflects an analog input level of its reference × 5 / 3. So when the TS pin is measuring a thermistor in ratiometric mode using the 1.8V internal regulator for its reference, the 16-bit LSB is 1.8 V × 5 / 3 / 32768  $\cong$  92  $\mu$ V. When the TS pin is measuring in ADCIN mode using the VREF1 reference, the 16-bit LSB is 1.1962 V × 5 / 3 / 32768  $\cong$  61  $\mu$ V. The processing performed on the ADC data before reporting is shown below, using the *Calibration:Temperature:TS Offset* data memory parameter.

TS Measurement() = (16-bit ADC counts) – (TS Offset)

#### 5.5 Measurement Calibration

The BQ76905 device includes optional capability for the customer to calibrate offset and gain for the cell voltage measurement, the current measurement, and the internal temperature measurement. It also supports gain calibration for the top-of-stack (TOS) voltage measurement and offset calibration for the TS pin measurement. Table Table 5-11 shows the calibration configuration values provided.

Table 5-11. Calibration Configuration Settings

| Name                                  | Description                                                                                                                                                 |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calibration:Voltage:Cell 1 Gain       | Cell 1 voltage gain calibration value in unsigned 16-bit format                                                                                             |

| Calibration:Voltage:Cell 2 Gain Delta | Signed 8-bit value which is added to Cell 1 Gain to obtain the Cell 2 Gain calibration value.                                                               |

| Calibration:Voltage:Cell 3 Gain Delta | Signed 8-bit value which is added to Cell 1 Gain to obtain the Cell 3 Gain calibration value.                                                               |

| Calibration:Voltage:Cell 4 Gain Delta | Signed 8-bit value which is added to Cell 1 Gain to obtain the Cell 4 Gain calibration value.                                                               |

| Calibration:Voltage:Cell 5 Gain Delta | Signed 8-bit value which is added to Cell 1 Gain to obtain the Cell 5 Gain calibration value.                                                               |

| Calibration:Voltage:TOS Gain          | Top-of-stack (TOS) voltage gain calibration value in unsigned 16-bit format                                                                                 |

| Calibration:Current:Curr Offset       | Current offset calibration value in units of signed 24-bit ADC counts (this is a 16-bit value, so only has range of +/- full-scale raw current range / 256) |

| Calibration:Current:Curr Gain         | Current gain calibration value in unsigned 16-bit format                                                                                                    |

**Table 5-11. Calibration Configuration Settings (continued)**

| Name                                    | Description                                                                                                                                                     |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calibration:Current:CC1 Offset          | CC1 Current offset calibration value in units of signed 24-bit ADC counts (this is a 16-bit value, so only has range of +/- full-scale raw current range / 256) |

| Calibration:Current:CC1 Gain            | CC1 Current gain calibration value in unsigned 16-bit format                                                                                                    |

| Calibration:Temperature:TS Offset       | TS measurement offset calibration value in units of signed 16-bit ADC counts.                                                                                   |

| Calibration:Temperature:Int Temp Offset | Internal temperature offset calibration value in units of signed 16-bit ADC counts                                                                              |

| Calibration:Temperature:Int Temp Gain   | Internal temperature gain calibration value in unsigned 16-bit format                                                                                           |

If the host does not overwrite values for the calibration gain or offset configurations, the BQ76905 device uses the factory trim values stored in OTP for each respective setting. When a calibration configuration value is written, the device uses that in place of the respective factory trim value.

Each cell voltage has an associated Cell # Gain value, which is used to scale the raw ADC result to convert it into units of mV. The *Cell 1 Gain* is stored directly in data memory, while the remaining Cell # Gain values for cells 2 to 5 are encoded as a delta value versus the *Cell 1 Gain* value, as shown below.

$$Cell \ 2 \ Gain = (Cell \ 1 \ Gain) + (Cell \ 2 \ Gain \ Delta)$$

$$\tag{1}$$

$$Cell\ 3\ Gain = (Cell\ 1\ Gain) + (Cell\ 3\ Gain\ Delta)$$

$$(2)$$

$$Cell \ 4 \ Gain = (Cell \ 1 \ Gain) + (Cell \ 4 \ Gain \ Delta)$$

$$(3)$$

$$Cell \ 5 \ Gain = (Cell \ 1 \ Gain) + (Cell \ 5 \ Gain \ Delta) \tag{4}$$

The BQ76905 uses these calibration values to calculate the reported measurements from the raw ADC data as described below.

$$Cell \ 1 \ Voltage() = \frac{[(16 - bit ADC counts) \times (Cell \ 1 \ Gain)]}{65536}$$

(5)

$$Cell \ 2 \ Voltage() = \frac{[(16 - bit ADC counts) \times (Cell \ 2 \ Gain)]}{65536}$$

(6)

$$Cell \ 3 \ Voltage() = \frac{[(16 - bit ADC counts) \times (Cell \ 3 \ Gain)]}{65536}$$

(7)

$$Cell \ 4 \ Voltage() = \frac{[(16 - bit ADC counts) \times (Cell \ 4 \ Gain)]}{65536}$$

(8)

$$Cell \ 5 \ Voltage() = \frac{[(16 - bit ADC counts) \times (Cell \ 5 \ Gain)]}{65536}$$

(9)

$$Stack\ Voltage \left( \right) = \frac{(16 - bit\ ADC\ counts) \times (TOS\ Gain)}{16384} \tag{10}$$

www.ti.com Measurement Subsystem

$$TS Measurement() = (16 - bit ADC counts) - (TS Offset)$$

(11)

$$Int Temperature \left( \right) = \frac{\left[ (16 - bit ADC counts) - (Int Temp Offset) \right] \times (Int Temp Gain)}{65536}$$

(12)

$$CC1 \ Current \left( \right) = \frac{\left[ (16 - bit \ ADC \ counts) - (CC1 \ Offset \ / \ 256) \ \right] \times (CC1 \ Gain)}{32}$$

(13)

$$Current\left(\right) = \frac{\left[\left(24 - bit\ ADC\ counts\right) - \left(Curr\ Offset\right)\right] \times \left(Curr\ Gain\right)}{8192} \tag{14}$$

The cell voltage calibration is implemented by writing the *Calibration:Voltage:Cell 1 Gain* value to 65535 and all *Calibration:Voltage:Cell # Gain Delta* values to 0, then applying two precise DC voltages to a cell input (such as 2.5 V and 4.5 V) and averaging multiple raw ADC measurements in 16-bit counts obtained from the *Cell # Voltage()* command for each voltage. The gain is then calculated as:

$$Cell # Gain = \frac{65536 \times (Voltage1_{in \ mV} - Voltage2_{in \ mV})}{(16 - bit \ ADC \ Counts)_{Voltage1} - (16 - bit \ ADC \ Counts)_{Voltage2}}$$

(15)

The calibration for the TOS measurement gain is implemented by similarly writing the *Calibration:Voltage:TOS Gain* value to 16384, then applying two precise DC voltages to the VC5 pin and averaging multiple raw ADC measurements in 16-bit counts obtained from the *0x26 Stack Voltage()* command. Note: one of the voltages can be skipped to reduce calibration time. The gain is then calculated as:

$$TOS \ Gain = \frac{16384 \times (Voltage1_{in \ mV} - Voltage2_{in \ mV})}{(16 - bit \ ADC \ Counts)_{Voltage1} - (16 - bit \ ADC \ Counts)_{Voltage2}}$$

(16)

The calibration for the TS pin measurement offset is implemented by similarly first writing the **Calibration:Temperature:TS Offset** value to zero. A precise DC voltage can be applied to the TS pin, and the 16-bit ADC counts obtained from the 0x6A TS Measurement() command. The offset is then calculated as:

$$TS\ Offset = (16 - bit\ ADC\ Counts)_{TS\_Voltage} - \frac{32768 \times 3 \times (TS\_Voltage_{in\ V})}{VREF1 \times 5} \tag{17}$$

Although it is typically not practical in a production environment, the Internal Temperature measurement can be calibrated by first writing the *Calibration:Temperature:Int Temp Gain* value to 65535 and *Calibration:Temperature:Int Temp Offset* value to zero, then exposing the system to two precise temperatures and averaging multiple raw ADC measurements in 16-bit counts obtained from the *Int Temperature()* command for each temperature. The gain is then calculated as:

$$Int Temp \ Gain = \frac{65536 \times (Temp\_1_{in} \circ_{\mathcal{C}} - Temp\_2_{in} \circ_{\mathcal{C}})}{(16 - bit \ ADC \ Counts)_{Temp\_1} - (16 - bit \ ADC \ Counts)_{Temp\_2}}$$

$$(18)$$

The offset for the Internal Temperature measurement is calculated using this new value of *Calibration:Temperature:Int Temp Gain* as shown below:

$$Int Temp \ Offset = (16 - bit \ ADC \ Counts)_{Temp\_1} - \frac{65536 \times (Temp\_1_{in} \circ C)}{Int \ Temp \ Gain} \tag{19}$$

The 0x3A Current() current measurement can be calibrated by applying two precise DC currents and averaging multiple raw ADC measurements in 24-bit counts obtained from the 0x36 Raw Current() command for each current. The 0x3C CC1 Current() current measurement, which is used to calculate the charge integration data available from the 0x0004 PASSQ() command, can be calibrated by applying two precise DC currents and

SLUUCI8 – NOVEMBER 2023 BQ76905 29

averaging multiple raw ADC measurements in 16-bit counts obtained from the 0x3C CC1 Current() command for each current, while the value of **Calibration:Current:CC1 Gain** is set to 32.

These gains are then calculated as:

$$CC1 \ Gain = \frac{32 \times (Current\_1_{in \ mA} - Current\_2_{in \ mA})}{(16 - bit \ ADC \ Counts)_{Current\_1} - (16 - bit \ ADC \ Counts)_{Current\_2}}$$

(20)

$$Curr \ Gain = \frac{8192 \times (Current\_1_{in \ mA} - Current\_2_{in \ mA})}{(24 - bit \ ADC \ Counts)_{Current\_1} - (24 - bit \ ADC \ Counts)_{Current\_2}}$$

(21)

then quantizing to an integer.

While a current measurement offset *Calibration:Current:Curr Offset* can be calculated using one of the two currents measured earlier, a more practical approach is to set the current to zero, and use the average of multiple raw ADC measurements in 24-bit counts obtained from the *0x36 Raw Current()* command as *Calibration:Current:Curr Offset*, which uses the 16 LSBs from this calculation. The value for *Calibration:Current:CC1 Offset* can be obtained by setting the *Calibration:Current:CC1 Gain* to 32 and summing 256 samples of *0x3C CC1 Current()*.

A table of example gains and resulting LSB values for various sense resistor values and maximum current levels is shown below (with gains quantized to ensure support for the Max Current listed).

Table 5-12.

| Table 5-12. |                    |                    |                         |                       |                           |                           |                                  |

|-------------|--------------------|--------------------|-------------------------|-----------------------|---------------------------|---------------------------|----------------------------------|

| Rsense (μΩ) | Max Current<br>(A) | Max Voltage<br>(V) | Min LSB<br>Allowed (mA) | Quantized CC1<br>Gain | Quantized<br>Current Gain | Quantized CC1<br>LSB (mA) | Quantized<br>Current LSB<br>(mA) |

| 5000        | 3                  | 0.015000           | 0.091553                | 524                   | 524                       | 0.091618                  | 0.091618                         |

| 5000        | 15                 | 0.075000           | 0.457764                | 104                   | 104                       | 0.461614                  | 0.461614                         |

| 5000        | 40                 | 0.200000           | 1.220703                | 39                    | 39                        | 1.230970                  | 1.230970                         |

| 2000        | 10                 | 0.020000           | 0.305176                | 393                   | 393                       | 0.305393                  | 0.305393                         |

| 2000        | 50                 | 0.100000           | 1.525879                | 78                    | 78                        | 1.538712                  | 1.538712                         |

| 2000        | 100                | 0.200000           | 3.051758                | 39                    | 39                        | 3.077424                  | 3.077424                         |

| 1000        | 32.767             | 0.032767           | 0.999969                | 240                   | 240                       | 1.000163                  | 1.000163                         |

| 1000        | 50                 | 0.050000           | 1.525879                | 157                   | 157                       | 1.528911                  | 1.528911                         |

| 1000        | 100                | 0.100000           | 3.051758                | 78                    | 78                        | 3.077424                  | 3.077424                         |

| 1000        | 200                | 0.200000           | 6.103516                | 39                    | 39                        | 6.154848                  | 6.154848                         |

| 500         | 32.767             | 0.016384           | 0.999969                | 480                   | 480                       | 1.000163                  | 1.000163                         |

| 500         | 100                | 0.050000           | 3.051758                | 157                   | 157                       | 3.057822                  | 3.057822                         |

| 500         | 250                | 0.125000           | 7.629395                | 62                    | 62                        | 7.743196                  | 7.743196                         |

| 500         | 400                | 0.200000           | 12.207031               | 39                    | 39                        | 12.309696                 | 12.309696                        |

| 250         | 32.767             | 0.008192           | 0.999969                | 960                   | 960                       | 1.000163                  | 1.000163                         |

| 250         | 100                | 0.025000           | 3.051758                | 314                   | 314                       | 3.057822                  | 3.057822                         |

| 250         | 250                | 0.062500           | 7.629395                | 125                   | 125                       | 7.681250                  | 7.681250                         |