## Technical Article Understanding MOSFET Data Sheets, Part 4 - Pulsed Current Ratings

Brett Barr

Welcome back, fellow FET enthusiasts to part four of the "Understanding MOSFET Data Sheets" blog series! Today I'll be talking about pulsed current ratings, how they are calculated, and how they are represented in the safe operating area graph on the FET datasheet.

The pulsed current rating ( $I_{DM}$ ) that appears on the front page of the datasheet, is not unlike the continuous current rating, in that it is a theoretically calculated value. However, unlike the continuous current, the  $I_{DM}$  is only calculated as a function of thermal constraints, from normalizing  $R_{\theta JC}$  to the given pulse duration and duty cycle specified in the footnote of the "Absolute Maximum Ratings" table.

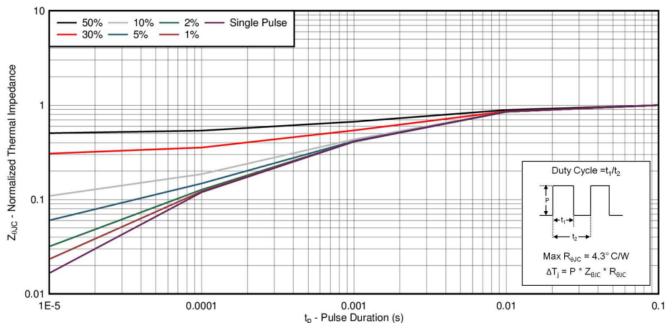

Take for instance, the recently released CSD17579Q5A 30V N-Channel MOSFET. The data sheet for this part has a maximum pulsed current rating of 105A, based on the conditions that the pulse duration is less than or equal to 100µs and the duty cycle is less than or equal to 1%. To determine the transient thermal impedance to use in calculating the  $I_{DM}$ , we will refer to the normalized thermal impedance curve, shown in Figure 1 below. If we look at the 1% duty cycle (brown) line at 100µs, we get a normalization factor of 0.12, which we will use to calculate the max power and thereby current the device can handle for this duration and duty cycle. This value is given by 0.12 multiplied by the max DC  $R_{\theta JC}$  (4.3°C/W), yielding a transient  $Z_{\theta JC}$  of 0.52°C/W.

Figure 1. CSD17579Q5A Normalized Transient Thermal Impedance Curve

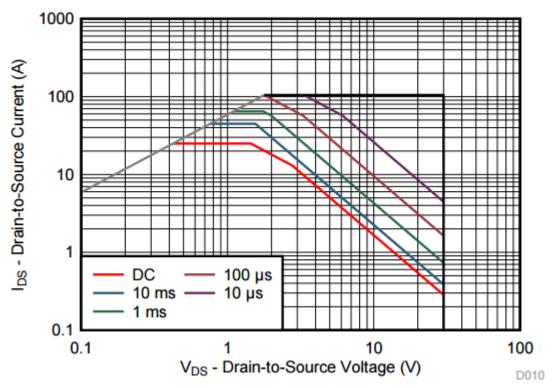

Using this value for thermal impedance and calculating the max current just as we did for its continuous counterpart, we will calculate a thermally limited current of 119A. But wait! The datasheet said 105A! So what gives? If you look at the SOA of the device, shown below in Figure 2, it can be seen that the 100us line actually bumps into the  $R_{DS(ON)}$  limitation before it can get to 119A. This intersection occurs at 105A. So in cases like this, we will retroactively derate the absolute maximum pulsed current as the physical limitations of the device's  $R_{DS(ON)}$  will limit the device from being able to reach its thermal limitation.

Current limitations are calculated for each greater pulse appearing in the SOA, and provided they don't run into the R<sub>DS(ON)</sub> limitation first, this value is where those curves are capped.

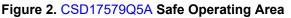

Because the absolute maximum current is entirely theoretical, prior to release of the part we will attempt to get some hard data to further convince ourselves that the part is capable of handling this much power. Unfortunately, our best boards and testers are only capable of pulsing the devices up to 400A, which is why that value has served as an artificial cap for all devices we release. Some vendors have a similar cap, while others do not limit themselves in such a manner. While you will never see TI rate a FET beyond 400A I<sub>DM</sub>, either on the front page or in the SOA, Figure 3 below shows you how ridiculously high the theoretical pulsed current rating can get, in this case for the CSD17570Q5B, a part with very low  $R_{DS(ON)}$  (0.69m $\Omega$  max) and thermal impedance (0.8°C/W). This demonstrates how different vendors can get away with displaying higher ratings, if they play with features such as pulse duration and ignore practical limitations of testing the device.

| Calculated I <sub>DM</sub><br>(A) |       | Duty Cycle      |     |      |      |      |      |                 |

|-----------------------------------|-------|-----------------|-----|------|------|------|------|-----------------|

|                                   |       | 50%             | 30% | 10%  | 5%   | 2%   | 1%   | SINGLE<br>PULSE |

| Pulse<br>Duration<br>(ms)         | 0.001 | 51 <del>9</del> | 670 | 1158 | 1634 | 2561 | 3570 | 13006           |

|                                   | 0.01  | 518             | 667 | 1141 | 1583 | 2361 | 3044 | 4789            |

|                                   | 0.1   | 513             | 652 | 1039 | 1312 | 1623 | 1768 | 1863            |

|                                   | 1     | 487             | 582 | 749  | 799  | 820  | 822  | 823             |

|                                   | 10    | 409             | 424 | 433  | 433  | 433  | 433  | 433             |

|                                   | DC    | 367             | 367 | 367  | 367  | 367  | 367  | 367             |

## Figure 3. CSD17570Q5B Calculated Pulsed Currents

In part five of "Understanding MOSFET data sheets," I will provide a similar analysis for the pulsed current rating,  $I_{DM}$ , and show how this ties into the other parameters on the datasheet, including the SOA. In the meantime,

watch a video "NexFET™:Lowest Rdson 80 and 100V TO-220 MOSFETs in the World" and consider one of TI's NexFET power MOSFET products for your next design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated