SNAS518J July 2011 – July 2015 ADC12D1800RF

PRODUCTION DATA.

- 1 Device Overview

- 2 Revision History

- 3 Pin Configuration and Functions

-

4 Specifications

- 4.1 Absolute Maximum Ratings

- 4.2 ESD Ratings

- 4.3 Recommended Operating Conditions

- 4.4 Thermal Information

- 4.5 Converter Electrical Characteristics: Static Converter Characteristics

- 4.6 Converter Electrical Characteristics: Dynamic Converter Characteristics

- 4.7 Converter Electrical Characteristics: Analog Input / Output and Reference Characteristics

- 4.8 Converter Electrical Characteristics: I-Channel to Q-Channel Characteristics

- 4.9 Converter Electrical Characteristics: Sampling Clock Characteristics

- 4.10 Converter Electrical Characteristics: AutoSync Feature Characteristics

- 4.11 Converter Electrical Characteristics: Digital Control and Output Pin Characteristics

- 4.12 Converter Electrical Characteristics: Power Supply Characteristics

- 4.13 Converter Electrical Characteristics: AC Electrical Characteristics

- 4.14 Converter Electrical Characteristics: Serial Port Interface

- 4.15 Converter Electrical Characteristics Calibration

- 4.16 Typical Characteristics

-

5 Detailed Description

- 5.1 Overview

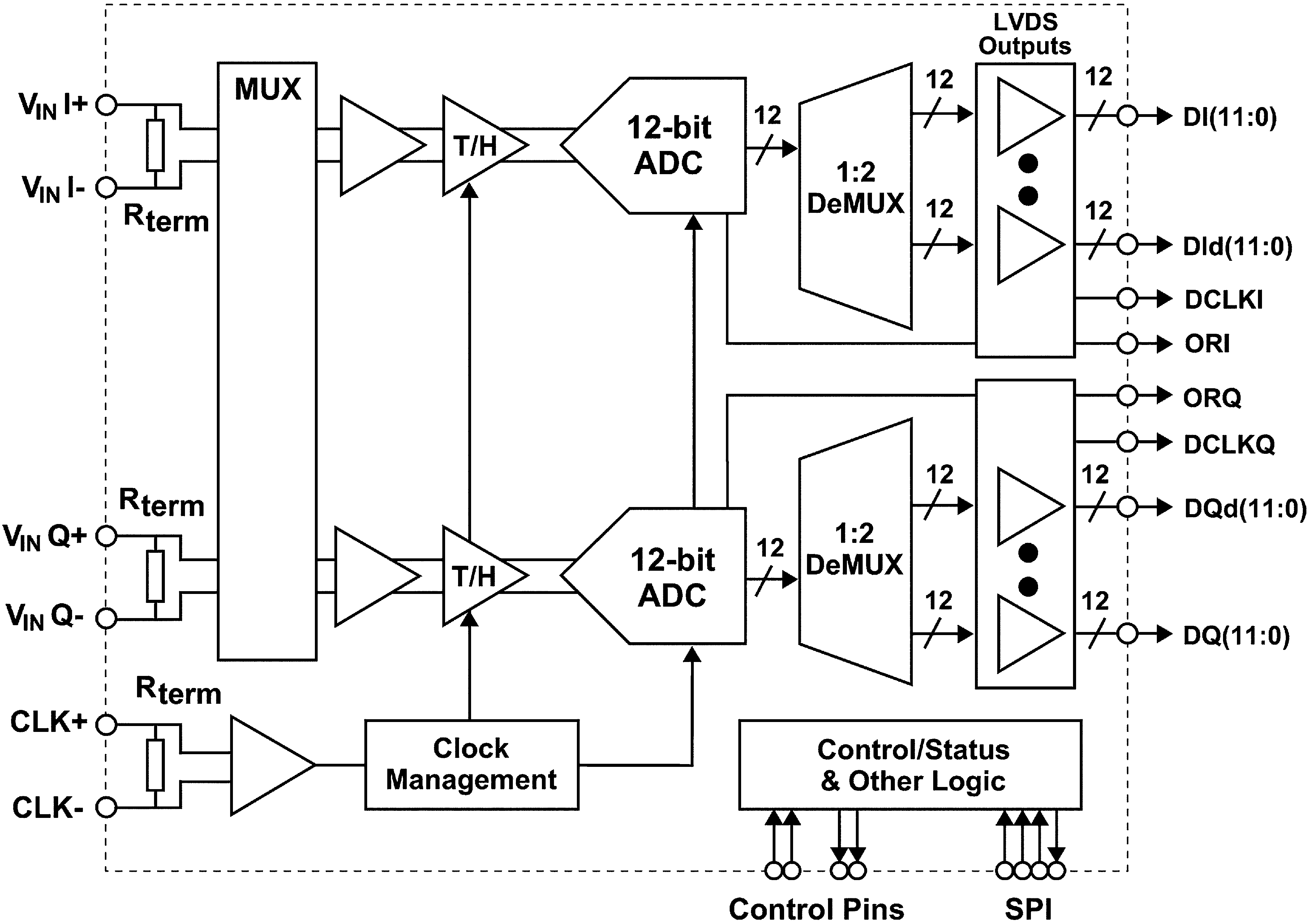

- 5.2 Functional Block Diagram

- 5.3 Feature Description

- 5.4 Device Functional Modes

- 5.5

Programming

- 5.5.1

Control Modes

- 5.5.1.1

Non-Extended Control Mode

- 5.5.1.1.1 Dual Edge Sampling Pin (DES)

- 5.5.1.1.2 Non-Demultiplexed Mode Pin (NDM)

- 5.5.1.1.3 Dual Data Rate Phase Pin (DDRPh)

- 5.5.1.1.4 Calibration Pin (CAL)

- 5.5.1.1.5 Calibration Delay Pin (CalDly)

- 5.5.1.1.6 Power Down I-channel Pin (PDI)

- 5.5.1.1.7 Power Down Q-channel Pin (PDQ)

- 5.5.1.1.8 Test Pattern Mode Pin (TPM)

- 5.5.1.1.9 Full-Scale Input Range Pin (FSR)

- 5.5.1.1.10 AC / DC-Coupled Mode Pin (VCMO)

- 5.5.1.1.11 LVDS Output Common-mode Pin (VBG)

- 5.5.1.2 Extended Control Mode

- 5.5.1.1

Non-Extended Control Mode

- 5.5.1

Control Modes

- 5.6 Register Maps

- 6 Application and Implementation

- 7 Power Supply Recommendations

- 8 Layout

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

1 Device Overview

1.1 Features

- Excellent Noise and Linearity Up to and Above fIN = 2.7 GHz

- Configurable to Either 3.6 GSPS Interleaved or 1800 MSPS Dual ADC

- New DESCLKIQ Mode for High Bandwidth, High Sampling Rate Apps

- Pin-Compatible with ADC1xD1x00, ADC12Dx00RF

- AutoSync Feature for Multi-Chip Synchronization

- Internally Terminated, Buffered, Differential Analog Inputs

- Interleaved Timing Automatic and Manual Skew Adjust

- Test Patterns at Output for System Debug

- Time Stamp Feature to Capture External Trigger

- Programmable Gain, Offset, and tAD Adjust

- 1:1 Non-Demuxed or 1:2 Demuxed LVDS Outputs

- Key Specifications

- Resolution: 12 Bits

- Interleaved 3.6 GSPS ADC (all typical)

- IMD3 (Fin = 2.7GHz at -13dBFS) –62 dBc

- IMD3 (Fin = 2.7GHz at -16dBFS) –64 dBc

- Noise Floor Density -155.0 dBm/Hz

- Power 4.29 W

- Dual 1800 MSPS ADC, Fin = 498 MHz

- ENOB 9.3 Bits (typ)

- SNR 58.1 dB (typ)

- SFDR 71.7 dBc (typ)

- Power per Channel 2.15 W (typ)

1.2 Applications

- 3G/4G Wireless Basestation

- Receive Path

- DPD Path

- Wideband Microwave Backhaul

- RF Sampling Software Defined Radio

- Military Communications

- SIGINT

- RADAR / LIDAR

- Wideband Communications

- Consumer RF

- Test and Measurement

1.3 Description

The 12-bit 1.8 GSPS ADC12D1800RF is an RF-sampling GSPS ADC that can directly sample input frequencies up to and above 2.7 GHz. The ADC12D1800RF augments the very large Nyquist zone of TI’s GSPS ADCs with excellent noise and linearity performance at RF frequencies, extending its usable range beyond the 3rd Nyquist zone.

The ADC12D1800RF provides a flexible LVDS interface which has multiple SPI programmable options to facilitate board design and FPGA/ASIC data capture. The LVDS outputs are compatible with IEEE 1596.3-1996 and supports programmable common mode voltage. The product is packaged in a lead-free 292-ball thermally enhanced BGA package over the rated industrial temperature range of –40°C to +85°C.

To achieve the full rated performance for Fclk > 1.6 GHz, it is necessary to write the max power settings once to Register 6h via the Serial Interface; see Section 5.6.1, Register Definitions, for more information.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| ADC12D1800RF | BGA (292) | 27.00 mm x 27.00 mm |

1.4 Functional Block Diagram