JAJSED4A September 2013 – January 2018 CSD13202Q2

PRODUCTION DATA.

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DQK|6

サーマルパッド・メカニカル・データ

発注情報

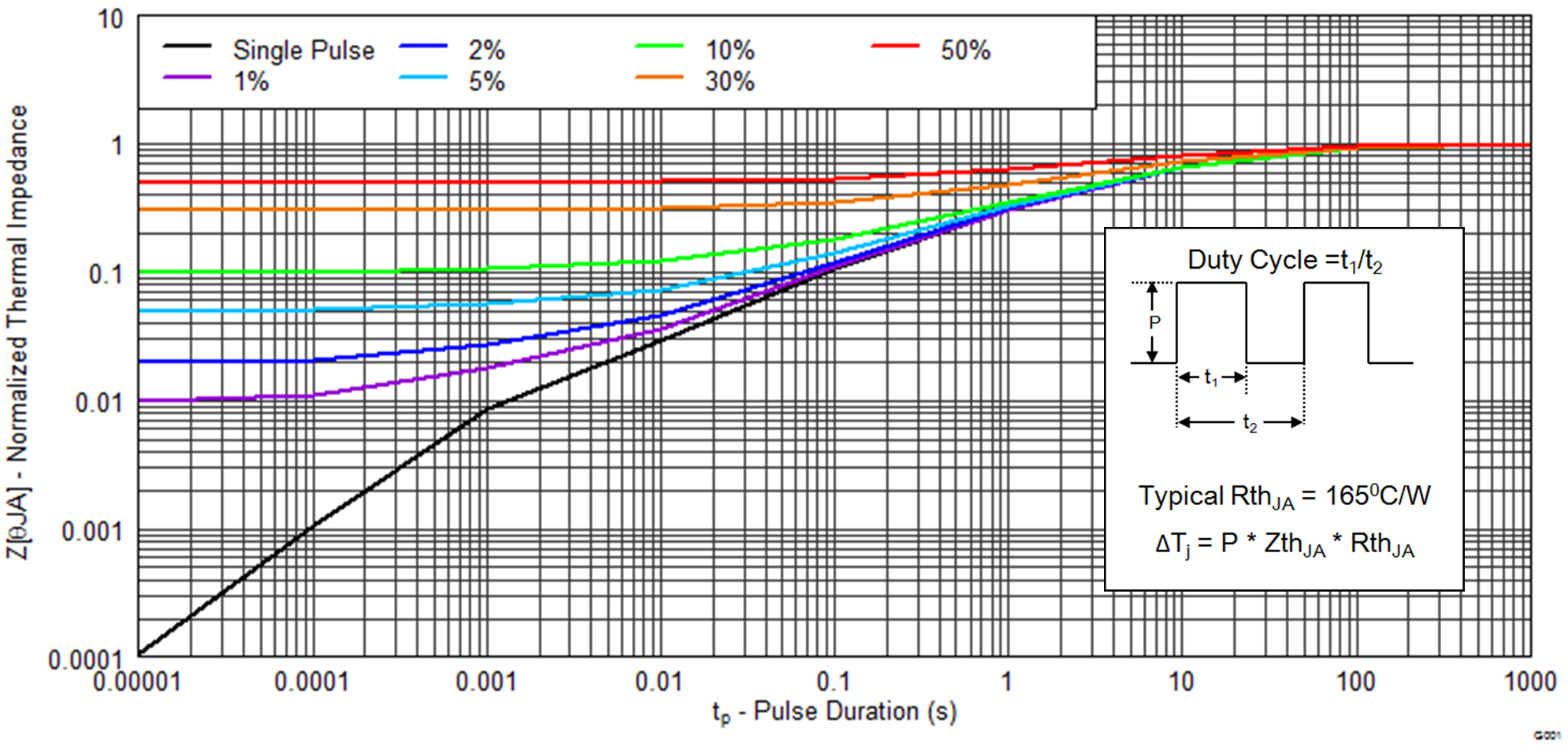

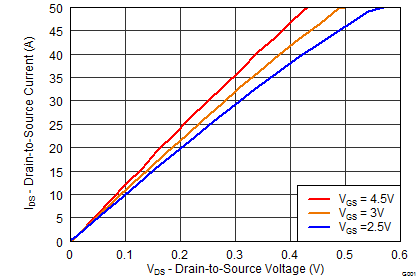

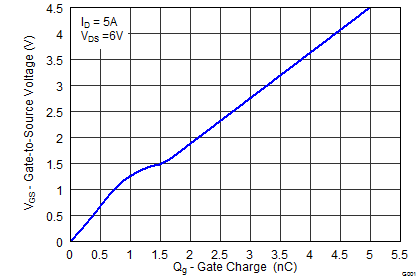

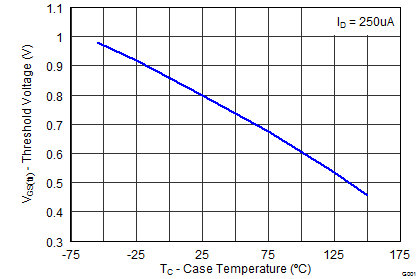

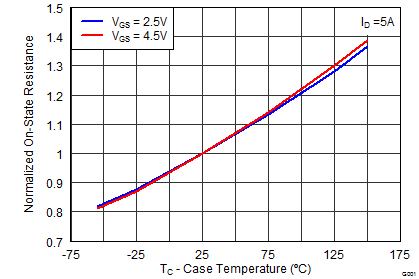

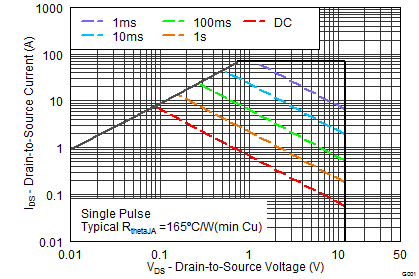

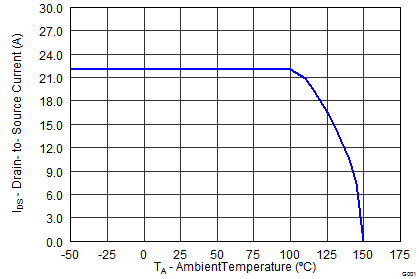

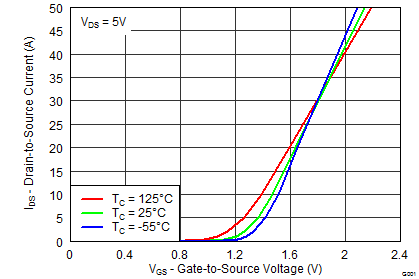

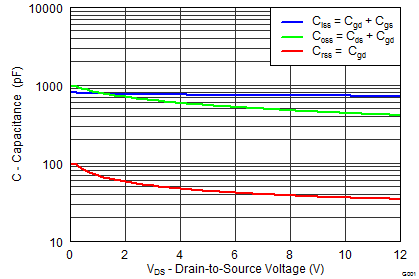

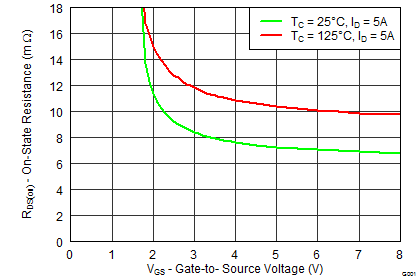

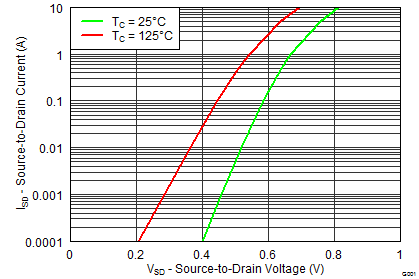

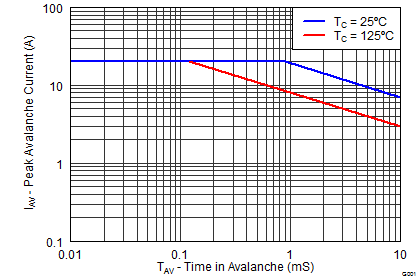

5.3 Typical MOSFET Characteristics

TA = 25°C unless otherwise stated

Figure 1. Transient Thermal Impedance

Figure 2. Saturation Characteristics

Figure 4. Gate Charge

Figure 6. Threshold Voltage vs Temperature

Figure 8. Normalized On-State Resistance vs Temperature

Figure 10. Maximum Safe Operating Area

Figure 12. Maximum Drain Current vs Temperature

Figure 3. Transfer Characteristics

Figure 5. Capacitance

Figure 7. On-State Resistance vs Gate-to-Source Voltage

Figure 9. Typical Diode Forward Voltage

Figure 11. Single Pulse Unclamped Inductive Switching